Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# Fault-Tolerant Distributed Algorithms for On-Chip Tick Generation: Concepts, Implementations and Evaluations

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Leitung von

A.o.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Institut für Technische Informatik Embedded Computing Systems Group Technische Universität Wien

eingereicht an der

Technischen Universität Wien Fakultät für Informatik

von

#### Dipl.-Ing. Mag.rer.soc.oec. Gottfried Fuchs

gottfried.fuchs@inode.at

Matrikelnummer: 9825939 Canavesegasse 14/4 A-1230 Wien, Österreich

Wien, August 2009

### Kurzfassung

Im Zuge dieser Dissertation wird ein neuartiger Ansatz zur On-Chip Generierung eines fehlertoleranten Taktes entwickelt und im Detail vorgestellt. Die Relevanz der Forschungsarbeiten wird dabei mit den immer kleiner werdenden Strukturgrößen im Chip-Design und dem damit einhergehenden Anstieg der Fehlerraten motiviert. Um zukünftige Schaltungen ausreichend robust gestalten zu können, muss in Anbetracht der erhöhten Fehlerraten unter anderem auch das Taktsignal, welches einen kritischen "single point of failure" von synchronen Schaltungen darstellt, durch Fehlertoleranz-Mechanismen geschützt oder durch fehlertolerante Alternativen ersetzt werden. In der vorliegenden Arbeit wird daher eine solche Alternative zu herkömmlichen zentral getakteten Schaltungen erarbeitet.

Der in dieser Arbeit vorgestellte Taktgenerierungsansatz basiert auf der Hardware-Implementierung eines bekannten verteilten Algorithmus. Das Besondere an dieser Implementierung ist, dass in einem System von  $n \geq 3f + 2$  Knoten f dieser Einheiten beliebig (byzantinisch) fehlerhaft sein dürfen. Einen weiteren wichtigen Vorteil stellt die Tatsache dar, dass im Gegensatz zu herkömmlichen Verfahren keine Taktquellen (Oszillatoren) benötigt werden. Die asynchrone Implementierung des präsentierten Ansatzes ermöglicht es, die Taktsignale synchron zu generieren statt auf die Synchronisation von exisitierenden Taktquellen zurückzugreifen. Desweiteren, und noch viel wichtiger, werden durch die vorgeschlagene Architektur Metastabilitätsprobleme an den Schnittstellen zwischen verschiedenen Taktdomänen gänzlich vermieden.

Die Transformation des im Bereich der Software angesiedelten Algorithmus in die Welt des asynchronen Schaltungsentwurfs stellte sich als nicht trivialer Prozess heraus und repräsentiert einen wichtigen Teil der durchgeführten Arbeiten. Um den aus den zuvor erwähnten Transformationen schlußendlich hervorgehenden VLSI (Very Large Scale Integration) Chip und die darauf aufbauende fehlertolerante Taktgenerierungsarchitektur charakterisieren zu können, wurden umfangreiche Messreihen durchgeführt und ausgewertet. Die Evaluierungen umfassen dabei sowohl die Validierung der aus formalen Modellen des Ansatzes hervorgehenden Verhaltensweisen unter möglichst ungünstigen Randbedingungen (worst-case Szenarien), als auch die detailierte Charakterisierung unter Normalbedingungen. Die durchgeführten Messreihen wurden zusätzlich durch Simulationen unterstützt, um einzelne Betriebsmodi genauer zu analysieren.

Im abschließenden Teil dieser Arbeit werden vorliegende Forschungsergebnisse kurz zusammengefasst. Desweiteren werden Limitierungen des Ansatzes aufgezeigt und mögliche Verbesserungen erwähnt.

### Abstract

In the course of this thesis a novel approach for the on-chip generation of a fault-tolerant clock is developed. At first this is motivated by the fact that with shrinking feature sizes and the accompanying increase of transient failure rates it is more and more desirable to provide VLSI (Very Large Scale Integration) circuits that incorporate mechanisms for fault tolerance. In particular, the conducted research concentrates on the most prominent single point of failure of modern chip design, namely, the clock signal of synchronous circuits. After surveying alternative design approaches and existing schemes for achieving fault tolerance a novel fault-tolerant clocking scheme is introduced.

The proposed clock generation method is based on the hardware implementation of a well known distributed clock synchronization algorithm. Most notably, it provides scalable fault tolerance for up to f arbitrary (Byzantine) failures in a system of  $n \ge 3f + 2$  tick generation nodes. Additionally, the clocking scheme's operation does not rely on the synchronization of clock sources, like quartz oscillators; in fact, the distributed clock signals are generated in a synchronized way. This unique property relieves the design from metastability issues at clock boundaries.

The transformation of the original software-based algorithm to the peculiarities of chip design proved to be an intricate task. Therefore, the major part of the work deals with the design and development process of the algorithm's hardware equivalent finally resulting in a fully operational VLSI chip design. To assess the properties of the novel fault-tolerant clocking approach and to show its feasibility exhaustive evaluations have been performed. The presented assessments aim at a thorough characterization of (i) the developed chip design and (ii) the distributed clock generation scheme on which these chips are based. Additionally, the conducted measurements allowed to validate worst-case measures which were derived in advance from the formal analysis of the clocking approach. In order to attain a more comprehensive characterization of the design, the presented worst-case evaluations have been supported by measurements and simulations for typical operating scenarios.

The presented work concludes with a short summary and a brief treatment of the most notable topics for ongoing and future research.

### Acknowledgements

My personal thanks go to Andreas Steininger, for asking me to join his team and the excellent supervision of this thesis as well as the mentoring during the different phases of work. To Matthias Függer I am especially grateful for the perfect teamwork in the DARTS project<sup>1</sup>, the numerous discussions leading to new insights and publications, and last but not least the detailed feedback on an earlier version of this thesis. In the context of the DARTS project I also want to thank Sigrid Heubeck, Gerald Kempf, Manfred Sust, Franz Zangerl and Roman Zangl from RUAG Aerospace Austria for the fruitful cooperation. For the initial project idea and the strength and endurance which finally led to the DARTS project I want to thank Ulrich Schmid. I also want to thank Thomas Handl for conceiving the standard node's test infrastructure. The discussions with my colleagues Josef Widder and Martin Biely — mostly starting in the evening and lasting half the night — have on the one hand been very exhausting, but on the other hand also helped to broaden my horizon. For her professional proofreading I am once again in deep debt to Angela Schörgendorfer.

Sincere thanks to my family, especially my parents and Sandra. Without your help, all of this would not have been possible.

Gottfried Fuchs Vienna, Austria, August 25, 2009

<sup>&</sup>lt;sup>1</sup>The work received funding from the FIT-IT program of the Austrian bm:vit (contract 809456-SCK/SAI).

For Anna Fennesz (1922-2006) and Susanna Fuchs (1915-2008)

## Contents

| 1        | Pre  | ace                                                                                                                                                                             | 1            |           |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|

|          | 1.1  | Motivation                                                                                                                                                                      | 2            |           |

|          | 1.2  | Design principles                                                                                                                                                               | 1.2 Design   | 3         |

|          |      | 1.2.1 Synchronous design                                                                                                                                                        | 1.2.1        | 4         |

|          |      | 1.2.2 Asynchronous design                                                                                                                                                       | 1.2.2        | 5         |

|          | 1.3  | Related design approaches                                                                                                                                                       | 1.3 Related  | 6         |

|          |      | 1.3.1 Globally asynchronous, locally synchronous                                                                                                                                | 1.3.1        | 6         |

|          |      | 1.3.2 Interconnected rings and oscillators                                                                                                                                      | 1.3.2        | 7         |

|          |      | 1.3.3 The distributed clock generator $\ldots \ldots \ldots$    | 1.3.3        | 8         |

|          |      | 1.3.4 Purely asynchronous design                                                                                                                                                | 1.3.4        | 8         |

|          |      | 1.3.5 Discussion $\ldots \ldots \ldots$                         | 1.3.5        | 9         |

|          | 1.4  | Fault tolerance                                                                                                                                                                 | 1.4 Fault to | 10        |

|          |      | 1.4.1 Fault models in VLSI design 11                                                                                                                                            | 1.4.1        | 11        |

|          | 1.5  | Distributed systems and algorithms                                                                                                                                              | 1.5 Distribu | 12        |

|          |      | 1.5.1 Modeling distributed systems $\ldots \ldots \ldots$       | 1.5.1        | 13        |

|          |      | 1.5.2 Distributed systems failure models $\ldots \ldots \ldots$ | 1.5.2        | 15        |

|          | 1.6  | Fault-tolerant clocking                                                                                                                                                         | 1.6 Fault-to | 16        |

|          | 1.7  | Problem definition and contribution                                                                                                                                             | 1.7 Problem  | 17        |

|          | 1.8  | Structure of the thesis                                                                                                                                                         | 1.8 Structu  | 19        |

| <b>2</b> | Dist | ributed Fault-Tolerant Clocking 21                                                                                                                                              | Distributed  | <b>21</b> |

|          | 2.1  | Definitions and common terms                                                                                                                                                    | 2.1 Definiti | 22        |

|          | 2.2  | Clock synchronization                                                                                                                                                           | 2.2 Clock s  | 23        |

|          | 2.3  | Tick generation                                                                                                                                                                 | 2.3 Tick ge  | 28        |

|          |      | 2.3.1 Algorithms for weaker failure models                                                                                                                                      | 2.3.1        | 32        |

|          | 2.4  | Hardware implementation challenges 33                                                                                                                                           | 2.4 Hardwa   | 35        |

| 3        | Implemented Fault-Tolerant Tick Generation |                                                                           |                                                                         |  |  |  |  |  |  |

|----------|--------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

|          | 3.1                                        | Constraints, requirements and characteristics                             |                                                                         |  |  |  |  |  |  |

|          | 3.2                                        | Identifying building blocks for an asynchronous hardware implementation . |                                                                         |  |  |  |  |  |  |

|          | 3.3                                        | Hardv                                                                     | vare design considerations                                              |  |  |  |  |  |  |

|          |                                            | 3.3.1                                                                     | Combining fault tolerance and transition signaling                      |  |  |  |  |  |  |

|          |                                            | 3.3.2                                                                     | Glitch avoidance                                                        |  |  |  |  |  |  |

|          |                                            | 3.3.3                                                                     | Ensuring non-interference of subsequent ticks                           |  |  |  |  |  |  |

|          |                                            | 3.3.4                                                                     | Count and compare                                                       |  |  |  |  |  |  |

|          | 3.4                                        | Refine                                                                    | ed tick generation algorithm                                            |  |  |  |  |  |  |

|          |                                            | 3.4.1                                                                     | Signals and zero-bit message channels                                   |  |  |  |  |  |  |

|          |                                            | 3.4.2                                                                     | Component and architecture specification                                |  |  |  |  |  |  |

|          |                                            | 3.4.3                                                                     | Timing constraints                                                      |  |  |  |  |  |  |

|          |                                            | 3.4.4                                                                     | Correctness and performance measures                                    |  |  |  |  |  |  |

| 4        | The                                        | e DAR                                                                     | TS ASIC Implementation                                                  |  |  |  |  |  |  |

|          | 4.1                                        | The b                                                                     | ig picture                                                              |  |  |  |  |  |  |

|          | 4.2                                        | Queue                                                                     | eing ticks                                                              |  |  |  |  |  |  |

|          |                                            | 4.2.1                                                                     | Muller C-Element                                                        |  |  |  |  |  |  |

|          |                                            | 4.2.2                                                                     | Elastic pipeline                                                        |  |  |  |  |  |  |

|          | 4.3                                        | Count                                                                     | ing ticks                                                               |  |  |  |  |  |  |

|          |                                            | 4.3.1                                                                     | Difference Module                                                       |  |  |  |  |  |  |

|          |                                            | 4.3.2                                                                     | Pipeline compare signal generation                                      |  |  |  |  |  |  |

|          | 4.4                                        | Gener                                                                     | ating ticks                                                             |  |  |  |  |  |  |

|          |                                            | 4.4.1                                                                     | Threshold Modules                                                       |  |  |  |  |  |  |

|          |                                            | 4.4.2                                                                     | Tick generation                                                         |  |  |  |  |  |  |

|          | 4.5                                        | TG-A                                                                      | lg implementation characteristics                                       |  |  |  |  |  |  |

|          | 4.6                                        | Discus                                                                    | ssion on algorithm implementations for weaker failure models $\ldots$ . |  |  |  |  |  |  |

|          |                                            | 4.6.1                                                                     | Failure transformation                                                  |  |  |  |  |  |  |

| <b>5</b> | On-                                        | chip E                                                                    | Evaluation and Measurement Setup                                        |  |  |  |  |  |  |

|          | 5.1                                        | Stand                                                                     | ard node                                                                |  |  |  |  |  |  |

|          |                                            | 5.1.1                                                                     | Test support                                                            |  |  |  |  |  |  |

|          | 5.2                                        | Exper                                                                     | imental node                                                            |  |  |  |  |  |  |

|          |                                            | 5.2.1                                                                     | Test support                                                            |  |  |  |  |  |  |

|          |                                            | 5.2.2                                                                     | Reset/set scan chain                                                    |  |  |  |  |  |  |

|          |                                            | 5.2.3                                                                     | Freeze logic                                                            |  |  |  |  |  |  |

|          |                                            | 5.2.4                                                                     | Pipeline extension and overflow detection                               |  |  |  |  |  |  |

| 6                         | Experiment Specifications and Theoretical Foundation           |         |                                                  |     |  |  |  |  |

|---------------------------|----------------------------------------------------------------|---------|--------------------------------------------------|-----|--|--|--|--|

| 6.1 Worst-case properties |                                                                |         |                                                  |     |  |  |  |  |

|                           |                                                                | 6.1.1   | Precision                                        | 98  |  |  |  |  |

|                           |                                                                | 6.1.2   | Accuracy                                         | 100 |  |  |  |  |

|                           |                                                                | 6.1.3   | Slowest and fastest progress                     | 103 |  |  |  |  |

|                           |                                                                | 6.1.4   | Queue size                                       | 104 |  |  |  |  |

|                           |                                                                | 6.1.5   | Booting                                          | 105 |  |  |  |  |

|                           | 6.2                                                            | Averag  | ge case properties                               | 106 |  |  |  |  |

|                           |                                                                | 6.2.1   | Operating condition dependence                   | 106 |  |  |  |  |

|                           |                                                                | 6.2.2   | Start-up behavior                                | 107 |  |  |  |  |

|                           |                                                                | 6.2.3   | Effects of faults                                | 107 |  |  |  |  |

|                           | 6.3                                                            | Suppo   | rtive simulation model                           | 108 |  |  |  |  |

| 7                         | Eva                                                            | luatior | n and Measurement Results                        | 111 |  |  |  |  |

|                           | 7.1                                                            | Assess  | ing and validating the standard node HITS design | 112 |  |  |  |  |

|                           |                                                                | 7.1.1   | Delay validation                                 | 112 |  |  |  |  |

|                           |                                                                | 7.1.2   | Operating condition dependence                   | 113 |  |  |  |  |

|                           |                                                                | 7.1.3   | Jitter and stability                             | 115 |  |  |  |  |

|                           |                                                                | 7.1.4   | Fault tolerance properties                       | 118 |  |  |  |  |

|                           | 7.2 Assessing and validating the experimental node HITS design |         |                                                  |     |  |  |  |  |

|                           |                                                                | 7.2.1   | Delay validation                                 | 120 |  |  |  |  |

|                           |                                                                | 7.2.2   | Elastic pipeline assessment                      | 120 |  |  |  |  |

|                           |                                                                | 7.2.3   | Operating condition dependence                   | 122 |  |  |  |  |

|                           |                                                                | 7.2.4   | Precision                                        | 122 |  |  |  |  |

|                           |                                                                | 7.2.5   | Accuracy                                         | 124 |  |  |  |  |

|                           |                                                                | 7.2.6   | Queue size                                       | 126 |  |  |  |  |

|                           |                                                                | 7.2.7   | Oscillations and start-up behavior               | 128 |  |  |  |  |

| 8                         | Con                                                            | clusio  | ns and Future Work                               | 131 |  |  |  |  |

| Bi                        | Bibliography 133                                               |         |                                                  |     |  |  |  |  |

## LIST OF FIGURES

| 1.1 | Generic design block                                                               | 3  |

|-----|------------------------------------------------------------------------------------|----|

| 1.2 | Logic design block                                                                 | 4  |

| 1.3 | Synchronous logic design block                                                     | 4  |

| 1.4 | Bounded delay (BD) and delay insensitive (DI) asynchronous approach $\ .$ .        | 5  |

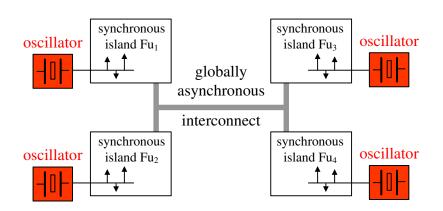

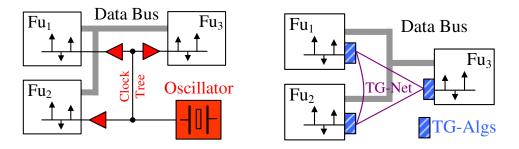

| 1.5 | Globally asynchronous locally synchronous (GALS) architecture $\ldots$ .           | 7  |

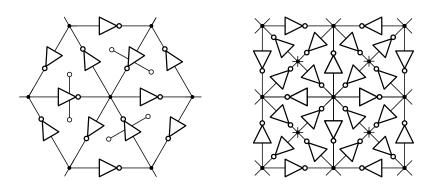

| 1.6 | Interconnected ring oscillator architectures                                       | 8  |

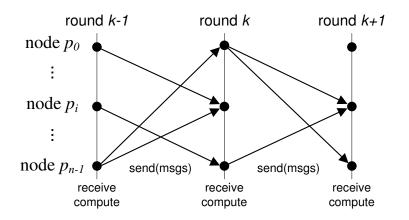

| 1.7 | Execution of a synchronous message-passing algorithm $\ldots \ldots \ldots \ldots$ | 14 |

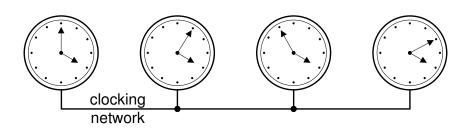

| 1.8 | Example for de-synchronized clocks                                                 | 17 |

| 1.9 | Replacing synchronous clocking by fault-tolerant distributed tick generation       | 18 |

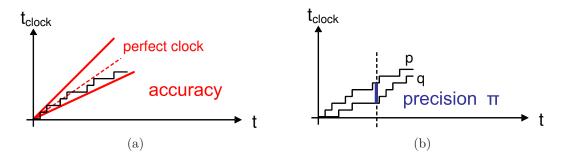

| 2.1 | Accuracy and precision                                                             | 22 |

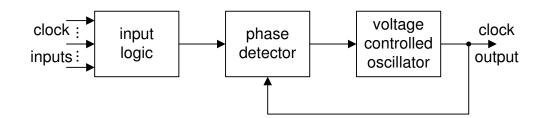

| 2.2 | Phase-locked loop hardware clock synchronization                                   | 27 |

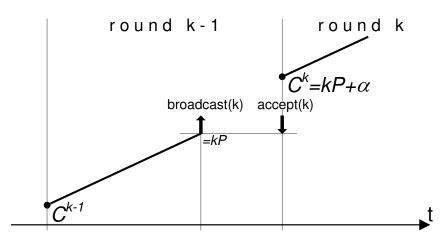

| 2.3 | Non-authenticated broadcast execution at node $p$                                  | 29 |

| 2.4 | Hardware clock signal vs. tick numbers                                             | 35 |

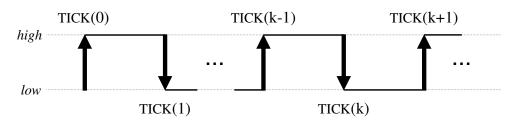

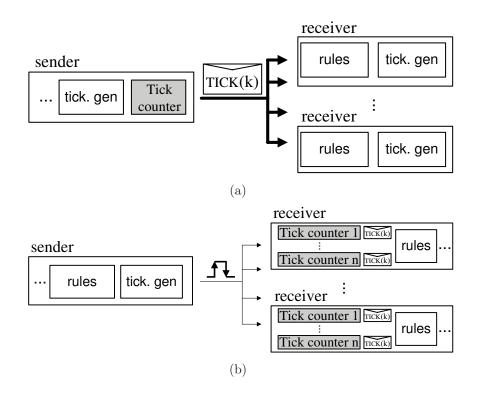

| 3.1 | Schemes for conveying tick number $k$                                              | 41 |

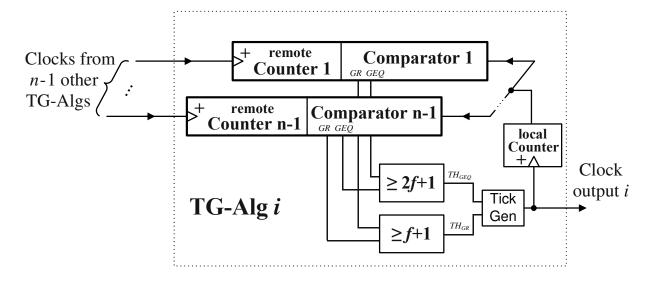

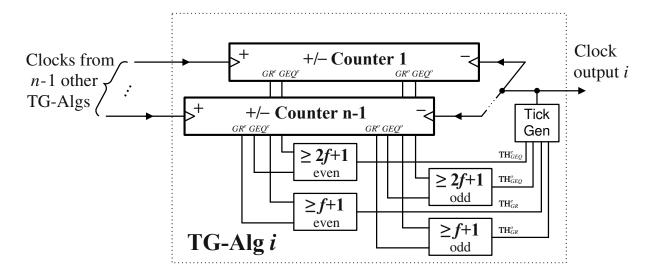

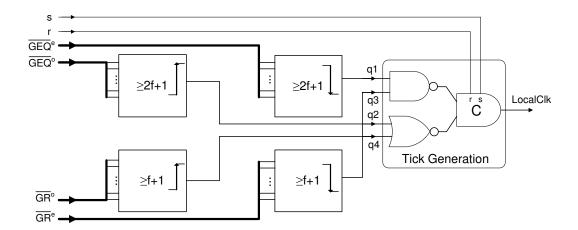

| 3.2 | Basic hardware architecture of Algorithm 7                                         | 43 |

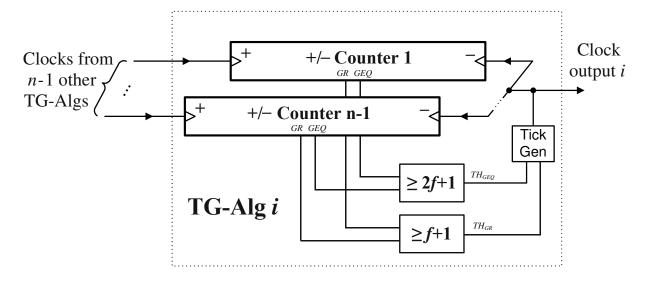

| 3.3 | Tick generation architecture handling relative tick numbers                        | 44 |

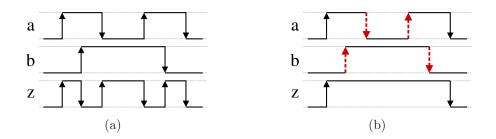

| 3.4 | Transition processing of (a) XOR-gate and (b) OR-gate                              | 45 |

| 3.5 | Tick generation design with separate treatment of even and odd ticks $\ . \ .$     | 47 |

| 3.6 | TG-Alg architecture including observation points                                   | 51 |

| 3.7 | Timing paths of the interlocking constraint                                        | 56 |

| 3.8 | Timing paths of the synchronization constraint                                     | 57 |

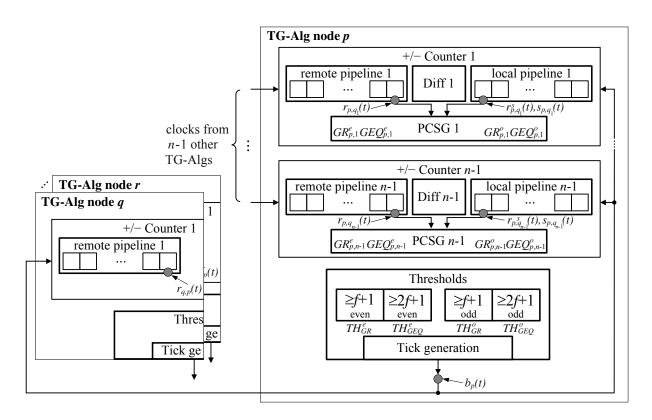

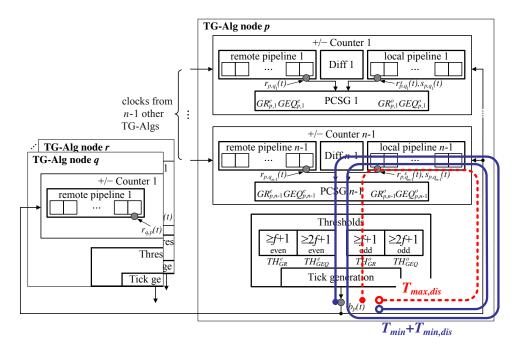

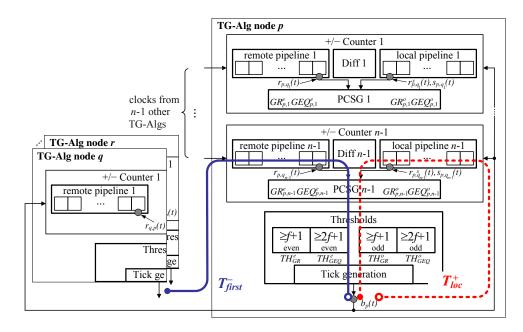

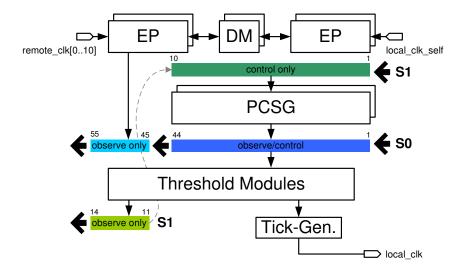

| 4.1 | TG-Alg ASIC design architecture                                                    | 63 |

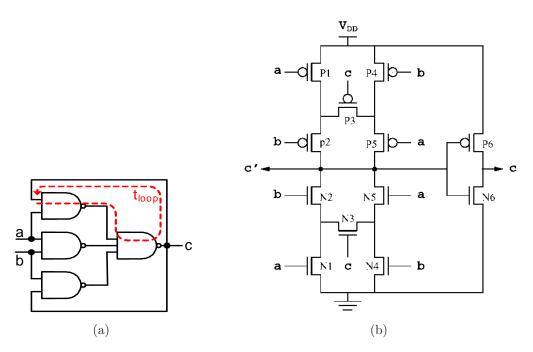

| 4.2 | Muller C-Element implementation on (a) gate level (b) transistor level             | 64 |

| 4.3 | Customized ASIC Muller C-Element                                                   | 65 |

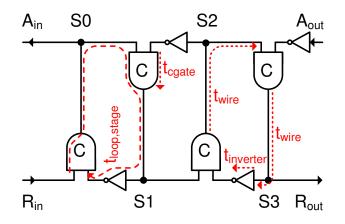

| 4.4  | Elastic pipeline design                                                                                                  | 66  |

|------|--------------------------------------------------------------------------------------------------------------------------|-----|

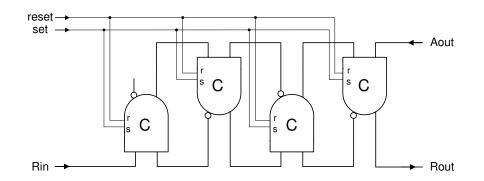

| 4.5  | TG-Alg ASIC elastic pipeline design                                                                                      | 67  |

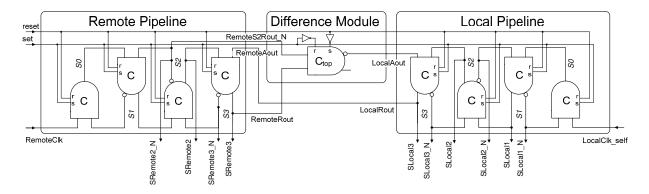

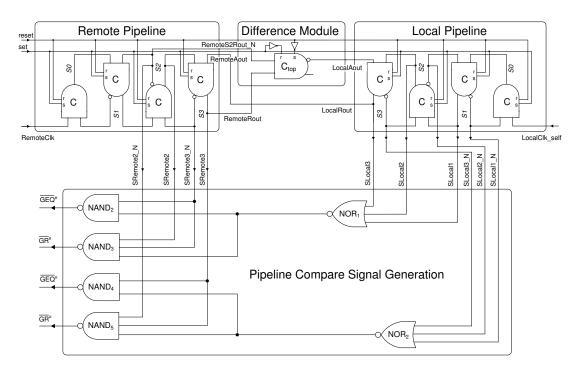

| 4.6  | TG-Alg ASIC Difference Module and elastic pipelines                                                                      | 69  |

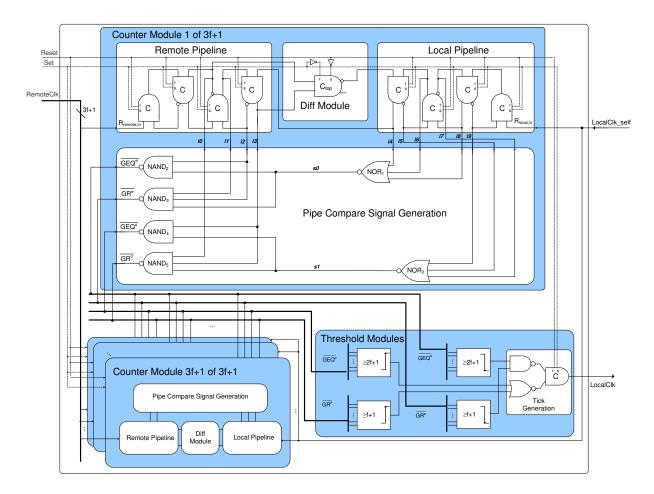

| 4.7  | TG-Alg ASIC $+/-$ Counter Module $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$          | 71  |

| 4.8  | TG-Alg ASIC Threshold Modules and Tick Generation                                                                        | 73  |

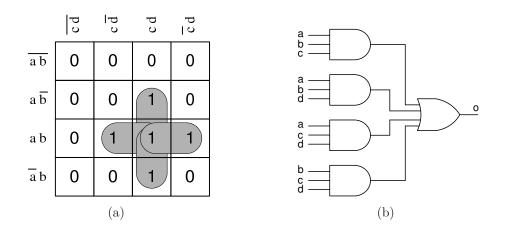

| 4.9  | 3-out-of-4 threshold circuit (a) Karnaugh-Veitsch diagram and (b) sum of products implementation based on standard gates | 74  |

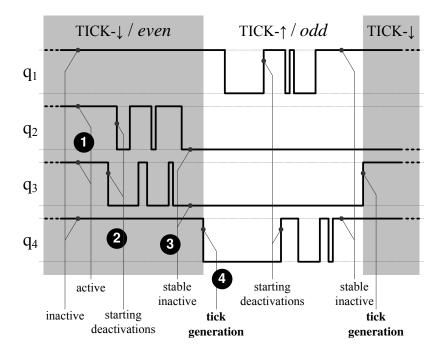

| 4.10 | Example trace of the tick generation signals $q_1, q_2, q_3$ and $q_4$                                                   | 76  |

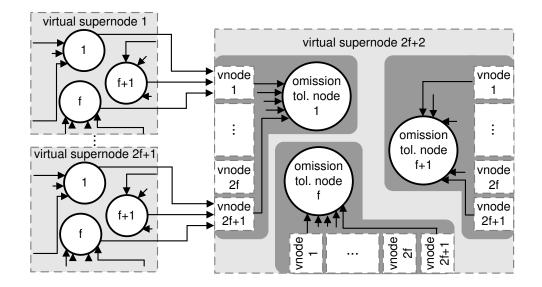

| 4.11 | Simulation of an omission-tolerant system                                                                                | 82  |

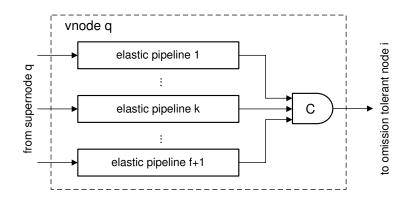

| 4.12 | Implementation of a single vnode of the transformation algorithm                                                         | 82  |

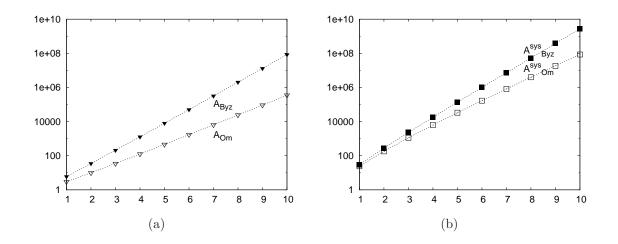

| 4.13 | Implementation complexities for (a) single Byzantine- and omission-tolerant                                              |     |

|      | node and (b) respective systems                                                                                          | 84  |

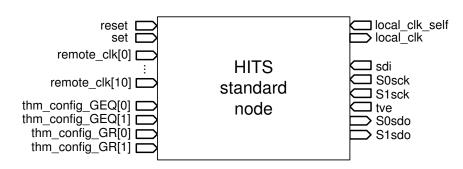

| 5.1  | Interfaces to the HITS standard node design                                                                              | 88  |

| 5.2  | Standard node scan chain overview                                                                                        | 90  |

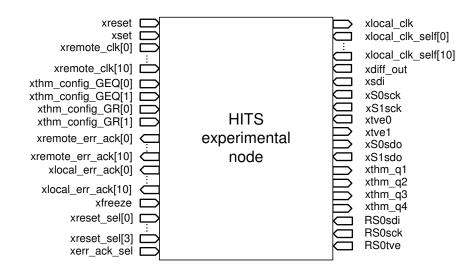

| 5.3  | Interfaces to the HITS experimental node design                                                                          | 91  |

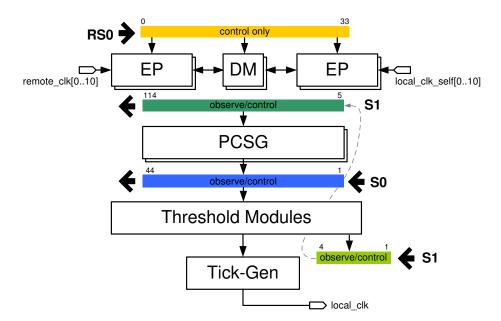

| 5.4  | Experimental node scan chain overview                                                                                    | 92  |

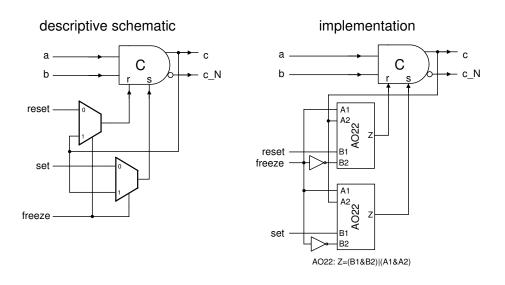

| 5.5  | TG-Alg halting mechanism via Muller C-Element freeze logic enhancement                                                   | 93  |

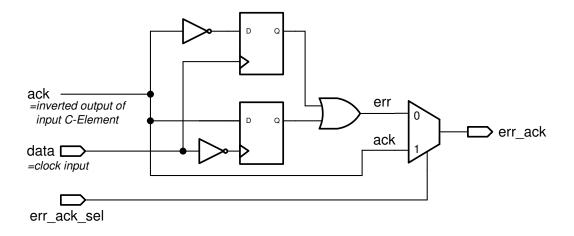

| 5.6  | Pipeline extension and overflow detection circuit                                                                        | 94  |

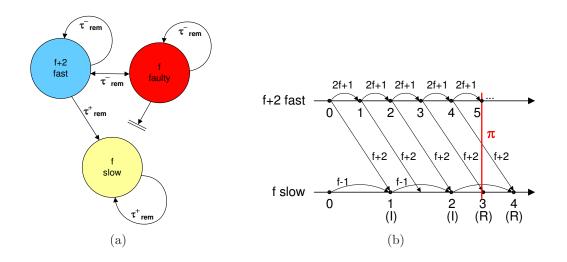

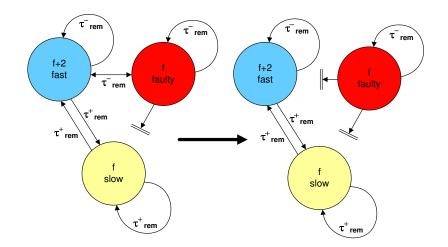

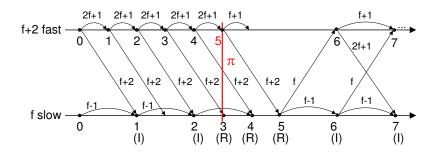

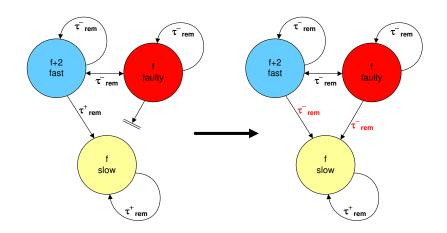

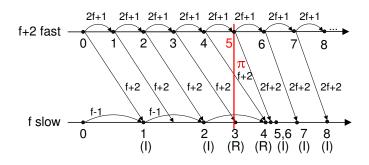

| 6.1  | Evaluation scenario to attain worst-case precision $\pi$                                                                 | 99  |

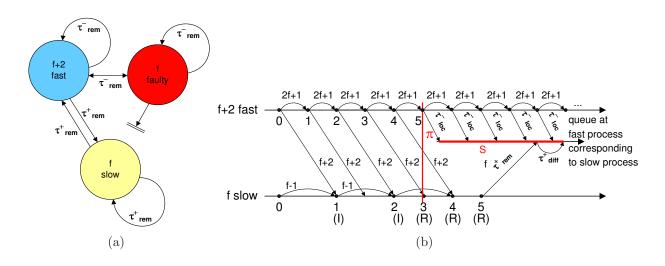

| 6.2  | Evaluation setup to attain worst-case lower bound for accuracy                                                           | 101 |

| 6.3  | Example trace for lower bound for accuracy                                                                               | 102 |

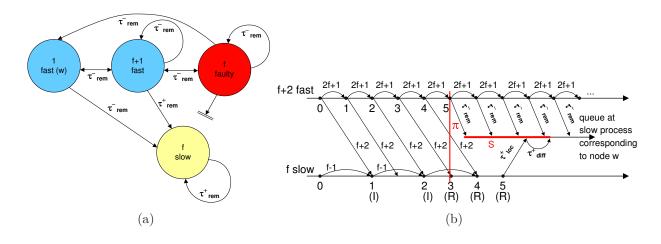

| 6.4  | Evaluation setup to attain worst-case upper bound for accuracy                                                           | 103 |

| 6.5  | Example trace for upper bound for accuracy                                                                               | 103 |

| 6.6  | Evaluation scenario to assess local queue size constraint                                                                | 104 |

| 6.7  | Evaluation scenario to assess remote queue size constraint                                                               | 105 |

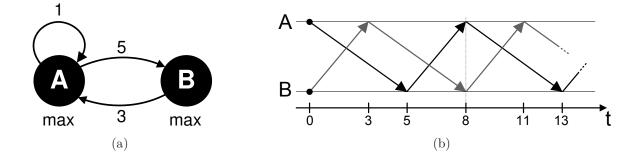

| 6.8  | Two-node wait-for-all system (a) graph representation (b) execution trace .                                              | 108 |

| 6.9  | <min,max,+> system (a) whole graph (b) first projection (c) second pro-</min,max,+>                                      |     |

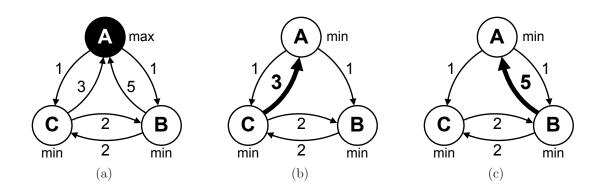

|      | jection                                                                                                                  | 109 |

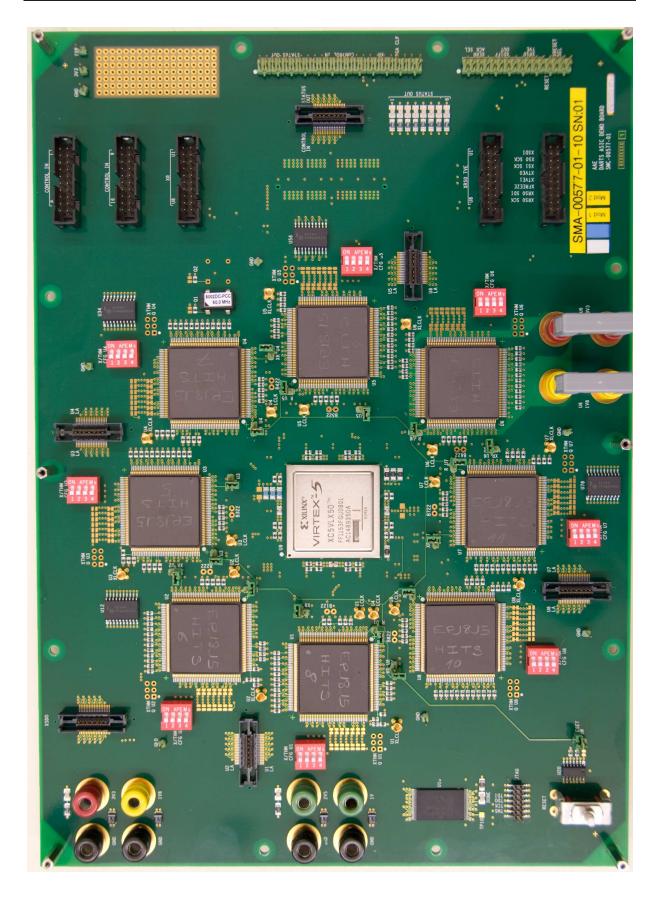

| 7.1  | DARTS prototype board, comprising 8 interconnected HITS chips                                                            | 114 |

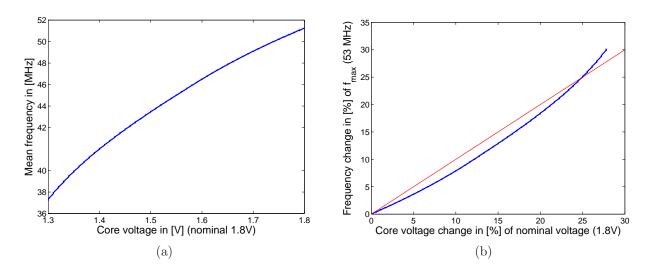

| 7.2  | DARTS cluster's mean clock frequency core voltage dependence $\ . \ . \ .$ .                                             | 115 |

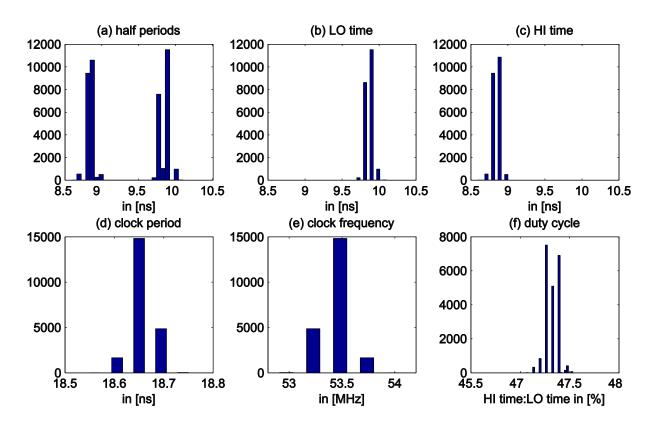

| 7.3  | Statistical single clock evaluation of a running standard node cluster $% \mathcal{S}_{\mathrm{stat}}$                   | 116 |

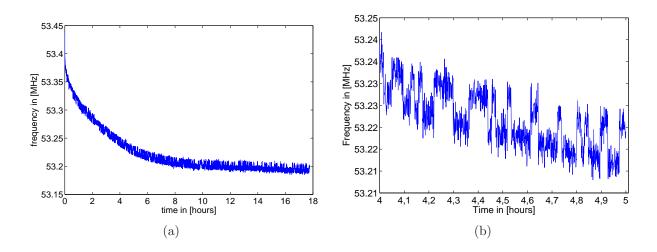

| 7.4  | Long term clock stability (a) 17 hours run, (b) hour four at higher resolution                                           | 117 |

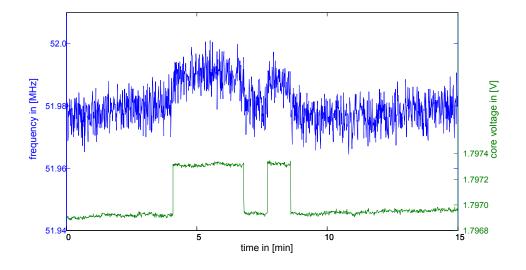

| 7.5  | Frequency and voltage trace showing power supply variations                                                              | 118 |

\_\_\_\_

| 7.6  | Mean frequency (a) trend and (b) histogram of all 8 nodes $\ldots \ldots \ldots$                                   | 119 |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

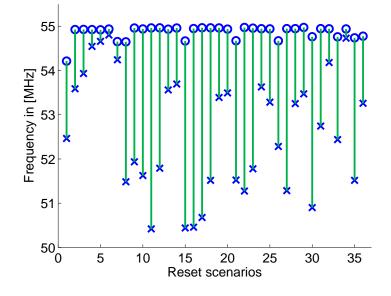

| 7.7  | Mean Frequency (o) pre and (x) post reset of 1 or 2 nodes $\ldots \ldots \ldots$                                   | 120 |

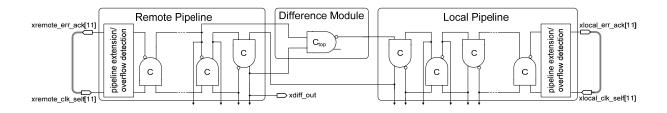

| 7.8  | Ring oscillator implementation via pipeline pair and Difference-Module $\ .$ .                                     | 121 |

| 7.9  | Trace of a ring oscillator with uninitialized pipelines                                                            | 122 |

| 7.10 | Trace of a ring oscillator with initially full pipelines                                                           | 123 |

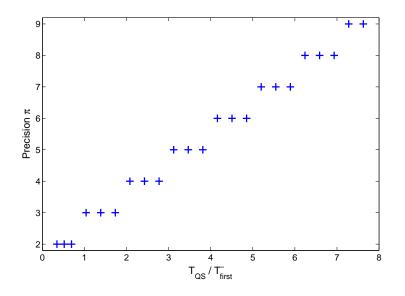

| 7.11 | Precision vs. fastest to slowest path controlled via the maximum remote delay                                      | 124 |

| 7.12 | Verification measurement for accuracy lower bound                                                                  | 126 |

| 7.13 | Local queue size bound verification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 127 |

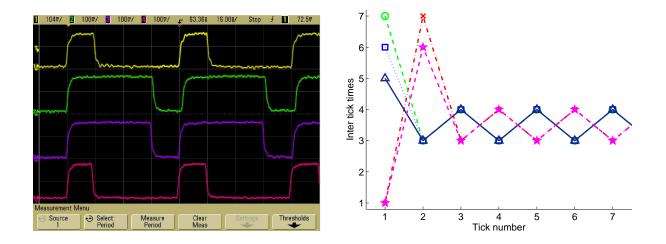

| 7.14 | DARTS cluster with unbalanced delays (a) oscillations of tick generation                                           |     |

|      | periods (b) simulation of settling                                                                                 | 128 |

## LIST OF TABLES

| 1.1 | Comparison of design methodologies                                                                                                                                                 | 10  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Activation patterns for fill-level signals                                                                                                                                         | 72  |

| 4.2 | Hardware effort for queueing and counting ticks                                                                                                                                    | 77  |

| 4.3 | Hardware effort for Threshold Modules                                                                                                                                              | 77  |

| 4.4 | Hardware effort of a single TG-Alg and its components                                                                                                                              | 78  |

| 4.5 | Comparison of Byzantine-, omission- and crash-tolerant algorithms, i.e., Al-<br>gorithms 8, 6 and 5 in a system with $f = 3 \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 79  |

| 4.6 | Implementation complexities of Byzantine- and omission-tolerant system $% \mathcal{A}^{(n)}$ .                                                                                     | 83  |

| 5.1 | Threshold configuration for (a) $2f + 1$ and (b) $f + 1$ circuits                                                                                                                  | 88  |

| 5.2 | Reset-selector configuration patterns                                                                                                                                              | 92  |

| 7.1 | Cluster of 8 standard nodes: voltage scaling                                                                                                                                       | 113 |

| 7.2 | Cluster of 8 experimental nodes: voltage scaling                                                                                                                                   | 123 |

| 7.3 | Characteristics of HITS tick generation                                                                                                                                            | 130 |

## LIST OF ALGORITHMS

| 1 | Non-authenticated algorithm for clock synchronization at node $p$ [81]                                              | 29 |

|---|---------------------------------------------------------------------------------------------------------------------|----|

| 2 | Acceptance function selecting valid clock ticks [81]                                                                | 30 |

| 3 | Consistent broadcast primitive without local clock source $\ldots \ldots \ldots \ldots$                             | 31 |

| 4 | Modified version of Srikanth & Toueg's Byzantine-tolerant tick generation $\left[93\right]$                         | 32 |

| 5 | Crash-tolerant tick generation                                                                                      | 33 |

| 6 | Omission-tolerant tick generation                                                                                   | 34 |

| 7 | By<br>zantine-tolerant tick generation $\left[93\right]$ suitable for bounded tick numbers<br>$% \left[93\right]$ . | 36 |

| 8 | Refined TG-Alg reflecting the asynchronous VLSI building blocks $\ldots$ .                                          | 55 |

| 9 | Transformation algorithm at subnode $p.i$                                                                           | 81 |

### CHAPTER 1

### PREFACE

First things first, but not necessarily in that order.

Doctor Who

S THE title of the thesis already suggests, the presented research follows a multi disciplinary approach. While on one side having VLSI (Very Large Scale Integration) design with electronic circuits and computer chips, the other aspect is given by the area of distributed algorithms and systems. At first sight both topics appear to be completely orthogonal to each other. A closer look at both worlds, however, reveals fundamental similarities, i.e., modern VLSI chips can be seen as microscopically small distributed systems. As a consequence it seems to be quite natural to combine both worlds and for instance use solutions from the distributed systems community to solve current and upcoming problems of VLSI design. High level approaches from distributed systems might be able to alleviate some of the challenging issues and burdens when dealing with modern VLSI circuits. As an example, coping with pronounced parameter variations due to difficulties related to the manufacturing process is a burning issue. Additionally, the increased susceptibility to radiation-induced soft-errors enabled by shrinking transistor feature sizes is also considered a major VLSI design problem [47]. These adverse effects of circuit miniaturization, together with concepts to overcome some of the involved challenges are used as foundation for the problem definition of the thesis. More specifically, the main effort of the conducted research is directed towards the important field of digital circuit clocking. In particular, reliability under variations in manufacturing and operation as well as faults is taken into account, thus leading to the core topic of the work, namely, fault-tolerant clocking (FT-clocking).

### 1.1 MOTIVATION

Advancement in digital electronics is stated to be the most prominent driving force behind technological progress. Electronic devices are omnipresent and almost any innovation involves computer chips in one way or another. In everyday life we are surrounded by and accustomed to electronic devices like cell phones, personal computers, satellite technology, medical imaging, etc. The key enabler for the fact that computer chips are omnipresent is given by the ever increasing processing power and speed of modern digital circuits and the accompanied possibilities for new applications. Over the past 30+ years the increase of digital circuit complexity as well as their performance gain followed Moore's Law [65] quite well, which essentially predicts that the amount of transistors on a chip double about every two years. The miniaturization of transistors which allows Moore's law to persist not only enables the above mentioned performance increase, but also introduces adverse effects. Transistor feature sizes of recent and future computer chips are approaching the dimension of a few dozens of atom diameters. As shown in the recent version of International Roadmap for Semiconductors (ITRS07) [47] it is increasingly difficult to manufacture these extremely small structures in a reliable way. Additionally, process variations in the manufacturing process may lead to severe fluctuations of the processing speed of a chip's components [9]. Furthermore, the diminishingly small electrical charges present in modern transistors are susceptible to different sources of disturbance, e.g., electrical discharge induced by particle hits [5,75,94], crosstalk or electromagnetic interference [60] might yield multiple faults. To maintain reliable computing technological and/or architectural measures have to be taken.

An issue with current circuit design related to the problems described above arises from the fact that the greater part of modern digital circuits follow the synchronous design paradigm. Proper operation of a circuit following this design style utterly relies on a single source—the clock signal. The globally synchronous design with its one large isochronous region<sup>1</sup> is hard to maintain as clock periods are less than the time a signal needs to traverse the whole chip. The distribution of the clock signal from a single source (typically a quartz/crystal oscillator) all over a chip has become an art of its own given the die size of a modern VLSI chip with millions of transistors and its operating frequency in the GHzrange. Tremendous design effort has to be made to distribute the clock signal in such a way that it arrives with minimal skew at every component to guarantee the correct behavior of the synchronous circuit. Facilitated approaches use H-tree and X-tree clock distribution networks combined with mesh and grid interconnects. Additionally, large numbers of clock buffers and de-skewing units have to be placed at carefully chosen positions to guarantee minimal skew between any two clock sinks [31, 70, 74]. An issue arising with these large efforts necessary to achieve proper clock distribution is power consumption. Modern VLSI chips' clock distribution adds up to 25 to 50% of the overall power budget of a chip [21,68]. Referring to the design challenges presented in the previous paragraph the question arises whether or not the apparently strong, but critical clock signal suffers from any of the

<sup>&</sup>lt;sup>1</sup> "The maximum distance that a switching signal can travel across a region, in which the time of flight does not limit the signal propagation, circumscribes a region known as the isochronous region." [61]

adverse effects of technology scaling mentioned above. Despite the fact that the clock tree is driven by strong buffers, in [76] radiation-induced errors have been reported for the clock distribution network of classic synchronous chips using recent semiconductor technology. Moreover, the mechanical properties of clock sources like quartz oscillators are severely limiting system reliability, since sensitivity to vibration, temperature and shock as well as problematic cold start-up behavior have to be noted. One could argue the globally synchronous design style with its single clock source should be replaced by a more promising alternative. In light of the current technology trends global clock distribution with reasonable synchrony is hard to attain, and comes at the price of great effort to properly design the sophisticated clock distribution with its power consuming buffers, grids, meshes and other more complex de-skewing circuits [31, 71].

To give a sound introduction to the research topic and the involved application fields of this thesis the reader is successively introduced to the underlying principles and technologies. In this context the concepts of logic design in general, fault tolerance, as well as distributed systems and algorithms are established to provide common terms for the rest of the thesis. Moreover, design alternatives as possible remedies for the hard-pushed synchronous approach will be surveyed.

#### 1.2 Design principles

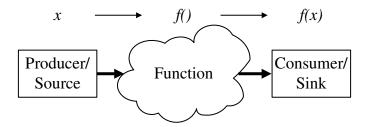

Electronic circuits in general comprise a multitude of (different) components to implement a desired functionality. Signal processing in such components follows a scheme similar to the one shown in Figure 1.1. A producer/source block generates a data item x that is further processed by a functional unit f(). The end of such a generic processing stage is given by a consumer/sink, operating on the results f(x) of the previous blocks.

Figure 1.1: Generic design block

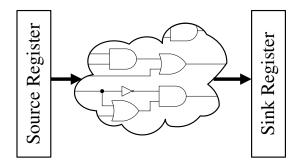

Typical design components for producer/source and consumer/sink blocks are given by storage elements (registers), whereas the function f() may comprise simple logic gates like AND-, OR-gate, inverter, register, and the like. The processing of these design units has to be controlled in a way such that old and new data cannot interfere with each other in an unintended way. Hence, in general, data is first read from a producer/source-register, afterwards processed by some logic elements and in the end stored in a consumer/sinkregisters as depicted in Figure 1.2. However, what is missing in Figure 1.2 as well as Figure 1.1 is the mechanism which ensures the above demanded non-interference of different data waves. In other words, the issuing of data items and their consumption has to be coordinated somehow.

Figure 1.2: Logic design block

This fundamental kind of flow-control/data synchronization can be achieved by different means, the approaches typically being grouped into design styles following the synchronous or asynchronous design paradigm. It further has to be noted that the better part of currently available computer chips (processors, micro-controllers, FPGAs, etc.) are built to work according to the synchronous design paradigm. However, asynchronous design has its niche application fields, e.g., ultra low power circuits [56] and seems to provide superior properties when dealing with large parameter variations of current and future deep sub-micron and nanoscale devices [9, 10]. Furthermore, specialized designs, for instance high-speed random access memory (RAM) [17], field programmable gate arrays (FPGAs) operating at GHz speed [84] as well as terabit network routers [86], may also rely on asynchronous design styles to achieve elevated performance goals.

#### 1.2.1 Synchronous design

A synchronous design is characterized by the centralized mechanism controlling the instants when data is stored into registers, i.e., the combinatorial logic has finished its computations

Figure 1.3: Synchronous logic design block

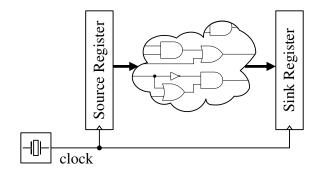

Figure 1.4: Bounded delay (BD) and delay insensitive (DI) asynchronous approach

and is ready for new data. As shown in Figure 1.3 each register is controlled by the same clock signal which originates from one single clock source (e.g., a quartz oscillator) and provides a global time base. All registers simultaneously store the currently available data as soon as a clock transition (for instance low-to-high) occurs at the registers' clock inputs. For proper operation of the synchronous approach it is of utmost importance that clock transitions are received and processed nearly at the same time at all registers (with only small timing margins). To ensure this global isochronous behavior clock distribution with minimal skew is the most critical and challenging part of synchronous circuit design [31].

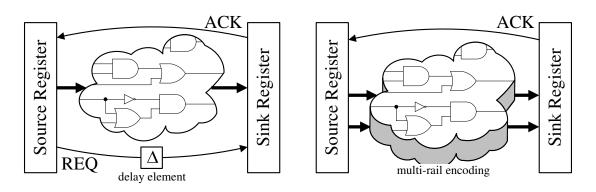

#### 1.2.2 Asynchronous design

In contrast to the global/centralized time base of the synchronous design approach, asynchronous methodologies rely on local handshakes between any source/sink pair. This handshake is partitioned into two parts, (i) the request (REQ) generated by the source indicating the sink that new data is available and (ii) the acknowledge (ACK) indicating that the sink has already stored the data and is ready to process new one. Unlike the synchronous approach, in asynchronous circuit design there is no single generally adopted methodology, but there are rather a few different design styles to solve the fundamental data synchronization problem.

By picking two popular asynchronous design methodologies the manifoldness of asynchronous data processing is illustrated. The bounded delay (BD) approach [80] depicted in Figure 1.4 (left panel) and the delay insensitive (DI) approach [26] shown in Figure 1.4 (right panel) are the chosen representatives. Both the bounded delay and the delay insensitive approach have in common that the generation of the ACK signal is typically triggered together with the storage of data into the sink register. The difference of the BD and DI methodology is in the way the REQ signal—indicating new valid data—is generated. In BD methodology the data source issues an explicit REQ signal together with the data. Correct circuit behavior is achieved by the insertion of individual matched delay elements into the signal-path of every REQ signal, cf. Figure 1.4. The delay elements have to be configured in a way that ensures that data—after its actual processing via some combinatorial logic—is already valid when REQ arrives. In contrast to BD, the delay insensitive approach has no explicit request signal. The information that valid data is available is directly encoded into the data itself—there is no need to know timing parameters of the design or to insert matching delays<sup>2</sup>. To be able to convey this validity information to the sink some sort of extended signal encoding has to be used. For example in Four State Logic (FSL) [63] or Null Convention Logic (NCL) [26] two signal rails are used to be able to sufficiently encode every data bit. In essence there must be a coding for invalid data in addition to HI and LO. Independent of timings and delays a completion detection unit at the sink decodes the dual-rail data signal, extracts the validity information and decides accordingly if the data is valid and can be consumed.

A more thorough introduction to asynchronous design principles and methodologies can be found in Hauck [43] as well as the textbooks by Myers [67] and Sparsø/Furber [80].

#### 1.3 Related design approaches

#### 1.3.1 GLOBALLY ASYNCHRONOUS, LOCALLY SYNCHRONOUS

The Globally Asynchronous Locally Synchronous (GALS) approach provides an alternative alleviating the stringent clock distribution issues of the purely synchronous design style [12]. Systems following the GALS design style are based on the generic architecture depicted in Figure 1.5. Small (local) synchronous islands implement functions (sub-tasks) of the whole system. Each local island's function is executed using the traditional synchronous design style, whereas global interaction follows an asynchronous communication style. Each island is provided with its own oscillator as clock source for the locally synchronous computations. Compared to the high effort for global clocking of a purely synchronous system in local synchronous islands skew optimization of the clock signal is much easier to attain. Although GALS simplifies the clock distribution to some extent, some other issues are still left. The need for a particular oscillator for each synchronous island adds additional mechanical components (quartz oscillators) to a system which clearly decreases reliability of the whole design. As an alternative to the error-prone quartz oscillators (which are sensitive to, e.g., vibration, temperature, shock, etc.) on-chip RC-oscillators could be used. However, RCoscillators are known for their strong dependence on operating conditions like temperature and supply voltage which leads to frequency changes in the range of 10 to 30%. There are several issues in the context of the local clocking of GALS systems. On the one hand the extremely unstable clock signal of RC-oscillators might be a problem for many applications. On the other hand, there are mechanical issues with quartz-oscillators which are known to be problematic in harsh environments like the aero-space domain. In general, if compared to a synchronous system the GALS concept has two major disadvantages. First of all, a

$<sup>^{2}</sup>$ To be more precise, strict DI circuits offer only very limited functionality. Therefore, implementations typically follow the quasi delay insensitive (QDI) approach which, however, introduces a constraint for forking paths [58].

Figure 1.5: Globally asynchronous locally synchronous (GALS) architecture

GALS design does not implicitly provide the convenient common notion of time within the system which most hardware designers are used to and design tools are made for. All clock sources are free running—no synchronization precision among the clocks can be assumed as they may drift arbitrarily apart from each other. As long as communication only affects a local island there is no problem and everything stays the same way as in a synchronous design. However, with communication leaving the bounds of a local island's clock domain and asynchronously traversing the chip to another island introduces the need for synchronization. The fact that the interface between globally asynchronous communication and locally synchronous data processing has to incorporate some sort of synchronizer circuits poses the second, probably the most severe disadvantage of GALS. Unfortunately, synchronizing clock domains with arbitrary, possibly changing, relation to each other, cannot be solved in a safe way. Metastability issues might even upset the synchronizer circuits [41] and can only be made more unlikely by adding synchronizer stages. Taking parameter variations and clock jitter into account synchronizers have to be designed very conservatively, thus introducing significant performance penalties into the asynchronous/synchronous interfaces.

Recent synchronizer implementations incorporate sophisticated designs using stoppable (pausable) and/or stretchable clocks [22, 66] to reduce performance loss due to synchronization.

#### 1.3.2 INTERCONNECTED RINGS AND OSCILLATORS

This concept proposed by Maza and Aranda in [61, 62] also addresses the difficulties of synchronous clock distribution in GHz designs and presents an alternative approach for generating and distributing clocks. The design relies on the self-oscillation property when interconnecting an odd number of inverters in a ring topology (shown in Figure 1.6) and achieves high clock frequencies due to the simplicity of the design. Inverter and buffer placement of the proposed architecture determines wiring costs (in terms of wire length), speed and skew of the generated clocks. The design especially fits as on-chip clocking

Figure 1.6: Interconnected ring oscillator architectures

scheme for the previously introduced GALS systems. It can be seen as a refinement of the GALS, RC-oscillator clocking. Due to the fact that all inverters of the clock generation scheme are interconnected directly (locally) or indirectly (globally, through some additional inverter stages) with each other, the local islands of a GALS system cannot arbitrarily desynchronize (at least in the fault-free case). This property severely eases synchronization within the GALS design since the synchronizers can take advantage of the fact that the local clocks are not entirely unrelated.

#### 1.3.3 The distributed clock generator

The scheme of a distributed clock generator (DCG) introduced by Fairbanks and Moore [24, 25] represents a special form of asynchronous FIFO implementation for the purpose of on-chip generation and distribution of a synchronized clock. Similarly to the approach by Maza and Aranda, interconnected clock generation hardware is distributed in a grid all over the chip, but the locally generated clocks are generated at approximately the same instant having only small skew. Every DCG instance is interconnected with its four neighbors and half of the DCG units are initialized with a clock token. Due to the asynchronous FIFO implementation of each DCG the so-called Charlie effect [25] ensures that clock tokens are passed over to neighboring nodes in a synchronous way, generating a chip wide synchronized clock signal (the Charlie effect describes the force that slows down a subsequent token within a FIFO if it is closing in on a previous one).

#### 1.3.4 Purely asynchronous design

Asynchronous design styles [43] are considered a viable alternative for synchronous design in the future. This is at least true for special application fields like low power circuits [56]. Moreover, some recent work [17,86] shows the general applicability in high-speed design. With asynchronous design the burden of clock distribution can be entirely eliminated and the clock tree be substituted by far less timing critical local handshake signals. Parameter variations are much less problematic in the context of, e.g., quasi delay-insensitive circuits [59] since only performance but not the correct function is influenced by variations. Furthermore, the inherent robustness of asynchronous design styles allows to address the issue of increased failure rates in future VLSI technology [32,48] to some extent. On the downside of asynchronous design the manifoldness of design styles (bounded delay, quasi delay-insensitive, scalable delay-insensitive, etc.) prevent a generally accepted methodology. The huge diversity in asynchronous design styles additionally leads to lacking design and verification tools which further handicaps the wide-spread usage. Moreover, non-negligible area overhead, higher design complexity and the more intricate circuit testing also have to be mentioned. Despite the fact that a certain robustness is inherent to asynchronous designs, established techniques, like the majority voting of triple modular redundancy schemes (TMR), for implementing fault tolerance cannot be directly applied to asynchronous systems. This limitation is based on the fact that sometimes it might not be clear if data to be voted is faulty, e.g., missing due to a crashed sender, or if it simply is late [18].

#### 1.3.5 DISCUSSION

In summary, none of the above described alternatives to globally synchronous clocking sufficiently addresses the reliability issues of multiple transient and permanent faults that are upcoming with current and future technology scaling. In the presented methodologies the incorporation of mechanisms for fault tolerance and a special focus on robustness to cope with faults as well as parameter variations is mostly lacking. GALS in general has issues with interfacing multiple uncorrelated clock domains (synchronizer problem), furthermore, the lacking global time severely complicates the design process (which is also the case for purely asynchronous approaches). The interconnected rings and oscillators as well as the distributed clock generator approach are not able to cope with failures. To be able to tolerate arbitrary failures in a clock synchronization process theory shows that almost fully connected networks are needed [23] which is clearly not fulfilled by these two approaches. Therefore, a transient fault might lead to major clock deviation, over-clocking phenomena or could even stop the whole clock generation process. Table 1.1 summarizes the characteristics of the discussed design methodologies.

In the face of the challenges introduced at the beginning of this section and trends in semiconductor technology which lead to more powerful but also potentially less robust designs, the work described in this thesis focuses on the development of a robust clocking scheme for future dependable systems. Therefore an approach is employed which provides local synchrony similar to GALS. Compared to GALS the distinctive feature given by the enhancement that a globally distributed fault-tolerant time base (with slightly relaxed synchrony assumptions) is maintained also. The ongoing miniaturization and the speed-up of digital circuits in conjunction with accompanied adverse effects of technology scaling, suggest to incorporate mechanisms for fault tolerance to attain reliable systems. Especially in — but not limited to — safety- and mission-critical environments like in the automotive and aerospace domain robustness against faults is of utmost importance.

|                                | variation<br>robustness | fault<br>tolerance | design/area<br>overhead                            | established<br>design method |

|--------------------------------|-------------------------|--------------------|----------------------------------------------------|------------------------------|

| purely synchronous             | no                      | no                 | none                                               | yes                          |

| GALS                           | partially               | no                 | small<br>(synchronizer)                            | somewhat                     |

| interconnected rings           | partially               | no                 | small<br>(inverter chains)                         | no                           |

| distributed clock<br>generator | partially               | partially          | small<br>(DCG units)                               | no                           |

| purely asynchronous            | yes                     | no                 | large<br>(multi-rail coding and<br>REQ/ACK scheme) | somewhat                     |

#### Table 1.1: Comparison of design methodologies

#### 1.4 FAULT TOLERANCE

Technological advancements, especially in the domain of computer design, introduce increasingly complex systems into everyday life. Cell phones, personal computers, cars, airplanes, (nuclear) power plants or even microwave ovens, for instance, are equipped with at least one, but more often a set of interacting electronic processing unit(s) executing comprehensive program code. As systems get more and more complex, the chance of failure of a single component — affecting the proper operation of the whole system — increases steadily. A failing cell phone would at least be annoying but usually not dramatic. In contrast, if the brakes of a car or the controls of an airplane fail due to a glitch in the control system lives are at stake. Therefore, fault tolerance is an important design aspect, at least in modern safety-critical systems. Further, it has to be noted that in the face of increasing failure rates of modern VLSI technology even non-critical, e.g., multimedia devices, will soon be augmented by fault tolerance mechanisms to allow for proper operation with reasonable failure rates [15, 77].

In the previous paragraph two important terms, *failure* and *fault* have been used without clear distinction. To treat these important items in more detail a short definition for fault, *error* and failure will be given below. The definitions (following [3]) will be used throughout the rest of this thesis.

**Definitions of failures, errors, faults:** If a system fails, its output behavior deviates from the specified characteristics—a *failure* can be observed at the interface. The cause of a failure can usually be traced back to an erroneous state within the system itself which led to the incorrect output. An *error* can therefore be defined as an unintended/corrupted internal state of the considered system. The cause for an error

is called *fault* which may indirectly lead to a failure if it is not masked in some way. The origin of faults can be manifold ranging from physical effects, e.g., broken wires, EMI, etc., over handling faults to design faults.

Many different definitions for fault tolerance and fault-tolerant computing can be found in literature, but the essential part is similar for most of them [3,50,78]. A system can be considered fault tolerant if it continues proper operation even after a fault has occurred the fault does not lead to a failure. In other words, a fault that would affect the system's interface behavior is handled before it can propagate to the output.

Fault tolerance usually relies on error detection and some form of redundancy to cope with the erroneous data — via replicated components and/or repeated computation. An example for an approach using hardware replication is given by the widely used Triple Modular Redundancy (TMR) scheme. In TMR processing units are triplicated and the outputs are compared via a special voter circuit which is able to mask the failure of one component if both other replicas operate properly. Time diversity is also a method for achieving fault tolerance, e.g., repeated processing of data on the same hardware can mask short noise effects (at the price of decreased overall throughput) as long as no permanent faults are present. An important point regarding fault tolerance which has been neglected so far is concerned with the fault hypothesis. The fault hypothesis specifies assumptions about number and types of faults that a fault-tolerant system must be able to tolerate [50]. These assumptions have major impact on the fault tolerance concept of the system. Therefore, the fault hypothesis has to be thoroughly defined during the design phase, because faults not covered by the assumptions, but which may occur in real world scenarios, may bring the whole system fail.

Assumptions on the nature and type of failing components in the context of VLSI hardware design are usually classified using several different types of fault models.

#### 1.4.1 FAULT MODELS IN VLSI DESIGN

Fault models typically applied in VLSI consider faults on the abstraction level of single gates or transistors. Where a set of interconnected gates forms a circuit. If a gate or interconnect stops to work in its intended way a fault has occurred. It has to be noted that in the context of this fault classification only static fault scenarios are considered, i.e., once a component is affected by a fault, it will stay faulty. The most commonly treated faults are introduced below.

stuck-at fault There are two types of stuck-at faults, the stuck-at-0/LO and stuck-at-1/HI. A stuck-at-X fault occurring at time  $t_F$  at signal S manifests itself in a way that S takes on logic level X at time  $t_F$  and is no longer able to change its value after  $t_F$ . Note that, if for example signal S is currently LO and a stuck-at-HI occurs, the fault will generate one last erroneous transition to HI and remain there.

- stuck-open fault A stuck-open fault appearing at  $t_F$  disconnects the affected signal S from its driving buffer which leads to an undefined voltage level, the signal is "floating". This floating state may lead to inconsistent perception of the logic level when read by multiple inputs.

- **delay fault** A *delay fault* increases or decreases the time a signal change needs to propagate through the respective signal or gate. The altered timing behavior of the affected component may lead to the violation of timing constraints in subsequent circuits.

- **bit-flip fault** A *bit-flip fault* changes the logic level of a component to the opposite value. This type of fault is usually treated with state-holding devices only, i.e., sequential logic. A bit-flip fault occurring at time  $t_F$  at a single bit storage component C manifests itself in a way that component C takes on the inverted state of C prior time  $t_F$ .

#### 1.5 DISTRIBUTED SYSTEMS AND ALGORITHMS

Distributed systems are typically defined as a set of autonomous computer/computing systems — often called nodes — that communicate and cooperate in some way with each other [2, 85]. This definition includes wide-area networks (e.g., the internet), local-area networks, multiprocessor computers as well as single VLSI chips. In general, this wide range of very different distributed systems can be subdivided and classified by the node's grade of coupling. For instance, a multiprocessor system is coupled much tighter than the internet. Another classification usually considers the purpose for building a system in a distributed way. Here the reasons are manifold, spanning from simple resource sharing over aiming at increased performance to the improvement of system reliability. As already sketched at the beginning of this chapter, as well as in Section 1.4 on fault tolerance, the *improvement of system reliability* is the main driving force for considerations within this thesis.

If a stand-alone component fails, the whole computing task is affected. By replication of computing nodes the overall reliability of a distributed system can be increased compared to a stand-alone component. This enhanced resilience against failures is usually provided by replicas performing the same tasks as the failed component augmented by some kind of voting mechanism(s) to mask faulty outputs, hence compensating for failed nodes. In contrast to the straight forward way of a single (stand-alone) component which performs a computation task, this distributed processing of and voting on data has to be enabled by incorporating elaborate algorithms coordinating all actions.

Algorithms operating in a distributed system have to cope with at least three main difficulties if compared to traditional centralized algorithms. In centralized systems algorithms usually have access to the *global state* of the system. This cannot be assumed for distributed algorithms, which only have direct access to their own local state. Even though state information can be exchanged between nodes, the state of other units may have already changed and therefore be invalid when the information arrives. The second issue with distributed algorithms is related to *synchronization* or *global time*. Temporal ordering of computations is provided naturally in a centralized system by their sequential execution of tasks. In contrast, total ordering of events in distributed systems is sometimes not possible, e.g., it cannot be determined which of two events occurred first, given timing uncertainties incorporated with sending and receiving of data in a distributed system [51]. Another difficulty when dealing with distributed systems is given by *non-determinism* of executions (e.g., due to failures). A centralized processing node's operation sequence and global state can usually be determined exactly. In contrast, a node of a distributed system may process the same set of input data in a different way, for example by starting at a different time depending on the current state of all other nodes.

#### 1.5.1 Modeling distributed systems

When taking a closer look at the modeling of distributed systems, different computation models can be identified. The main distinctive features are specified by the way nodes communicate with each other and whether or not and what kind of timing assumptions (e.g., synchronous, partially synchronous, asynchronous, etc.) are considered. Another dimension for distinction is given by the considered failures modes. However, the distributed system models presented in the following paragraphs are at first introduced for systems free of faults. Nevertheless, these models can be augmented for the faulty case by adapting them for certain failure models.

A widely-used system model operates on *message-passing* [2]. In message-passing systems, n nodes  $p_0, \ldots, p_{n-1}$  communicate with each other by sending messages over communication channels. Typically a communication channel is modeled as bidirectional link between two nodes and the specific interconnections of nodes define the topology of the system. An algorithm in a message-passing system is specified by its program code executed on the system's set of n nodes, whereas each node can be modeled as state machine with a set of states  $Q_i$ . A node may perform actions like receiving from and sending messages to neighboring nodes as well as executing local computations. Each node contains as many input and output buffers as it has incoming connections from and outgoing links to other nodes, respectively. The outgoing buffers store messages already sent by the node that have not yet been delivered to the receiving node, similarly input buffers hold messages until they are processed. Transitioning from one state of a node to the next involves the processing of all messages stored in the input buffers, performing computation events, updating the local state and sending at most one message to neighboring nodes (by placing the message(s) into the respective output buffers). The behavior of a message-passing system over time is modeled as an execution, with an execution defined as an alternating sequence of events (computation and sending) and configurations, where configurations Care given by the states of the nodes  $C = (q_0, q_1, \ldots, q_{n-1})$  with  $q_i$  being the state of  $p_i$ . What is usually demanded from a correct distributed algorithm is that some conditions are valid for its execution. The *safety condition* has to hold for any reachable sequence

of configurations and events, and states that "nothing bad ever happens". Additionally, a *liveness condition* has to hold at least several times and can be translated to, "eventually something good happens". To illustrate these two conditions consider a street crossing with two traffic lights as an example. A safety condition has to ensure that both traffic lights will **never** show green at the same time, while a possible liveness condition states that the a traffic light eventually changes from red to green. So far no assumptions on the timing of messages have been made. However, as initially stated, asynchronous, synchronous and some systems between can be distinguished. Asynchronous message-passing systems can be characterized by the fact that there is no fixed upper bound on message delivery and computation time. Therefore, algorithms designed for this kind of model have to operate without knowledge of such bounds. In contrast to the asynchronous model, a synchronous system works in a lock-step manner, that is, executions are partitioned into rounds. Relying on this round scheme, depicted in Figure 1.7, where every node can send one message to each neighbor and may perform a computing step on received messages, gives a convenient model with only little uncertainty. A problem that in the context of an asynchronous model is initially quite intricate may be substantially simplified by mapping it to synchronous lock-step rounds. However, from this the challenge of establishing this synchronous round scheme emerges. Unfortunately, for most distributed systems in practice a truly synchronous system cannot be achieved. On the other hand some distributed computing problems might not be solvable in a purely asynchronous framework, e.g., distributed consensus in the presence of faults [30].

Figure 1.7: Execution of a synchronous message-passing algorithm

Shared memory [2] based distributed systems rely on communication via a set of shared variables. Various types of variables can usually be distinguished, where a characterization can be given by the values returned from and the operations allowed on these variables. Typically applied types of shared variables allow operations like read and write, however, several more complex functions can be employed. Similarly to the message-passing, systems of n nodes  $p_0, \ldots, p_{n-1}$  are treated as state machines with executions represented by alternating sequence of configurations and events. Input and output buffers are not needed

for shared memory systems, however, m registers  $R_0, \ldots, R_{m-1}$  representing shared variables are employed. Typical operations on registers are for instance reading a value v from register R, returning v and leaving R unchanged, or writing a new value v to R, whereas this operation does not return a value. In contrast to the message-passing approach, the configuration C in a shared memory system is defined by  $C = (q_0, \ldots, q_{n-1}, r_0, \ldots, r_{m-1})$  with  $q_i$  again denoting node i's state and  $r_j$  being the value of register j. The events within an execution are computations which follow a specific scheme starting with node  $p_i$  issuing an operation on a variable determined by  $p_i$ 's actual state  $q_i$ . Afterwards,  $p_i$ 's state changes according to  $p_i$ 's current state and the return value of the shared memory access. Analogous to the message-passing approach, executions of a correct algorithm have to fulfill safety and liveness conditions.

### 1.5.2 DISTRIBUTED SYSTEMS FAILURE MODELS

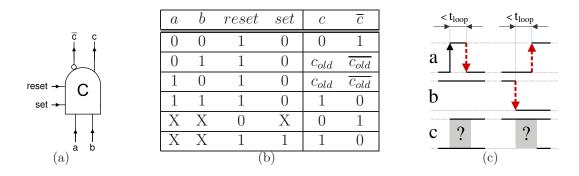

To augment the modeling techniques presented above by the notion and effects of faulty behavior various established component failure models may be applied. The most commonly used component failure models for distributed systems research are introduced below.