Thesis for the Degree of Master

# Interface Characterization Methods and Properties of GaN Metal-Insulator-Semiconductor Structures

**Clemens** Ostermaier

Department of Electronics, Major in Semiconductor and Display Engineering The Graduate School

December 2007

The Graduate School Kyungpook National University

## Interface Characterization Methods and Properties of GaN Metal-Insulator-Semiconductor Structures

**Clemens** Ostermaier

Department of Electronics, Major in Semiconductor and Display Engineering The Graduate School

Supervised by Professor Jung-Hee Lee

Approved as a qualified thesis of Clemens Ostermaier for the degree of Master by the Evaluation Committee

December 2007

Sugho Hal Prof. Sung-Ho Hahm Chairman Prof. Jung-Hee Lee Prof. Jong-Ho Lee

The Graduate School Council, Kyungpook National University

## Acknowledgement

It has been an overwhelming experience to work in this research laboratory within Korea, far away from any situation I had faced before. Therefore I would like to thanks my advisor Professor Jung-Hee Lee for giving me that opportunity, integrating me into the group, supporting me throughout the research but also giving me the freedom to explore my own ideas.

To my committee members, Professor Sung-Ho Hahm and Professor Jong-Ho Lee. I am grateful for the discussions we had during the one and a half year on my research. You gave me a lot of ideas and comments on my work and inspired me for several parts of it. Further, I am thankful for the sound background I could gain from your classes.

To my colleagues, 김기원, 이우영, 윤상원, 현선영, 이화철, 양충모, 이동식, 조현익, 나경일, and 하종봉. I am grateful for the time we spend together and the things you have taught me inside and outside the laboratory. Since we spend most time together you have been a big part of my work, my life and my cultural experience. Special thanks to 홍진 for his generous help and support for using his furnace and wire bonding machine and also to 상일 for his assistance in writing the Korean abstract and his daily support and company in the cleanroom.

To Hamid and Max. I am grateful for your support throughout the time here in physical and mathematical problems as well as cosmopolitan discussions. I wish we all can save our memories and find each other back again later on talking about the fun we had and the challenges we faced.

To my Korean and international family and friends here, back home and far away. I was always pleased about your company and sharing our life experiences has been an important part of my stress relaxation.

To Mama, Papa and Lukas. Your love and support throughout the years made me to what I am and encouraged me to explore further from wherever I have been and will be. I can never really repay for all that you have done to me.

To Felicity-Young Kyung. Thanks for your love and courage that brought me into all this and showed me a new spot that I have never even imagined before:

#### Korea, with all its characteristic and cultural facets

## Abstract

This work presents a detailed study on the characterization methods of the interface properties of GaN-insulator structures for several dielectric materials. It is an pre-study for the purpose of fabricating inversion metal insulating semiconductor field-effective transistors (MISFETs) based on GaN, which are believe to have higher breakdown and current capability than those of other materials, due to the wide band gap related properties of GaN.

The focus is divided into a theoretical discussion about the characterization methods, the fabrication, the measurement and the analysis of MIS structures based on the interface properties and the field-effective mobility measured by Hall measurement and extract from Schottky transistors. As characterization methods, capacitive measurement with over band gap UV light has been used to study the interface charge induced flatband voltage shift and was compared to conductive AC measurement for extraction of the interface state density. The investigation of p-type and n-type substrates allowed a characterization over the whole band gap. Due to the lack of inversion ability in the samples the field effective mobility was extracted from accumulation in enhancement device structures.

As dielectric materials silicon nitride and silicon oxide deposited by plasma-enhanced chemical vapor deposition (PECVD) where compared to aluminum oxide from atomic layer deposition (ALD) under certain annealing conditions. Amorphous aluminum oxide has several advantages as a high dielectric constant, a high energy barrier and a high breakdown field, but shows a lower thermal stability only up to around 800°C.

The capacitive analysis was based on virtual-ground MIS devices in order to remove any distortion effects by not perfectly rectified ohmic contacts, which was necessary on p-type

iv

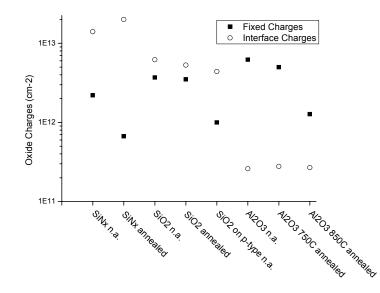

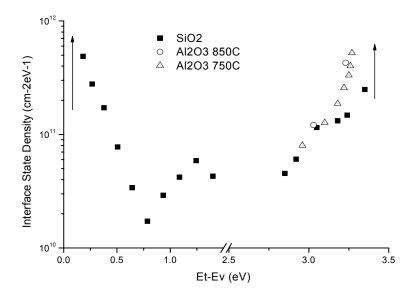

GaN. It resulted into symmetric interface state distribution over the band gap with a maximum at the band edges. Aluminum oxide showed the best performance with an interface state density below  $2x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> in the middle of the band gap and below  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> at the band edge after thermal treatment in nitrogen ambient. Silicon oxide interfaces showed similar behavior but less effect on annealing.

For p-type substrates high interface density were observed depending on the epitaxially grown substrate. The interface characteristics were generally less dependent on the dielectric or surface treatment due to the defects from the grown bulk material which could be shown by comparison to photoluminescence measurement. Inversion carriers were not observed using Schottky barrier MISFET devices. Further, capacitive study on p-type GaN, which is up to now rarely presented, is discussed with focus on the high series resistance due to the low mobility of holes in GaN. An accurate result was measured using silicon oxide with a minimum interface state density of  $4x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> around the band edge.

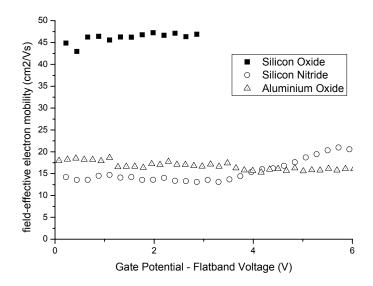

The Gated Hall mobility was extracted from the carriers in accumulation and separated from the bulk carriers. The Hall measurement resulted in a field-effective mobility of 150  $cm^2/Vs$  for silicon nitride in a bulk material with mobility around 300  $cm^2/Vs$ . Similar configuration was measured for transistors with Gate lengths of 4 to 30 µm. The channel length dependent resistance was extracted and led to a maximum field-effective conductivity mobility for silicon oxide of 50  $cm^2/Vs$ , while silicon nitride and aluminum oxide showed mobilities around 15  $cm^2/Vs$ .

## GaN Metal-Insulator-Semiconductor 구조의 계면 특성화 방법과 특성

## 클레멘스 오스테르마이아 Clemens Ostermaier

## 경북대학교 대학완 전자공학과 반도체 및 디스플레이 공학 (지도교수 이정희)

(초록)

본 논문에서는 GaN 절연체 구조의 계면특성 분석을 위한 특성화 방법에 대하여 세부적인 연구를 보여준다. 이 연구는 GaN을 기반으로 한 Inversion MISHFET (metal insulating semiconductor field effective transistors)를 만들기 위한 예습이라고 할 수 있다. GaN를 기반으로 한 물질의 특성은 다른 물질들 보다 넓은 에너지 갭을 가지기 때문에 높은 항복 전압과 전류용량을 가질 것으로 기대된다. 중요내용으로는 특성화 방법에 관한 이론적인 논의, 제작, 계면특성을 기반으로 한 MIS 구조의 측정 및 분석 그리고 홀 측정법으로 구한 Fieldeffective conductivity로 구성이 되어 있고, Schottky transistors를 이용하여 측정하였다. UV light에 대한 band gap의 용량성 측정 특성화 방법을 위해 flatband voltage shift로부터 야기된 계면 전하와 계면 전하 밀도의 추출을 위해 비교된 전도성 AC 측정에 대하여 연구를 하였다. 측정은 공핍 소자에서 반전의 결핍으로 인하여 항상되었다. 절연물질로서 PECVD (plasma-enhanced chemical vapor deposition)으로 길러진 Silicon nitride와 Silicon oxide는 일정한 조건에서 ALD (atomic layer deposition)로 길러진 Aluminum oxide와 비교 되었다. Aluminum

vi

oxide는 높은 절연상수 같은 많은 장점을 가지고 있지만 800℃에서는 낮은 열적 안정도를 보여주었다. 전기적 용량의 분석을 위하여 가상 접지 MIS 소자를 사용하여 완전하게 정류된 저항성 접촉에 의한 왜곡 영향을 제거 하였다. 결과적으로 밴드 가장자리에서 밴드 갭에 대하여 대칭적인 계면 상태 분포를 보여주었다. Aluminum oxide는 밴드 갭 중앙에서 2x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> 이하의 최대 계면상태밀도를 보여주고, 질소 분위기에서 열처리 후에는 밴드 가장자리 부근에서10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> 의 결과를 보여주었다. Silicon oxide 계면은 비슷한 결과를 보여주지만 열처리 효과가 적은 것으로 보여졌다. 또한 p형 물질에서 계면 밀도는 에피택셜 물질에 따라 변화하는 것이 관측되었다. 보통 계면 특성은 bulk 물질의 결함에 의해 발생하기 때문에 절연물질이나 표면 처리에 의존한다. Schottky barrier 소자에 의하여 테스트 된 반전 전하들은 관측 되지 않았다. 지금까지 소개된 p형 GaN 용량성에 관한 연구는 낮은 홀의 이동도 때문에 나타나는 직렬 저항 문제에 관하여 보여주고 있다. Silicon oxide를 사용함으로서 2x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>의 최소 계면 상태 밀도의 정확한 결과가 측정 되었다. 마지막으로 field-effective conductivity와 Gated Hall mobility에 대한 결과를 요약하면, 홀 측정은 150 Vs/cm<sup>2</sup> 의 Field-effective conductivity의 결과를 보여주었고, Bulk 물질에서는 약 300 Vs/cm<sup>2</sup> 의 이동도를 보여주었다. 그리고 4~30um의 Gate길이를 가지는 transistors 에서도 비슷한 형태가 측정되었다. Silicon nitride와 Aluminum oxide가 약 15 Vs/cm<sup>2</sup> 의 이동도를 가질 때 채널 길이의 변화에 따른 저항을 구할 수 있었고, 50 Vs/cm<sup>2</sup> 의 Silicon oxide에 대한 최대의 field-effective conductivity를 이끌어 내었다.

## Contents

| Ackn  | owledgement                                   | 111 |

|-------|-----------------------------------------------|-----|

| Abst  | ract                                          | IV  |

| 초록    |                                               | VI  |

| LIST  | OF FIGURES                                    | Х   |

| LIST  | OF TABLES                                     | XIV |

| 1.    | INTRODUCTION                                  | 1   |

| 1.1.  | GaN & Modern Semiconductor Devices            | 1   |

| 1.2.  | History of Inversion MOSFETs in GaN           | 3   |

| 1.3.  | Thesis Outline                                | 4   |

| 2.    | TECHNICAL BACKGROUND                          | 6   |

| 2.1.  | GaN Properties                                | 6   |

| 2.1.  | 1. Crystal Structure                          | 6   |

| 2.1.2 | 2. Band Structures                            | 8   |

| 2.1.3 | 3. Piezoelectric and Spontaneous Polarization | 9   |

| 2.1.4 | 4. Typical Compounds of GaN                   | 11  |

| 2.2.  | Gate Dielectrics on GaN                       | 13  |

| 2.3.  | The basic MIS Structure                       | 16  |

| 2.3.  | 1. 2-Terminal Behavior of Gallium Nitride     | 16  |

| 2.3.2 | 2. Interface Properties                       | 24  |

| 3.    | CHARACTERIZATION TECHNIQUES                   | 26  |

| 3.1.  | CV Measurement in GaN                         | 26  |

| 3.1.  | 1. Capacitive Method                          | 26  |

| 3.1.2 | 2. Conductive Method                          | 29  |

| 3.1.3 | 3. Dynamic Behavior of Interface States       | 32  |

| 3.2.  | Hall and Gated-Hall Measurement                   | 35  |

|-------|---------------------------------------------------|-----|

| 3.3.  | Characterization by Schottky Barrier Transistor   | 40  |

| 4. F  | ABRICATION                                        | 44  |

| 4.1.  | Technology                                        | 44  |

| 4.1.1 | Metal-Organic CVD                                 | 44  |

| 4.1.2 | Dielectric Deposition                             | 46  |

| 4.2.  | Device Processing                                 | 52  |

| 4.2.1 | MIS Capacitor                                     | 52  |

| 4.2.2 | Gated Hall Pattern                                | 56  |

| 4.2.3 | Schottky Barrier Transistor                       | 59  |

| 5. E  | EXPERIMENTAL RESULTS                              | 61  |

| 5.1.  | Characteristic of CV measurement                  | 61  |

| 5.2.  | Dielectric Characterizations                      | 68  |

| 5.2.1 | Silicon Nitride (Si <sub>3</sub> N <sub>4</sub> ) | 71  |

| 5.2.2 | Silicon Oxide (SiO <sub>2</sub> )                 | 75  |

| 5.2.3 | Aluminum Oxide (Al <sub>2</sub> O <sub>3</sub> )  | 82  |

| 5.3.  | Mobility Characterization from Gated Hall         | 86  |

| 5.4.  | Characterization by 3-Terminal Gated Device       | 90  |

| 6. 5  | SUMMARY & CONCLUSION                              | 94  |

| LITEF | ATURE                                             | 99  |

| SCIE  | NTIFIC ARTICLES FROM THIS WORK                    | 106 |

| APPE  | NDIX A: TYPICAL PARAMETERS OF GAN                 | 107 |

| APPE  | NDIX B: MATHCAD CODE FOR CV CALCULATION           | 110 |

| APPE  | NDIX C: NUMERICAL CV SOLUTION                     | 111 |

## List of Figures

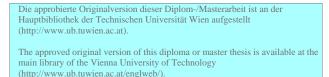

| Figure 1.1: Application field of materials based on frequency and power performance 3                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

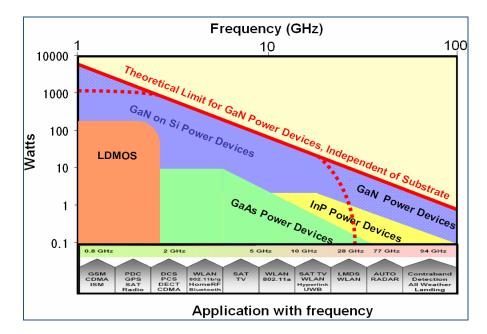

| Figure 2.1: Crystal structure of wurtzite structure, typically used in GaN. Right side shows the N-polar phase which is exactly turn around of the Ga-polar phase on the left7                         |

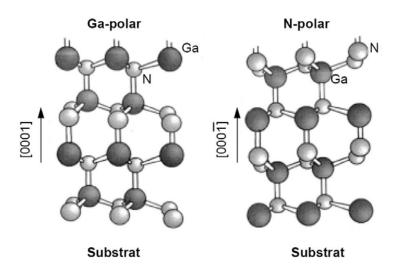

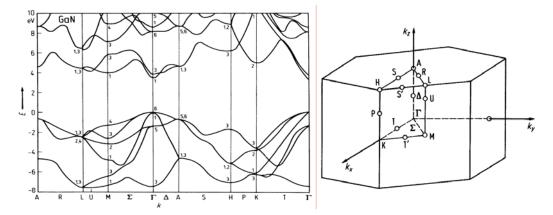

| Figure 2.2: Band energy of conduction bands and valence bands in GaN based on theoretical calculation [22] (left). The right side shows the crystal directions based on the unit lattice cell. 9       |

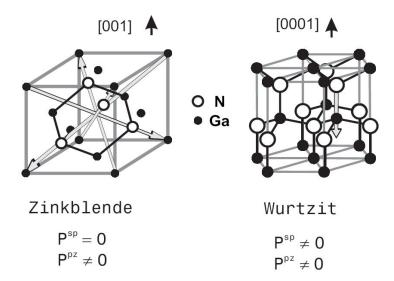

| Figure 2.3: Unit cell structure of zincblende (left) and wurtzite crystal (right). The polarization can be understood by adding up the vectors from N atoms to GaN atoms (white arrows)                |

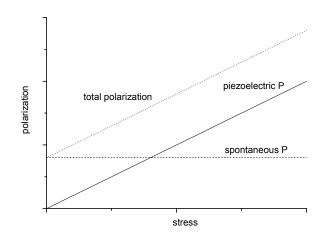

| Figure 2.4: Qualitative graph of the polarization based on the stress in the lattice perpendicular to the [1000] direction. The stress can be introduced by interfaces with III-N alloys               |

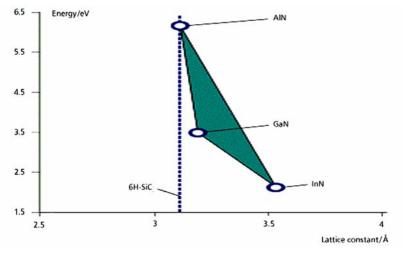

| Figure 2.5: Band gap energy versus lattice constant for the basic nitride materials (dots).<br>Along the outside line of the triangle the band gap energy for possible compounds can<br>be seen        |

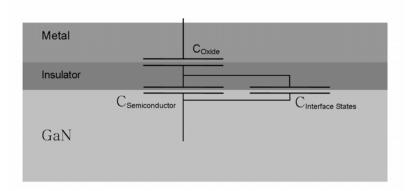

| Figure 2.6: MIS structure and basic equivalent circuit of capacitors. For the ideal case the interface state capacitor is zero and only the semiconductor and oxide capacitor remain.                  |

| Figure 2.7: Qualitative band diagram of the MIS structure for accumulation and depletion19                                                                                                             |

| Figure 2.8: Total calculated amount of semiconductor charges versus the surface potential of the semiconductor                                                                                         |

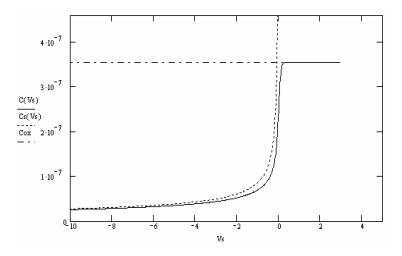

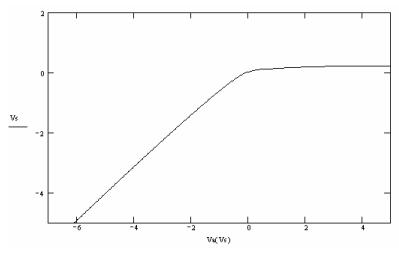

| Figure 2.9: Calculation result of the total Capacitor of the MOS structure (solid line),<br>semiconductor capacitor (dashed line) and the constant oxide capacitor                                     |

| Figure 2.10: Calculation of the relation between surface potential and the Gate potential. In the depletion region both change linear. From the flatband voltage the surface potential does not change |

| Figure 2.11: Calculation of the MOS capacitor (deep depletion) versus applied Gate voltage (solid). Again semiconductor capacitor (dashed) and oxide capacitor are additionally shown                  |

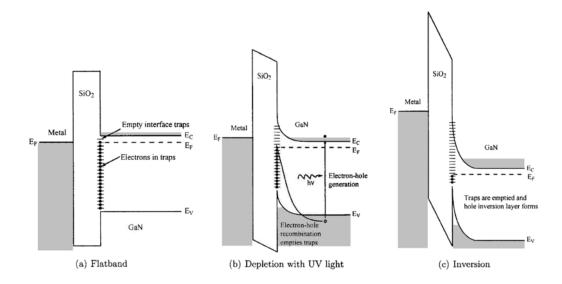

| Figure 3.1: Energy diagram of the MOS structure at flatband condition (a), depletion                                                                                                                   |

| condition with incident UV light (b) and inversion (c)                                                                                                                                                                                                                                                                                      | 28 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

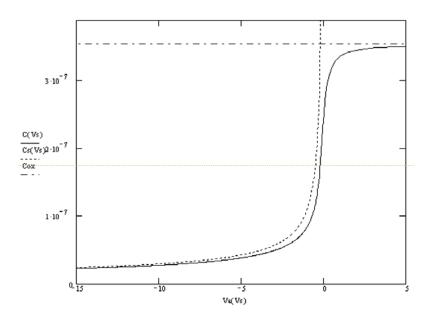

| Figure 3.2: Calculated CV Graph showing the Flatband shift induced by oxide constant charges on n-type GaN (right) and p-type GaN (left)                                                                                                                                                                                                    | 29 |

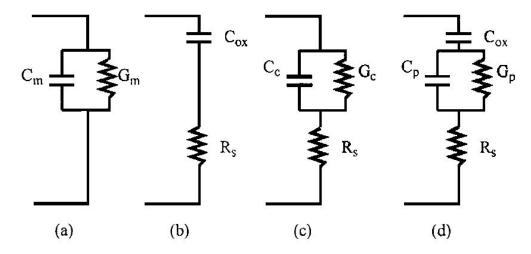

| Figure 3.3: Equivalent circuit models used for conduction measurement analysis:<br>measurement circuit (a), circuit in accumulation, where the semiconductor capacitance<br>does not play a role (b), simple MOS circuit of extracting the corrected MOS<br>capacitance values Gc and Cc (c) and total equivalent circuit given explicit Gp |    |

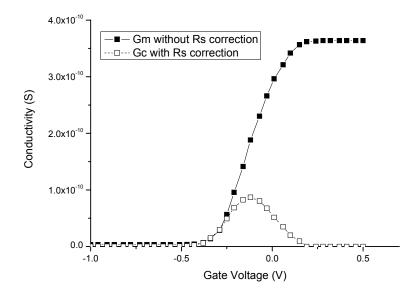

| Figure 3.4: Comparison between the conductivity of the MOS interface before and after series resistance correction.                                                                                                                                                                                                                         | 32 |

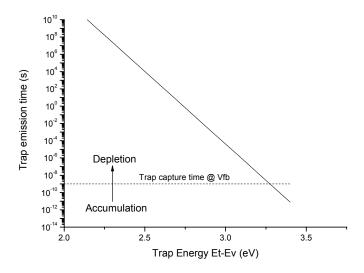

| Figure 3.5: Calculation of the trap emission time versus Trap Energy relative to the band gap (solid line). As a reference the capture time for flatband condition is drawn (dashed line).                                                                                                                                                  | 33 |

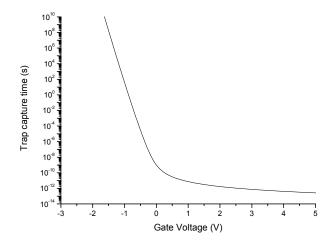

| Figure 3.6: Calculation of the Trap capture time in dependence of the Gate voltage, the surface potential and the surface carrier concentration, respectively. The flatband voltage is at zero Gate voltage assuming ideal case.                                                                                                            | 35 |

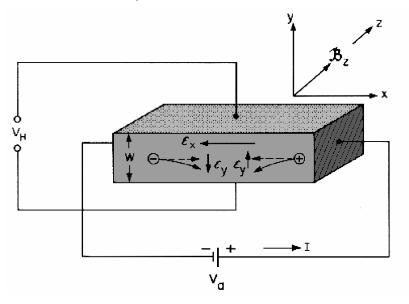

| Figure 3.7: Model of Hall measurement: electric field in x-direction, magnetic field in z-<br>direction, Hall voltage in y-direction.                                                                                                                                                                                                       | 36 |

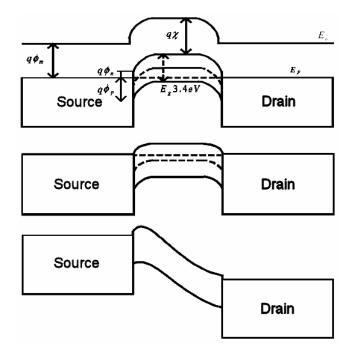

| Figure 3.8: Schematic Band diagram of Schottky barrier transistor from Source to Drain for thermal equilibrium (upper), barrier lowering by Gate voltage (middle) and forward current by $V_{DS} > 0$ and turned no channel                                                                                                                 |    |

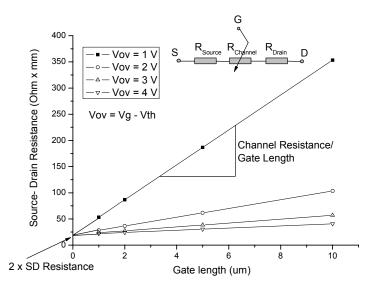

| Figure 3.9: Modeling of the channel resistance from Schottky barrier transistor by comparing the total Source – Channel – Drain resistance for different Gate lengths                                                                                                                                                                       | 42 |

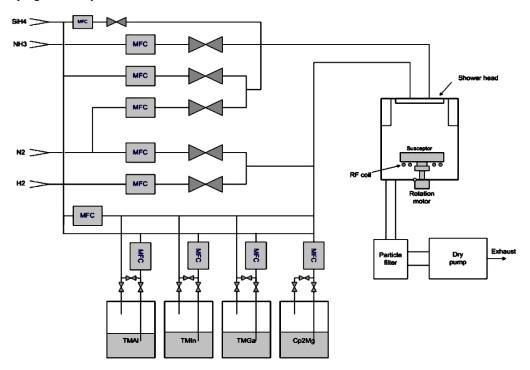

| Figure 4.1: Schematic of the MOCVD reactor and its components.                                                                                                                                                                                                                                                                              | 45 |

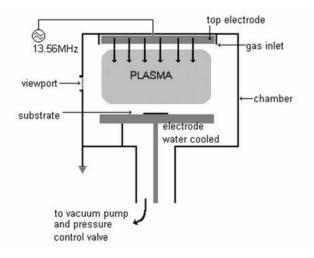

| Figure 4.2: Schematic view of a planar PECVD reactor                                                                                                                                                                                                                                                                                        | 47 |

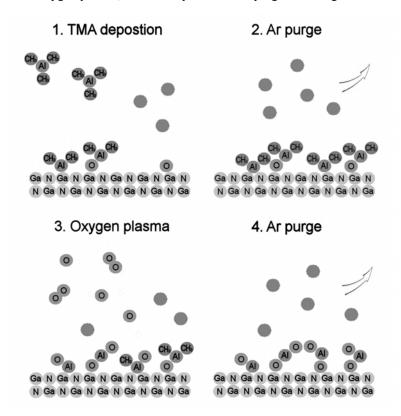

| Figure 4.3: Schematic view of the chemical reaction in the four cycle atomic layer deposition process for aluminum oxide                                                                                                                                                                                                                    | 49 |

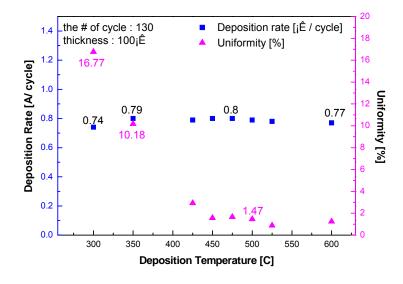

| Figure 4.4: Deposition rate and uniformity of the ALD in dependence of the deposition temperature.                                                                                                                                                                                                                                          | 50 |

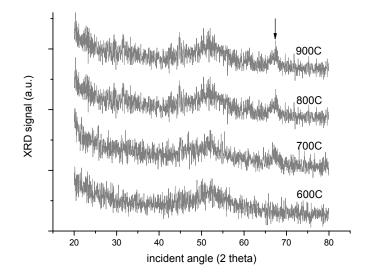

| Figure 4.5: XRD results of 28 nm aluminum oxide films after annealing in oxygen for 60s at several temperatures                                                                                                                                                                                                                             |    |

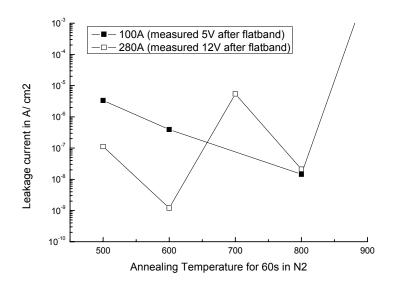

| Figure 4.6: Leakage current measured for 10 nm and 28 nm aluminum oxide films. The measured current values were taken from the same potential difference starting from the flatband voltage in order to neglect differences in the interface                                                                                                |    |

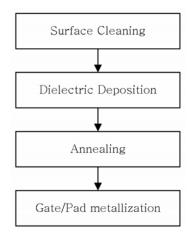

| Figure 4.7: Schematic process flow for MIS capacitors                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

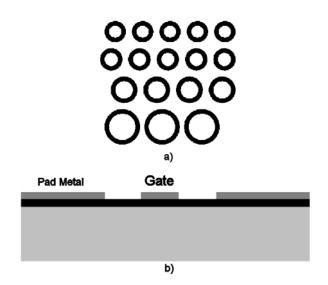

| Figure 4.8: Mask used for the fabrication of MIS capacitors (a). The bottom figure (b) shows a schematic view of the cross section of the capacitors with the dielectric (black) on the GaN substrate and the single metal layer on the top for both electrodes.                                                         |

|                                                                                                                                                                                                                                                                                                                          |

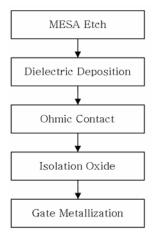

| Figure 4.9: Schematic process flow of the Hall pattern                                                                                                                                                                                                                                                                   |

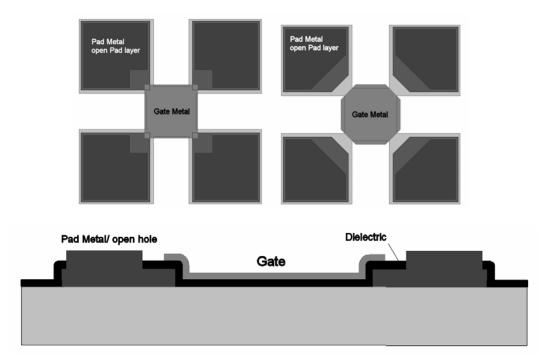

| Figure 4.10: Schematic Mask design for the Gated Schottky Hall pattern (top right) and the Gated Hall pattern (top left). The bottom figure shows the cross section of the Gated Schottky Hall pattern with overlapping pad and Gate metallization. The normal Gated Hall pattern is same except no overlap is necessary |

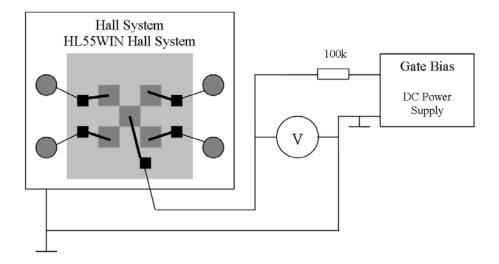

| Figure 4.11: Measurement circuit for Gated Hall measurement. The sample was bonded and connected to the Hall system, with external Gate bias control                                                                                                                                                                     |

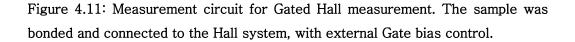

| Figure 4.12: Mask design (top) and cross section (bottom) of the Schottky Transistor 60                                                                                                                                                                                                                                  |

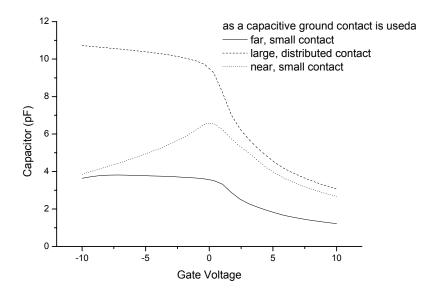

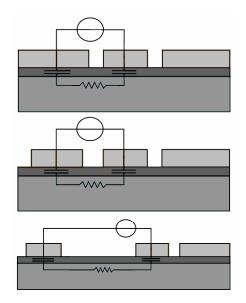

| Figure 5.1: Measurement of the same capacitor with different common ground contact configurations according to figure 5.2                                                                                                                                                                                                |

| Figure 5.2: Schematic cross-section for standard common ground contact (upper), reduced size common ground contact (middle) and far reduce size contact (lower)                                                                                                                                                          |

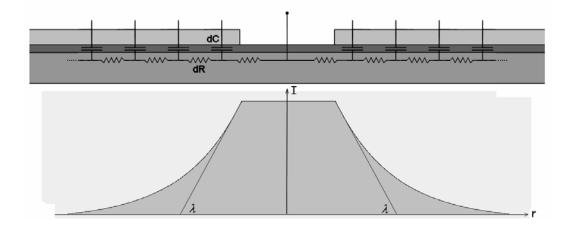

| Figure 5.3: Schematic description of the current distribution in radial direction in an infinite structure under consideration of the series resistance and the MIS capacitor                                                                                                                                            |

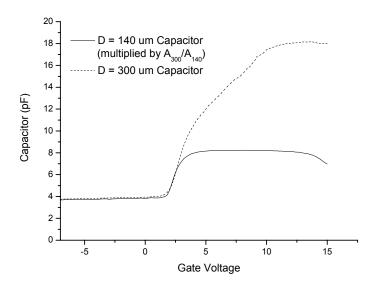

| Figure 5.4: Comparison between the same capacitor measured at large and small capacitor pattern. The value of the small pattern is multiplied by the aerial ratio between the two capacitors for normalization. 67                                                                                                       |

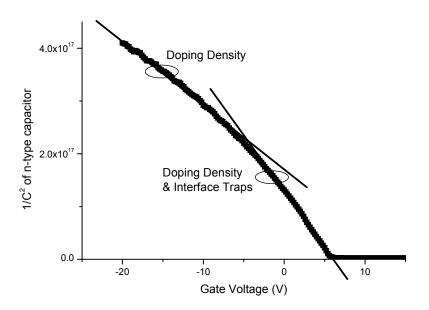

| Figure 5.5: $1/C^2$ extraction on deep depletion CV measurement on n-type for SiO <sub>2</sub>                                                                                                                                                                                                                           |

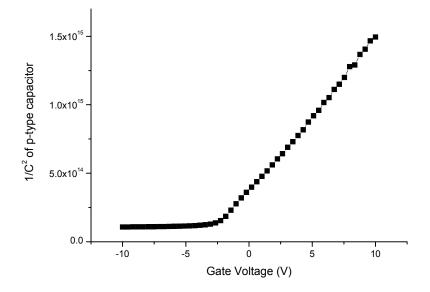

| Figure 5.6: $1/C^2$ extraction of deep depletion CV measurement on p-type GaN for SiO <sub>2</sub> 70                                                                                                                                                                                                                    |

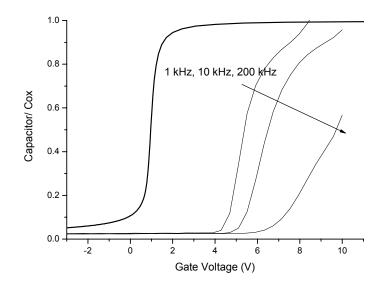

| Figure 5.7: CV graph of non-annealed Si <sub>3</sub> N <sub>4</sub> showing high flatband voltage dependence on frequency. Ideal graph is shown for comparison. The oxide capacitor of the 24 nm dielectric film was 180 pF                                                                                              |

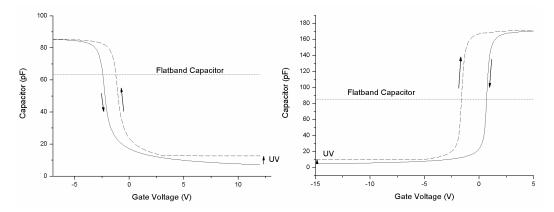

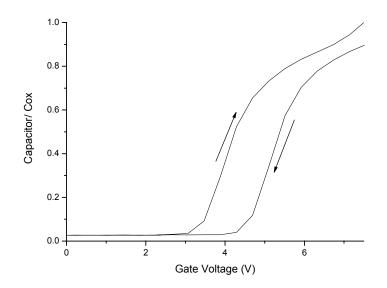

| Figure 5.8: Hysteresis effect on $Si_3N_4$ capacitor measured at 1 kHz and indicating a very high interface density close to the conduction band. The oxide capacitor was 180 pF.73                                                                                                                                      |

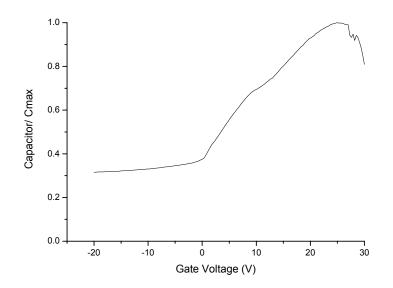

| Figure 5.9: CV graph of annealed $Si_3N_4$ measured at 1 MHz without UV light. The graph shows dispersion and is therefore normalized to its maximum value. ( $C_{ox} = 61.1 \text{ pF}/72 \text{ nm } Si^3N^4$ )                                                                                                        |

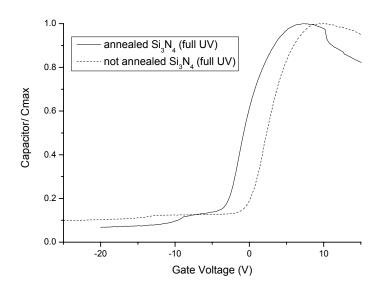

| Figure 5.10: Comparison between n-type CV graphs with annealed and non-annealed Si <sub>3</sub> N <sub>4</sub> measured during UV illumination. The threshold shift shows a lower fixed charge density for the annealed dielectric. Both oxide capacitors are 61.1 pF74                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

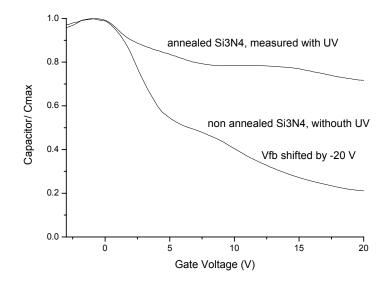

| <ul> <li>Figure 5.11: Comparison of p-type CV graphs with Si<sub>3</sub>N<sub>4</sub>. Upper Graph shows annealed sample measured with UV light illumination at 1 MHz (C<sub>ox</sub>=61.1 pF) while lower graph (shifted by -20V) shows the non-annealed sample measured without light at 1 kHz (180 pF).</li> <li>75</li> </ul> |

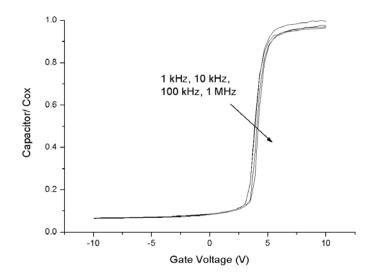

| Figure 5.12: CV of 40 nm non-annealed $SiO_2$ on n-type GaN over frequency. $C_{ox} = 70$ pF.                                                                                                                                                                                                                                     |

| Figure 5.13: CV graph of 40 nm $SiO_2$ on n-type GaN with and without UV light, measured at 1 MHz. ( $C_{ox} = 70 \text{ pF}$ )                                                                                                                                                                                                   |

| Figure 5.14: CV graph of annealed SiO <sub>2</sub> (72 nm) with and without UV light. Capacitor shows large dispersion at 1 MHz                                                                                                                                                                                                   |

| Figure 5.15: Interface state density extracted from p-type sample for the lower half and from n-type sample for the upper half of the band gap                                                                                                                                                                                    |

| Figure 5.16: Photoluminescence Measurement of Mg doped p-type GaN. The energy is plotted reversely from the conduction band to match it with the valence band. The PL peak from the valence band electrons is drawn light grey, that it can be differed from bulk traps by the viewer's inspection                                |

| Figure 5.17: CV graph, measured at 1 MHz of p-type $SiO_2$ capacitor, with and without UV light. Graph is normalized by its maximum, due to dispersion at high frequency. $C_{max}$ = 14 pF/ $SiO_2$ 40nm80                                                                                                                       |

| Figure 5.18: Frequency dispersion in p-type GaN with 40 nm SiO <sub>2</sub> ( $C_{ox}$ = 70 pF)81                                                                                                                                                                                                                                 |

| Figure 5.19: Inversion behavior at white light exposure in p-type GaN with 72 nm SiO <sub>2</sub> after annealing. Measurement was done at 1 MHz                                                                                                                                                                                  |

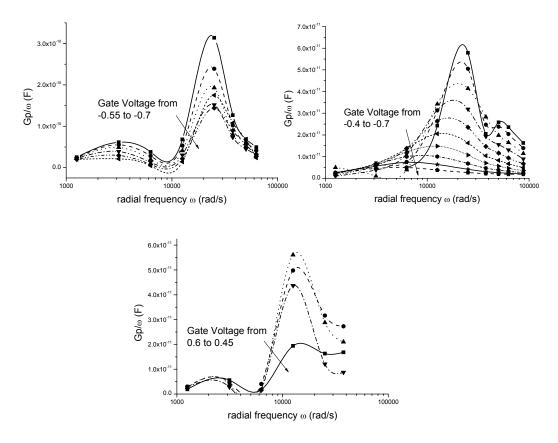

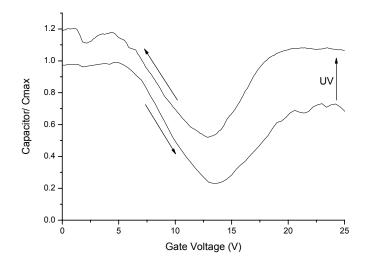

| Figure 5.20: CV graphs for Al <sub>2</sub> O <sub>3</sub> MOS capacitors for non-annealed (upper, left), 750°C (upper, right) and 850°C (lower) annealed samples                                                                                                                                                                  |

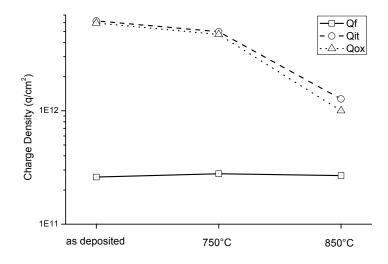

| Figure 5.21: Summary of oxide charges, fixed charges and interface charges for different annealing conditions of Al <sub>2</sub> O <sub>3</sub>                                                                                                                                                                                   |

| Figure 5.22: Extracted and normalized parallel conductivity for the non-annealed sample (upper, left), the 750°C annealed sample (upper, right) and the 850°C annealed sample (lower)                                                                                                                                             |

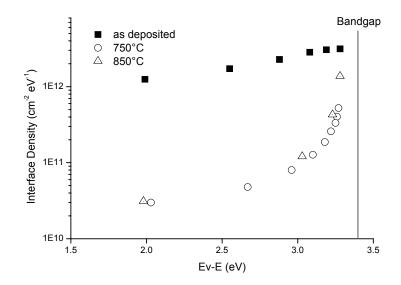

| Figure 5.23: Summary of interface state density plotted over the band energy relative to the valence band                                                                                                                                                                                                                         |

| Table 1.1: Comparison of electrical properties of semiconductor materials                                                                                                                       |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Table 2.1: Spontaneous polarization for AlN, GaN and InN in [0001] direction of the te structure given in standard unit and number of charges per cm <sup>2</sup> for comparison rface charges. | son to su |

| Table 2.2: Summary of dielectirc materials used on GaN.                                                                                                                                         | 14        |

| Table 5.1: Summary of succussful fabriacted MOSFET devices                                                                                                                                      |           |

## 1. Introduction

This first chapter provides a low level technical background focusing on the reason of GaN as a material for transistors in general and on inversion metal insulting semiconductor field-effective transistors (MOSFETs) in particular. A brief review about the history of GaN MOSFETs is also presented summarizing the results up to today and gives reasons for this work. A detailed introduction over this work is given at the end of this chapter.

## 1.1. GaN & Modern Semiconductor Devices

The recent progress in GaN devices [1, 2] is driven by its superior material parameters as wide band gap (3.44 eV), high critical electric field (3 MV/cm), similar thermal conductivity as silicon and high mobility in polarization charge induced two dimensional electron gas (2DEG) due to its polar nature. All those parameters and the fact that prior growth difficulties could be solved, lead to dominance in high power and high voltage operation devices. A comparison of the main material parameters to other materials used for power devices is shown in table 1.1.

Prior to its success in transistors, light emitting diodes (LEDs) where developed emitting blue light according to its high band gap energy. In the standard lattice structure, wurtzite, GaN, AlN and InN form a continuous alloy system whose direct band gaps range from 1.9 eV for InN, to 3.4 eV for GaN and up to 6.2 eV for AlN. Thus the III-nitride family potentially could cover the whole spectra from red to deep ultraviolet. Indeed, this is what recent reports show, even though the crystal quality, which is crucial for effective devices, is still the major problems for those materials [3].

Also, GaN power transistors gain several benefits due to the large band gap. The intrinsic carrier concentration is around 10<sup>-10</sup> cm<sup>-3</sup> at room temperature, which allows much higher operation temperatures, until the extrinsic carriers dominate. Indeed device performances at temperatures higher than 1000°C were shown recently at the IWN 2006 [4], which did not result to any degradation in device operation. In achieving the same depletion width in a junction, GaN can be doped higher according to the wide band gap, which improves the on-state resistance of power

device and the on-state power loss. Additional, for the same depletion width GaN shows a better breakdown voltage [5, 6] as it has a ten times higher breakdown field than silicon and 5 times higher than GaAs.

|                       | Si                       | GaAs                     | 4H-SiC                   | GaN                                 |

|-----------------------|--------------------------|--------------------------|--------------------------|-------------------------------------|

| e saturation velocity | 1×10 <sup>7</sup> cm/sec | 1×10 <sup>7</sup> cm/sec | 2×10 <sup>7</sup> cm/sec | ~ 3×10 <sup>7</sup> cm/sec          |

| Breakdown field       | 0.3 MV/cm                | 0.6 MV/cm                | 2 MV/cm                  | 3.3 MV/cm                           |

| 2DEG density          | -                        | ~ 10 <sup>12</sup> /cm2  | -                        | ~ 10 <sup>13</sup> /cm <sup>2</sup> |

| Bandgap               | 1.1 eV                   | 1.4 eV                   | 3.3 eV                   | 3.4 eV                              |

| Electron Mobility     | 1400 cm <sup>2</sup> /Vs | 8500 cm <sup>2</sup> /Vs | 800 cm <sup>2</sup> /Vs  | 900(H) cm <sup>2</sup> /Vs          |

| Thermal conductivity  | 1.5 W/mK                 | 0.5 W/mK                 | 4.9 W/mK                 | 1.3 W/mK                            |

| ε <sub>r</sub>        | 11.8                     | 12.8                     | 10                       | 9                                   |

#### Table 1.1: Comparison of electrical properties of semiconductor materials

Even though GaAs provides a four times higher mobility in 2DEG as GaN it can not be used for high power device due to its low breakdown field. Therefore GaN shows the combination of all benefits making it the leading material in this field. This can also be seen in figure 1.1, describing that the limits for GaN devices cover the whole spectra of LDMOS devices and GaAs power transistors [7, 8]. Indeed, Cree [9] and Nixtronex [10] recently presented their first power transistors products on GaN based on high electron mobility transistors (HEMTs) for output power up to 100 W and frequency range up to 10 GHz. Further high frequency device operation with an output power of 35 dBm at 110 GHz have been shown [11] for RF power MMIC applications.

In summary, GaN provides the highest power device capability based on today's fabrication possibilities. There are still materials as diamond or AlN [12] which provides higher band gaps, but the limits of these materials are simply the difficulties in growth which have to be solved prior to device fabrication.

Figure 1.1: Application field of materials based on frequency and power performance

## 1.2. History of Inversion MOSFETs in GaN

Depletion MOSFETs in GaN have been investigated since Ambacher et al. described the effect of two dimensional carrier gas [13, 14]. However, for real device applications, those transistors suffer from two major issues. First, depletion transistors are normally-on, which is often not accepted for many applications (i.e. in automobiles) regarding safety reasons and second, those devices show always a certain leakage through the buffer in turn-off state and the sub-threshold slope gets horizontal. Therefore the on-state current can achieve high current values but in total the devices often show a low on-off current ratio, which increases the off-state power consumption.

In contrast, inversion MOSFETs include a reverse pn junction in turn-off mode but do suffer from less forward current in turn-on state, since the carrier concentration is less and the mobility is around one order lower than in the 2DEG. First attempts for this were done by Irokawa et al. [15] who showed a non-self aligned device structure with MgO dielectric. Similar to all devices up to today, they used Si for n+ doped Source and Drain regions into Mg doped p-type GaN. Even though, MgO was described to have a good interface quality, the device showed very low

inversion current. At a Gate length of 22  $\mu$ m the maximum Gate current at 12 V Gate voltage was 20  $\mu$ A/mm. The threshold voltage was around 6 V. The output characteristic showed only linear behavior up to 5 V. The extracted electron mobility was extremely low, which is not sufficient for reasonable current capability.

One year later Matocha et al. [16] presented a self aligned structure on n-type GaN with silicon oxide as Gate electric. The Gate structure was fabricated by poly silicon. The device showed a maximum Drain current at 34 V of about 12 mA/mm for a 8  $\mu$ m Gate length and a 3 orders lower off current. The field-effective electron mobility was extracted from the linear region to be 45 cm<sup>2</sup>/Vs. Further tests on the breakdown voltages showed that a maximum breakdown voltages could be achieved at a Gate Drain spacing of 9  $\mu$ m without field plate.

The same group presented on year later by Huang et al. [17] a similar device on p-type substrate. The Drain current was increased up to 15 mA/mm with a lower turn off current. The sub threshold slope was extracted to be 490mV/decade. The field effective mobility was increased to 167 cm<sup>2</sup>/Vs, while the Hall mobility showed 200 cm<sup>2</sup>/Vs. The small difference was explained to be due to the interface charges, which was proved to be low by CV method.

Another very unconventional idea was pulished by Jang et al. in 2006, trying to make a Source Drain doping by Si diffusion [18]. Using a temperature of 1000°C for long time annealing cycles a reasonable doping could be achieved. However the magnesium oxide interface resulted in lower Drain currents around 22  $\mu$ A/mm.

Very recently Otake et al. [19] presented a vertical trench structure for GaN MOSFETs with silicon oxide and nitride as Gate dielectric deposited by sputtering. The results were however a bit lower then from Huang et al. and showed a field effective mobility of 133 cm<sup>2</sup>/Vs.

All these results show a promising outlook for GaN MOSFETs, since the mobility is comparable to other materials and only a factor two lower than Si. However in comparison to high electron mobilities in two dimensional electron confinements it is still a factor ten below.

## 1.3. Thesis Outline

As this topic is quite new and only a few groups reported on it, compared to the total research in GaN devices, this thesis focuses not just on the experimental work but also on the theory of the applied methods. Several reports have been presented which did not show an accurate analysis. Therefore I am focusing on the background of the interface characterization.

In the second chapter, a general overview of GaN is given with a review on dielectrics studies. The last part of the chapter provides the basic theoretical background on capacitive measurement and the non-ideal behavior. Since this part is already well known from silicon, I built up on this general knowledge and added the specific characteristics of GaN or wide band gap materials in general.

The third chapter explains the method of capacitive and conductive interface analysis and shows a discussion on the accuracy and errors that can occur. This knowledge is a key issue of this work and most of the actual time was spend in finding the right measurement and analysis condition. Also a short explanation on the Hall mobility and the Schottky Transistor is given to show the basic model that was used in the extraction.

A summary on the whole fabrication processes is given in chapter four with a short introduction into the MOCVD growth and the dielectric deposition. Later one focuses on PECVD, which was used for silicon nitride and oxide, and on atomic layer deposition (ALD), which was used for aluminum oxide. Some process details are also given for each of the used devices, as capacitor, Gated Hall pattern and Schottky barrier transistor.

Chapter five shows the results of several experiments and discusses typical measurement issues of the capacitive methods. The first part focuses on the series resistance problem which occurs mainly in p-type GaN and its effect on the virtual ground contact used in the capacitors. The occurring effects are discussed and some solutions are presented. In a second part, the characteristic given by the measurements methods discussed in chapter 3 are shown for silicon nitride, silicon oxide and aluminum oxide. Finally the results of Hall measurements in n-type and p-type GaN and the transistor characteristics are presented.

## 2. Technical Background

This chapter presents all the general descriptions necessary to understand later characterization methods or fabrication processes. Starting with the bottom of the MIS structure, the first sub chapter summarizes the most important properties of GaN or related materials from the III-nitride family. Even though, this work implies only non-heterostructures, I use them to explain the effect of polarization charges, which have also relevance in bulk materials. The second part covers a summary of important dielectrics, which are applied on GaN in this work. Finally, I show the simple theoretical calculation used to describe a two terminal behavior as it appears generally for wide band semiconductors. This should help to understand the detailed characteristics of capacitive or conductive studies described in chapter 3. A summary of the most important material parameter is further shown in appendix A.

## 2.1. GaN Properties

In order to understand the origin for the benefits of GaN, listed in chapter 1.1, the crystal structure and the band structure will be discussed in the following part. Based on this, the spontaneous and piezoelectric polarization can be discussed. Also related to this is the importance of other nitride materials, which will be mentioned at the end of this part

#### 2.1.1. Crystal Structure

GaN as well as other group-III nitrides can crystalline into wurtzite, zincblende and rocksalt structure. Last one is probably least common since it requires very high pressures. The zincblende structure for GaN and InN can be grown by epitaxy of thin films on cubic substrates and shows lower effective mass and less dangling bonds on the surface. However, under ambient conditions, the thermo dynamical stable structure is wurtzite for bulk GaN, AlN or InN. Therefore the most common used crystal structure in devices is wurtzite which has a hexagonal unit cell and thus two lattice constants, c and a. It consists of two interpenetrating hexagonal

closed packed (HCP) sublattices.

The origin for many properties of the III-nitride family lies in the extreme high thermal and chemical stability. This originates from the mixed binding mechanism with covalent and ionic components, due to the difference in electro negativity between the group-III and group-V elements. Therefore these semiconductor materials show a high binding energy per atom (GaN 9.8 eV/atom, AlN 11.5 eV/atom, InN 7.7 eV/atom).

Figure 2.1: Crystal structure of wurtzite structure, typically used in GaN. Right side shows the N-polar phase which is exactly turn around of the Ga-polar phase on the left.

For the wurtzite structure, it is differed between the Ga phase and the N phase. Even though the structures are the same, the order in which the crystal appears is opposite, as can be seen in figure 2.1. The GaN phase is defined as [0001] direction while the N phase is refers as [000/1]. Usually templates grown by MOCVD lead to a Ga-polar substrate, even though N. Fichtenbaum [20] reported very recently an N-polar MOCVD growth by using different orientations of sapphire substrates. In MBE growth both polar structures can be grown, depending on the nucleation layer and the applied MBE (Plasma or NH<sub>3</sub>). Differences between the two polarities occur also in physical and chemical surface properties. The Ga-polar phase shows usually more smooth surface morphology and is therefore more resistant against wet etching or oxidation. It should be noted, that the orientation of an epitaxial GaN layer does not depend on the

termination of the surface. A Ga phase or a N phase can be terminated by either a N layer or a Ga layer, without any change of its phase. Only by flipping around the wafer, the polarity can be changed.

Even though, epitaxial growth is limited by those two polarities for stable wurtzite structure, it was shown that non-polar devices can be fabricated using GaN wafers out of bulk crystal material [19, 21]. The differences for GaN MIS structures using different substrate orientations will be discussed further at the spontaneous polarization effects.

### 2.1.2. Band Structures

The calculated band structure for the wurtzite phase of GaN is shown in figure 2.2 (left) [22]. In figure 2.2 (right) the crystal orientations are shown for the high symmetrical points of the hexagonal structure. It can be seen that the band gap, resulting from the lowest and highest energy point of the conduction and valence band, respectively, is in the  $\Gamma$ -point, which is the center of hexagonal structure. GaN is, like all other materials of the group III-nitride family, a direct semiconductor and therefore high efficient in transforming electrical energy into optical energy.

Under consideration of the spin-orbit splitting energy and the crystal field splitting energy, the valence band splits into two bands for light holes and heavy holes. The crystal field splitting energy, which occurs only in the wurtzite phase, also depends on the strain of the lattice.

An important issue in GaN is the very low mobility of holes based on a high effective mass. Typical values are found by  $mh/m_0 = 0.8$  [23], even though the results differ quite [24, 25]. It was generally observed that the band gap energy is indirect proportional to the effective carrier mass [26], which also leads to increased masses in other high energy gap materials as GaAs or InP. Additionally, wide band semiconductors show a higher intra band scattering, which further reduces the mobility of holes.

The fundamental material property of low hole mobility and respectively high resistive p-type GaN films, is the main reason why GaN devices focus almost exclusively on electron carriers. Therefore bipolar devices as inversion MOSFETs or heterostructure bipolar transistors (HBTs)

are far behind the development in comparison to unipolar devices as HEMTs.

Figure 2.2: Band energy of conduction bands and valence bands in GaN based on theoretical calculation [22] (left). The right side shows the crystal directions based on the unit lattice cell.

### 2.1.3. Piezoelectric and Spontaneous Polarization

The high number of polarization charges is probably the most important factor of GaN based devices. It causes extremely high carrier concentration called two-dimensional electron gas (2DEG) or its opposite two-dimensional hole gas (2DHG) at the interface to other materials. The polarization charges depend on two independent components; the material dependent spontaneous polarization and the stress dependent piezoelectric polarization.

The spontaneous polarization depends directly on the hexagonal structure on the wurtzite phase. It is called spontaneous, since no external field or force is required. From figure 2.1 can be seen, that Ga layers are followed by N layers or vice versa, depending on the polarity. In order to get the total polarization from the Ga - N binding (with ionic component), the single dipoles in [0001] should be add up. While this leads to a constructive addition in the wurtzite structure, the total sum of polarization charges is zero in the zincblende structure, as can be found from figure 2.3. The diagonal directions are faced in all eight directions and cancel each other.

Figure 2.3: Unit cell structure of zincblende (left) and wurtzite crystal (right). The polarization can be understood by adding up the vectors from N atoms to GaN atoms (white arrows).

It should be noted, that inside the crystal the spontaneous polarization is zero (or only appears as a higher order multi pole with neglectable influence) due to the ongoing sequence of atomic layers. Spontaneous charges occur therefore at terminating surfaces, as material interfaces of air interfaces. In terms of material interfaces the net charges depends on the difference between the spontaneous polarization fields the two materials. Theoretical values have been calculated by Bernardini et al. [27] and are listed in table 2.1. The table inlcudes the values for charges per square meter and values normalized for the elementary charge. It appears quite clear that those values are very large, if they represent the carriers in a 2DEG or the surface charge to a dielectric interface. Later one is the reason why several groups try to use non-polar materials [21, 28].

|                   | AlN      | GaN      | InN      |

|-------------------|----------|----------|----------|

| $P_{sp} [C/m^2]$  | -0.081   | -0.029   | -0.032   |

| $P_{sp} [q/cm^2]$ | -5.06e13 | -1.81e13 | -2.00e13 |

Table 2.1: Spontaneous polarization for AlN, GaN and InN in [0001] direction of the wurtzite structure given in standard unit and number of charges per  $cm^2$  for comparison to surface charges.

The second component of polarization charges arises from the fact, that hetero interfaces produce

stress (tensile or compressive), which deforms the crystal structure and causes therefore piezoelectric induced charges. The amount of charges is therefore not constant and depends on the polarity and on the stress, which is material and alloy dependent. A qualitative graph summarizes the effect of stress on the piezoelectric charges and the total polarization charges in figure 2.4. The induce stress on a hetero interface is an almost linear function to the mole fraction of the III-N alloys. A simple limit for piezoelectric charges is the difficulty in growing such stress related interfaces. If materials with a higher lattice constant difference are grown in sequence on top of each other, the critical thickness, until the surface of the upper layer cracks, reduces drastically. Therefore the number of polarization charges is limited by the capability of growing such structures. An exact evaluation of the piezoelectric induced charges depends on the stress tensor and the piezoelectric tensor, which is not discussed further here, as piezoelectric charges do not play a role in single GaN layers.

Figure 2.4: Qualitative graph of the polarization based on the stress in the lattice perpendicular to the [1000] direction. The stress can be introduced by interfaces with III–N alloys.

## 2.1.4. Typical Compounds of GaN

The III-nitride family contains the three basic materials GaN, AlN, InN and there alloys. Not only the high band gap differences, mentioned at the band structures, but also the large

conduction band offsets make devices based on electrons very interesting. The most commonly used alloy is probably AlGaN in High Electron Mobility Transistors (HEMT). Since it was found that there is a minimum thickness that the AlGaN layer requires to form a 2DEG channel [29], the aluminum content is quite limited around 30%. Further increase would lead to higher stress and therefore more piezoelectric charges but also enhances the roughness of the interface, which provides another scattering mechanism to the electron channel [30]. Very recently AlN/GaN HEMTs were demonstrated [31, 32] showing a critical thickness around 7 nm and an optimum, regarding the current flow, at 5 nm. Due to the higher carrier concentration, provided by higher spontaneous charges based on higher difference in polarization field and by higher piezoelectric charges due to increased stress according to the lattice constant difference, this device shows the highest current capability of any state-of-the-art GaN device.

Another newly applied alloy is AlInN (also written as InAlN), which can be grown lattice matched on GaN with an In content of about 17% according to figure 2.5 [33, 34]. For this structure the growth does not provide any stress and therefore less difficultness, but also no piezoelectric charges. Later one is compensated by increasing spontaneous polarization, which makes this device another promising candidate for high current devices.

On the issue of MOSFETs, GaN is commonly applied due the vast amount of growing experience and the high band gap, providing higher breakdown voltages. Using AlN as a bulk material would be another great step in terms of higher voltage drivability, but therefore numerous problems for the device fabrication, as doping and ohmic contacts must be solved. Another approach is to use AlN as a dielectric, which it certainly is, due to its wide band gap. In order to apply larger thicknesses it has to be grown at lower temperatures around 500°C to be relaxed, otherwise interface charges would appear, as described above. In our group we could recently show that AlGaN alloys on p-type GaN showed also relaxation effects, if the p-type layer is thick enough. Also AlN directly grown on p-type layer showed an extremely smooth surface, compared to the same thickness on undoped GaN. This approach might be another step to find better interfaces for dielectric materials on GaN.

The third alloy of the III-nitride family, InGaN, shows the smallest band gap and therefore if used in a stack of the same polarity, shows opposite behavior in polarization charges. This was used in an approach to raise the conduction band on the backside of a 2DEG channel for further channel confinement [35]. A second approach was shown, using InGaN on the top of the HEMT structure to raise the conduction band before the 2DEG and change the device to enhancement mode [36].

Figure 2.5: Band gap energy versus lattice constant for the basic nitride materials (dots). Along the outside line of the triangle the band gap energy for possible compounds can be seen.

In summary, designing within the III-nitride family heterostructure can be done by crystal structure, crystal orientation, polarity of orientation and the order and type of materials. Several new ideas are therefore potentially possible by using those materials.

In terms of MOSFET devices, those polarity properties are rather unwanted, as they provide additional surface charges. Even though, they can be taken into account to the fixed charges, it should be noted that the polarization charges have a strong dependence on the temperature and therefore cause shifts in the device parameters.

## 2.2. Gate Dielectrics on GaN

This chapter provides a basic overview over numerous dielectric materials. Several different reports have been shown that it is very difficult to find a good material on GaN. But also the applied measurement methods for characterizing differed a lot in the past, making an accurate comparison difficult. However the dielectric interface seems to be the major reason, why

inversion MOSFETs rarely have been reported, compared to depletion devices. Those need only a Fermi level shift to the mid gap to deplete the conduction band sufficiently. In inversion MOSFETs the Fermi level must sweep through the full gap, which is often prevented by high interface states, which pin the Fermi level and make the minority carrier generation impossible. I will discuss this problem in detail in the experimental chapter of this work.

In table 2.2 the basic parameters, as dielectric constant, the band gap and the conduction band discontinuity  $\Delta Ec$  to GaN, of several dielectrics are listed.

| Material  | Dielectric constant | Eg (eV) | ΔEc to GaN | Reference |

|-----------|---------------------|---------|------------|-----------|

| GaN       | 9.5                 | 3.4     | -          |           |

| $SiO_2$   | 3.9                 | 9       | 2.3        | [37]      |

| $Si_3N_4$ | 7.4                 | 4.5     | Unknown    | [38]      |

| $Al_2O_3$ | 8.6-10              | 9       | 2          | [39-43]   |

| AlN       | 8.5                 | 9       | 1.7        | [13]      |

| $Ga_2O_3$ | 10                  | 5.4     | 0.9        | [44]      |

Table 2.2: Summary of dielectirc materials used on GaN.

Silicon Oxide was one of the first reported dielectrics on GaN [45], and many reports followed [46-49], showing different pre-dielectric-deposition surface treatments [50] or different deposition techniques. Those methods as PECVD [51], liquid phase deposition [52] and electron beam deposition [53] show all interface charges in the order of  $10^{11}$  cm<sup>-2</sup> to  $10^{12}$  cm<sup>-2</sup> close to the conduction band edge. In 2006 Huang et al. report PECVD deposited silicon oxide at 300°C showing a very nice result from  $10^{11}$  cm<sup>-2</sup> at the upper band edge to  $10^{10}$  cm<sup>-2</sup> in the midgap [54]. This work includes also a short discussion on the result of p-type GaN MIS capacitors, which were generally less investigated. Huang et al. and Nakano et al. observed both an inversion behavior in p-type GaN without light illumination [55]. A general advantage of SiO<sub>2</sub> is the large conduction band, decreasing tunneling currents through the oxide, but it also has a more than two times lower dielectric constant which causes lower breakdown behavior. From a process technological view point silicon oxide is probably the easiest material and it can be applied in several ways to a fabrication process, which makes it a very useful candidate.

Few works are shown for silicon nitride usually deposited by PECVD [56, 57]. In comparison the results are better than  $SiO_2$  by a factor 10 at the band edge [51]. The result von Nakasaki et al.

was measured by Terman's method [58] and is therefore probably not accurate enough, especially on the band edge. For device surface passivation, most groups use SiNx which is known to reduce the dangling bonds and surface charges, influencing the device [59]. It should be noted that those results are not applicable on inversion MOSFETs since they not only require low fixed charges but also a low interface state density throughout the whole band gap.

A very new approach is aluminum oxide, often deposited by atomic layer deposition (ALD) on GaN, which also this work focuses on.  $Al_2O_3$  depletion devices have been shown with a reasonable performance [60-63], without noticing about the passivation effects on the frequency behavior. A rough estimation of average interface states density for different annealing conditions have been shown by Wu et al [64] for 40 nm thick aluminum oxide, using the total UV shift of the capacitor measured at the inversion capacitor level. The work also showed an improvement of the average interface states for thermal treatment up to 800°C down to 10<sup>11</sup> cm<sup>-2</sup>. While Al<sub>2</sub>O<sub>3</sub> after deposition is in amorphous phase, it change to polycrystalline phase at thermal treatment around 800°C for very thin films, less than around 5 nm, or lower temperature for thicker film. The reason therefore is simply that a long range order can easier be established in a thicker film rather than very thin film [65]. Therefore thin films around 10 nm change their phase easily to polycrystalline at temperatures below 800°C, which increases the leakage current by several orders of magnitude. Further results on this will be shown in the experimental chapter. In conclusion on this, aluminum oxide shows good results and improvement through annealing. The point is just, that too high annealing temperature might not be possible to be applied, as the phase changes and the material looses its properties of a good Gate dielectric.

Gallium oxide has been also reported as dielectric grown by dry thermal oxidation in oxygen ambient [66-69], but does not provide the same benefits as silicon oxide to silicon. A few reports show higher values than usually on  $SiO_2$  by PECVD.

As mentioned in the previous chapter, AlN can be also applied as a dielectric with its large band gap of 6.2 eV. In order to grow a relaxed AlN film on GaN the growth temperature should be much lower around 500°C. However, the results are not better than from silicon oxide as shown from Hashizume et al., who used thick AlN and characterized them by UV light [70].

In summary many reports on several dielectric show the difficulty of finding a good interface on GaN, but also the critical issue of applying an accurate method to analyze them.

## 2.3. The basic MIS Structure

The Metal-Insulator-Semiconductor structure has been the reason for the long time success of the integrated circuit era. Most of its study has been done on silicon as a p-type or n-type semiconductor with a  $SiO_2$  oxide layer and there is probably not much, which needs to be developed in this field. In order to describe the ideal case of the MIS structure in GaN, the basic physics known from silicon can be applied but several behaviors of the total structure change due to the wide band gap.

The following to subchapters will review the physical-mathematical background for this field for the ideal case, where the insulator and its interface to the underlying bulk material is supposed to be free of charges or interface states, and later the qualitative effects for the real case. In chapter 3 I will then describe how the interface quality and the charges in the insulator can be determined.

### 2.3.1. 2-Terminal Behavior of Gallium Nitride

The basic MIS structure consists of a semiconductor bulk material with an insulating material and a metal layer on its top, as shown in figure 2.6. The metal is assumed to have no ohmic resistance so that its thickness is irrelevant for this observation. The insulting material often has a thickness from a few nanometers to hundreds of nanometers, but in any case we want to neglect any vertical current trough this structure. Since the integration density of modern integrated transistors is steadily increasing, this thickness became one of the most crucial factors, as tunnel current increases exponentially and hence makes a low operation current impossible. However, this problem does not yet play a critical role in GaN MOSFETs.

The semiconductor in my model has a sufficient thickness, that any band bending at its surfaces is decayed at least until its bottom end at any bias condition. Also I assume to have no bulk potential. Therefore the bulk semiconductor can be set as a potential reference point somewhere deep inside. For a given surface potential (of the semiconductor) the electric field and the resulting charges in the semiconductor can be calculated using Maxwell equations. On the other side of the dielectric, the Gate voltage can be written as a function of the surface potential and the charges in the semiconductor which again are functions of the surface potential. Therefore the easiest way is to search a parametric function based on the surface potential of the semiconductor. After finding the two equations it can be noticed, that those equations do not have an analytical inverse function. Therefore numerical solutions are necessary to solve the

implicit equation. In appendix B the straight forward parametric solution is presented and appendix B suggests a simple numerical solution for Matlab. The split from the implicit function to two parametric functions can be described as

$$C_{MIS}(V_{Gate}) \longrightarrow C_{MIS}(V_{Surface})$$

$\mapsto V_{Gate}(V_{Surface})$

The MIS capacitor can be divided into a series of the insulating capacitor, with a fixed thickness, and a semiconductor capacitor, with a surface voltage dependent depletion thickness. In order to find the thickness of the depletion width we start describing the changes of charges in the surface region of the semiconductor.

Figure 2.6: MIS structure and basic equivalent circuit of capacitors. For the ideal case the interface state capacitor is zero and only the semiconductor and oxide capacitor remain.

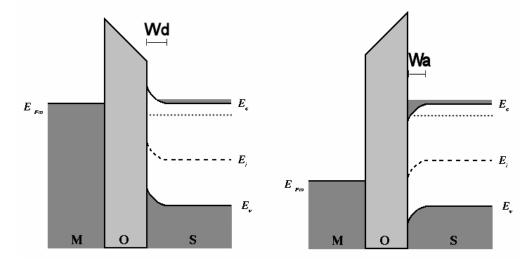

Assuming an n-type GaN material with a doping concentration N, the surface can either be depleted or accumulated. As shown in figure 2.7 a negative voltage causes negative charges at the metal surface and positive charges in the semiconductor. A source of positive charges can either be fixed ionized donors in a depleted surface region or free holes at surface inversion. Later one can only be supplied by external hole sources since the minority carrier response time  $\tau_R$  is vast too long in wide band materials. A brief calculation can prove this when  $\tau_R$  is given by

$$\tau_{R} = \frac{1}{\sqrt{2}} \frac{N}{n_{i}} \tau_{0} = \frac{1}{\sqrt{2}} \frac{10^{17}}{10^{-10}} 10^{-8} \cong 10^{19} \, s \cong 3 \cdot 10^{11} \, years \,, \tag{2.1}$$

where  $n_i$  is the intrinsic carriers density and  $\tau_0$  is the carrier lifetime. Therefore any capacitive measurement in GaN should result into deep depletion graphs without external carrier supply [71,72].

In accumulation the conduction band bends down and electrons can gather in a certain surface region. The relation between electrons and the band potential is given by

$$n(x) = N \cdot e^{\frac{q \varphi(x)}{kT}}, \qquad (2.2)$$

where n is the electron concentration along the x coordinate, which belongs to the depth of the structure and  $\varphi$  is the potential, which is zero at the band edge deep inside the bulk. Assuming that all donor are ionized, Poisson's equation can be written as

$$\frac{\partial^2 \varphi(x)}{\partial x^2} = -\frac{q}{\varepsilon} N \left[ e^{\frac{q\varphi(x)}{kT}} - 1 \right].$$

(2.3)

Unfortunately, this equation can not be solved analytically and an assumption should be made to simplify the problem. Therefore the accumulation width  $W_a$  is defined according to figure 2.7, where the electron concentration is higher than N for  $x < W_a$  and equal to the bulk concentration for all values  $x > W_a$ . This includes an assumption as it is used similarly for the depletion assumption. The Poisson equation can now be noted as

$$\frac{\partial^2 \varphi(x)}{\partial x^2} \cong -\frac{q}{\varepsilon} N e^{\frac{q \varphi(x)}{kT}}$$

(2.4)

including the assumption  $n \gg N$ . Considering that the potential and its first deviation (electric field) is zero at the accumulation width the solution of above equations and the electric field is

$$\varphi(x) = \frac{kT}{q} \ln \left\{ \sec^{2} \left[ \frac{Wa - x}{\sqrt{2}L_{D}} \right] \right\}$$

$$\vec{E}(x) = -\frac{2kT}{q} \frac{1}{\sqrt{2}L_{D}} \tan \left\{ \frac{x - Wa}{\sqrt{2}L_{D}} \right\}$$

(2.5)

Using the solution of the potential in equation 2.2 gives the carrier concentration of the accumulation region. Further more, the integral of the accumulated electrons defined by

$$n_{acc}(x) = N \cdot \left( e^{\frac{q\varphi(x)}{kT}} - 1 \right)$$

(2.6)

shows the total amount of accumulated charges

$$Q_{s,acc} = -\sqrt{2 \cdot \varepsilon \cdot V_T \cdot N \cdot q} \cdot \sqrt{e^{\frac{Vs}{V_T}} - 1}, \qquad (2.7)$$

where

$$V_T = \frac{kT}{q}$$

. (2.8)

This result is the first part used for the theoretical capacitance behavior.  $V_s$  is the surface potential which belongs to the surface carrier n(x) for x = 0 and can be found by equation 2.5-1.

Figure 2.7: Qualitative band diagram of the MIS structure for accumulation and depletion

Looking on the opposite Gate voltage direction, the semiconductor surface will be depleted of electrons. As discussed, no further mobile carriers can reach the surface and the surface depletes deep into the bulk. The description is much easier since only one type of charges is involved and equals a simple diode analysis starting with Poisson's equation

$$\frac{\partial^2 \varphi(x)}{\partial x^2} = -\frac{q}{\varepsilon} N . \qquad (2.9)$$

Similar to previous analysis a certain depletion width can be assumed. From the potential solution the total amount of depletion charges is

$$Q_{s,dep} = \sqrt{2 \cdot \varepsilon \cdot V_s \cdot N \cdot q} \ . \tag{2.10}$$

With this second solution, all charges, occurring in a wide band gap semiconductor are

numerically described. The total semiconductor charges Qs is noted as

$$Q_{S}(V_{S}) = Q_{S,acc} + Q_{S,dep} = \sqrt{2 \cdot \varepsilon \cdot N \cdot q} \cdot \sqrt{V_{T} e^{\frac{V_{S}}{V_{T}}} - V_{T} - V_{S}}$$

(2.11)

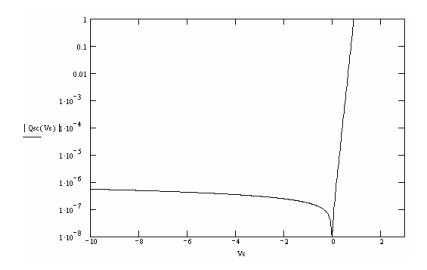

and plotted over the surface potential in figure 2.8.

This pre-result tells how many charges are developed in the semiconductor at a surface potential. From that information the capacitance belonging to those charges is simply given by the derivative after the surface potential

$$C_{S}(V_{S}) = -\frac{dQ_{S}}{dV_{S}} = \frac{\sqrt{2 \cdot \varepsilon \cdot N \cdot q}}{2} \cdot \frac{e^{\frac{V_{S}}{V_{T}}} - 1}{\sqrt{V_{T}e^{\frac{V_{S}}{V_{T}}} - V_{T} - V_{S}}}.$$

(2.12)

Since the oxide capacitor is constant and in series with the semiconductor capacitor (figure 2.6), the total capacitance is described by

$$C(V_{s}) = C_{ox} \parallel C_{s}(V_{s}) = \frac{1}{\frac{1}{C_{ox}} + \frac{1}{C_{s}(V_{s})}}.$$

(2.13)

This result, which is the first function of the parametric function solution, is shown in figure 2.9. It can be seen, that the semiconductor in accumulation reaches a value much higher than the oxide capacitor, which therefore is neglected. On the other side in depletion, the thickness of the ionized donor surface is increasing and dominates the total capacitor.

A final analysis belongs to the second part of the parametric function and develops the relation between the surface potential and the Gate voltage  $V_a(V_s)$ . As mentioned, the potential has a reference point deep in the semiconductor, which requires adding up all potential changes from the bottom to the top of the structure. The first component is the surface potential, which does not need any description, since it is the parameter of the function. Further, the charges in the semiconductor cause an electric field, which must be supplied by the Gate voltage trough the oxide capacitor. When the semiconductor has totally flat bands (no bending in either direction), which requires no fields in the vertical structure, it is called to be in flatband. For the ideal description this case happens under zero applied voltage. In a real device, the difference in workfunctions, fixed and interface charges ( $Q_f$ ,  $Q_{int}$ ) play an additional role [73, 74].

Figure 2.8: Total calculated amount of semiconductor charges versus the surface potential of the semiconductor

Those charges will be discussed further in the next chapter. At this point, it should only be mentioned that interface charges are another function of the surface potential.

$$V_{FB} = \Phi_M - \chi_s - \left[\frac{E_g}{2} - \frac{kT}{q} \ln \frac{N}{n_i}\right] - \frac{Q_F}{C_{ox}} - \frac{Q_{INT}}{C_{ox}}$$

(2.14)

where  $\Phi_M$  is the metal work function,  $\chi_s$  is the electron affinity of the semiconductor,  $E_g$  is the

band gap energy, k is the Boltzmann constant, T is the temperature, q is the elementary charge, N is the doping density,  $n_i$  is the intrinsic carrier concentration,  $Q_F$  is the density of fixed charges,  $Q_{INT}$  the density of interface trap charges and  $C_{ox}$  is the oxide capacitor. Except the interface trap density (equal to interface charges if filled), all other components are constant in respect to the surface potential  $V_s$ . Any charges within the oxide can be contributed in the fixed charge, but do usually not play a dominant role since the fixed charge at the surface are higher and more effective.

Adding up the discussed components for the applied Gate voltage results to

$$V_a(V_s) = V_s - \frac{Q_s}{C_{ox}} + V_{FB}. \qquad (2.15)$$

This function is plotted for zero flatband voltage in figure 2.10. It can be seen that, except in accumulation region, the surface potential and the Gate potential increase proportional.

Since both functions are known, also the capacitance-voltage graph can be plotted, as it appears theoretically in wide band gap semiconductors, shown in figure 2.11. This result can be used as a reference for measurements on CV results.

Figure 2.10: Calculation of the relation between surface potential and the Gate potential. In the depletion region both change linear. From the flatband voltage the surface potential does not change.

Figure 2.11: Calculation of the MOS capacitor (deep depletion) versus applied Gate voltage (solid). Again semiconductor capacitor (dashed) and oxide capacitor are additionally shown.

Finally, I want to show the basic circuit model of the MIS structure based on this charge model. Even though this model is widely known, it is very important to be understood for the conductive measurement analysis which is based on a slightly more extended circuit including the series resistance of the bulk material.

From above analysis it is shown that the total charge in the MIS structure is given by

$$Q = -Q_s - Q_f - Q_{\text{int}}$$

(2.16)

Based on this charge the total capacitor is

$$C(V_a) = \frac{dQ}{dV_a} = \frac{\frac{dQ}{dV_s}}{\frac{dV_a}{dV_s}} = \frac{\frac{d}{dV_s} \left(-Q_s - Q_f - Q_{int}\right)}{\frac{d}{dV_s} \left(V_s - \frac{Q_s}{C_{ox}} - \frac{Q_{int}}{C_{ox}}\right)}.$$

(2.17)

By changing the charges to there equivalent capacitors as

$$C_s = -\frac{dQ_s}{dV_s}$$

and  $C_{\rm int} = -\frac{dQ_{\rm int}}{dV_s}$ , (2.18)

the final capacitance formula is

$$C = \frac{C_s + C_{\text{int}}}{1 + \frac{C_s}{C_{ox}} + \frac{C_{\text{int}}}{C_{ox}}} = \frac{1}{\frac{1}{C_{ox}} + \frac{1}{C_s + C_{\text{int}}}}.$$

(2.19)

Equation 2.19 shows the above described circuit in figure 2.6, for neglected interface charges. In chapter 3 this model will be expanded and conductivities will be added for integrating interface traps. In contrast to the real behavior of interface traps, this shows advantages, since the frequency response of a single trap level can be modeled more accurate by a resistive-capacitive circuit.

### 2.3.2. Interface Properties

In the previous section I already mentioned the flatband voltage shift by the given formula 2.14. Here I will discuss the charges and how they act by simple physical description.

The atoms on the surface of the epitaxial GaN layer can not have the same bonding structure than inner crystal atoms. Therefore bonds of Ga or N atoms are unsaturated and provide different energy states for electrons, which also lie within the band gap. This means that electrons can be placed at energy positions at the surface, where they actually can not exist within the bulk. Therefore those electrons, once trapped in an interface state have a stable position. In an n-type GaN material, electrons can easily fill surface states below the band gap, but those states can not be emptied, since hole carriers, which are necessary for recombination do not exist and the required thermal energy is too high for deep traps. This behavior can be described by the capture and emission time of carriers [75]. The emission time depends on the trap capture cross section  $\sigma$ , the thermal velocity of the carrier, the intrinsic carrier density and the exponential dependence of trap energy  $E_t$  to the mid band gap  $E_i$  (intrinsic energy level).

$$\tau_e = \frac{1}{\sigma_{trap} v_{th} n_i} \cdot e^{-\frac{E_T - E_i}{kT}}$$

(2.20)

In contrast the capture time does not depend on the energy level of the trap, since the electrons fall into the trap from the conduction band.

$$\tau_c = \frac{1}{\sigma_{trap} v_{th} n_s},\tag{2.21}$$

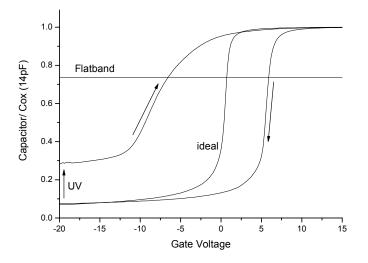

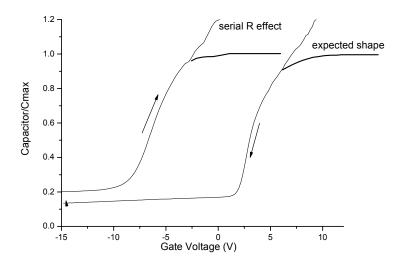

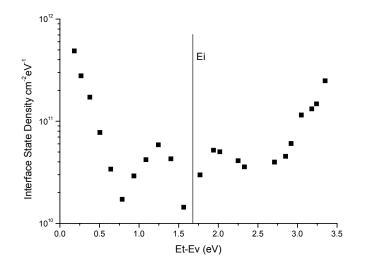

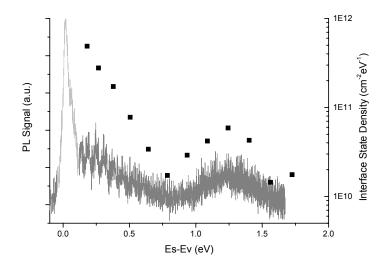

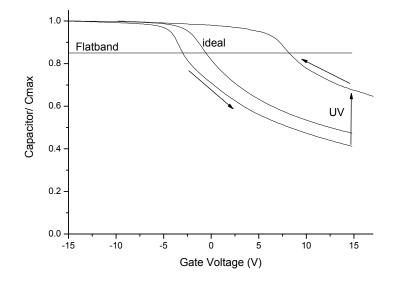

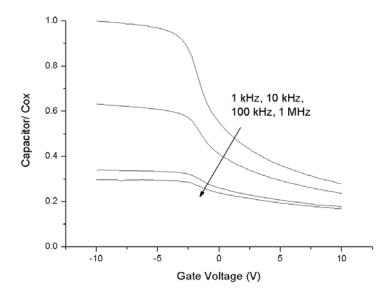

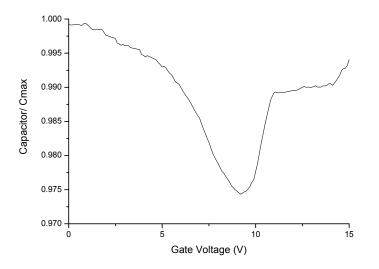

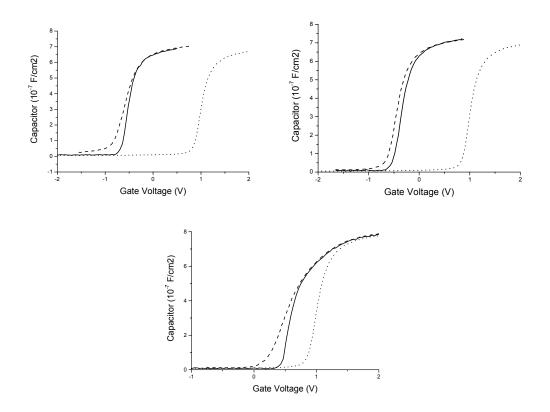

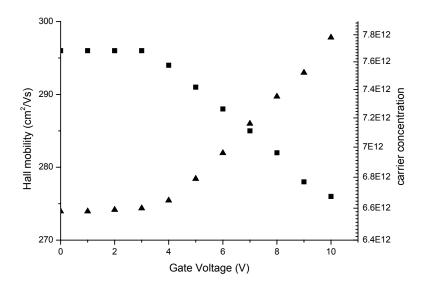

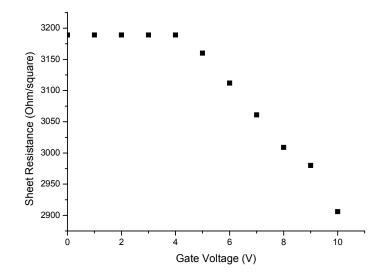

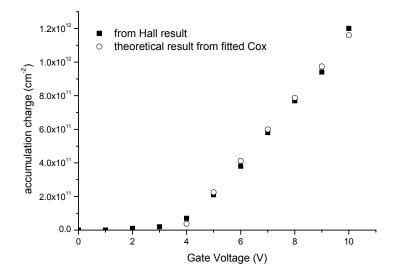

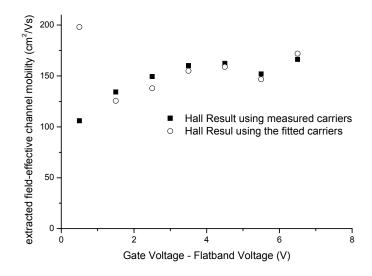

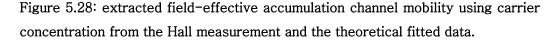

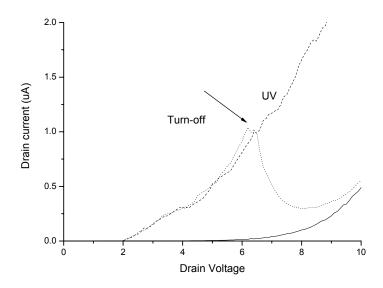

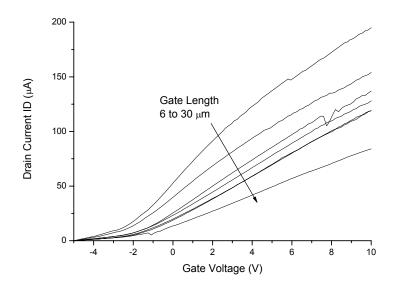

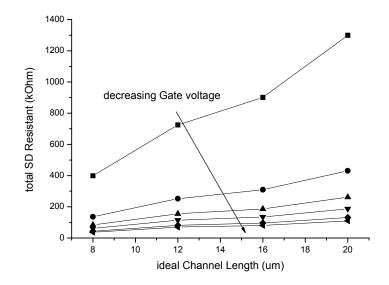

where  $n_s$  is the (volume) carrier concentration at the surface. By describing the number of interface charges, the surface potential first leads to the surface carrier concentration, which than results into a dynamic property of the trap filling mechanism. I will discuss this behavior in detail in section 3.1.3 after the characterization techniques have been described.