Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## MASTERARBEIT

## Dynamic Binary Translation for Automatically Generated Simulators

ausgeführt am Institut für Computersprachen der Technischen Universität Wien

unter der Anleitung von Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

durch

DAVID RIGLER Defreggerstrasse 4E/1 3100 St. Pölten

Wien, am 30. September 2008

## Abstract

The development effort for an application specific processor design with an associated software toolchain can be considerably reduced by the use of automatic tool generators. The idea of a universal processor architecture description language as basis for the automation of as many as possible parts of the toolchain, seems to be a promising approach in this direction.

The language xADL is able to universally describe architectures on a structural level and was especially developed for the embedded systems field. The xADL framework has a modular extendable design: various modules share a common preprocessed architecture description to generate different parts of the software toolchain.

In this work an xADL module that generates processor simulators along with applied basic concepts is presented. In the main part the technique of dynamic binary translation to improve the performance of those simulators is discussed and the LLVM framework, which is employed for this purpose is briefly described. Several methods to further increase simulation speed are presented and their effects are finally evaluated by means of simulators for two exemplary architectures.

# Kurzfassung

Die Erstellung eines anwendungsspezifischen Prozessordesigns inklusive passender Entwicklungswerkzeuge kann durch den Einsatz von Generatoren erheblich erleichtert werden. Ein Ansatz in diese Richtung ist der Einsatz einer universellen Architekturbeschreibungsprache, auf deren Grundlage möglichst viele Teile der Entwicklungswerkzeuge automatisch erstellt werden können.

Die Sprache xADL wurde speziell für den Embedded-Systems Bereich entwickelt und ermöglicht eine universelle Beschreibung auf einer strukturellen Ebene. Das zugehörige Framework ist erweiterbar und modular im Aufbau: verschiedene Module teilen sich eine vom Framework aufbereitete Architekturbeschreibung, um die unterschiedlichen Softwareteile zu generieren.

Die vorliegende Arbeit stellt ein xADL Modul zur Generierung von Simulatoren vor und erklärt die dafür verwendeten Konzepte. Im Hauptteil wird die dynamische Übersetzung von Maschinencode zur Beschleunigung dieser Simulatoren diskutiert und auf das dazu eingesetzte LLVM-Framework kurz eingegangen. Diverse Ansätze zur weiteren Steigerung der Performance werden präsentiert und in einem abschließenden Vergleich anhand zweier konkreter Beispiel-Architekturen bewertet.

# Contents

| Introduction |     |                                    |                                              |    |  |  |  |  |  |  |

|--------------|-----|------------------------------------|----------------------------------------------|----|--|--|--|--|--|--|

| 1            | Cor | nputer                             | Architectures                                | 9  |  |  |  |  |  |  |

|              | 1.1 | Instru                             | ction Set Architectures                      | 10 |  |  |  |  |  |  |

|              |     | 1.1.1                              | Categorisation                               | 10 |  |  |  |  |  |  |

|              |     | 1.1.2                              | Operations                                   | 11 |  |  |  |  |  |  |

|              |     | 1.1.3                              | Operands                                     | 12 |  |  |  |  |  |  |

|              |     | 1.1.4                              | Memory Access                                | 12 |  |  |  |  |  |  |

|              | 1.2 | Comp                               | uter Micro Architecture                      | 13 |  |  |  |  |  |  |

|              |     | 1.2.1                              | Pipelining                                   | 14 |  |  |  |  |  |  |

|              |     | 1.2.2                              | Stalling                                     | 14 |  |  |  |  |  |  |

|              |     | 1.2.3                              | Forwarding                                   | 15 |  |  |  |  |  |  |

|              |     | 1.2.4                              | Caching                                      | 15 |  |  |  |  |  |  |

|              |     | 1.2.5                              | Branch Prediction                            | 15 |  |  |  |  |  |  |

|              |     | 1.2.6                              | Advanced Pipelining                          | 16 |  |  |  |  |  |  |

| <b>2</b>     | Arc | Architecture Description Languages |                                              |    |  |  |  |  |  |  |

|              | 2.1 | 2.1 Classification                 |                                              |    |  |  |  |  |  |  |

|              | 2.2 | Relate                             | d Work                                       | 19 |  |  |  |  |  |  |

|              |     | 2.2.1                              | MIMOLA                                       | 19 |  |  |  |  |  |  |

|              |     | 2.2.2                              | ISDL                                         | 20 |  |  |  |  |  |  |

|              |     | 2.2.3                              | Expression                                   | 20 |  |  |  |  |  |  |

|              |     | 2.2.4                              | LISA                                         | 21 |  |  |  |  |  |  |

|              |     | 2.2.5                              | nML                                          | 21 |  |  |  |  |  |  |

|              |     | 2.2.6                              | MADL                                         | 21 |  |  |  |  |  |  |

|              |     | 2.2.7                              | PD-XML                                       | 21 |  |  |  |  |  |  |

|              |     | 2.2.8                              | ArchC                                        | 22 |  |  |  |  |  |  |

|              |     | 2.2.9                              | Generic Netlists                             | 22 |  |  |  |  |  |  |

|              |     | 2.2.10                             | Portable Compiled Instruction-set Simulators | 22 |  |  |  |  |  |  |

|              | 2.3 | xADL                               | -<br>· · · · · · · · · · · · · · · · · · ·   | 23 |  |  |  |  |  |  |

|              |     | 2.3.1                              | Syntax                                       | 24 |  |  |  |  |  |  |

|              |     | 2.3.2                              | Instruction Set                              | 27 |  |  |  |  |  |  |

| 3 | Simulator Generator |         |                                                                                                                                    |  |  |  |  |

|---|---------------------|---------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | 3.1                 | Simula  | ator Framework                                                                                                                     |  |  |  |  |

|   |                     | 3.1.1   | Simulation Model                                                                                                                   |  |  |  |  |

|   |                     | 3.1.2   | Architectural State                                                                                                                |  |  |  |  |

|   |                     | 3.1.3   | Pipeline Organisation                                                                                                              |  |  |  |  |

|   |                     | 3.1.4   | Pipeline Simulation                                                                                                                |  |  |  |  |

|   | 3.2                 | System  | n Calls                                                                                                                            |  |  |  |  |

|   | 3.3                 | Binary  | $7 File Loading \dots \dots$ |  |  |  |  |

|   | 3.4                 | Intern  | al Description                                                                                                                     |  |  |  |  |

|   |                     | 3.4.1   | Memory-Elements                                                                                                                    |  |  |  |  |

|   |                     | 3.4.2   | Call Sequence                                                                                                                      |  |  |  |  |

|   |                     | 3.4.3   | Condition Tree                                                                                                                     |  |  |  |  |

|   |                     | 3.4.4   | Building up Internal Description                                                                                                   |  |  |  |  |

| 4 | Dvr                 | namic ' | Translator 37                                                                                                                      |  |  |  |  |

|   | 4.1                 |         | d Work                                                                                                                             |  |  |  |  |

|   |                     | 4.1.1   | History of JIT                                                                                                                     |  |  |  |  |

|   |                     | 4.1.2   | Shade                                                                                                                              |  |  |  |  |

|   |                     | 4.1.3   | Dynamo                                                                                                                             |  |  |  |  |

|   |                     | 4.1.4   | PIN                                                                                                                                |  |  |  |  |

|   |                     | 4.1.5   | Strata                                                                                                                             |  |  |  |  |

|   |                     | 4.1.6   | UQDBT                                                                                                                              |  |  |  |  |

|   |                     | 4.1.7   | bintrans                                                                                                                           |  |  |  |  |

|   |                     | 4.1.8   | Hot Code Recognition                                                                                                               |  |  |  |  |

|   |                     | 4.1.9   | High Speed CPU Simulation using JIT Binary Translation 40                                                                          |  |  |  |  |

|   |                     | 4.1.10  | iboy                                                                                                                               |  |  |  |  |

|   | 4.2                 | L2 LLVM |                                                                                                                                    |  |  |  |  |

|   | 4.3                 | Genera  | ation of LLVM Code                                                                                                                 |  |  |  |  |

|   |                     | 4.3.1   | Memory-Elements                                                                                                                    |  |  |  |  |

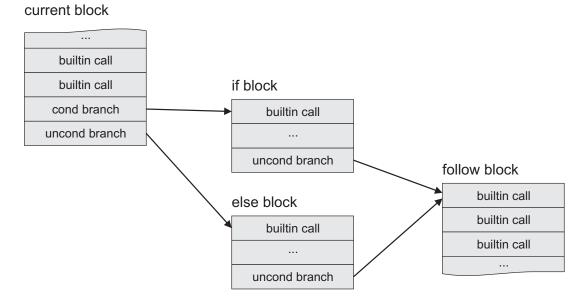

|   |                     | 4.3.2   | Conditional Structures                                                                                                             |  |  |  |  |

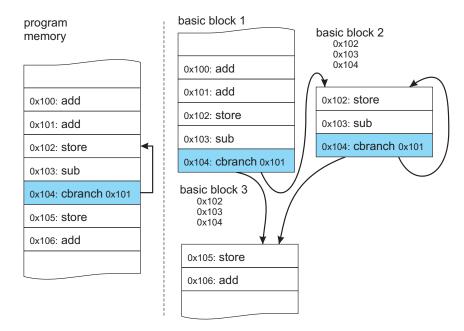

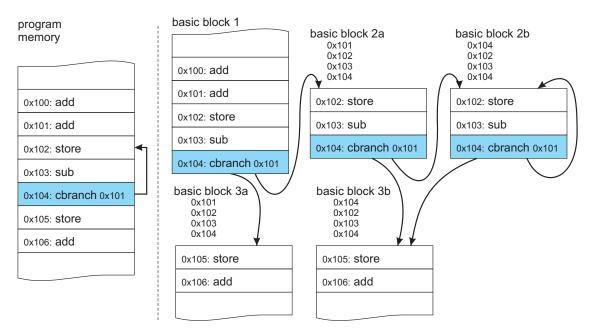

|   | 4.4                 |         | $Blocks \dots \dots$         |  |  |  |  |

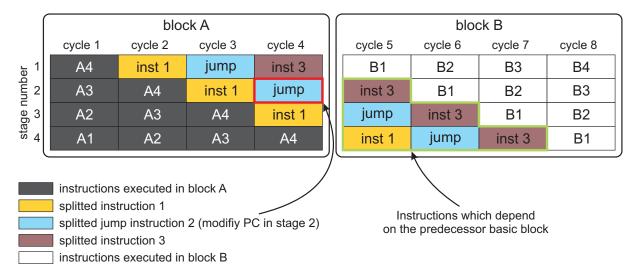

|   |                     | 4.4.1   | Overlapping Instructions                                                                                                           |  |  |  |  |

|   | 4.5                 | Cachir  | 0                                                                                                                                  |  |  |  |  |

|   | 4.6                 | -       | ilation in the Framework $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                     |  |  |  |  |

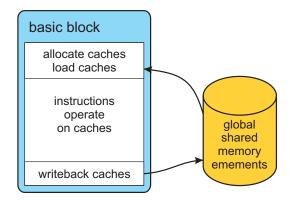

|   |                     | 4.6.1   | Compilation of Basic Blocks                                                                                                        |  |  |  |  |

|   |                     | 4.6.2   | Pipeline State Restoration                                                                                                         |  |  |  |  |

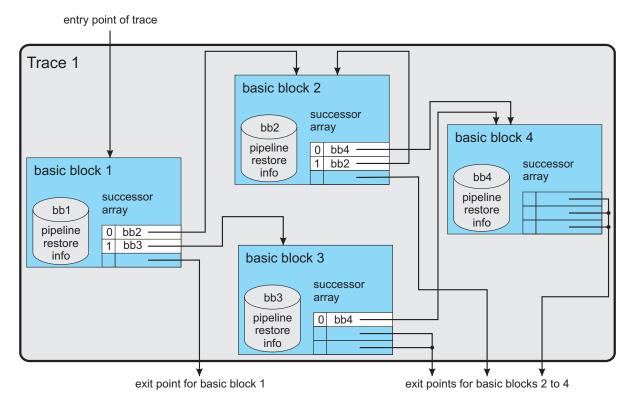

|   | 4.7                 |         | g of Basic Blocks                                                                                                                  |  |  |  |  |

|   |                     | 4.7.1   | Uncertainty of Successor Blocks                                                                                                    |  |  |  |  |

|   |                     | 4.7.2   | Return Values of Basic Blocks                                                                                                      |  |  |  |  |

|   | 10                  | 4.7.3   | Jump Analysis                                                                                                                      |  |  |  |  |

|   | 4.8                 | Traces  |                                                                                                                                    |  |  |  |  |

|   |                     | 4.8.1   | Recompilation of Hot Paths 54                                                                                                      |  |  |  |  |

|     | 4.8.2 Return Values of Traces                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4.9 | Optimisations                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 4.9.1 LLVM Passes                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 4.9.2 Compiletime Constants                   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 4.9.3 Reduced Global Scope                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Eva | Evaluation 6                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 5.1 | Benchmark Setup                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

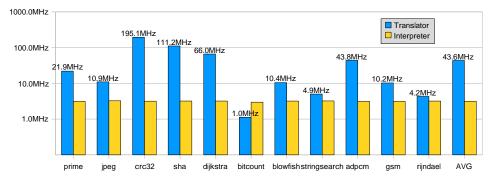

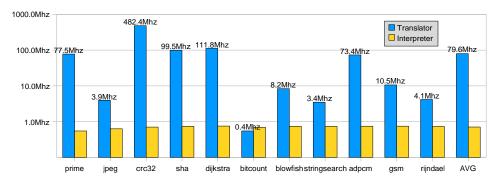

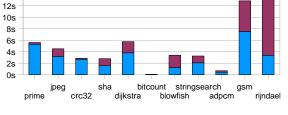

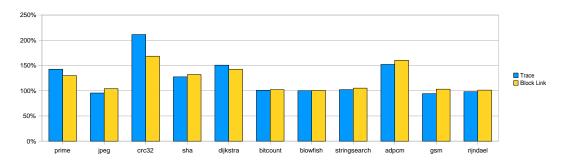

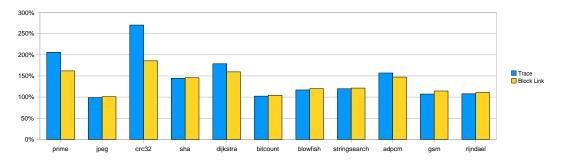

| 5.2 | 2 Comparison to Interpreter                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 5.3 | Analysis of Benchmark results                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

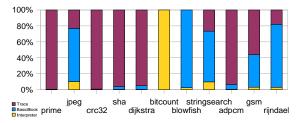

|     | 5.3.1 Benchmark Properties                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

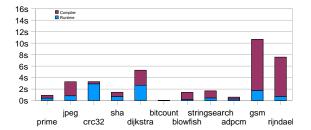

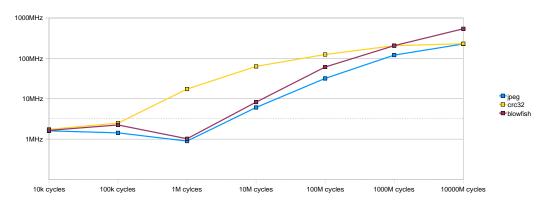

|     | 5.3.2 Compile Time Overhead                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 5.4 | Trade-off for Compile Thresholds              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

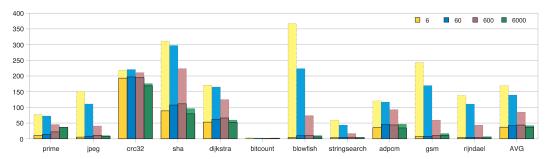

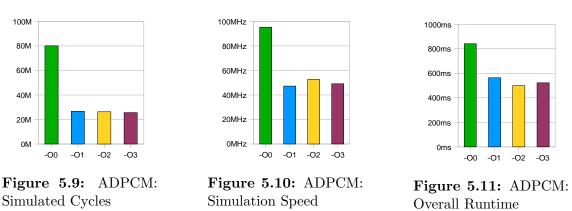

| 5.5 | Simulation of Unoptimised Applications        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

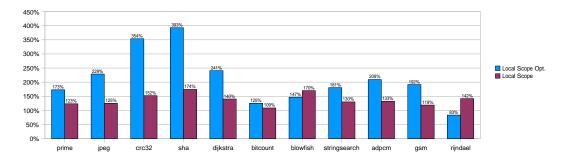

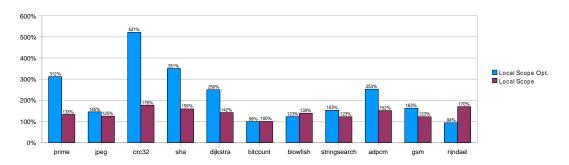

| 5.6 | Impact of Applied Optimisations               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

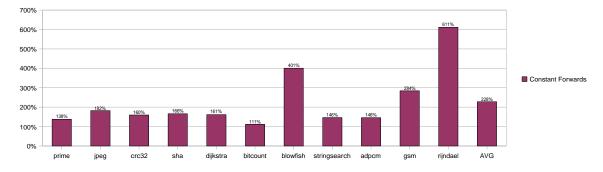

|     | 5.6.1 Constant Evaluation of Forward Links    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | <b>Eva</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | 4.9       Optimisations       5         4.9.1       LLVM Passes       5         4.9.2       Compiletime Constants       5         4.9.3       Reduced Global Scope       5         Evaluation       6         5.1       Benchmark Setup       6         5.2       Comparison to Interpreter       6         5.3       Analysis of Benchmark results       6         5.3.1       Benchmark Properties       6         5.3.2       Compile Time Overhead       6         5.4       Trade-off for Compile Thresholds       6         5.5       Simulation of Unoptimised Applications       6 |  |  |  |  |

## Conclusion

## Bibliography

vi

70

72

## Introduction

The Institute of Computer Languages at the TU Vienna has initiated the development of a generic architecture description language called xADL. It originates in the need for optimising retargetable compilers for application-specific embedded processors and revealed to be generic enough for the automatic generation of a wide range of hard- and software components like processor simulators or even hardware descriptions (VHDL). Besides the definition of the xADL language, an extensible framework is provided that comprises a variety of modules. These modules analyse a described architecture and generate specific parts of its toolchain.

In the course of two master theses a simulator generator module was implemented. Besides the development of a generator, producing retargetable simulators with instruction decoders, techniques of dynamic binary translation were applied to speed up these simulators. The design and implementation of the simulator generator and its optimisations were done in close collaboration of the authors. As two separate theses were intended the presentation of the overall project is divided into two individual parts: While one explains all necessary steps needed to translate an xADL description to a full-blown interpreting simulator, the other one focuses on applying dynamic binary translation in the context of these retargetable simulators.

As the fundamentals of the two theses have the same origin, the first chapters (including parts of this introduction) were authored in close cooperation and are identical in both works. At the beginning of the shared part various aspects of computer architectures to be considered for description languages and simulations are summarised (with a focus on embedded systems). A choice of description languages is categorised and compared to the philosophy of xADL. Its syntax and semantic are briefly defined and language constructs are outlined. The last shared chapter describes the simulation framework (those parts of the simulator not being generated) and roughly explains an internal description used as the basis for the two different parts of generated simulators: the interpreter and the dynamic binary translator.

This thesis describes the concepts of the applied dynamic binary translation. After the shared chapters, related work regarding runtime translation of binary code is summarised. An introduction to the LLVM compiler framework, which was used as a substructure for

runtime code compilation is presented next. The main part explains dynamic binary translation in detail and how it was deployed and refined to obtain high efficiency in the scenario of retargetable simulators. Starting at the compilation of basic blocks, considerations about increasing performance are made, which eventually lead to the concept of hot code identification and the "trace" as compilation unit. Additionally caching of compiled code and the aspects of simulation at the processor pipeline level are discussed. Special optimisations that are used to overcome shortcomings of LLVM finalise this part.

In a detailed evaluation two example architectures are used to sumarises the efficiency of the proposed translation technique for automatically generated simulators and its performance is compared to simulation using pure interpretion. The impact of different parameters on translation behaviour is investigated and forms the end of this diploma thesis.

This work is supported in part by ON DEMAND Microelectronics and the Christian Doppler Forschungsgesellschaft.

## Chapter 1

# **Computer Architectures**

It may be helpful to have definitions at hand when introducing abstract concepts like computer architecture. But as both terms "computer" and "architecture" cover wide areas in culture, science and everyday life such an exact definition can hardly be stated without some aspects getting out of sight.

To approach computer architectures let us first ask for the purpose of architecture in terms of planning and constructing buildings. Buildings serve fundamental and practical human needs like protection against natural environment as well as aesthetical ones. In practice there are a variety of subtle needs, goals and constraints a building has to meet. Without getting too philosophical this view clearly focuses on material aspects - the intended end product.

A similar view can be put on micro processor architecture. For one of the biggest sectors of the computer market - the desktop computer - there is a demand for the highest performance available per cost unit. This manifests in the end product: Small feature sizes provide maximal transistor counts, allowing expensive (in terms of transistors) performance optimisations at reasonable price.

When looking at a computer architecture, one can ask, what the reasons for design decisions might have been and find explanations for them - but immediately the question arises if one can think of a better implementation. This leads to another view: Architecture can be seen as the translation of abstract ideas to a concrete plan. A plan that most likely (but sometimes only hopefully) covers all needs and respects all constraints. Chapter 2 will cover architecture description languages that account for this view and allow to formalise, to plan computer architectures.

## **1.1 Instruction Set Architectures**

A look at the computer's history reveals that computer architecture first was a synonym for instruction set architecture. The instruction set architecture defines the number and types of operations, registers and memory addressing modes to be covered by the instruction set. The need for convenient assembler programming, maximal instruction execution frequency and minimal instruction count was initially seen as a problem of designing optimal instructions. It revealed that rapidly growing register budgets allowed on-chip dynamic translation of instruction sets - the structural implementation of computer (micro)architectures began to play the key role.

Nevertheless the instruction set architecture is important, as it is the interface to the micro architecture - still an instruction set may be favoured over another depending on how computer resources are accessed. Scientific computing may favour instruction sets with special operations while for complicated string operations rich addressing modes and conversion operations may be interesting. Recent instruction sets feature subsets that can be dynamically switched between (e.g. arm thumb) or high parallelism to be solved at compile time (VLIW architectures).

The following sections are a rough overview and mainly summarise [Hennessy and Patterson, 2007].

#### 1.1.1 Categorisation

Instruction set architectures differ in how operands and results are treated - a first categorisation of instruction sets pays attention to these differences. Typically sources for operands and destinations for results are organised as register files, linear memories or stacks.

- **Stack:** All operands are taken from the top of a memory stack. The result is pushed back on top again.

- Accumulator: One special register (the accumulator) is implicitly taken as one operand. The result of an operation is stored back to the accumulator again.

- **Memory/Register:** Operands of operations can be either taken from memory or a register file. The result may be stored back to a register or a memory location.

- **Register/Register Load/Store:** Operands must be taken from register files, the result must be stored back to a register. Access to memory is realised solely by special load/store instructions.

#### 1.1.2 Operations

The main purpose of an instruction set is to define the operations a micro architecture can perform per instruction cycle. One categorisation divides instructions into data manipulation instructions and control flow instructions.

Finer differentiation of data manipulation instructions divide them further into arithmetic and logical, data transfer, floating point, decimal and string manipulation instructions. Every field of operation may favour some special purpose operations like multiply-add for signal processing, powerful bit manipulation for control systems or high precision floating point for scientific calculations.

It is worth to take a closer look at control flow instructions, as they are some of the most frequently executed instructions, terminate basic blocks and need special handling in simulators that use binary translation. In general they can be divided into three categories (compare with [Hennessy and Patterson, 2007]):

Conditional Branches: Change programflow under certain conditions

Jumps: Unconditionally change programflow

Calls and Returns: Change programflow, save/restore the program counter

Control flow instructions (called jumps for simplification) must define how the program counter is modified. Either it is directly set to an absolute value (register value, value in memory, etc.) or it is modified by adding a displacement, which is called PC-relative. PC-relative addressing saves bits for short distance jumps and makes code positionindependent. Absolute jumps are used for constant jump targets like long distance calls but also when jumping to calculated addresses (typically called computed jump) like dynamically loaded library functions, virtual functions and branches of a switch statement. Calculated jumps play a key role in simulators as they cannot be easily evaluated before runtime. It should be noticed, that the return instruction is a special form of a calculated jump.

Theoretically every state within the microarchitecture is a candidate to be used as a condition for branches. In practice either a single register value, the relation between two registers, a single flag or the logical combination of flags determine if a branch is taken or not.

Some instruction set architectures (like ARM) define conditional execution not exclusively for branch instructions. Another extension to conditional execution are speculative instructions. These can be used to give the microarchitecture hints, if a branch is likely to be taken or to prefetch data (speculative loads). Instruction set architectures that are designed for low power consumption introduce even more special techniques. Some of these are: loads and stores that bypass the tag memory of a cache (a hit must be statically known), a register file hierarchy, energy-reduced instruction alternatives and explicit exception state management [Asanovic, 2000].

### 1.1.3 Operands

Operations can be seen as functions taking one or more input values producing (after a finite amount of microarchitecture cycles) one or more output values. The categorisation of different sources and destinations will be fuzzy, as theoretically every architectural state may be a source operand or a destination for a result:

- Registers, often specified by their index within a register file

- Internal state, often defined by a name (e.g. flags)

- Constant values, immediate values (also called constants and immediates)

- Memory objects, specified by their address

Section 1.1.4 describes handling of memory objects. Subsequently some aspects of register file access will (not exhaustively) be mentioned. First, registers may be divided into several banks. Each bank may be used by a subset of instructions or banks may act as shadow registers that can be dynamically switched. Partitioning to form register file hierarchies pays attention to the principle of locality (like caches do). Finally subregister naming allows instructions to access parts of a register by a special name (e.g. within the x86 instruction set).

### 1.1.4 Memory Access

An instruction set architecture must define how memory is accessed. Theoretically every method that brings bits onto the data/address bus of a memory is relevant. But with description languages in mind only the most common and important aspects of memory accesses should be summarised here.

Byte order is a first aspect differing from machine to machine. Byte order is relevant whenever multiple bytes are read/written to form larger entities (e.g. 32 Bit words). If a 4 Byte word is written and read again, the internal order of bytes is irrelevant, but if the same word is read with single byte accesses the order does matter. More precise: It defines how small portions of memory are aligned within larger ones.

The two common byte orders are called little endian and big endian. Little endian puts the least significant byte to the lowest byte address and the following ones to ascending addresses, while big endian places bytes exactly reverse. Order can also be relevant for smaller portions of memory and even single bits, but smaller than byte sized memory accesses are uncommon, single bits are usually masked out of larger entities.

Data transfer sizes within an instruction set are typically the size of the data bus and multiples/fractions of it. The MIPS architecture for example has a 32 Bit wide data bus and allows 8, 16, 32 and for special cases 64 Bit wide objects to be accessed within one instruction. An access to an object of size S at address A is called aligned if  $A \mod S = 0$ . Some architectures do not allow unaligned accesses, as they might impose multiple accesses to memory.

Another aspect of memory usage within the instruction set is the calculation of memory addresses. Typically the address used by an instruction is composed of a base address and a displacement (which is added to the base). The base typically is a register value (represented in the instruction by a register index) and the displacement may be a register or an immediate value. Techniques like memory management or usage of multiple memories lead to more complicated memory addressing.

Furthermore a memory access may not only fetch data but also increase registers (by a displacement or a constant), make physical out of virtual addresses, throw exceptions caused by violation of permissions or ranges and finally may reorder bytes. Thus memory accesses are not trivial to simulate, which is also true for micro architecture in general as methods to overcome the gap between memory bandwidth and latency (e.g. caches) cause high complexity.

### **1.2** Computer Micro Architecture

The micro architecture of a processor deals with the processors internal structure. It mainly provides a correct implementation of the instruction set making technical details like access to a cache, branch prediction or address calculations transparent. Of course these details are not fully hidden, they manifest (for example) in bounds for instruction execution times.

For a simulator this means that the more accuracy is required, the more aspects of the micro architecture have to be simulated. Without going into too much details this chapter presents those structures and methods used by micro architectures influencing cycle counts - targeting structures to be simulated by cycle accurate simulators. The intended use of the simulator for embedded systems further narrows down the topics.

#### 1.2.1 Pipelining

"Pipelining is an implementation technique whereby multiple instructions are overlapped in execution; it takes advantage of parallelism that exists among the actions needed to execute an instruction. Today, pipelining is the key implementation technique used to make fast CPUs" [Hennessy and Patterson, 2007].

Each instruction is divided into operations to be handled at each pipeline stage. For a given instruction set this division is not immediately clear. The longest delay of a stage determines the speed of the whole pipeline and pipeline hazards may occur. On the other hand pipeline design may influence instruction set decisions.

Hazards are the danger of influencing the instruction set in a way that was not intended: the danger of producing wrong results. They result from the nature of pipelined execution and are typically divided into three categories.

- **Structural Hazards:** A resource is needed in n different stages simultaneously only less than n accesses are possible.

- **Data Hazards:** Two instructions are in the pipeline. Read after Write (RAW) also called true dependency: the result of one instruction is needed by another one in the pipeline. Write after Write (WAW) and Write after Read (WAR), also called anti dependencies: writebacks to the register file may be out of order and cause wrong register file content (at some time).

- **Control Hazards:** The program counter is changed some instructions not being intended to get executed are in the pipeline.

One way to overcome pipeline hazards without introducing new hardware structures is to simply forbid instruction sequences causing them - the compiler must rearrange instructions or insert instructions that do not modify the architectural state (no-operations or nops) to overcome hazards. Below other methods are presented that do have impact to hardware structures in micro architectures, each addressing one or more types of hazards.

#### 1.2.2 Stalling

A prominent structural hazard occurs in Von Neumann architectures: the simultaneous access of the memory by the instruction fetch unit and some other unit needing an operand from memory. A solution is to stall the pipeline: The fetch stage neither touches the memory nor increases the program counter during that cycle - it produces a bubble (nop instruction) instead. The bubble resolves the conflict but consumes one extra cycle (the real fetch is delayed).

More general: If the hazard caused by two stages with numbers i and j (let i < j) is to be resolved by stalling, stage i delays its conflicting operation until the conflict is resolved. Every delayed cycle a nop is passed to the successor stage and all stages < i are blocked.

#### 1.2.3 Forwarding

Data hazards may also be solved by stalling, but it is more efficient (in terms of cycles needed) to directly connect the output of one unit producing the result to the input of another unit needing it as an operand. For example the result of the ALU can be forwarded to both inputs of the ALU itself. Two criteria must apply to make use of the forwarded value: The destination register index for that value must be the same as for the input value and the forwarded value must be valid for that cycle. Thus only the needed register value (no future or former value) is forwarded.

#### 1.2.4 Caching

A cache together with stalling can also resolve structural hazards. It is a special form of memory duplication: It holds a subset of the values of the cached memory - if a value is present in the cache it can be fetched from there, while another pipeline stage can use the main memory or another cache of it. Nonetheless the pipeline has to be stalled if a cache miss occurs. Of course the main purpose of a cache is to overcome high memory latencies and not to resolve pipeline hazards.

#### **1.2.5** Branch Prediction

The fetch unit has to know whether a conditional branch was taken and to which address control flow was transferred to. Within a pipeline this information may not be available in time: Instructions following the branch may be in the pipeline although the branch is taken. Depending on the instruction set architecture these instructions are either executed as so-called delay slots or have to be replaced by nop instructions (pipeline flush). For example the MIPS R4000 branch instruction consumes 3 cycles with one of them used as a delay slot. Branch predictors are state machines that "guess" the outcome of a branch to fetch instructions likely to be in the pipeline after a branch and thus try to avoid CPU cycles consumed by wrongly fetched instructions. A well designed fetch unit will correctly predict jumps at a high rate.

#### 1.2.6 Advanced Pipelining

A microarchitecture may contain more than one pipeline (e.g. in case of VLIW architectures) and a pipeline may split up to allow parallel execution and then reunion again for writing results.

The assignment of instructions to different successor stages is called issue. An exemplary implementation of Tomasulo's algorithm and extensions to it (solving problems involved in instruction scheduling (e.g. imprecise interrupts) are presented in the illuminating article [Sohi, 1990]. VLIW architectures have one fetch unit and multiple decode units but issuing may be fixed - therefore the multiple pipelines are called slots.

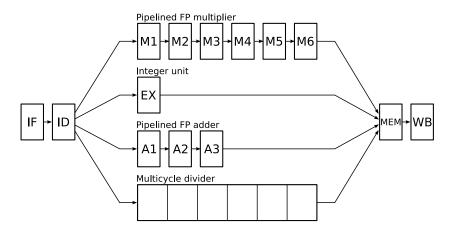

Figure 1.1: An advanced MIPS pipeline

Figure 1.1 illustrates an advanced MIPS pipeline presented in [Hennessy and Patterson, 2007]. It should be noticed that subpipelines may have different length and therefore instructions may reach the stage that merges the pipelines out of order - simultaneous writebacks and WAW hazards may occur. To avoid such hazards the issue stage must stall parts of the pipeline in scenarios detected by a stall logic. Reservation tables can be used by compilers to avoid stalls or by cycle accurate simulators to account for them. The advanced MIPS pipeline enables parallel execution of instructions, however every cycle at most one instruction can be issued. In contrast so-called superscalar architectures are able to issue multiple instructions each cycle - they reach a clock count per instruction smaller than one.

VLIW can be seen as a simplification of superscalar architectures - instruction scheduling is no longer done in hardware at runtime, but instead by the compiler at compile time. Multiple already scheduled instructions are fetched simultaneously - each filling a slot and being executed in a dedicated pipeline. The obvious advantage of this concept is its (hardware architectural) simplicity with the downside of increased instruction bandwidth and the dependency on high quality compiler designs. Other advanced topics include dynamic scheduling resulting in out-of-order issue, execute and writeback (e.g. CDC 6600 processor with scoreboards) or register renaming (solving WAR and WAW hazards) - But these topics go beyond the scope of this work.

## Chapter 2

# Architecture Description Languages

Advances in microchip technology lead to integration densities that allow whole systems to be implemented on a single die. These system-on-chip (SoC) systems offer interesting opportunities like shorter interconnects between subsystems and thus higher bandwidths or composition of many subsystems that are optimised for the specific application. Designs can profit from such application specific optimisations (e.g. in terms of performance or energy efficiency) but they have the drawback of longer design and implementation phases (compared to commercial of-the-shelf products) resulting in higher non-recurring engineering (NRE) cost.

Especially application specific processors are challenging as design decisions not only affect the hardware itself but also tools that are needed within the implementation process of the application software like compilers, assemblers or simulators. In the phase of design space exploration these tools are typically implemented and evaluated in an iterative process. Processor architecture description languages that support automatic generation of tools have the potential to dramatically shorten this process of design space exploration.

The term architecture description language covers hardware and software architectures but will be used as a synonym for hardware architecture description languages within this work.

### 2.1 Classification

Several processor description languages have been proposed, many of them originate in the demand for retargetable compilation infrastructures (see [Qin and Malik, 2002]). A first categorisation can be made in respect of the level of abstraction used. The higher the abstraction of a language the more difficult the task to cover a wide range of processors very specific or uncommon features may not be covered by the semantics - the lower the level of abstraction the more details must be explicitly stated, resulting in longer, more error-prone and harder to read and understand descriptions.

Hardware description languages such as VHDL or Verilog allow descriptions to be very low level - for example they allow for strongly asynchronous designs but lack sufficient abstraction to explore architectures at the system level [Mishra, 2005]. Modelling languages like UML on the other hand put focus on the whole system, describing subsystems and interfaces but leave open how components of subsystems function.

A quite common level of abstraction for architecture descriptions is that of register transfer level or RTL. It is characterised by using the clock cycle as the granularity of time, which is the time between two consecutive clock events on the physical hardware. Furthermore dataflow is modelled to happen after each clock cycle (at a clock event) by moving data from the input side of a register to its output side (infinitely fast). Data manipulation operations happen during one (or more) clock cycles. For synchronous systems this representation is very intuitive and has a long tradition in digital design.

Besides different levels of abstraction a distinction can be drawn between structural and behavioural descriptions, where in fact architecture description languages will contain both with putting focus on one of them. The semantics of a "structural" language together with a given description (e.g. a netlist) imply possible behaviours of the system. A "behavioural" description together with language semantics imply possible (possibly a lot of) structures that realise that behaviour. Even classical programming languages could be used to model hardware solely behavioural, but as they support a very high level of generality every single detail would have to be hand-coded.

### 2.2 Related Work

#### 2.2.1 MIMOLA

MIMOLA is a language developed in the late 70 is at the University of Kiel. With MI-MOLA hardware descriptions at RT-level can be generated out of descriptions of typical applications (in a Pascal-like form) together with execution frequencies of paths through these applications and replacement rules for application elements [Mishra and Dutt, 2004]. Besides MIMOLA allows predefined resource specifications that can partly or fully describe a machine structure (through modules and their interconnects at a RTlevel). Missing structures are generated by MIMOLA as a result of transforming different MIMOLA language inputs - MIMOLA is therefore categorised as a structural description language [Mishra, 2005].

#### 2.2.2 ISDL

With ISDL (Instruction Set Description Language) an architecture is described on a behavioural level. It is designed to cover a broad range of instruction set types like VLIWs or DSP extensions and serves as a starting point for generating a compiler and an assembler [Hadjiyiannis et al., 1997]. Generality is reached through the use of C syntax wrapped into different language constructs that form several sections:

- Instruction Word Format: Names are provided for bitfields (i.e. consecutive bits).

- Global Definitions: Definitions in this section support the generation of Lex and Yacc [Levine et al., 1992]. So-called split functions allow long bit sequences (like immediate values) to be split up into multiple bitfields.

- Storage Resources: Register files, single registers and memories can be defined.

- Assembly Syntax: Parallel operations for each single instruction are defined.

- Constraints: Reduces the number of possible combinations of operations to those allowed by the architecture.

- Optimisations: This section is optional and intended to give compiler hints resulting in faster code.

Later achievements [Hadjiyiannis et al., 1999] include an instruction set simulator and present algorithms for extraction of structural information that can be used by a hardware synthesis tool. The generation of the simulator is not described in detail.

#### 2.2.3 Expression

Expression is a description language that consists of behavioural and structural elements. Its main goal is the support of design space exploration and software toolkit generation. An interesting feature of Expression is its ability for rapid design space exploration that allows the designer to make use of reduced accuracy of descriptions resulting in coarse evaluation of alternative design candidates. With the full description it is possible to generate an optimising compiler and a cycle accurate simulator. Scheduling information for the compiler that is caused by conflicts in the pipeline is not explicitly specified in the description but computed out of the structural description. Different memory systems (including hierarchies and buses) can be specified in expression and are respected by the generated optimising compiler. The language itself consists of different sections that specify operations, instructions, components, data transfer paths and memory systems. The use of expression for automated generation of VHDL hardware descriptions is presented in [Mishra et al., 2004].

#### 2.2.4 LISA

LISA is an architecture description language initially designed to enable retargeting of fast compiled simulators [Pees et al., 1999]. A LISA description allows to specify pipelined architectures on an operational level enabling the generated simulator to be cycle and even phase accurate. The behavioural description of one instruction is built up out of atomic operations (e.g. arithmetic or logical). Precise timing information on the other hand result from resource consumption expressed by atomic operations organised in extended Gantt charts. A restriction of LISA is the assumption that bubbles are inserted in the pipeline on resource conflicts, thus disabling simulation of out-of-order architectures. An extension to LISA is described in [Braun et al., 2004]. The generation of compilers was enabled by adding special semantics code to the description.

#### 2.2.5 nML

nML is a mixed description language that embodies structural an behavioural descriptions. Storages (memories) are the central elements being both used as a skeleton for structural interconnects and as the representation of the architectural state [Fauth et al., 1995]. The programmers view of the architecture (including assembler mnemonics and binary encoding) is used as the level of abstraction leaving details of the micro architectures implementation undefined. Descriptions in nML are however rich enough to be used as models for automatically generated simulators [Rajesh and Moona, 1999].

#### 2.2.6 MADL

The Mescal Architecture Description Language (MADL) described by [Qin et al., 2004] has been used to generate cycle accurate simulators, instruction schedulers and register allocators. The layered approach partitions toolset specific constructs and architecture specific functionality. A core ability of MADL is the possibility to define instructions via finite state machines. Structural and data resources are modelled as tokens passed to these state machines. Functional units can act as token managers assigning hardware resources to instructions. This describes parallelism in a natural way and covers more complex architectures like modern superscalar processors with out-of-order execution. MADL was used to generate cycle accurate simulators for different architectures.

#### 2.2.7 PD-XML

Seng et al. propose a language with XML syntax [Seng et al., 2002]. A description consists of three types of elements: storage (e.g. register files), an instruction set description

and a resource (microarchitecture) description. The microarchitecture is described on high or low level, where one high level description can be mapped to different low level implementations - supporting PD-XMLs claim for high flexibility.

#### 2.2.8 ArchC

ArchC [Azevedo et al., 2005] is a description language based on SystemC with a higher abstraction level intended for processor description. The two parts of the description define the architecture resources on one hand and the instruction set on the other. The possibility to verify detailed descriptions with coarse behavioural models is a useful feature of ArchC. A full blown simulator generator is able to generate cycle accurate simulators that optionally use compilation techniques. An ABI section in the description defines the application binary interface used by the simulators for handling of system calls which are used to simulate an operation system environment [Bartholomeu et al., 2003]. All tools and documentations are freely available as ArchC is developed as an open source project.

#### 2.2.9 Generic Netlists

Architecture Description Languages can be used to generate hardware descriptions as presented in [Gorjiara et al., 2006]. In this paper it is demonstrated how an application (in form of C Code) together with an XML based architecture description (generic netlist representation - GNR) can be translated to a synthesisable (and simulateable) hardware description. The architecture description only outlines the machine, while the instructions (in form of so-called control words) are generated and stored in the synthesised memories. The presented form of hardware description is targeted to very application specific processors ("tight" hardware/software co-design) but not suited to develop general purpose cores.

#### 2.2.10 Portable Compiled Instruction-set Simulators

D'Errico and Qin present a retargetable simulator framework that uses a behavioural description to generate interpreting and translating (both static and dynamic) simulators [D'Errico and Qin, 2006]. They highlight the advantages of retargetable and portable simulators. For their translating simulators, target instructions are converted to C++ code which is compiled with GCC to one of many supported host architectures. The dynamic translating simulator uses GCC to compile dynamically loaded libraries which are loaded at runtime. To reduce compiletime only frequently executed parts of the target application are compiled - the rest is interpreted. They include measurements highlighting speed gains obtained by using run-time translation (being approximately 4 times faster).

### 2.3 xADL

The xADL is a structural description language developed at the TU Vienna, Institute of Computer Languages. It uses extensible markup language (XML) syntax to describe embedded pipelined architectures. They are described by their structure in form of functional units, registers and memories connected in a network. Functional units can have user defined functionality described by atomic operations that are precisely defined in xADL. Only simple memory hierarchies (without a memory mapping unit) are supported in xADL (at least at the moment) which limits its application area to processors with simple memory subsystems often found in embedded systems. It is however possible to describe different types of caches that are characterised by their features (rather than by their explicit functionality).

The xADL language is distinguished by the following paradigm: A single compact description serves as the basis for a wide variety of analyses and generators (xADL modules). Language constructs that directly support generators by giving explicit hints are avoided. Therefore many different modules can be supported without redundancies that could make architecture changes (needed in design space exploration) cumbersome or even contradicting (which could lead to inconsistent results of different modules). Examples for this paradigm are lacking explicit listings of the instruction set or reservation tables.

The compact description shifts complexity to the analyses and generator modules - a module is responsible for extracting information out of a non-specific abstract description. As mentioned above this complexity is justified by descriptions being compact and consistent.

Another interesting aspect of xADL is its support for VLIW architectures - units can simply be duplicated by defining a repeat-count.

Besides pure hardware xADL describes the interface to the software system within a special ABI section. It defines how values are passed to functions, how registers are saved on calling functions and which registers are reserved for special purposes (like the program counter and the stack pointer). This information is especially useful for compiler related generator modules but can also be important for other modules.

Currently two different architectures are described in xADL: A MIPS R2000 derivate and the CHILI architecture (a novel 4-way VLIW architecture developed by ON DEMAND Microelectronics). While the MIPS description evolved together with the development of xADL and its modules the description of the CHILI architecture could be easily implemented afterwards without any major changes to xADL. Modules that are available by now include a generator for compiler related tables and rules, an instruction set extractor, a visualisation module (producing a network graph of the architectures structure) and a simulator generator. This simulator generator, its output and all involved technologies are the topic of this work and are described in the main chapters.

#### 2.3.1 Syntax

As already stated, XML is the base of the xADL syntax. An xADL architecture description must contain the <adl:Architecture> top level construct, an ABI tag, at least one configuration and the netlist of units and datapaths building the architectures structure.

#### ABI

The ABI tag specifies the binary interface used by the software system of the architecture. All registers are categorised in classes and their use for argument passing and return values is specified. Special registers like the stack pointer are defined and optionally a name is assigned to each register in the registerfiles - for example these names can be used by modules for debugging purposes or automated generation of documentation. Memories can be classified to be data and/or program memories. It is possible to define more (named) ABI sections inside one architecture description that can be switched between by executing the xADL toolkit "adlgen" with different parameters.

#### Configuration

It is possible to define multiple configuration tags each of which specifies values for symbolic parameters. These parameters can be used in the structured netlist description as bitwidth parameters (e.g. for registers or buses) repeat counts of units or register counts inside a registerfile. Therefore it is possible to explore different versions of an architecture with differing parameters in just one description (e.g. 32-Bit versus 64-Bit architecture). Additionally it is possible to define components inside configuration tags to enable different versions of components in a description.

#### Types

Before the structured netlist can be defined in xADL the types of all used components have to be declared. These components can be immediates, memories, caches, registers or functional units. The corresponding language constructs and its parameters that declare types are described in the following list.

• <MemoryType>

Like any other type declaration memory types must be given a name. The size of the memory is specified in bytes, its latency parameters is coarsely stated in cycles by the *min-delay* and *max-delay* properties. A number of input and output ports define the memory interface. An additional address (input) port does not need to be defined - it is added implicitly for each input and output port. The bitwidth of ports and the number of bits used for addressing can be specified together with optional *baseaddress* and *alignment* attributes.

$\bullet$  <CacheType>

Caches are roughly declared by their latencies (similar to memories) and a *type* attribute. For example such a *type* can be "set-associative". The exact semantics of these types is not defined in detail yet.

• <RegisterType>

Registers have these main attributes: *name*, *bitwidth* and *repeatcount*. For this type the *repeat-count* is not only useful in the case of VLIW architectures. It is used to define register files. Ports define the interface of register files: they can be assigned a read-only, write-only or read/write attribute. The bitwidth attribute of ports defines how many bits of a register are accessed while the offset attribute specifies which bits are accessed. Note that the ports bitwidth may be different from the registers *bitwidth* and thus allows definition of subregisters (as found on x86 for example). If offset and width are omitted the full register is accessed by default. On many architectures constant registers are found. A constant tag with its *index* and *value* attributes declares a register to be constant and what value it holds.

$\bullet~< \mbox{ImmediateType} >$

Immediates origin from instruction words. Although they are therefore not part of the hardware, they can be seen as data sources (similar to registers) and thus are connected to the network of units like any other read-only data component. The only attributes of immediate types are *name* and *bitwidth*.

• <UnitType>

Unit types are the most comprehensive types. Like others they have a name and contain ports defining their interface. Units are the components that implement a functionality defined by their operations that themselves consist of micro operations (built-in calls). Furthermore units can encapsulate networks of other components like registers, immediates or even (sub) units to support hierarchical design - such an encapsulating unit may not define operations as they are only permitted on the lowest level of the hierarchy.

Operations can process information delivered to input ports of units and specify how outputs are computed. It is possible to define several operations in a single unit. This means that these operations are alternative computations that can be performed by the unit. An example for this are different arithmetic operations performed in an ALU unit type.

Besides inputs, outputs and constants, temporaries serve as additional parameters for built-in calls. They are declared inside the unit type and have *name* and *bitwidth*

attributes, constants carry a value. The following section describes operations in detail.

#### Operations

As mentioned before operations are declared within unit types. Apart from a name operations have two specific attributes - *syntax* and *binary* which are described in Section 2.3.2. The building blocks of operations, named calls, are collected within *body* tags. Several predefined built-in calls are available to model a units behaviour. Additionally it is possible to implement user defined calls but their exact functionality and semantics are left open at the moment.

To define (complicated) operations several built-in calls can be combined - it is however not possible to nest calls. Instead temporaries are needed to reuse results as built-in call arguments. There is one distinguished built-in call to model conditional functionality: *cmove*. The functionality of the conditional move call is as follows: an argument is evaluated to true or false (like in C its value is compared to zero) and depending on that one of the two additional arguments is stored as the result of the call.

#### Instantiation of Types

This part of the xADL description forms up the concrete network out of instantiated components and connections. Typically it begins with instantiating the data sources (sinks) already mentioned: registers, immediates, memories and caches. These instantiations have in common to need a name tag and one to reference the instantiated type. For caches the memory instance that is cached needs to be stated. Registers have a *category* property that defines special purposes (e.g. integer, base, etc.).

However the major part of the instantiations is formed up by units. They are the only components allowed to use the *connect* tag that specifies the datapaths between components and thus the architectures structure. The syntax of these connect tags allows to specify separate *input* and *output* connections for the interface of the corresponding unit. Both of them use the *select* attribute to reference the other end of a connection (inputports for output connections and vice versa). When two functional units are connected to each other, it does not matter whether this is described by an input connect in one unit or an output connect in the other.

An important property of connections is declared by the *stageboundary* attribute: It gives connections the semantics of transferring data only on clock events (modelling of hardware register transfer). Such connections are used to split components that belong to different pipeline stages.

Hazards have a similar syntax to connections, but quite different semantics. They are used

to model (virtual) connections between units, that are used to resolve pipeline conflicts. The *forward* hazard is a connection that forwards a result from an output port to an input port and thus resolves data hazards. The *stall* hazard, if connecting an input and an output port has a similar purpose, but instead of forwarding a value it has the semantics to stall the pipeline until the result is available at the input port (e.g. until it is written back to the register file). If the *stall* hazard connects two output ports its semantics is to resolve WAW conflicts. The *ignore* hazard is a dummy signalling a hazard not being resolved in hardware (e.g. this information can be used by a compiler generating module to resolve conflicts in software).

#### 2.3.2 Instruction Set

As already mentioned the instruction set is not defined explicitly. The instruction set is extracted by following all possible paths in the network using a breath first search. Each path represents a potential instruction of the architecture. But typically not every path corresponds to an instruction, thus xADL uses a predicate/condition concept to exclude paths. Predicates and conditions can be defined along data paths inside units, unit types and operations. The *condition* tags evaluate *predicate* tags defined earlier on the path and omit instructions that do not satisfy those conditions.

An example for such *condition* is to use a restricted set of operations in an ALU for address calculation: A predicate *addressable* could be set for addition and subtraction an appropriate *condition* in a memory access unit could forbid all other ALU operations.

#### Syntax and Binary Representation

When describing an existing architecture the syntax or at least the binary encoding of instructions have to be specified to make fully automatic toolkit generation possible. In xADL the syntax of instructions is described constructively along the instruction path. In a syntax section one or more syntax templates specify different types of instructions. They may consist of strings and several tokens. Most components in the network (even connections) may use *syntax* tags that specify concrete values for tokens. Those values can be strings, values of immediates or indices in a register file.

The binary encoding of instructions is defined similarly with templates and tokens. Additionally bitmasks select characteristic bits of an instruction word. The values for these masks are assigned just like tokens along the instruction path.

This form of syntax and binary description is especially suited for orthogonal instruction sets, often found in embedded processors, because only few different syntax templates are needed.

## Chapter 3

# Simulator Generator

This chapter focuses on the automated generation of simulators for an architecture described in xADL. The architecture to be simulated is called "source", while the architecture that runs the generated simulator is called "host". There are many purposes for which simulators can be useful: (old) applications that are written for the source architecture can be used on (modern) hosts even when the sourcecode of these applications is not available or difficult to port; debugging is possible at a very low level and performance bottlenecks of applications can be detected at the microarchitectural layer where cache misses or pipeline stalls are relevant for execution speed.

When a simulator is generated from a high level description language it is easy to change important parameters of the architecture, like the number of registers or the number of functional units. To evaluate the properties of the resulting architecture, benchmarks compiled for this new architecture are needed. An automated generation of compilers from the same description language makes such benchmarks possible and enables to evaluate completely new architectures even in their (early) design phase. The xADL has the potential to provide these features and parts of them are already finished.

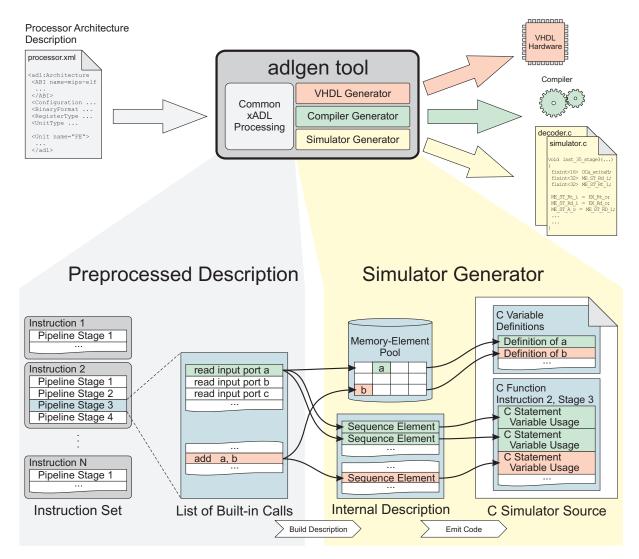

The simulator generator presented in this work supports the generation of both an interpreter and a dynamic binary translator. For code generation of the translator the LLVM framework is used; it provides a generic interface to produce code for a variety of host architectures and is frequently improved by its active developer community.

The core of the simulator generator is implemented in form of a module for the xADL framework. This framework (among other things) is able to extract the instruction set of a specified architecture. The simulator builds on this instruction set that specifies in detail when (in which pipeline stage) and which operations are to be performed by an instruction. This information is then transformed to an executable form and enriched by the operations needed for the simulation of the whole architecture. Besides the executable description of the instruction set, other important architecture specific parts, like the

instruction decoder or the virtual register files, are generated to complete the simulator.

### 3.1 Simulator Framework

The source code of the simulator is not completely generated out of the architecture description language. This chapter explains the hand-written framework that contains architecture independent parts of the simulator. Important parameters for this framework like the number of pipeline stages and slots or the sizes of memories are set by pre-processor macros in the generated code.

#### 3.1.1 Simulation Model

The core of a classical interpreting simulator consists of a loop iterating through simulated instructions of the source architecture. An instruction is loaded from the simulated program memory, decoded from its binary representation and then executed: The simulated registers and memories are altered according to the semantics of that instruction.

It is possible to implement simulation at different levels of abstraction: Instruction set simulators provide a semantic model of the instruction set but ignore the source architectures internal structure. While such simulators may perfectly run binary applications they are inherently inaccurate when exact timings (cycle count) of the simulation are needed. Especially for architectures that have memory hierarchies, multiple pipelines or other features that dynamically influence the execution speed of an application, at least some parts of the architecture's structure have to be taken into account to make cycle accurate simulations possible.

At a very low level of abstraction (e.g. transistor level simulation) internal timings even for physical phenomena like signal propagation can be taken into account.

Of course the simulation speed depends on the level of abstraction: Generally a lower abstraction level leads to lower simulation speed.

We use pipeline simulation that operates on a moderate level of abstraction and features an explicit model of the architectures pipeline structure. In that case one iteration of the simulators main loop does not simulate the semantics of a whole instruction but that of a clock cycle (shifting instructions through the pipeline).

#### 3.1.2 Architectural State