Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

### DIPLOMARBEIT

# A Resource Management Scheme for the TT-SoC Architecture

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Diplom - Ingenieurs

am

Institut für Technische Informatik 182/1

$\operatorname{der}$

Technischen Universität Wien

unter der Leitung von

o. Univ. - Prof. Dr. Hermann Kopetz

und

Univ.Ass. Dipl.-Ing. Bernhard Huber

als verantwortlich mitwirkendem Assistenten

durch

Bernhard Weirich Bakk.techn. Matr. - Nr. 0126357 Utendorfgasse 3/3, A–1140 Wien

Wien, im März 2008

# A Resource Management Scheme for the TT-SoC Architecture

The advance of computer chip manufacturing technology makes it possible to construct full-featured systems on a single chip, yielding a number of advantages. One of which is that very efficient interconnects with high data rates are possible, since each component is part of the chip.

However, there is the risk that the different components, if not properly separated, influence each other. Thus, even a low priority application might cause the operation of a highly critical real-time task to fail. To avoid such a situation the interactions between applications must be encapsulated. To this end the TTSoC architecture uses a central time-triggered on-chip interconnect. This interconnect is protected by a guard, denoted Trusted Interface Subsystem (TISS), at each micro component to guarantee the correct operation.

The objective of this thesis is the design and implementation of a resource management infrastructure for the TT-SoC architecture. Resource management is important when resources are limited, which is not unusual for embedded systems. In particular, on battery operated devices power consumption should be kept at a minimum. Dynamic resource management enables efficient usage of the resources, since they may be allocated on demand and freed when they are no longer needed. For the proposed resource management solution, the components which are involved, their mutual interfaces and the algorithms that run on the components are described and evaluated. Care is taken that the encapsulation, which is encouraged by the TT-SoC architecture, is preserved. This is achieved by dividing the system into trusted and non-trusted parts and by protecting the access to the components within the trusted part.

# Ein Resourcenverwaltungssystem für die TT-SoC Architektur

Der Fortschritt der Chipfertigungstechnik ermöglicht es, ein voll funktionsfähiges System auf einem einzelnen Chip unterzubringen, wodurch sich viele Vorteile ergeben. Einer der Vorteile ist die sehr effiziente Kommunikation der Komponenten untereinander.

Es besteht jedoch die Gefahr, dass die mitunter sehr verschiedenen Komponenten, sofern sie nicht entsprechend voneinander abgegrenzt sind, sich gegenseitig beeinträchtigen. Dadurch kann selbst eine Applikation mit niedriger Priorität die Funktion einer sicherheitskritischen Echtzeitanwendung stören. Um das zu vermeiden, benötigt man deterministische und vor unbeabsichtigten Eingriffen geschützte Schnittstellen. Die TT-SoC Architektur, die auf einem zeitgesteuerten On-Chip Netz aufbaut, wurde für diese Zwecke entworfen. Zugriffe auf das On-Chip Netz werden vom sogenannten Trusted Interface Subsystem (TISS) überwacht, wodurch eine korrekte Funktionsweise gewährleistet werden kann.

Das Ziel dieser Arbeit ist der Entwurf und die Implementierung einer Infrastruktur zur Ressourcenverwaltung für die TT-SoC Architektur. Ressourcenverwaltung ist für Systeme wichtig, in denen nur wenig Ressourcen zur Verfügung stehen. Im besonderen in batteriebetriebenen Geräten muss auf eine geringe Leistungsaufnahme geachtet werden. Dynamische Ressourcenverwaltung erlaubt effiziente Nutzung der Ressourcen, da diese nur bei Bedarf angefordert werden und nach Gebrauch wieder für andere Anwendungen nutzbar sind.

In dieser Arbeit wird ein Lösungsansatz zur Ressourcenverwaltung vorgestellt. Weiters werden die dafür notwendigen Komponenten, die gegenseitigen Schnittstellen und die verwendeten Algorithmen erläutert. Es wird dabei darauf geachtet, dass "Encapsulation" (Abkapselung), eine wichtige Eigenschaft der TT-SoC Architektur, nicht beeinträchtigt wird. Dies wird dadurch erreicht, indem das System in vertrauenswürdige und nicht vertrauenswürdige Teile unterteilt wird, wobei der Zugriff auf Komponenten im vertrauenswürdigen Bereich überwacht wird.

## Danksagung

Ich möchte mich an dieser Stelle bei jenen bedanken die zur Arbeit beigetragen haben. Allen voran meinem betreuenden Assistenten Bernhard Huber, der mit viel Mühe und Sorgfalt über der Entstehung der Arbeit gewacht hat. Weiters sollen meine Eltern Elisabeth und Herbert Weirich nicht unerwähnt bleiben, die mir während der gesamten Ausbildung den Rücken freigehalten haben und mir somit die Möglichkeit gaben mich voll und ganz auf das Studium zu konzentrieren. Mein Dank gilt auch meiner Freundin Nicole Fuchs, die mir den notwendigen Ausgleich zur manchmal trockenen Arbeit geboten hat.

Vielen Dank auch an jene durch die das TT-SoC Projekt entstanden ist und auch an diejenigen, die am Projekt an meiner Seite mitgewirkt haben.

# Contents

| Co            | onten | ats                                       | ix       |

|---------------|-------|-------------------------------------------|----------|

| $\mathbf{Li}$ | st of | Figures x                                 | iii      |

| $\mathbf{Li}$ | st of | Tables                                    | xv       |

| 1             | Intr  | oduction                                  | 1        |

|               | 1.1   | Motivation                                | 1        |

|               | 1.2   | Contribution                              | 2        |

|               | 1.3   | Structure of this Thesis                  | 2        |

| <b>2</b>      | Basi  | ic Terms and Concepts                     | <b>5</b> |

|               | 2.1   | Real-Time Systems                         | 5        |

|               |       | 2.1.1 Time Division Multiple Access       | 6        |

|               | 2.2   | Pulsed Data Streams                       | 6        |

|               | 2.3   | System-on-Chip                            | 7        |

|               |       | 2.3.1 Network-on-Chip                     | 8        |

|               | 2.4   | Scheduling Techniques                     | 8        |

|               |       | 2.4.1 Online vs. Offline Scheduling       | 9        |

|               |       | 2.4.2 Basic Techniques                    | 9        |

|               | 2.5   | Related Work                              | 10       |

| 3             | Tim   | e-Triggered System-on-a-Chip Architecture | 11       |

|               | 3.1   | Properties / Characteristics              | 11       |

|               | 3.2   | Structure                                 | 12       |

|               |       | 3.2.1 Trusted Interface Subsystem         | 13       |

|               |       | 3.2.2 CNI/Middleware Layer                | 14       |

|               |       | 3.2.3 Host                                | 14       |

|               |       | 3.2.4 Dedicated Hosts                     | 15       |

|               | 3.3   | Network-on-Chip                           | 16       |

| 4        | Solı         | tion Design 19                                                                                                                        |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.1          | Resource Management Cycle                                                                                                             |

|          | 4.2          | Resource Management Authority 22                                                                                                      |

|          | 4.3          | Trusted Network Authority 22                                                                                                          |

|          | 4.4          | Scheduling Constraints                                                                                                                |

|          | 4.5          | Scheduler for Pulsed Data Streams                                                                                                     |

|          |              | 4.5.1 Inputs $\ldots \ldots 23$                          |

|          |              | 4.5.2 Preparations $\ldots \ldots 24$      |

|          |              | 4.5.3 Scheduling order $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 28$                                            |

|          |              | 4.5.4 Algorithm Properties                                                                                                            |

|          |              | 4.5.5 Example Execution $\ldots \ldots 20$                             |

|          |              | 4.5.6 Restricted Pulses                                                                                                               |

|          |              | 4.5.7 Constraint $3 \ldots 3$                                                                                                         |

|          |              | 4.5.8 Static pulses $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 33$                                        |

|          | 4.6          | Listings                                                                                                                              |

|          | 4.7          | Verification                                                                                                                          |

|          |              | 4.7.1 Verification Tests $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$                                                         |

| -        | т            | 1 / ···                                                                                                                               |

| <b>5</b> | -            | lementation 41                                                                                                                        |

|          | 5.1          | Environment                                                                                                                           |

|          |              | 5.1.1 Hardware                                                                                                                        |

|          | 50           | 5.1.2 System-on-Chip Implementation                                                                                                   |

|          | 5.2          | Time and Durations                                                                                                                    |

|          |              | 5.2.1 Time format $\dots \dots \dots$ |

|          |              |                                                                                                                                       |

|          | 5.3          | 0                                                                                                                                     |

|          | 0.5          | Network-on-Chip Implementation405.3.1Clock and TimingClock and Timing4'                                                               |

|          |              | 5.3.2 Data Link Layer                                                                                                                 |

|          |              | 5.3.3 Transport Layer                                                                                                                 |

|          |              | $5.3.4$ Pulse Selection $\ldots \ldots 44$ |

|          | 5.4          | Reconfiguration Timing                                                                                                                |

|          | $5.4 \\ 5.5$ | Interfaces                                                                                                                            |

|          | 0.0          | 5.5.1 Overview                                                                                                                        |

|          |              | 5.5.2 Pulsed Data Stream Definition Layout                                                                                            |

|          |              | 5.5.3 Micro Component-to-RMA Interface                                                                                                |

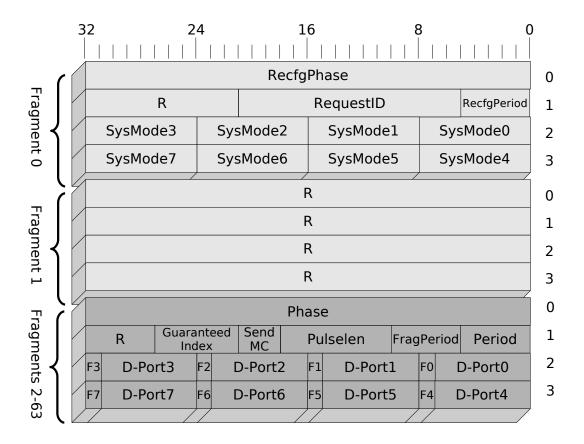

|          |              | 5.5.4 System Mode Information                                                                                                         |

|          |              | 5.5.5 Port Mapping                                                                                                                    |

|          |              | 5.5.6 RMA-to-TNA Interface                                                                                                            |

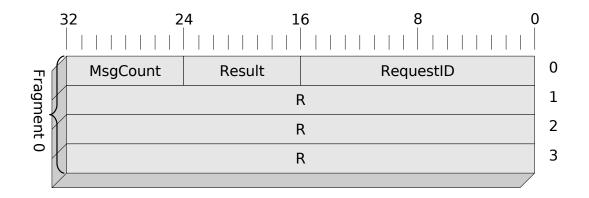

|          |              | 5.5.7 TNA-to-RMA Interface                                                                                                            |

|          |              | 5.5.8 TNA-to-TISS Interface                                                                                                           |

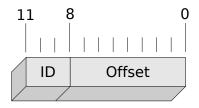

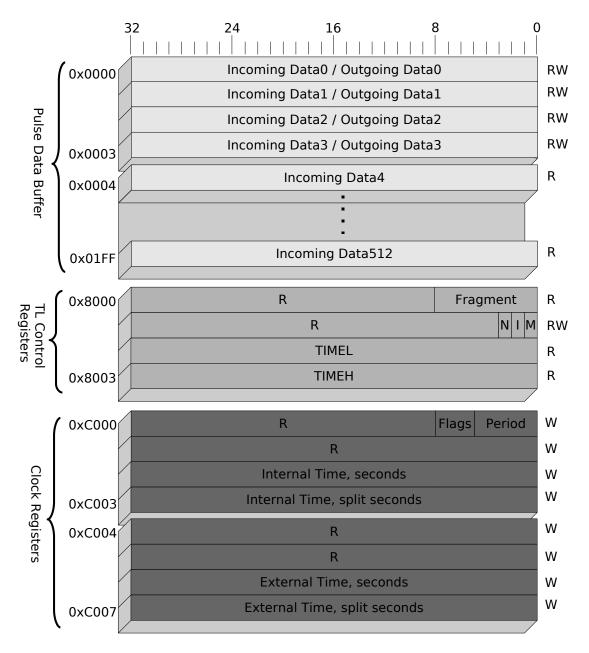

|          |              | 5.5.9 Network-on-Chip Interfaces                                                                                                      |

|          |              | sister freemon on one monitoristicos                                                                                                  |

|              | 5.6            | RMA/    | TNA Implementation     | . 65  |

|--------------|----------------|---------|------------------------|-------|

|              |                | 5.6.1   | Hardware               | . 65  |

|              |                | 5.6.2   | RMA Software           | . 65  |

|              |                | 5.6.3   | TNA Software           |       |

| 6            | Res            | ults    |                        | 79    |

|              | 6.1            | Genera  | al Function            | . 79  |

|              | 6.2            | In-Dep  | oth Tests              | . 81  |

|              |                | 6.2.1   | Fundamental Limits     | . 82  |

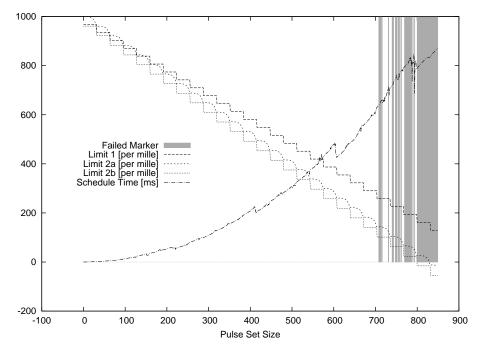

|              |                | 6.2.2   | Test 1: Pulse Set Size | . 84  |

|              |                | 6.2.3   | Test 2: Limit 1        | . 89  |

|              |                | 6.2.4   | Test 3: Limit 2        | . 94  |

|              |                | 6.2.5   | Possible Improvements  | . 98  |

| 7            | Cor            | nclusio | n                      | 99    |

|              | 7.1            | Summ    | ary                    | . 99  |

|              | 7.2            |         | bk                     |       |

| $\mathbf{A}$ | $\mathbf{Ext}$ | ernal I | interfaces             | 103   |

|              | A.1            | TNA-7   | TL Interface           | . 103 |

| В            | Acr            | onyms   | and Abbreviations      | 107   |

| Re           | efere          | nces    |                        | 109   |

# List of Figures

| 2.1<br>2.2<br>2.3                                         | Time-Division Multiple Access                          | 6<br>7<br>7          |

|-----------------------------------------------------------|--------------------------------------------------------|----------------------|

| $3.1 \\ 3.2 \\ 3.3$                                       | A typical micro component                              | 13<br>14<br>17       |

| 4.1<br>4.2<br>4.3                                         | Pulses of the same period and at least one common host | 19<br>25<br>27       |

| $ \begin{array}{r} 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \end{array} $ | Initial tree and slot reservation                      | 28<br>28<br>29<br>29 |

| 4.7<br>4.8<br>4.9<br>4.10                                 | Orthogonal $Pulse \#$                                  | 30<br>31<br>32       |

| 4.12                                                      | Slot allocation and message tree after <i>Pulse</i> 4  | 33<br>34<br>34       |

| $\begin{array}{c} 4.15\\ 4.16\end{array}$                 | Integration of a static pulse with phase offset 8      | 36<br>36<br>38       |

|                                                           | Steps performed during test 4                          | 39<br>40<br>42       |

| $5.2 \\ 5.3 \\ 5.4$                                       | Hardware modules overview                              | 43<br>45<br>46       |

| $5.5 \\ 5.6$                                              | 0                                                      | 49<br>51             |

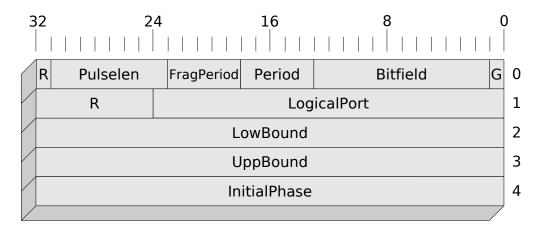

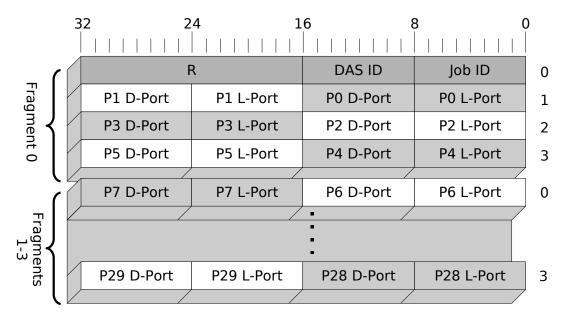

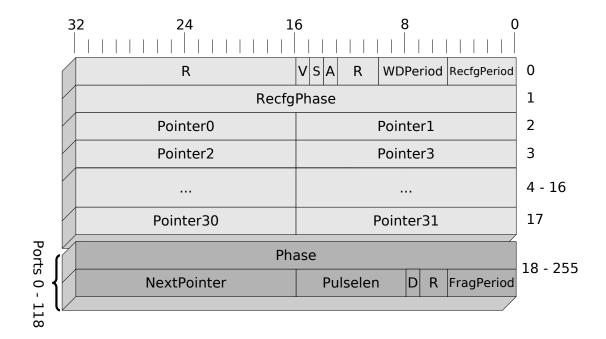

| 5.7                                                                                                                    | Pulsed data stream definition layout                 | 53                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 5.8                                                                                                                    | 0 1                                                  | 53                                                                                                                                 |

| 5.9                                                                                                                    | Micro component-to-RMA interface                     | 55                                                                                                                                 |

| 5.10                                                                                                                   | J                                                    | 56                                                                                                                                 |

| 5.11                                                                                                                   | 11 0                                                 | 57                                                                                                                                 |

| 5.12                                                                                                                   |                                                      | 60                                                                                                                                 |

| 5.13                                                                                                                   | TNA-to-RMA interface                                 | 61                                                                                                                                 |

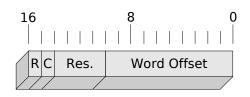

| 5.14                                                                                                                   | TISS address                                         | 61                                                                                                                                 |

| 5.15                                                                                                                   | TNA-to-TISS interface                                | 63                                                                                                                                 |

| 5.16                                                                                                                   | NoC interfaces                                       | 65                                                                                                                                 |

| 5.17                                                                                                                   | RMA program flow                                     | 66                                                                                                                                 |

| 5.18                                                                                                                   | Child relationships                                  | 69                                                                                                                                 |

|                                                                                                                        |                                                      | 73                                                                                                                                 |

| 5.20                                                                                                                   | nextPulse is enveloped by an already scheduled pulse | 73                                                                                                                                 |

| 5.21                                                                                                                   | Trap when checking the "Same Period Constraint"      | 73                                                                                                                                 |

| 5.22                                                                                                                   | TNA program flow                                     | 75                                                                                                                                 |

| 5.23                                                                                                                   | Data structure for pulsed data streams in the TNA    | 76                                                                                                                                 |

|                                                                                                                        |                                                      |                                                                                                                                    |

| 6.1                                                                                                                    | Test application overview                            | 80                                                                                                                                 |

| $6.1 \\ 6.2$                                                                                                           | 11                                                   | 80<br>83                                                                                                                           |

|                                                                                                                        | Arrangements of pulses within a period               |                                                                                                                                    |

| 6.2                                                                                                                    | Arrangements of pulses within a period               | 83                                                                                                                                 |

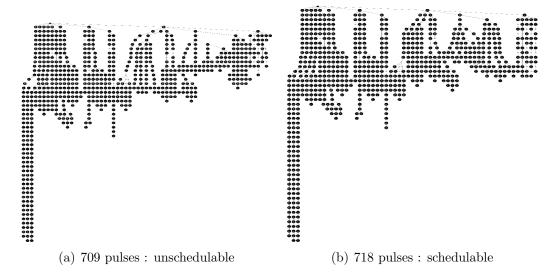

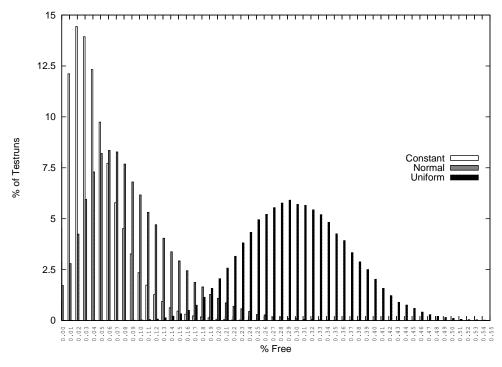

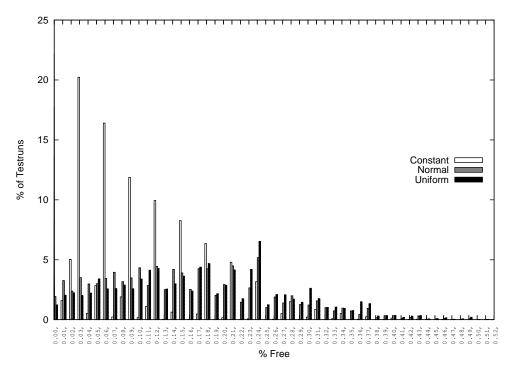

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$                                                                              | Arrangements of pulses within a period               | 83<br>86                                                                                                                           |

| $6.2 \\ 6.3 \\ 6.4$                                                                                                    | Arrangements of pulses within a period               | 83<br>86<br>86                                                                                                                     |

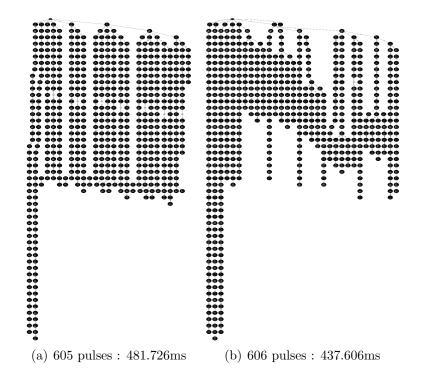

| $6.2 \\ 6.3 \\ 6.4 \\ 6.5$                                                                                             | Arrangements of pulses within a period               | 83<br>86<br>86<br>87                                                                                                               |

| $6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6$                                                                                      | Arrangements of pulses within a period               | 83<br>86<br>86<br>87<br>88                                                                                                         |

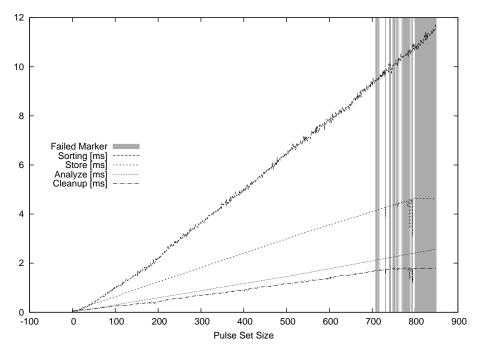

| $     \begin{array}{r}       6.2 \\       6.3 \\       6.4 \\       6.5 \\       6.6 \\       6.7 \\     \end{array} $ | Arrangements of pulses within a period               | 83<br>86<br>86<br>87<br>88<br>89                                                                                                   |

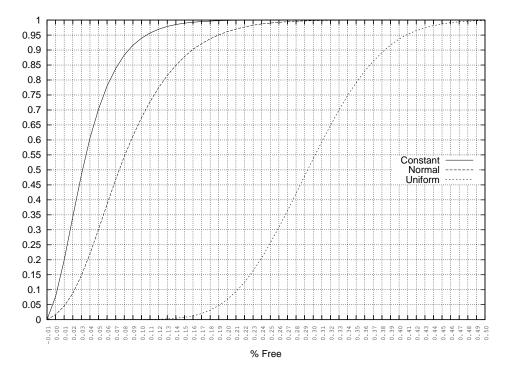

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \end{array}$                                           | Arrangements of pulses within a period               | 83<br>86<br>87<br>88<br>89<br>92                                                                                                   |

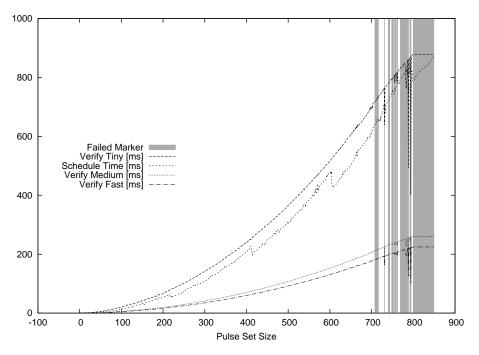

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \end{array}$                            | Arrangements of pulses within a period               | 83<br>86<br>87<br>88<br>89<br>92<br>92                                                                                             |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \end{array}$                    | Arrangements of pulses within a period               | <ul> <li>83</li> <li>86</li> <li>86</li> <li>87</li> <li>88</li> <li>89</li> <li>92</li> <li>92</li> <li>94</li> </ul>             |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \end{array}$            | Arrangements of pulses within a period               | 83<br>86<br>86<br>87<br>88<br>89<br>92<br>92<br>92<br>94<br>95                                                                     |

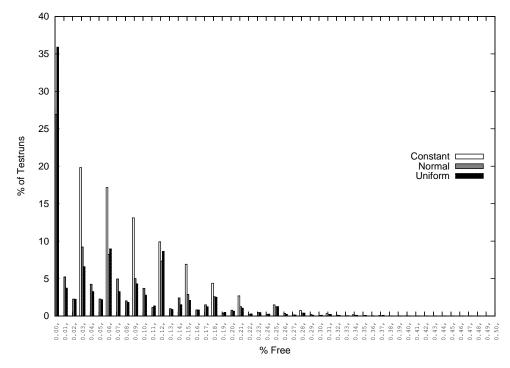

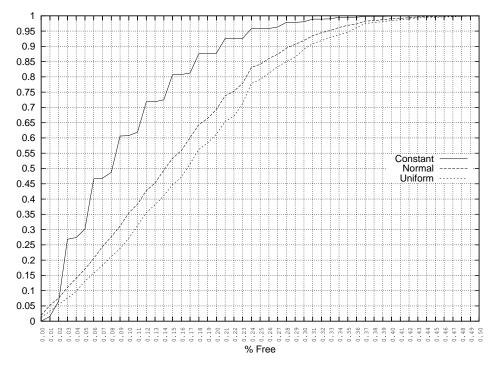

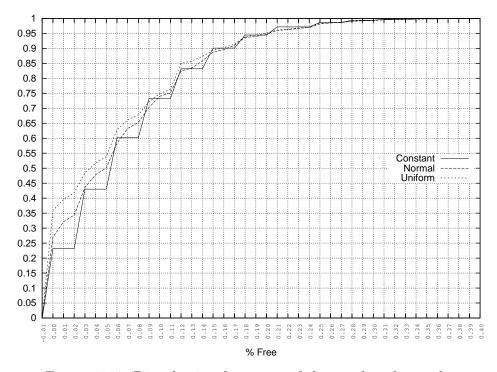

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \end{array}$    | Arrangements of pulses within a period               | <ul> <li>83</li> <li>86</li> <li>87</li> <li>88</li> <li>89</li> <li>92</li> <li>92</li> <li>94</li> <li>95</li> <li>96</li> </ul> |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \end{array}$    | Arrangements of pulses within a period               | 83<br>86<br>87<br>88<br>89<br>92<br>92<br>94<br>95<br>94<br>95<br>96<br>97<br>97                                                   |

# List of Tables

| 4.1  | Pulses to be Scheduled in the Example Execution                        |

|------|------------------------------------------------------------------------|

| 4.2  | Pulses for Demonstrations                                              |

| 5.1  | Stratix II EP2S60 features                                             |

| 5.2  | FPGA resource usage                                                    |

| 5.3  | Theoretical Period Durations                                           |

| 5.4  | Implemented Period Durations                                           |

| 5.5  | Timing of the reconfiguration steps                                    |

| 5.6  | Pulsed data stream definition attributes 54                            |

| 5.7  | Micro Component-to-RMA Interface Attributes 55                         |

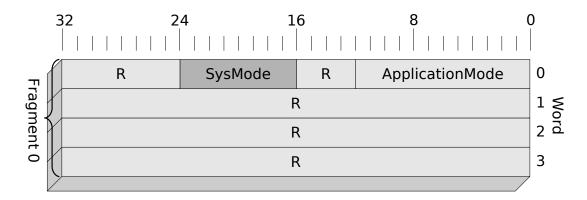

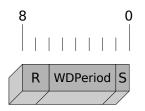

| 5.8  | System Mode Attributes                                                 |

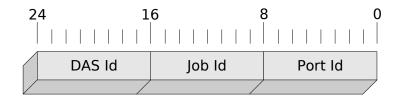

| 5.9  | Port mapping                                                           |

| 5.10 | RMA-to-TNA Interface Attributes                                        |

| 5.11 | TNA-to-RMA interface attributes                                        |

| 5.12 | TNA verification result values                                         |

| 5.13 | TISS address structure                                                 |

| 5.14 | TNA-to-TISS interface attributes                                       |

| 5.15 | RMA / TNA processor properties                                         |

|      | Period values and masks                                                |

| 6.1  | Pulses in the Test Application                                         |

| 6.2  | Execution Times for the Test Application                               |

| 6.3  | Pulses of the Basic Test Set                                           |

| 6.4  | Properties of remarkable Executions                                    |

| 6.5  | Limits Test 1                                                          |

| 6.6  | Parameters for the Normal Distribution used for the Fragment Period 91 |

| 6.7  | Worst case and best case results of test 2                             |

| 6.8  | Results of test 3a                                                     |

| 6.9  | Results of test 3b                                                     |

|      |                                                                        |

# Listings

| 4.1 | Computation of the usage of the pulse periods for use in sorting        | 37 |

|-----|-------------------------------------------------------------------------|----|

| 5.1 | Enumeration of Child-"Phases" and Invocation of the Schedule Pro-       |    |

|     | cedure                                                                  | 72 |

| 5.2 | Test for common host of two pulses                                      | 77 |

| 5.3 | Test for pulse interleaving                                             | 77 |

| 5.4 | Test for fitting of a pulse fits between two fragments of another pulse | 78 |

| 5.5 | Test for pulse overlapping                                              | 78 |

## Chapter 1

## Introduction

## 1.1 Motivation

The advances in chip manufacturing technology have made it possible to integrate a whole full-featured system on a single die. And still, the hardware structures are becoming smaller, allowing to put a great amount of functionality in small chip areas. It has become feasible to build multiple distributed application subsystems on a single chip. The advantages are promising: cost savings due to reduction of the number of hardware parts and increased reliability since on-chip interconnects are less susceptible to physical stress than connections on the PCB. Furthermore, a performance gain can be expected as data exchange can be done more efficiently and finally, power dissipation is cut when using a single chip.

However, the possibilities offered by this evolution are countered by challenges to the development of such highly integrated systems. The complexity of these systems becomes insurmountable if proper measures are not taken. Development gets error-prone as there are too many issues to be addressed at the same time. The most important technique to cope with this complexity is abstraction. By relying on well specified interfaces, the main focus can be put on the actual application development. In System-on-Chips (SoCs), the interconnect between different components is becoming more and more difficult to handle since the signal delay of on-chip wires is no more negligible with current technology. This complexity can be hidden from application developers using a Network-on-Chip (NoC) infrastructure to connect all components of the system. The challenge here is to design an efficient, yet flexible network with small overhead so that the cost does not outweigh the benefits. This issue is addressed by many research projects by now and appropriate solutions have been found already. However, hardly any of the solutions can be used in the context of safety-critical real-time application, which are very demanding in terms of reliability and need the provision of guarantees on communication properties.

The result is that the System-on-Chip solutions cannot be exploited by safetycritical real-time applications. For example, an electronic system in a car may be built of one application subsystem for electronic stability control, another for a multimedia system and a third for motor control. The classical approach is to form three distinct systems that share nothing except the battery as the common power source. With three systems this is not a big issue, but nowadays cars feature many more application subsystems than those mentioned already. Each system must be provided with the resources it needs during peak load. If the systems are combined on the same chip, resources can be shared and less resources are required in total if two systems never run at peak load at the same time. Often, the risk that one application subsystem has adverse effects on the execution of another is too big if they were put on the same chip if they are not properly separated. Thus, safety-critical real-time applications are mostly excluded from the benefits of SoC solutions.

## **1.2** Contribution

The context for the findings presented in this thesis is how safety-critical real-time systems can make use of chip technology and profit from SoC architectures.

For this, the Time-Triggered System-on-Chip (TT-SoC) architecture, an architecture designed for real-time safety-critical applications, is used as a basis for the design. Primary focus in this thesis is the dynamic resource management scheme that enables efficient use and sharing of resources in the SoC. It is explained how dynamic resource management can be realized even in the co-existence of application subsystems of different degree of criticality. In other words how it can be prevented that an application subsystem can negatively influence another application subsystem on the same SoC, sharing the same resources.

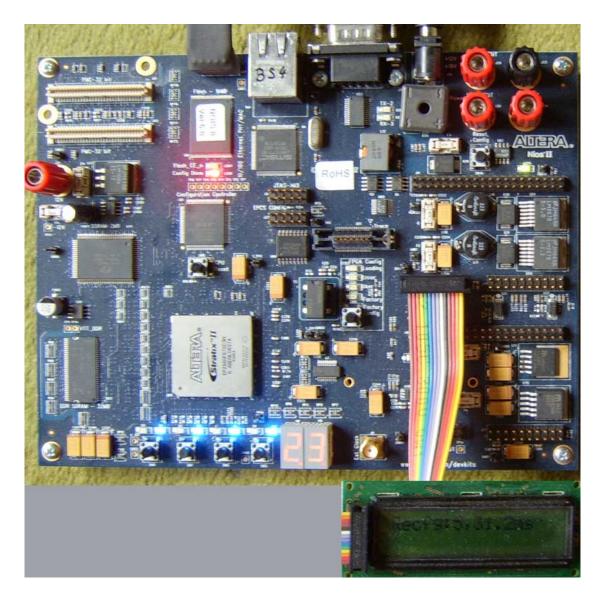

To prove the utility of the proposed architecture, the SoC design is then implemented on a Field-Programmable Gate-Array (FPGA) and the performance and behavior of the resource management facilities is evaluated.

### **1.3** Structure of this Thesis

The remainder of the thesis is organized as follows. Chapter 2 introduces the concepts on which the work is based and presents related work. In Chapter 3, the TT-SoC architecture, on which the System-on-Chip (SoC) designed in this thesis is based, is explained. The refined design of the SoC, for which resource management is implemented, is detailed in Chapter 4. Furthermore, the mechanisms working

together to make dynamic resource management possible are explained. Chapter 5 goes into the details of how the design was implemented and thoroughly describes the interfaces between the components. How the design was evaluated along with the results obtained can be found in Chapter 6. And, finally, Chapter 7 closes with the conclusions drawn from the work and what is left to do in future projects.

## Chapter 2

## **Basic Terms and Concepts**

## 2.1 Real-Time Systems

Real-time systems differ from conventional computer systems by having to provide results which must not only be correct in the value domain, but also have to arrive within a specified time interval (deadline). A system is called a hard real-time system if a violation of the deadline renders the result useless. In some systems this may lead to a system failure. If deadlines in a soft real-time system are missed, the quality of service is degraded (e.g. a frame is dropped). While usual systems try to optimize the average case, hard real-time systems focus on the worst case, since the timing requirements must be met in every single case. An exhaustive overview on the topic of real-time systems is available in [Kop97].

Real-time requirements do not only have an impact on the algorithms used in computations, but equally on the communication mechanisms. Especially the Medium Access Control (MAC) schemes must be devised carefully. For example, Carrier Sense Multiple Access (CSMA), which is used in Ethernet, cannot be used in realtime application without adding a flow-control mechanisms to an upper network layer. Using plain CSMA, it cannot be guaranteed that any packet arrives in time during high-load situations if access to the network is not coordinated. However, Kopetz et al. [KAGS05] have developed a variant of Ethernet called Time-Triggered Ethernet that guarantees collision free access to the Ethernet medium by synchronizing and coordinating the network nodes.

For the system described in this thesis, the Time-Division Multiple Access (TDMA) access scheme is used that works very well for real-time systems. It is explained in the next section.

#### 2.1.1 TDMA

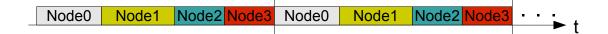

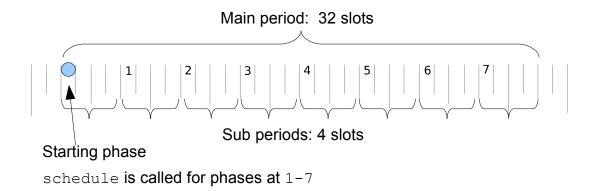

Figure 2.1: Time-Division Multiple Access (TDMA)

In TDMA, all network nodes are assigned a certain time interval where they are allowed to transmit data over the network. Each time interval is repeated periodically (cf. Figure 2.1). Obviously, these assignments must be exclusive so that in no case two nodes are ever sending simultaneously.

The big advantage of TDMA is that every node can rely on the network being available during its time share which is crucial for real-time applications. The drawback of TDMA is, that the network is much less flexible. If additional nodes are connected they must be assigned a time share before they can send messages. Furthermore, all nodes must be synchronized to a global time base for obvious reasons.

### 2.2 Pulsed Data Streams

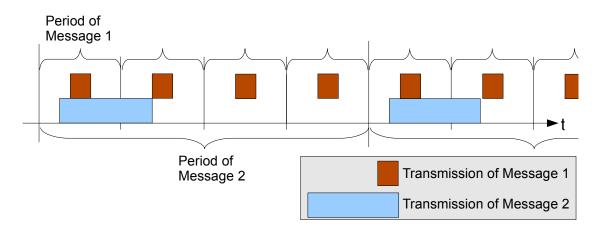

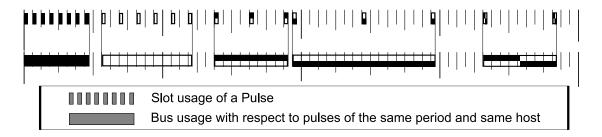

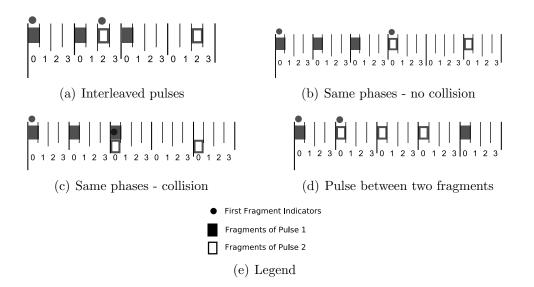

Pulsed data streams are a novel communication primitive proposed by Kopetz in [Kop06]. They were developed for TDMA networks to allow the coexistence of messages with short periods and messages with long periods. The problem with messages with long periods is that their duration may be long, thus they block the communication medium for too long a time so that messages with short periods are no more possible as illustrated in Figure 2.2.

The solution to this is simple but effective: divide message "2" into multiple parts and send the individual parts over a longer time interval leaving gaps of inactivity between the parts. The parts are called "Fragments". Similarly, divide message "1" so that it fits between the Fragments of message "2" (see Figure 2.3). These fragmented messages are called "pulsed data streams".

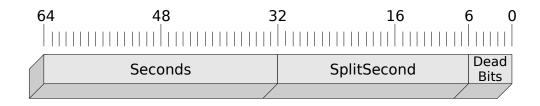

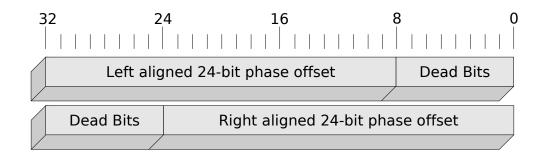

Summing up the above, a pulsed data stream is a periodic message that is split up into individual fragments. The size of a fragment is determined by the underlying communication system. The length of the Pulse period is a non-positive power of 2 seconds to reduce the complexity of the communication system. The distance between two neighboring fragments is determined by the Fragment Period of a pulse, which must be a non-positive power of 2 seconds as well. The four parameters that define a pulsed data stream are the Pulse Period, the Fragment Period, the Number of Fragments and the Phase Offset (cf. Figure 2.3).

Figure 2.2: Problems of mixing long and short periods

Figure 2.3: Spreading messages to pulsed data streams

Pulsed data streams follow the time-triggered paradigm which states that actions (e.g. transmission of packets) are triggered at predefined time instants. This allows very low latencies in a variety of applications, since the sending instants are defined a priori. For example, consider a control application where a sensor must be read, its data has to be sent to the control unit, which calculates the control values. The control values are then sent to the actuators to be applied. Proper alignment of both pulsed data streams makes it possible to generate a seamless flow of actions, which is not possible in event-triggered networks where transmission latencies depend on the network load.

## 2.3 System-on-Chip (SoC)

"The definition of an SoC is simply a chip where an entire system is designed into a single ASIC" (taken from Siewert [Sie06]). In the past, it was not possible to put all components that comprise a computer system on a single chip. So every component resided in its own chip, connected to the others via the connections on the Printed Circuit Board (PCB). In the 1970s and 1980s, attempts were made to build integrated circuit networks that use an entire silicon wafer to host a collection of components, but these were thwart by manufacturing complexities. Since the 1990s, as technology evolved, SoC architectures are used in a number of applications. They have numerous advantages. One of which is reduced cost compared to multiple chips since only one chip must be packaged, tested and mounted to the PCB. Second, the interconnection of components within a chip is more efficient in terms of power consumption, cost and throughput. Third, modular design of the SoC is achieved using Intellectual Property (IP)-Cores. An IP-Core is a hardware description of a component that can be integrated into the chip. IP-Cores from different vendors may co-exists on the SoC. Disadvantages of the SoC is an additional complexity in the system design and that a single chip corresponds to a single fault containment region. In other words, the reliability required for safetycritical applications cannot be achieved by having three instances of a component in the same SoC for use with Triple Modular Redundancy (TMR).

#### 2.3.1 NoC

In [LG02], Benini pointed out that for a sound SoC design, the system should be seen as a "micro-network of components". This on-chip network is called the NoC. With the advance of manufacturing technology the timing of on-chip wiring becomes more and more complex. With an NoC the complexities can be hidden from the cores in an elegant way. In [JT03], Jantsch comes to the same conclusion, that NoC are needed to "keep up with the pace of technology advances".

## 2.4 Message Scheduling Techniques

As already mentioned in Section 2.1, communication in real-time systems must be coordinated in order to be able to guarantee worst case end-to-end delays and to guarantee an upper bound on the jitter. This coordination is achieved basically by telling each network node at which instants in time they are allowed to send. Scheduling is the process to find correct values for the sending instants. However, it is not always trivial to find valid values for the sending instants. Messages may depend on others, have strict timing requirements or have to co-exist with message of different period lengths. A general overview on scheduling in distributed embedded systems can be found in [Kop97]. The terms relevant in the context of this thesis are explained below.

#### 2.4.1 Online vs. Offline Scheduling

Since scheduling can be such a resource demanding task, it is often done during the design phase of the system. Then it is called *Offline Scheduling*. If communication demands can change during run-time of the system, all possible cases must be scheduled and stored in different configurations. Thus, the system can adapt online, even if it is not capable to do the scheduling itself.

The alternative to Offline Scheduling is Online Scheduling. In this case the scheduling is performed during run-time according to requests of the network nodes. The main advantage of Online Scheduling over Offline Scheduling is that it is much more flexible. The message schedule is not limited to a certain set of pre-generated schedules, but may attain any possible configuration. However, this brings in a disadvantage. There may be situations where the scheduling fails which could compromise system stability if not handled properly. Another disadvantage is that Online Scheduling requires processing power in the running system. Since computational resources in typical embedded systems are scarce this implies that most Online Scheduling algorithms are non-optimal. A non-optimal scheduler is a scheduler that may fail to find a solution even if a solution exists. Most online schedulers use heuristics for finding solutions which can fail in unusual cases. However, online schedulers do not require memory for storing the pre-generated schedules.

### 2.4.2 Basic Techniques

#### **Full Enumeration**

Full Enumeration is a simple concept: try out all possible values until a valid solution is found. It is easy to implement, but in general it has an exponential time complexity. Therefore, it is hardly suitable for *Online Scheduling*. Often, it is even impossible for *Offline Scheduling*, because the number of items to check for a solution is too large.

#### Branch and Bound

Branch and Bound is a technique invented for solving optimization problems. It uses the two tools *Branch* and *Bound* to explore the problem space more efficiently than plain *Full Enumeration*. Assuming that function  $f(\ldots)$  is to be minimized, it starts with the set of solution candidates. Then, using *Branch* the set is divided to subsets ("Branches") to which tighter constraints apply. Based on these constraints the bounds for function  $f(\ldots)$  in all branches are evaluated in the *Bound* step. Branches with a lower bound that lies above the upper bound of

any other branch obviously cannot lead to the minimal solution. Therefore, they are excluded from further investigation. *Branch* and *Bound* are repeated until a solution is found. The topic was covered comprehensively by Clausen in [Cla99].

An example of how Branch and Bound can be used effectively for combined task and message scheduling is given by Abdelzaher and Shin in [DS94].

## 2.5 Related Work

As it is generally accepted that NoCs are a promising approach to counter the complexity of highly integrated SoCs, much research is done on the topic.

In addition to working on different topologies and hardware realizations of NoCs, the issue of controlling an NoC by software is addressed. Without software control, resources (i.e. power consumption and network bandwidth) cannot be used efficiently.

In [ANM<sup>+</sup>05], Avasare et al. presented an algorithm that performs flow control on end-to-end channels in best effort NoCs. They propose to install a monitor application on a centralized Operating System (OS) that collects statistics of all NoC nodes. If the network is congested at a node an algorithm is used to lower the message injection rate of affected nodes. When the network load subsides the injection rate is increased again. This mechanism assures that the network can be operated just below saturation, where maximum throughput is achieved. Furthermore, based on this NoC they developed heuristics to make use of hardware that is reconfigurable at run-time which are described in [NMAM05]. The paper addresses the issue of task migration in such systems.

Radulescu et al. have developed a real-time capable, TDMA based NoC called Æthereal, which is reconfigurable at run-time. It is based on end-to-end connections which may be established or released at run-time via a single or multiple configuration ports. The configuration ports are accessed solely through the NoC itself. Active connections have a guaranteed lower bound on throughput and a guaranteed upper bound on latency. A detailed description is given in [RDP+05].

Hansson et al. propose an alternative to global reconfiguration schemes in [HCG07]. They point out that the negative effects of a global reconfiguration can be avoided if partial reconfiguration is done. For this, the system is divided into parts which may be configured individually without disrupting the other parts.

## Chapter 3

# Time-Triggered System-on-a-Chip Architecture

In this chapter the Time-Triggered System-on-Chip (TT-SoC) architecture, for which dynamic resource management is implemented, will be presented.

The goal of this architecture is not primarily to optimize for highest performance of the SoC, but to provide an infrastructure that may host multiple application subsystems with different levels of criticality, where no application subsystem can have a negative effect on another application subsystem even in the presence of implementation faults in one of the application subsystems.

One of the most important requirements is the provision of services for safetycritical real-time applications. The next section presents some key properties of the TT-SoC architecture. Later follows the structure of the TT-SoC architecture and the resource management facilities. The TT-SoC architecture is discussed comprehensively in the PhD theses of Christian El Salloum [Sal08] and Bernhard Huber [Hub08].

## **3.1** Properties / Characteristics

In this section the properties that characterize the TT-SoC architecture and differentiate it from other SoC architectures are listed.

**Real-Time** The support for real-time applications is a key feature of the TT-SoC architecture. It inflicts the requirement that all latencies caused by the TT-SoC are predictable.

**Encapsulation** This is a very powerful property, that distinguishes this particular SoC architecture from many others. Encapsulation means that every component in the TT-SoC is fully independent from the other components from a functional point of view. In other words, a faulty component "F" cannot disturb the correct operation of components that do not depend on the results of component "F". The same is true for communication channels. Thus, encapsulation allows mixture of certified safety-critical application subsystems and untrusted application subsystems that provide additional non-critical services, without having adverse effects on the safety-critical one. Another benefit of encapsulation is that failures can be tracked down to the responsible component more easily. Furthermore it enforces composability. In short, a system features composability, if different modules may be developed independently and if the integration of further components does not affect the correct functioning of the other components in any way.

Encapsulation is achieved by the introduction of a trusted region, which components are certified to the highest required level of criticality. All configuration data relevant for the TT-SoC architectural elements which enters the trusted region is validated by trusted components to guarantee system integrity.

Support for Resource Efficiency In embedded systems resources may be scarce and must be used efficiently. Especially the power dissipation should be minimized as embedded devices are often battery powered. Resource efficiency must be reflected in the system design. The system has to be capable to adapt dynamically to changing resource demands during run-time. Examples for this are frequency scaling or complete shutdown of unneeded components, and avoidance of redundant transmissions. However, measures taken to improve the resource efficiency must not compromise the other properties of the system. Thus, 100% reliable resource management facilities are to be used.

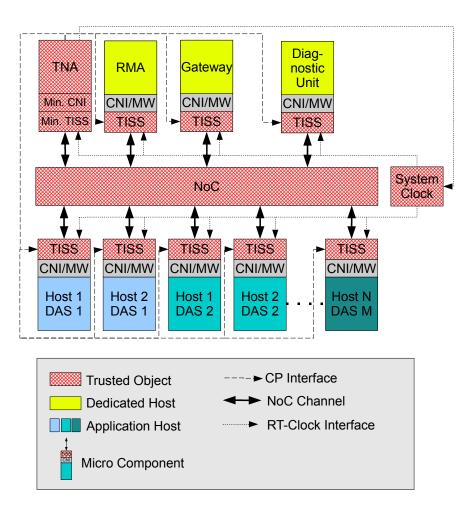

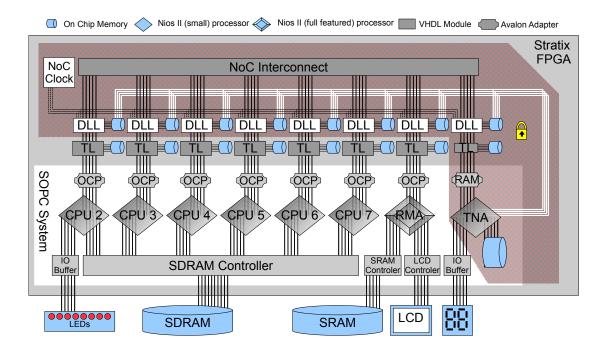

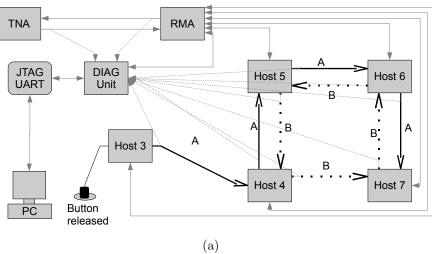

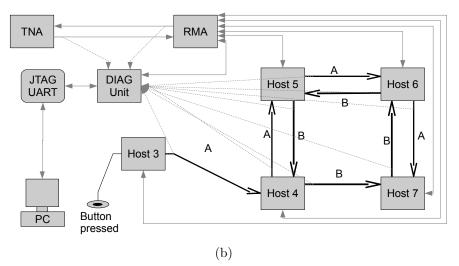

### 3.2 Structure

The structure of the TT-SoC is depicted in Figure 3.1. The central element is the NoC which connects all micro components. For the NoC, the micro components can be considered as clients using the network service. From the point of view of the NoC there is no difference between the individual micro components. The interface to the NoC is identical for all micro components.

The TT-SoC architecture, however, distinguishes between micro components dedicated to TT-SoC services on the one hand and micro components that implement the application on the other hand. The dedicated micro components are

Figure 3.1: TT-SoC components overview

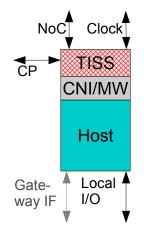

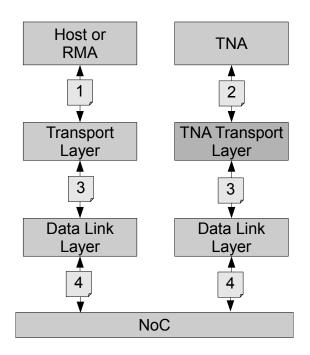

shown in the upper half in Figure 3.1. They comprise the Trusted Network Authority (TNA), the Resource Management Authority (RMA), the Diagnostic Unit (DU) and the Gateway. They are introduced in the sections after the micro component description. A typical micro component (as shown in Figure 3.2) is built up of three parts : the Trusted Interface Subsystem (TISS), the Communication Network Interface (CNI)/Middleware Layer and the host. They are discussed below.

#### 3.2.1 Trusted Interface Subsystem (TISS)

The TISS is the access point of the micro components to the NoC. It has to ensure that the hosts can access the NoC exclusively during the time-slots allocated for them. Neither sending nor receiving may be permitted in all other

Figure 3.2: A typical micro component

time-slots. Thus, a faulty host cannot interfere with the communication of probably safety critical jobs. Furthermore, if an intruder is able to break into an unsafe micro component, he cannot eavesdrop the exchange of sensitive data between safe micro components. The active time-slots for each TISS must be configured via the Configuration and Planning (CP)-Interface of the TISS. Obviously, only a trusted component is entitled to fulfill this task. The TISS has an interface to access the Global Time Base which is compared against the preconfigured timeslots to determine the active time-slots. Since the global time is of interest to the CNI/Middleware Layer and the host, the TISS forwards the current time to the CNI/Middleware Layer.

#### 3.2.2 CNI/Middleware Layer

The CNI/Middleware Layer provides higher level access to the NoC. Since the TISS must be trusted it has to be certified to the highest criticality level of any host in the SoC. To ease certification it is stripped down to a minimum of functionality. This lack of functions is filled by the CNI/Middleware Layer, so that access to the NoC is eased for the hosts. Depending on the host, there may be different versions of the CNI/Middleware Layer. For example, the TNA, which has to be certified as well, does not need a CNI/Middleware Layer with a rich feature set, so a minimal version suffices.

### 3.2.3 Host

The hosts perform the computational tasks. A host can be a processor within the SoC, an external processor or any logic circuit that can make use of the NoC. In

most cases, a host has an I/O interface to read sensor values, drive actuators or has an additional network or bus interface to connect to the outside world. However, hosts without further interfaces that are used solely for performing computational operations may be useful in some applications as well.

#### 3.2.4 Dedicated Hosts

Dynamic resource management is accomplished mainly by the cooperation of two dedicated micro components, the Resource Management Authority (RMA) and the Trusted Network Authority (TNA). Their role is described in the following sections. Thereafter, the components Diagnostic Unit (DU) and Gateway are presented which offer additional services to the TT-SoC application subsystems.

#### **Resource Management Authority (RMA)**

The RMA is the core of the dynamic resource management. It receives resource requests from other hosts via the NoC and calculates the resource allocation for the whole SoC. As the algorithms that perform this task can get very complex, it may not be reasonable to certify the RMA, thus it cannot be guaranteed to be free of design faults. Therefore, the results must be checked for validity and for syntactical correctness. A separate micro component, the TNA, is entitled to perform this delicate task. Thus, the resource allocation computed by the RMA is sent to the TNA again via the NoC. In fact, the RMA does not need an interface other than to the NoC.

The three principal resources to be managed by the RMA are: computational resources, communication resources and power. Computational resources include I/O allocation and memory allocation. The management of communication resources consists of creating a conflict-free message schedule that complies with the requirements (bandwidth, latency and phase alignments) of all micro components in the system. Finally, power management may lower clock frequencies and/or lower core voltages to reduce power dissipation significantly, when performance is not critical. The RMA may even completely disable a micro component, in which case it must be reactivated by another micro component of the same Distributed Application Subsystem (DAS).

#### Trusted Network Authority (TNA)

The TNA realizes together with the NoC and the TISSs the trusted part of the resource management. It has to ensure that no invalid resource allocation may ever be activated during system uptime. For this, it has to verify that the resource allocation received from the RMA does not violate any requirements of the system. First, collisions must not exist. For example, a sending slot may not be assigned to two different hosts. And, second, all resources needed by safety-critical application subsystems or dedicated architectural elements of the TT-SoC architecture (e.g. RMA, TNA) must be provided.

If these tests are passed, the TNA is also responsible for the establishment of the resource allocation. This is done via a separate dedicated channel to the CP-interfaces of the TISSs.

The second task of the TNA is to enable clock synchronization. The ability of the TT-SoC to synchronize to the clock of another system (which is not necessarily an SoC) allows to form clusters of systems. Since the global time-base is of integral importance to a time-triggered system as the TT-SoC, a trusted component has to perform external clock synchronization. The clocks is adjusted using rate correction to avoid discontinuities in time.

#### Diagnostic Unit (DU)

The DU collects status and diagnosis information from different parts of the TT-SoC. In particular, abnormal operation is recorded to locate the source of faults. All structural elements of the SoC (TNA,RMA,TISSs, hosts) can report such issues. For example, the TNA reports if the verification of the resource allocation fails. The TISSs report when a hosts violates its timing specifications (e.g. queue overflow, invalid time-slot).

#### Gateway

A Gateway host allows to connect the TT-SoC to other networks. In principal any network may be connected to the SoC via a gateway, but if inter-network real-time communication channels are needed, time-triggered protocols ease the interconnect and make it possible to use a minimum of buffers. Examples are TTP or Time-Triggered Ethernet. Furthermore, Gateway hosts enable interconnection of multiple TT-SoCs to form a cluster. This is necessary to construct ultra-dependable systems, which cannot be realized with only a single chip because of the relatively high soft error rate of deep submicron devices. In [Con02], Constantinescu analyzes the dependability of devices of this technology.

## 3.3 Network-on-Chip

The NoC provides the communication channels between the micro components. Although in an SoC it is easily possible to establish links between two micro components outside the NoC, doing so results in loosing all benefits provided by the NoC.

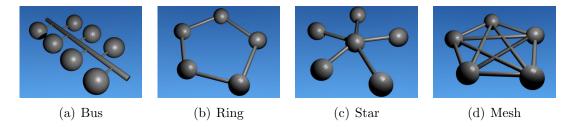

The structure of the NoC is not restricted to a particular topology. Some commonly used topologies are shown in Figure 3.3.

Figure 3.3: Commonly used network topologies

In conventional cabled networks mesh-like topologies (Figure 3.3(d)) are not always practicable. In an SoC "wires" are relatively cheap so mesh structures, which offer the highest throughput, can be realized more easily and therefore are a promising topology for NoCs.

Medium Access Control (MAC) The NoC must be real-time capable as all components of the TT-SoC. Therefore, TDMA (see Section 2.1.1), which guarantees collision-free operation, is used for all interactions with the NoC.

**Communication Primitives** All communication on the NoC is done using "pulsed data streams" (see Section 2.2). Pulsed data streams group multiple TDMA timeslots, called fragments, to a single message so they need not be allocated individually. The fragments are spread in such a way that long messages do not inhibit messages of very short periods.

**Ports** The access to the NoC from higher network layers is done via Ports. There are two different kinds of ports: Data-Link Ports (D-Ports) and Logical Ports (L-Ports). D-Ports are comparable to the ports in IP-based networks. An NoC interface has a number of D-Ports that may be assigned to individual communication channels and form the physical interface to the NoC. There may be some special ports with fixed numbers (e.g. port 0 for diagnostic data) but otherwise the assignment of port numbers to channels is arbitrary and should not be of interest to the application that is actually using the port. Applications operate on the higher level L-Ports. An L-Port identifies the semantics of the data on the channel. For instance the temperature reading of a sensor, a voltage level or the left channel of an audio stream. If an L-Port is activated, the RMA assigns

a currently unused D-Port which is then used for the transmission of the data identified by the L-Port. The advantage of this separation is that the software is independent from the low-level D-Ports. If the configuration changes, the D-Port numbers may change but the L-Port remain the same. Thus, even the relocation of the source of a channel is transparent to the receivers.

# Chapter 4

# Design of the Resource Management Solution

In this chapter the design of the SoC with dynamic resource management is presented. Also the resource allocation procedure and the algorithms used in the realization are explained.

# 4.1 Resource Management Cycle

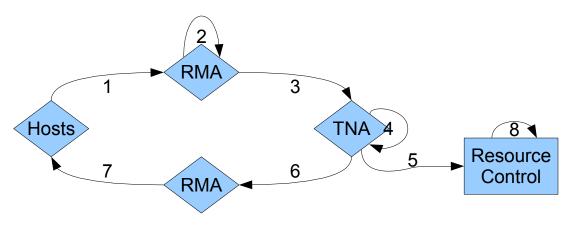

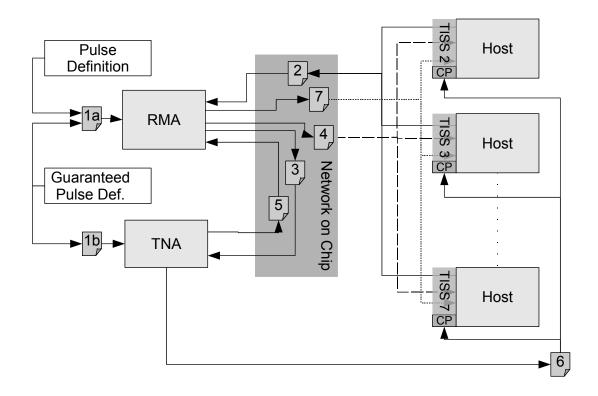

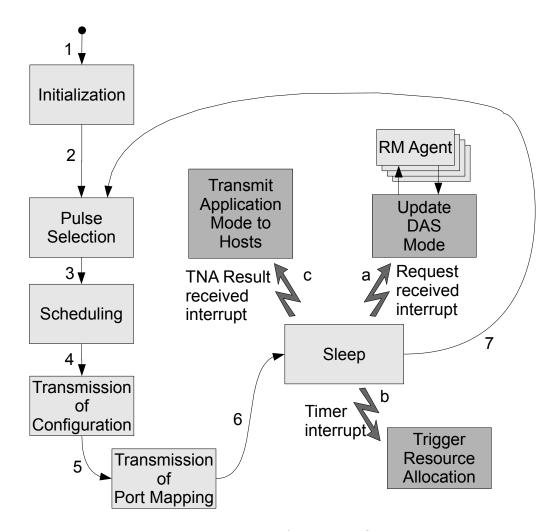

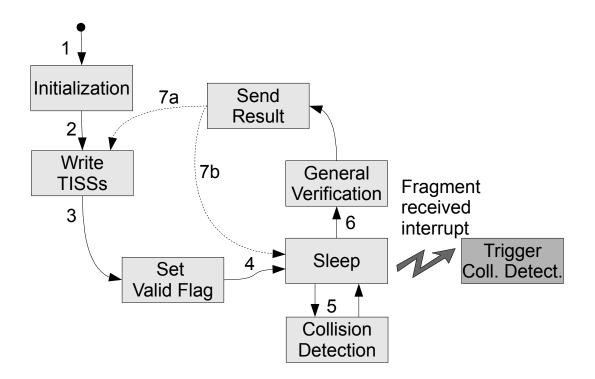

The resource management is a permanently active periodic process. Its course of actions is depicted in Figure 4.1. In [Hub08], this resource management cycle is motivated.

Figure 4.1: The resource management cycle

All of the micro components that dynamically allocate resources take part in the process. The other micro components may have static allocations that are always

active, or have their allocations done by another micro component of the same application subsystem.

After the completion of all eight steps a new resource allocation becomes activated. The period length of the process called reconfiguration period is a system parameter defined at system design time. It depends on the dynamics of the application and the performance of the RMA and the TNA. Furthermore, very short cycles result in a considerable "non-productive" network load, since resource management messages must be exchanged at very short intervals.

Since the TT-SoC is a time-triggered architecture for real-time systems, the send and receive instants of all messages are defined a priori. Therefore, the beginning of all steps has a fixed offset within the period, which dictates the maximum duration for all steps. Similar to the period length the instants are system parameters chosen during system design.

In the following, the steps depicted in Figure 4.1 are explained.

$1^{st}$  step: hosts request Resources In the first step, the hosts have to specify the resources they currently need. Since they are not in the position to allocate or deallocate resources themselves, they send a request to the RMA.

$2^{nd}$  step: RMA computes resource allocation In the second step, after the receive instant of the last resource request, the RMA calculates the new resource allocation based on the recently received requests. At that time no more resource requests can be issued for the current cycle.

$3^{rd}$  step: RMA transmits the resource allocation The third step consists of sending the resource allocation to the TNA in order to have it verified and applied.

$4^{th}$  step: TNA verifies the resource allocation The correctness of the results of the RMA are verified in the fourth step to make sure that no conflicts exist and that resources for critical components are allocated.

$5^{th}$  step: TNA writes the configuration If the configuration proves to be correct, it is written to the configuration registers of the TISSs in step five.

$6^{th}$  step: TNA reports verification result The RMA needs to know whether the allocation was correct to react on errors and to notify the hosts. The RMA may try a different allocation algorithm on a verification failure or at least output diagnostic information.

$7^{th}$  step: RMA notifies hosts The hosts must be informed if their requests could be satisfied. Since there is no communication channel between the TNA and the hosts, the RMA has to notify the hosts based on the verification result from the TNA. Furthermore, it is possible that a host's resources were altered by a request from another host. In short, this step assures that every host in the system is aware of the resources it will be assigned to after the oncoming reconfiguration.

$8^{th}$  step: Activation of the new configuration To avoid inconsistent intermediate configurations, the whole new allocation is activated at a predefined instant for all components.

# 4.2 Resource Management Authority (RMA)

The RMA implements the actual dynamic resource management. It is equipped with possibly a number of algorithms that are able to distribute the available resources to the hosts according to the resources they requested.

#### Tasks

**Process Requests** It is unpractical to realize the resource requests issued by the hosts as complete descriptions of all required resources since that would be a waste of network bandwidth. Therefore, a table of application modes, where each table entry describes the resources needed in this mode is employed. Thus, before the allocation computations can even start, the requests must be translated to detailed resource requirements.

**Compute Resource Allocation** After the processing, the resources can actually be assigned to the hosts.

**Provision of Resource Usage Information** It is not sufficient to inform the hosts if their request was successful. The knowledge how to access the resources must be included. In the implementation presented in this thesis, the hosts need to know the network ports for requested messages in order to use the network.

#### Interfaces

$Hosts \Rightarrow RMA$  Used to request or relinquish resources

$\mathbf{RMA} \Rightarrow \mathbf{TNA}$  Used to transmit the resource allocation to be verified and applied.

$TNA \Rightarrow RMA$  Used to receive the status of the verification.

$\mathbf{RMA} \Rightarrow \mathbf{Hosts}$  Used to inform the hosts which resources they were assigned to and how to access them.

# 4.3 Trusted Network Authority (TNA)

The TNA implements the guard function to assure that no corrupted resource allocation may enter the system. This makes it possible to use dynamic resource management even in systems of applications of mixed criticality. Without the TNA, there would be the risk that a fault in the resource allocation algorithm could lead to a resource shortage in crucial components leading to catastrophic failures. Through the TNA such a scenario is made impossible as the TNA maintains a list of guaranteed resources. The TNA checks that these resources are assigned in all allocations and hinders the activation of the allocation if the check fails.

#### Tasks

**Detect Resource Conflicts** Verify that no resource allocations conflict with each other.

**Detect Missing Allocations** Verify that all guaranteed resources are provided.

**Apply Resource Allocation** Write the configuration registers to effectuate the assignment of the resources to the hosts.

#### Interfaces

$\mathbf{RMA} \Rightarrow \mathbf{TNA}$  Used to receive the proposed resource allocation.

$\mathbf{TNA} \Rightarrow \mathbf{RMA}$  Used to return the verification result.

$TNA \Rightarrow TISS CP$  Used to write the resource configuration.

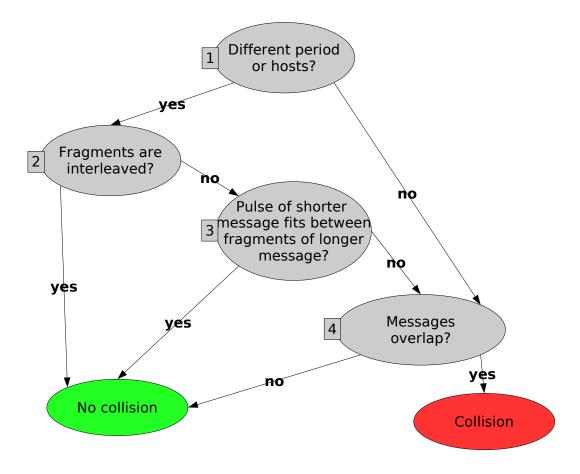

# 4.4 Scheduling Constraints

In addition to the apparent requirement that any two fragments must not be scheduled at the same phase the hardware implementation imposes three constraints.

- 1. The distance between two fragments must not be smaller than one bus clock tick (macrotick).

- 2. The distance between two fragments concerning the same host (but from different pulses) must not be smaller than MAX\_EVENT\_RATE. That is the time the hosts takes to switch between two pulses.

- 3. "Same Period Constraint": For each period a host can only process one pulse at a time (refer to Section 5.3.2 for details). This means that pulses of the same period that require attention from at least one common host may not be interleaved (i.e. fragments of one pulse cannot be placed between two fragments of the other pulse).

# 4.5 Scheduler for Pulsed Data Streams

Message scheduling is generally a non-trivial problem. However, with pulsed data streams the problem space becomes much larger because messages are allowed to overlap. Furthermore, while searching for a solution Constraint 3 must be satisfied and restrictions on the placement of messages defined by the system designer must be respected. This makes scheduling a very complex task. The proposed algorithm was designed to run on-chip under tight timing constraints. It cannot be expected that it is able to solve all possible scheduling problems. Nevertheless, it performs well for situations where the bus is operated well below full load.

## 4.5.1 Inputs

The input for the scheduling algorithm is a list of pulsed data stream definitions. Each pulse definition contains the following parameters:

**Logical Port ID** used to identify the pulse (irrelevant for scheduling, but must be kept for later usage).

**Pulse Period** determines the frequency of the pulse.

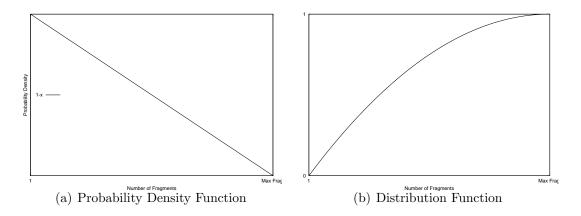

**Fragment Period** determines the distance between two neighboring fragments. To keep the scheduling effort manageable this value must

be specified. Alternative, possibly offline, scheduling algorithms might be able to select the fragment period dynamically since in many applications the actual fragment period is of little importance as long as the desired number of fragments is delivered within the pulse period.

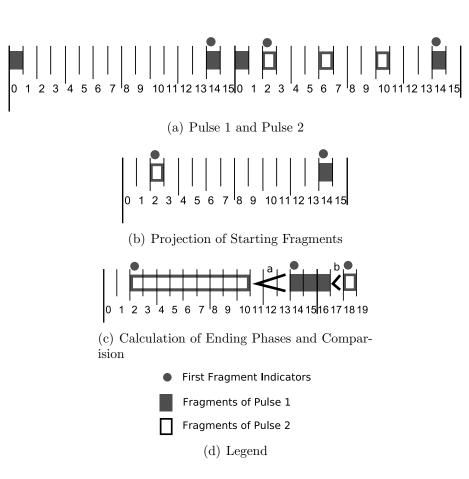

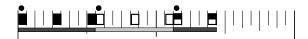

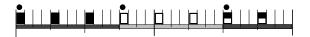

**Pulse Length** the number of fragments. This attribute along with the fragment period determines the **Pulse Duration** which is the time interval between the start of the transmission of the first fragment and the end of the transmission of the last fragment. Figure 4.2 shows pulsed data streams in the first row and their duration in the second row.

**Set of involved hosts** is a bitfield that selects the Hosts acting as sender or receiver of the pulse. It is required in order to account for "Constraint 3".

Lower Bound the system designer can use this field to specify that a pulse must be scheduled after a certain phase.

**Upper Bound** the system designer can use this field to specify that a pulse must be scheduled before a certain phase. "Lower Bound" and "Upper Bound" control the possible phase of the first fragment. If their values are equal, the phase offset of the pulse is predefined and will not be modified by the algorithm.

# 4.5.2 Preparations

The algorithm inserts one message after the other into the schedule. The more messages that were scheduled the harder it gets to find places for the remaining messages. So the pulses are ordered with those most difficult to schedule first.

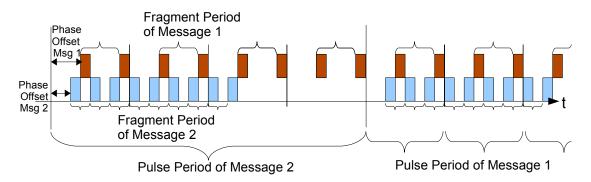

The ordering is based directly on the input values mentioned in the last section, but it has proved useful to calculate one further value for use in the sorting process. It models the constraint that pulses of the same period that have a common host must not overlap. If we consider pulses in this relation they can be regarded as blocks rather then pulses. Figure 4.2 illustrates this. It can be seen that there is much space for the fragments of a pulse in the first line but only very small blocks can fit in between the others. For a given period and a set of hosts the length of the blocks determines if it is easy to fit all blocks into the period. So the sort-index is the ratio length of all blocks to period length. The procedure that calculates the values can be found in Section 4.6, Listing 4.1

Figure 4.2: Pulses of the same period and at least one common host

### 4.5.3 Scheduling order

The pulses are sorted according to the following criteria:

#### 1 Ascending fragment period

Pulses with shorter fragment periods fit harder between the fragments of other pulses, so they are scheduled first.

#### 2 Ascending pulse period

Pulses with shorter pulse periods occur more often so it is more difficult to find a space for all occurrences.

#### 3 Ascending upper bound

To avoid that a pulse without an upper bound takes a valid place for a restricted pulse, most restricted pulses are scheduled first.

#### 4 Ascending lower bound

Although a high lower bound is more restrictive than a low lower bound, pulses with low lower bounds are preferred. This is because the pulse schedule is built up from left to right. Any gaps in the structure must be filled with so-called placeholders. So a pulse with a low lower bound could enable scheduling of a pulse with a high lower bound without use of a placeholder.

#### 5 Descending sort-index

As explained in Section 4.5.2, pulses that compete with many other pulses of the same host are prioritized. Note that at this decision level the pulses have the same pulse period.

#### 6 Descending fragment count

The last criterion is simply the pulse length since longer pulses are more difficult to schedule.

## 4.5.4 Algorithm Properties

The dynamic resource allocation relies on a scheduling algorithm that arranges the pulses so that all bandwidth and timing requirements can be satisfied. Since the computational effort of the scheduling algorithm is rather low, it is possible to do the calculations online during system operation. Compared to static offline scheduling it is the more flexible and less memory intensive solution.

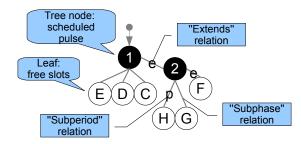

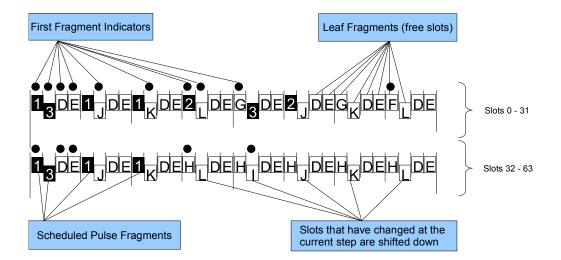

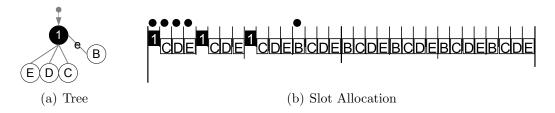

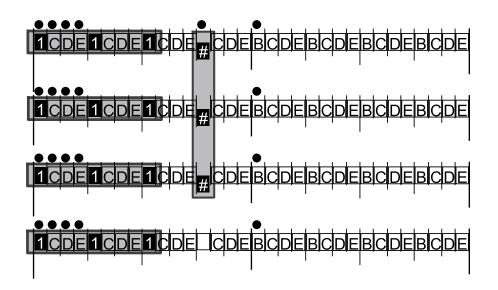

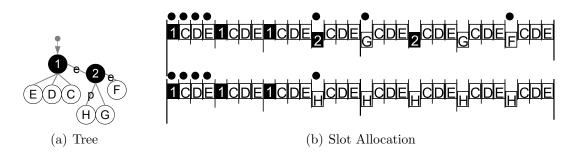

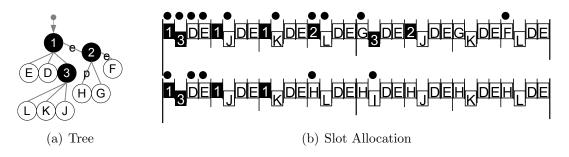

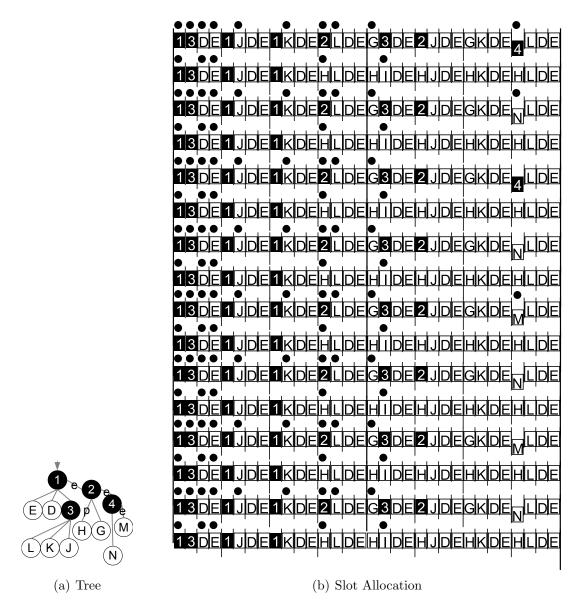

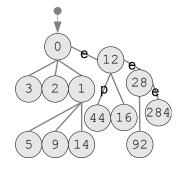

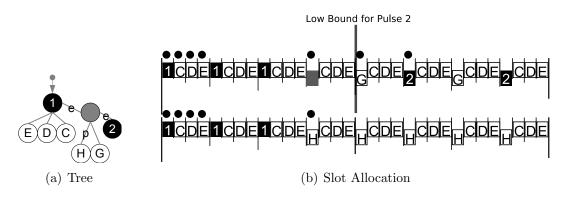

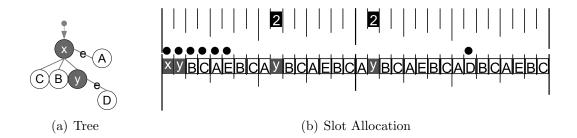

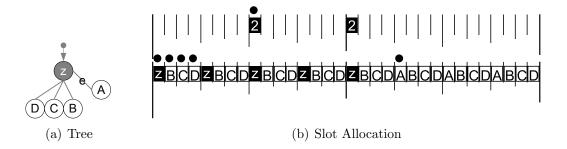

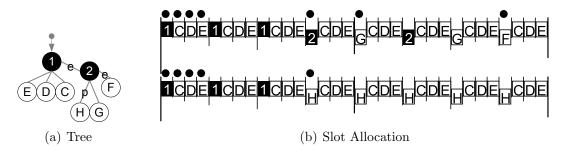

The scheduling algorithm developed for the resource management builds up the schedule in a tree structure. The nodes of the tree are the pulses that were already assigned a phase. The leaves represent phase offsets that can be used by yet unscheduled pulses. The leaves impose restrictions to pulses that may be scheduled at the respective phase.

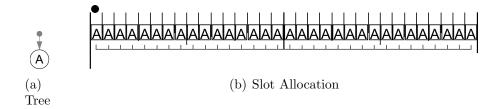

The algorithm starts with the single Leaf A that represents all slots (as shown later on in Figure 4.5). It has no restrictions except that the phase offset is zero. The first pulse is set at this location. If the lower bound of the first pulse lies above "0" a placeholder that starts at phase "0" must be inserted. More on placeholders follows later. The pulse becomes the root node and its leaves represent the fragments remaining free. The second pulse will be checked against the leaves until an appropriate leaf (=sequence of slots) is found. The order in which the leafs are tested is not arbitrary. First it is attempted to place the pulse at more restrictive leaves. If a leaf is found the pulse is inserted as a new node. If the leaf offered slots that were not used by the pulse these slots will be pointed to by the leaves of the new pulse node. Restrictions of the replaced leaf are inherited to the newly appearing leaves.

The following Section demonstrates the construction of the tree by means of an example execution.

#### 4.5.5 Example Execution

For a better understanding an example execution is presented here. To simplify the demonstration we assume that the network is able to transmit one fragment at each time instant in the 64-bit time format. In other words one fragment every  $2^{-32}s$  or  $2^{32}$  fragments per second. We refer to those time instants as *timeslots* or short *slots* to be consistent with TDMA terminology. The number of slots of a period is simply its length divided by the slot length.

$$\frac{2^{-X}}{2^{-32}} = 2^{32-X}$$

Table 4.1 lists the properties of the pulses used in the example. Bounded pulses are discussed later on. The pulses are already ordered according to the properties mentioned above.

| Number  | Period (Length  | Fragment Period   | Fragment | Duration |  |

|---------|-----------------|-------------------|----------|----------|--|

|         | in slots)       | (Length in slots) | Count    | in slots |  |

| Pulse 1 |                 | $2^{-30}$ (4)     | 3        | 9        |  |

| Pulse 2 | $2^{-26}$ (64)  | $2^{-29}$ (8)     | 2        | 9        |  |

| Pulse 3 | $2^{-26}$ (64)  | $2^{-28}$ (16)    | 3        | 33       |  |

| Pulse 4 | $2^{-23}$ (512) | $2^{-26}$ (64)    | 2        | 65       |  |

| Table 4.1: Pulses to be Scheduled in the Example Execu |

|--------------------------------------------------------|

|--------------------------------------------------------|

The pulses listed in Table 4.2 are not scheduled in the example execution but they are used in discussions to demonstrate the kinds of pulses that may be placed at a specific location. They are labeled with special characters.

| Number     | Period (Length  | Fragment Period   | Fragment | Duration |

|------------|-----------------|-------------------|----------|----------|

|            | in slots)       | (Length in slots) | Count    | in slots |