Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# Master's Thesis

# Extending Mondrian Memory Protection

carried out at the

Automation Systems Group Vienna University of Technology

under the guidance of Priv. Doz. Dipl.-Ing. Dr. techn. Christopher Krügel and Priv. Doz. Dipl.-Ing. Dr. techn. Engin Kirda as the contributing advisors responsible

by

Clemens Kolbitsch Lambrechtgasse 8/6, 1040 Wien Matr.Nr. 0126605

Vienna, February 2008

#### Acknowledgements

I would like to thank a couple of people from the Vienna University of Technology, my family, and friends who have contributed to this thesis or helped me during my studies.

First of all, a big thank you to my academic advisors Engin Kirda and Christopher Krügel for the inspiration for the topic and their many comments and suggestions that helped me keep headed in the right direction. Also, the fellow students at the SecLab offered a great environment to work and have a good time in.

My parents Arno and Maria deserve a very big thank you for supporting me during my studies and also on everything else I have ever done. To my elder brother Philipp, who taught me computer programming in the first place, and his partner Theresa, my younger brother Maximilian, and my sister Eva Maria, I also want to say thank you for supporting me and being a very important part of my life.

Of course, a very special and warm thank you to my partner Manuela for her encouragement and endless hours of listening to my, at times probably quite geeky, thoughts and ideas. At last, I want to thank all my friends for making sure I occasionally spent a night away from my computer and took me out for a beer or two.

#### Abstract

Most modern operating systems implement some sort of memory protection for user processes. Hence, it is possible to set access permissions that determine whether a region of memory allocated for a process can be read, written, or executed by this process. Mondrian memory protection is a technique that extends the traditional memory protection scheme and allows fine-grain permission settings. Instead of being able to set access permissions on a page-level, Mondrian memory protection supports different access permissions for individual words. However, this protection scheme is still limited to only two permission bits that have a pre-defined semantics. This is not sufficient to implement more complex security techniques, for example, a race condition detection system.

The presented solution proposes an extension to the simple Mondrian protection scheme that provides more flexibility to user programs and the operating system. Based on our extended architecture, we implement mechanisms to protect sensitive data structures on the heap and on the stack. Moreover, we present the implementation of a technique to detect race conditions. Our experiments demonstrate that the system can provide the expected protection and ability to detect races with reasonable overheads. Furthermore, our results show that even large systems such as the GNU C Library and the Apache web server contain problems related to race conditions.

#### Zusammenfassung

Speicherschutz für Anwenderprogramme ist ein Konzept, das vom Großteil der heutzutage verwendeten Betriebssysteme bereitgestellt wird. Dieses ermöglicht es, für die einzelnen Speicherbereiche eines Prozesses unterschiedliche Zugriffsberechtigungen für Lese- und Schreib-Operationen sowie das Ausführen von Code zu setzen. Eine Erweiterung der traditionellen Schutzmechanismen ist Mondrian Memory Protection. Dieses Schema erlaubt das genaue Spezifizieren unterschiedlicher Berechtigungen auf Wort-Basis anstelle der traditionellen Speicherseiten-Basis. Allerdings ist auch hier die Spezifikation auf zwei Zugriffsbits limitiert. Zusätzlich ist die Bedeutung der einzelnen Bitkombinationen vorgegeben, was es unmöglich macht, damit komplexere Sicherheitstechniken, wie beispielsweise einen Race Condition Detector, zu implementieren.

Der Ansatz, der in dieser Arbeit präsentiert wird, ist eine Erweiterung der einfachen Mondrian Memory Protection. Sie soll eine größere Flexibilität für Anwenderprogramme und das Betriebssystem ermöglichen. Aufbauend auf unserer Architektur zeigen wir die Implementierung von Mechanismen zum Schutz von heiklen Datenstrukturen im Heap und Stack Speicher. Des Weiteren präsentieren wir eine Technik zum Erkennen von Race Conditions, die auf der vorgeschlagenen Architektur basiert.

Unsere Experimente beweisen, dass das System, bei akzeptablem Mehraufwand, den gewünschten Schutz und die Möglichkeit zum Erkennen von Race Conditions bietet. Zusätzlich zeigen die Ergebnisse, dass sogar große Systeme, wie die GNU C Bibliothek und der Apache Webserver, Probleme in Zusammenhang mit Race Conditions aufweisen.

# Contents

| 1        | Introduction                                         | <b>1</b>   |

|----------|------------------------------------------------------|------------|

|          | 1.1 Motivation                                       | 1          |

|          | 1.2 Organization of this thesis                      | 2          |

| <b>2</b> | State of the art                                     | 4          |

|          | 2.1 Intel x86 memory management                      | 4          |

|          | 2.2 Mondrian memory protection                       | 7          |

| 3        | Description of our approach 1                        | 0          |

|          | 3.1 Protection hierarchy                             | 1          |

|          | 3.2 Memory access control                            | 15         |

|          | 3.3 Memory access policies                           | 17         |

| <b>4</b> | System implementation 1                              | .8         |

|          | 4.1 Instruction set extension                        | 18         |

|          | 4.2 Kernel adaptions                                 | 26         |

| <b>5</b> | Application of extended Mondrian memory protection 3 | 5          |

|          | 5.1 Stack Protection                                 | 35         |

|          | 5.2 Heap Protection                                  | 14         |

|          | 5.3 Race Condition Detection                         | 18         |

| 6        | Evaluation 6                                         | 60         |

|          | 6.1 Performance                                      | 60         |

|          | 6.2 Memory Overhead                                  | 52         |

|          |                                                      | 52         |

| 7        | Related Work 6                                       | <b>5</b> 9 |

8 Summary and conclusion

$\mathbf{72}$

# List of Figures

| 2.1 | Logical to linear memory translation. [23]                       | 5  |

|-----|------------------------------------------------------------------|----|

| 2.2 | Example segmentation of a memory address space using two         |    |

|     | segments. $[23]$                                                 | 6  |

| 2.3 | Linear to physical memory translation. [23]                      | 7  |

| 2.4 | Page-table entry of a 4 kibibyte page. [23]                      | 8  |

| 2.5 | Mondrian memory protection system design. [38]                   | 9  |

| 3.1 | Protection hierarchy.                                            | 12 |

| 3.2 | Structure of the newly introduced control register CR6           | 12 |

| 3.3 | Structure of a protection directory entry                        | 13 |

| 3.4 | Structure of a protection table entry                            | 14 |

| 3.5 | Structure of a protection page entry                             | 14 |

| 3.6 | Access control decision for a read access yielding a protection  |    |

|     | violation                                                        | 16 |

| 3.7 | Access control decision for a read access granting the memory    |    |

|     | access                                                           | 16 |

| 4.1 | Structure of the newly introduced control register CR7           | 22 |

| 4.2 | Upper half of the common protection fault base handler           | 32 |

| 4.3 | Lower half of the common protection fault base handler. $\ldots$ | 33 |

| 5.1 | Stack layouts with (a) no, (b) StackGuard [15], and (c) our      |    |

|     | extended Mondrian memory protection                              | 38 |

| 5.2 | In-band information of a free chunk [3]                          | 45 |

| 5.3 | Race condition detection state machine [29]                      | 50 |

# Chapter 1

# Introduction

### 1.1 Motivation

Most modern operating systems implement some sort of memory protection for user processes [16, 31, 33]. That is, it is possible to set access permissions that determine whether a region of memory allocated for a process can be read, written, or executed by this process. Typically, for operating systems that support paged virtual memory, the granularity of these access permission are on a per-page basis. This means that a process or the operating system can assign different protection settings to each individual page of the process (where the size of a page is typically between 1 and 8 KB [33]).

The page-based protection is useful to mark the text portion of a process as non-writable, preventing unintentional modifications of the code due to programming errors. Another use of access permissions is to flag the data and stack segments as non-executable<sup>1</sup>. This increases the security [27, 32] as an attacker can no longer execute shellcode that he injects into the heap or the stack (e.g., by exploiting a buffer overflow vulnerability).

While memory protection is a useful technique to improve the reliability and security of processes, it is fairly coarse-grain. The reason is that permission settings can only be applied to complete pages. This limits the flexibility, especially when there are small memory fragments located close to each other that would require different permission settings. A standard example for such a memory area is the stack. A stack stores both data (such as function

<sup>&</sup>lt;sup>1</sup>Provided that the hardware provides the necessary means to set different permissions for read and execute access, such as the No eXecute bit [22].

parameters or local variables) that a process must be able to read and write, as well as function return addresses, which should never be modified by the application. Because data and return addresses are stored in the same page, the least restrictive protection settings must be applied. As a result, a return address can be modified by an application function. This leads to the problem of buffer overflow exploits that trick a memory write operation to change the return address on the stack to a value of the attacker's choice.

Mondrian memory protection [37, 38] is a technique that extends the traditional memory protection scheme and allows fine-grain permission settings. More precisely, instead of being able to set access permissions on a pagelevel, Mondrian memory protection supports different access permissions for individual words. This allows a process to use different memory protection settings for different words on the stack. However, Mondrian memory protection is still limited to only *two* permission bits with a pre-defined semantics. Similar to the bits at the page-level, these permission bits control read, write, and execute access. This might not be sufficient in all cases. For example, in order to keep track of the memory accesses of multiple threads to detect race conditions, the available mechanism is insufficient. Unfortunately, race conditions are an important problem and lead to bugs and security problems that are difficult to track down [10, 11, 34, 36]. This problem is exacerbated by the increasing use of parallel programming and multi-threaded applications.

In this thesis, we propose an extension to the simple Mondrian protection scheme that provides more flexibility to user programs and the operating system. More precisely, instead of two protection bits, we propose to use 30-bit protection labels that can be assigned to each memory word. These labels can be freely used as a basic mechanism to implement different techniques such as return address protection, heap protection, or race condition detection. The protection labels are controlled via a simple interface that allows user programs controlled access to protection information. In case of a protection fault, the operating system invokes a user-defined module in the kernel that can implement a flexible policy to handle the exception.

### **1.2** Organization of this thesis

In this thesis, we first describe existing memory protection schemes and the general mechanisms that our extended system supports in Chapters 2 and 3, respectively. Chapter 4 handles the details of implementing the mechanisms using CPU extensions as well as operating system adaptions. Then, we discuss concrete techniques that leverage the general memory protection mechanisms to realize return address protection on the stack, heap memory protection, as well as a race condition detection in Chapter 5.

Finally, we describe our experiments that demonstrate that the system can provide the expected protection and ability to detect races with reasonable overheads in Chapter 6. In a last chapter, we put our work into context with previous publications on memory protection and race condition detection.

# Chapter 2

### State of the art

In this chapter, we explain memory protection as it is available on current Intel x86 CPUs. Furthermore, we deal with the idea of Mondrian memory protection as described in [38].

### 2.1 Intel x86 memory management

Intel's x86 processor family provides two basic concepts for protecting memory [23]:

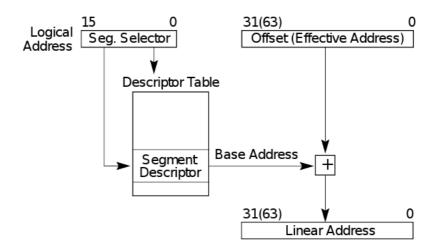

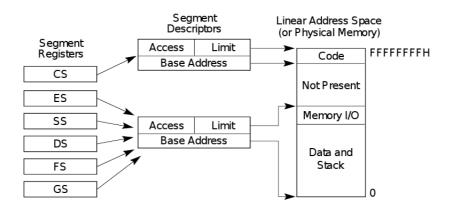

Segmentation allows to split the memory address space visible to a user application into multiple segments. In this addressing mode, every logical memory address is represented by a segment:offset tuple. Thus, for every access to memory, one of the six segment registers (code segment register CS, stack segment register SS and data segment registers DS, ES, FS, and GS) has to be provided. If no such register is provided for the access, the register most appropriate for the operation is chosen (e.g. the stack segment register is automatically used when pushing a value on stack). Figures 2.1 and 2.2 show how these registers are used to access a memory address.

Each segment register either points into the *global descriptor table* or into the *local descriptor table*, holding the segment's

- base address used for translating the logical address into a linear or physical address,

- size (limit),

Figure 2.1: Logical to linear memory translation. [23]

- access control information, as well as

- status information.

For every segment, the operating system can provide four bits for controlling memory access, including *read-only*, *read-write*, and *execute-only* access types. To achieve portability with most architectures, Linux only employs very limited use of segmentation [30], however. In fact, Linux only employs a non-standard segment register when accessing thread specific data. By default, logical and linear addresses coincide and access is restricted through the use of *paging*, only.

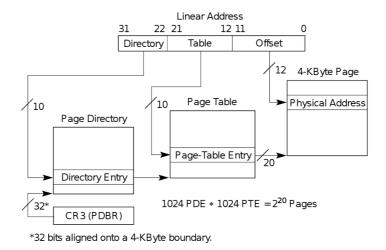

Paging is Intel's second concept for memory protection: Modern operating systems divide the linear address space visible to a user program into sections of equal size, typically called *pages*. Each memory page allocated for a program is represented by a *page table entry* in the program's *page directory* / *page table* hierarchy. The page hierarchy is used by the operating system and the CPU's memory management unit to map virtual memory pages to the corresponding physical frames in the RAM<sup>1</sup>. This mapping is necessary to find the location in physical memory that corresponds to an

<sup>&</sup>lt;sup>1</sup>When referring to physical addresses, a memory region holding data of a virtual page is called a frame.

Figure 2.2: Example segmentation of a memory address space using two segments. [23]

address in the virtual address space. Figure 2.3 shows how a virtual memory address is resolved into a physical memory frame using this hierarchy and the per process unique control register CR3.

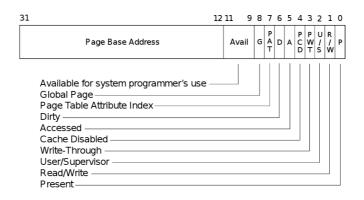

Figure 2.4 shows the structure of a page table entry: Each entry contains the page's physical base address used for the address mapping <sup>2</sup>, a set of bits to store access statistics, and two bits informing the CPU whether a page is **read-only** and whether access is restricted to **supervisor** code.

On every access to a virtual memory address, the CPU consults the mapping (or possibly the TLB<sup>3</sup>) to find the respective physical memory. It then checks the aforementioned access bits. When an invalid access is detected, the CPU raises a page fault. This signals the operating system's kernel that a problem has occurred and allows for a proper reaction to resolve the problem (e.g., by terminating the offending process).

Summarizing, the use of paging has four implications: For one thing, each process has an unique address spaces (i.e. page hierarchy). This allows the kernel to protect processes from one another. Secondly, processes cannot destroy read-only memory regions (e.g. text mappings) by writing to such addresses accidentally. Furthermore, the operating system's kernel can protect vital memory structures by marking them as supervisor pages and

$<sup>^{2}</sup>$ Virtual pages have to be aligned onto a 4 KByte boundary. This leaves the 10 least significant bits to be used for other purposes.

<sup>&</sup>lt;sup>3</sup>The *Translation Lookaside Buffer* stores mapping information for all recently accessed pages.

Figure 2.3: Linear to physical memory translation. [23]

lastly, paging does not provide a method for marking memory regions as non-executable.

### 2.2 Mondrian memory protection

While Intel x86's memory protection techniques are useful in improving the system's stability as well as reliability and security of processes, it is fairly coarse-grain. As mentioned in the introduction already, the reason is that permission settings can only be applied to complete pages. This limits the flexibility, when having to apply the least restrictive protection settings to different adjacent memory areas.

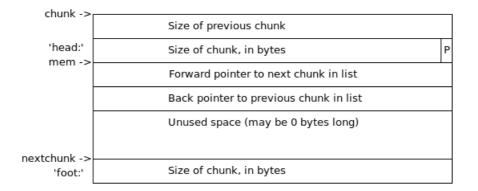

Mondrian<sup>4</sup> memory protection [37, 38] is a technique that extends Intel's traditional memory protection scheme and allows fine-grain permission settings: Similar to the x86 architecture, Mondrian memory protection employs two bits to store four different access permissions (*no*, *read-only*, *read-write*, and *execute-read*) for every memory region available in the system. However, instead of storing the permission information in the per-process unique page

$<sup>^{4}</sup>$ The authors of [38] called their protection system Mondrian memory protection (MMP), because figures of protection ranges occasionally resembled works by the eponymous early twentieth century artist.

Figure 2.4: Page-table entry of a 4 kibibyte page. [23]

hierarchy, Mondrian memory protection uses an additional *permissions table*. This allows the system to store protection information for each memory word (instead of the page-level granularity of the x86 architecture). Moreover, every thread is a member of one *protection domain*, possibly sharing the permission table with other threads of the same domain.

On every access to a memory address, the CPU's protection enhancement consults the currently executing thread's protection domain register to look up the address protection bits stored in the corresponding protection table. To reduce the memory overhead introduced by the protection tables, the implementation in [38] provides different possibilities for storing the table's structure. This allows to adjust the size of the region the protection information applies to.

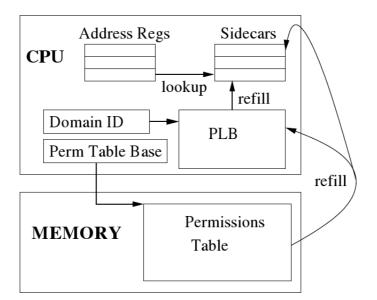

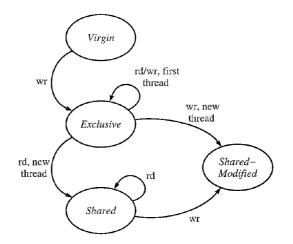

Figure 2.5 shows a design overview of Mondrian memory protection. To avoid repeated look ups of access permissions, a *permissions lookaside buffer* (PLB) caches entries from the permissions table. Furthermore, every address register contains an additional *sidecar register*. This sidecar register stores the last table segment accessed through the corresponding address register.

Summarizing, Mondrian memory protection proposes finer-grained memory protection than Intel's x86 standard. Each word in the memory address space can be assigned two permission bits. This overcomes the problem of least restrictive protection on the stack, where read-only and writable memory addresses are stored adjacently. To minimize the memory overhead for storing permission information, multiple words sharing common permissions can be

Figure 2.5: Mondrian memory protection system design. [38]

grouped. Furthermore, a permissions lookaside buffer and sidecar registers are used to increase the system's performance.

# Chapter 3

# **Description of our approach**

In Chapter 2, we described Intel's standard x86 protection as well as Mondrian memory protection schemes. Despite the simplicity and broad acceptance of the former and flexibility of the latter, they share one shortcoming which is the fact that one cannot associate more than two bits of protection information with a memory region. Moreover, the pre-defined meaning of the four possible bit combinations significantly limits the flexibility of the protection system.

These two drawbacks are the starting point of the extended Mondrian memory protection technique described in this chapter: While trying to combine the simplicity of x86 memory protection with the fine granularity of the original Mondrian memory protection, this implementation allows a *user-specified examination* of *expanded protection information* stored for memory regions. For this purpose, the protection architecture is split into the following three components:

- The first component implements the *protection hierarchy*. This protection hierarchy stores, for each process, a mapping between *30-bit protection labels* and memory addresses. That is, it is possible to associate a 30-bit protection label with each word in the process address space. This is a generalization of the two bits used by the original Mondrian memory protection. This component also provides an interface that lets user processes and the OS kernel modify the protection settings.

- The second component is responsible for checking memory accesses. To this end, the system uses a special *protection control register*. The

content of this control register is compared with the protection label associated with the memory location that is accessed. In case there is a mismatch, a protection fault is invoked. In addition to the control register, there are two bit-masks that allow to refine (or modify) the value of the control register prior to this comparison, depending on whether the process performs a read or a write operation.

• The third component, called the *protection fault handler*, implements the response to a protection fault. This handler code is realized as a loadable kernel module, which allows users to define complex policies that can be exchanged while the system is running. In the protection fault handler, the system can change the protection settings of certain memory areas, as well as the content of the protection control register (and the associated bit-masks).

### 3.1 Protection hierarchy

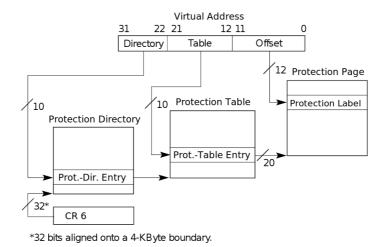

Similar to the page hierarchy, which is used in the x86 architecture to perform a mapping from virtual to physical addresses, our extended Mondrian memory protection uses a two-level hierarchy of *protection tables*. That is, there is a *protection directory* that stores entries that point to *protection tables*. Each protection table, in turn, has entries that point to *protection pages*. Each allocated word of virtual memory is represented by an entry in the protection page. The newly introduced register CR6 serves as entry point into the protection hierarchy. An overview of the protection hierarchy can be seen in Figure 3.1.

To save space when the protection labels of all words in a particular page are identical, we use three different levels of granularity:

- *High granularity protection*: This method adds 30 bits of protection information to every word in the virtual address space. The protection information is stored in a protection page allocated in the process' virtual address space, but is protected from direct access by user code.

- Low granularity protection: This method stores protection information directly into the entry of the protection table, allowing to specify 30 bits of protection information for a complete page of virtual memory.

Figure 3.1: Protection hierarchy.

• *Minimal granularity protection*: This method stores protection information directly into the entry of the protection directory, allowing to specify 30 bits of protection information for a set of 1024 adjacent pages of virtual memory.

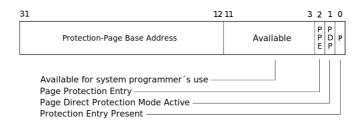

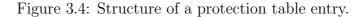

The structure of the individual entries in Figure 3.1 can be seen in Figures 3.2, 3.3, 3.4, and 3.5. The meanings of the individual fields and bits are as follows:

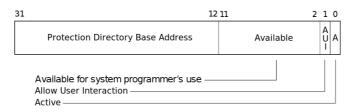

Figure 3.2: Structure of the newly introduced control register CR6.

#### Control register CR6:

- Active bit (bit 0): Indicates whether the extended Mondrian memory protection system is currently active. If this bit is cleared, bits 1 through 31 my be used arbitrarily by the programmer.

- Allow user interaction bit (bit 1): Indicates whether non-supervisor code may inspect/modify protection information. For details on protection information interaction, refer to later sections.

- **Protection directory base address** (bits 12 through 31): Specifies the most significant bits of the virtual address of the first byte in the protection directory. This forces the protection directory to be aligned on a 4-KByte boundary.

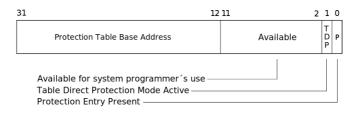

Figure 3.3: Structure of a protection directory entry.

#### Protection directory entry:

- **Present bit** (bit 0): Indicates whether the protection directory entry should be used during a protection look up. If this bit is cleared, bits 1 through 31 may be used arbitrarily by the programmer.

- Table direct protection mode active (bit 1): Indicates if the 1024 pages referenced by this protection directory entry use minimal granularity protection. If the bit is set, bits 2 through 31 hold protection information directly.

- **Protection table base address** (bits 12 through 31): Specifies the most significant bits of the virtual address of the first byte in the protection table. This forces protection tables to be page-aligned.

#### **3.1. PROTECTION HIERARCHY**

#### Protection table entry:

- **Present bit** (bit 0): Indicates whether the protection table entry should be used during a protection look up. If this bit is cleared, bits 1 through 31 may be used arbitrarily by the programmer.

- Page direct protection mode active (bit 1): Indicates if the page referenced by this protection table entry uses low granularity protection. If the bit is set, bits 2 through 31 hold protection information directly.

- Page protection entry (bit 2): Indicates if the page referenced by this protection table entry is a protection page. As protection pages lie in the user address space, applications must be prevented from tampering with the protection information directly. This bit is therefore the equivalent to the supervisor bit of x86 memory protection.

- **Protection page base address** (bits 12 through 31): Specifies the most significant bits of the virtual address of the first byte in the protection page. Thus, page-alignment is required for protection pages.

Figure 3.5: Structure of a protection page entry.

#### **3.2** Memory access control

When performing a memory access, the CPU has to do a look up of the protection information for the corresponding address. This is done by navigating through the protection hierarchy, starting from the current value of the control register CR6 (as described in the previous section). When high granularity protection is used, the protection table entry looked up by the CPU serves as pointer to a protection page, which contains the 30-bit protection label used for memory access control. Otherwise, in case of low or minimal granularity protection, the corresponding bits of the protection directory/table entry are directly used for access control (thus the term table/page direct protection mode).

In case no protection information is found (because the protection directory or protection table does not contain a corresponding entry or protection has been disabled through the corresponding bit in the control register CR6), the access to the memory address is immediately granted. Also, note that regardless of the granularity level, it is possible that a memory access requires looking up more than one protection label. Typically, this happens when a multi-byte access is unaligned or spans two pages. In these cases, the memory protection checks all protection labels. Access is only granted when all labels permit it.

Once a 30-bit protection label is retrieved, it can be used to perform an access control decision. That is, given this label and additional information, the system must decide whether an access should be granted or whether a protection fault should be thrown. The aforementioned additional information that allows the access decision to be made is the value of a new processor register, the protection control register CR5. In addition, there are two access bit-masks, called a read-mask and a write-mask.

To reach an access control decision, the system takes the 30-bit protection label obtained during look up and performs a logic AND operation with the appropriate access bit-mask (depending on whether this is a read or write access). The result of this operation is a *protection token*. Similarly, the values currently stored in the control register CR5 and the mask are ANDed, obtaining a *control token*. Comparing both tokens decides if the current memory access should be granted or not. More precisely, a protection fault is raised in case the two tokens do not match. Figures 3.6 and 3.7 show two examples for access control decisions that yield different results.

Early tests of our protection system showed that it is very desirable to have a

#### 3.2. MEMORY ACCESS CONTROL

|                  | Hex        | Binary                                  |

|------------------|------------|-----------------------------------------|

| Protection label | 0x000271d0 | 0b000000000000100111000111010000        |

| CR5              | 0x000211d0 | 0b0000000000000000000000000000000000000 |

| Read mask        | 0x8003fffc | 0b1000000000000111111111111111100       |

|                  |            |                                         |

$\operatorname{Result}$

Protection violation

Figure 3.6: Access control decision for a read access yielding a protection violation.

|                  | Hex        | Binary                            |

|------------------|------------|-----------------------------------|

| Protection label | 0x000271d0 | 0b000000000000100111000111010000  |

| CR5              | 0x070271d0 | 0b0000011100000100111000111010000 |

| Read mask        | 0x8003fffc | 0b100000000000111111111111111100  |

|                  |            |                                   |

| Result           |            | Read access granted               |

Figure 3.7: Access control decision for a read access granting the memory access.

mechanism that allows deactivation of the protection examination for a single instruction or memory access. To handle such situations, we introduced two read-and-clear bits in the CPU's flag set, one for read- and one for writeaccesses.

The CPU consults these flags before signalling a protection violation. If the according flag bit is set, the fault is skipped and both bits are reset to zero. The use of two flag bits instead of just one comes from the fact that some x86 assembler instructions<sup>1</sup> may cause multiple accesses into memory that might want to be handled individually.

<sup>&</sup>lt;sup>1</sup>E.g. **cmpxchg mem32 reg32** compares register EAX with memory address mem32, modifying either register reg32 or memory mem32, depending on the result of the comparison.

### **3.3** Memory access policies

As previously mentioned, the extended Mondrian memory protection does not specify any specific meaning for the individual bits protecting a memory address. The system only performs access control checks as outlined above. The way in which the protection labels and the content of the protection register (together with the bit-masks) are used is completely up to the user of the system. In Chapter 5, we demonstrate the flexibility of the approach by showing how different applications can be implemented on top of the general architecture.

To specify rules or policies for using the memory protection system, the user has two mechanisms. On the one hand, a program (or a compiler) can use a set of newly introduced instructions to manipulate the memory protection settings (labels) during process execution. The following set of new machine instructions has been introduced allowing a process to read, set, or modify protection information:

- prot\_mov reg, mem: Load the protection information of a memory address into a register,

- prot\_mov mem, reg/imm: Set the protection information of a memory address to an immediate or register's value,

- prot\_and mem, reg/imm: AND the protection information of a memory address with an immediate or register's value, and

- prot\_or mem, reg/imm: OR the protection information of a memory address with an immediate or register's value.

In addition to this first mechanism, the user can load a kernel module into the operating system that defines the protection fault handler. This protection fault handler can be arbitrarily complex and runs in the context of the kernel. Thus, it has full control over both the control registers and the memory protection information. Also, the kernel module is notified whenever a new process or thread is started, or when the operating system schedules a new thread. This allows the system to react to events that might require to load thread- or process-specific protection values.

# Chapter 4

# System implementation

### 4.1 Instruction set extension

This section deals with the details of providing extended Mondrian memory protection. To provide the instructions to modify the protection labels, the instruction set of the x86 processor needs to be extended. Also, we had to add additional control registers and a cache similar to a translation lookaside buffer, which is responsible for caching the protection labels for recently accessed memory locations.

The open source system emulator Qemu [8] served as base for our implementation. Besides the necessary processor extensions, we extended the code for translating virtual addresses to also look up protection labels and to do the necessary access control checks. Similar to the occurrence of a page fault, protection faults are passed to the emulated system using interrupts, and thus, need no special extensions. Furthermore, this section explains additional extensions made to Qemu. These extensions are not part of the actual protection system but were necessary to evaluate the experiments described in Chapter 6.

#### Qemu internals

When simulating a guest system on a host computer, there are two general approaches: *Virtualization* allows to run the guest's machine code on the host directly. Obviously, this requires some sort of support by the underlying hardware and operating system alike. *Emulation*, on the other hand, is a much simpler approach and does not require any specific hardware or

operating system support. The big disadvantage is that emulated systems are much slower, in general.

Qemu uses a combination of both approaches, unifying simplicity of emulation and some speed advantages of virtualization: Every block of machine code executed by the guest system is first translated into code understandable by the host system. Register manipulations are translated into code storing the new values in Qemu's internal memory structures and every memory access inside this *translation block* (or TB) is sanitized by simulating a memory management unit, checking presence of the accessed pages and accordance of their protection bits and access type. This TB is then run directly on the host's CPU and cached to minimize the overhead of translation in case the the same code is executed repeatedly.

#### Control register extension

Due to Qemu's code translation approach, it is very easy to add new items to the CPU instruction set. To add the control registers CR5, CR6, and CR7 (this control register will be discussed shortly), only the functions responsible for code translation and Qemu's internal CPU state structure had to be adjusted. Setting the CR5 read- and write-masks and the read-and-clear flags mentioned in Section 3.2 was implemented using the two least significant bits of CR5. As protection labels can only hold 30 bits of information, these two extra bits in the control register are used as shown in Table 4.1.

| Bits 1 and 0 | Meaning                                      |  |  |  |

|--------------|----------------------------------------------|--|--|--|

| 0x00         | Remaining bits (bits 31 through 2) are used  |  |  |  |

|              | as new <i>value</i> of the control register  |  |  |  |

| 0x10         | Read-and-clear flags for disabling read- and |  |  |  |

|              | write-protection are set depending on the    |  |  |  |

|              | remaining bits 3 and 4, respectively         |  |  |  |

| 0x01         | Remaining bits are used as CR5 read-mask     |  |  |  |

| 0x11         | Remaining bits are used as CR5 write-mask    |  |  |  |

Table 4.1: Bits 0 and 1 of control register CR5.

#### Access control enforcement

As described in the previous chapter, every access to a page protected by our extended Mondrian memory protection requires enforcement of the memory access policies. For this reason, TB code not only includes memory access sanitation, as mentioned in Section 4.1, but also resolves the protection label for the accessed memory address.

The code then checks access permissions using CR5 and the appropriate mask, as described in Section 3.2. In case of an access violation, the page fault method is used to trigger an interrupt. The emulated guest system can distinguish between a casual page fault and a protection violation using the extended error code table, as shown in Table 4.2.

| Bit           | it Bit mask Meaning                                           |                                         |  |  |  |  |

|---------------|---------------------------------------------------------------|-----------------------------------------|--|--|--|--|

|               |                                                               |                                         |  |  |  |  |

| Standard x86: |                                                               |                                         |  |  |  |  |

| 0             | 000000000000000000000000000000000000                          | Accessed page not found                 |  |  |  |  |

|               | $0 \times 0000000001$                                         | Page access violation                   |  |  |  |  |

| 1             | 0x000000000000000000000000000000000000                        | Read access                             |  |  |  |  |

|               | $0 \ge 0 \ge$ | Write access                            |  |  |  |  |

| 2             | 0x000000000000000000000000000000000000                        | Kernel mode access                      |  |  |  |  |

|               | $0 \ge 0 \ge$ | User mode access                        |  |  |  |  |

| 3             | 0x0000001000                                                  | Access to reserved bit                  |  |  |  |  |

| 4             | 0x0000010000                                                  | Access was instruction fetch            |  |  |  |  |

|               |                                                               |                                         |  |  |  |  |

| Exte          | ended Mondria                                                 | n memory protection:                    |  |  |  |  |

| 5             | 0x0000100000                                                  | Protection violation                    |  |  |  |  |

| 6             | 0x00000000000                                                 | 4-byte access (possibly unaligned)      |  |  |  |  |

|               | $0 \ge 0 \ge$ | 8-byte access (possibly unaligned)      |  |  |  |  |

| 7             | 0x0010000000                                                  | Reserved for kernel internal use        |  |  |  |  |

| 8             | 0x010000000                                                   | Reserved for race detection system      |  |  |  |  |

| 9             | 0x100000000                                                   | Protection violation is user protection |  |  |  |  |

|               |                                                               | information interaction                 |  |  |  |  |

Table 4.2: Error code signalling a page fault or protection violation.

The x86 memory management unit employs a TLB to store the physical base addresses of recently accessed pages. Qemu's Mondrian memory protection extension additionally stores the protection table entry found during the look up. Thus, the protection label can be fetched directly from the TLB when using minimal or low granularity protection. For high granularity protection, the virtual address of the protection page can be taken from the TLB allowing to skip parsing the protection hierarchy.

To quicken access control even further, the extended TLB also holds the physical base address of the associated protection page. This allows to reference protection labels directly, even if high granularity protection is employed. The drawback of this last enhancement is the fact that when a protection page is swapped out (i.e. removed from RAM), all references to this now unavailable memory frame have to be removed from the TLB.

#### Protection manipulation instructions

To keep compliance with existing compilers and code inspection tools (such as debuggers and disassemblers), the machine instructions to access the memory protection settings were realized by adding another control register CR7<sup>1</sup>. Furthermore, unlike access to other control registers, user mode code is allowed to access and modify the content of this register.

To implement the protection instructions, each bit assigned to this register was given a special meaning, indicating source and destination registers as well as the requested modification operation. That is, the **prot**\* instructions introduced in Section 3.3 are expressed as instructions that modify the control register CR7.

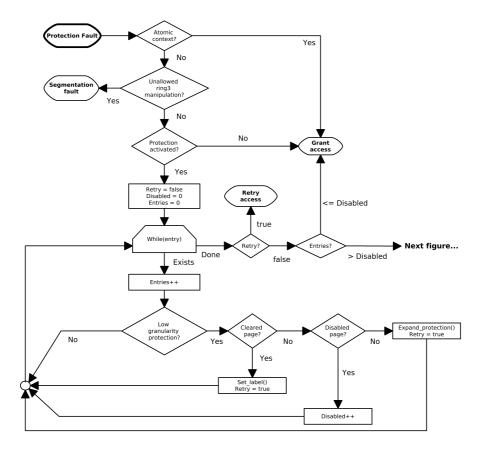

Figure 4.1 shows the bit layout used when interacting with the control register. The meaning of the individual bits is as follows<sup>2</sup>:

- Operation (bits 1 and 0): Defines the requested operation: Get (0x00), Set (0x01), AND (0x10), and OR (0x11).

- Address Register (bits 4, 3, and 2): The register holding the memory address to be inspected/modified: EAX (0x000), ECX (0x001), EDX (0x010), EBX (0x011), ESP (0x100), EBP (0x101), ESI (0x110), and EDI (0x111).

<sup>&</sup>lt;sup>1</sup>Although only control registers CR1 through CR4 and CR8 may be used currently, Intel has specified the op-codes for CR1 through CR15. Thus, most compilers and code inspection tools can already handle code using these registers.

$<sup>^{2}</sup>$ Bits 31 through 29 will be dealt with in the following sections.

| 31 30 2928                                                                                                                                                                | 20 19         | 18 15 | 14     | 13 11 | 10          | 96    | 5      | 4 2  | 1 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------|-------|-------------|-------|--------|------|-----|

| P B E D D Reserved                                                                                                                                                        | V<br>D<br>S   | VDisp | V<br>P | VReg  | A<br>D<br>S | ADisp | A<br>P | AReg | Ор  |

| Value Displ. Signed<br>Value Displacemen<br>Value Pointer<br>Value Register<br>Address Displacem<br>Address Displacem<br>Address Pointer<br>Address Register<br>Operation | t<br>ent Sigi |       |        |       |             |       |        |      |     |

Figure 4.1: Structure of the newly introduced control register CR7.

- Address Pointer (bit 5): Specifies whether the *address register* holds the memory address directly (bit 5 cleared) or points to a memory location holding the memory address (bit 5 set).

- Address Displacement (bits 9 through 6): An optional displacement added to the memory address. We only allow word-aligned displacement a displacement of 2 therefore means 8 bytes.

- Address Displacement Signedness (bit 10): The sign of the optional address displacement: If this bit is set, the displacement is subtracted from the memory address.

- Value Register (bits 13, 12, and 11): The register holding the value to be used for the label manipulation or the register/memory receiving the obtained label value. Register bit representation analogous to *address register*.

- Value Pointer (bit 14): Specifies whether the *value register* holds the value directly (bit 14 cleared) or points to a memory location holding the value (bit 14 set).

- Value Displacement (bits 18 through 15): An optional displacement added to the value address.

• Value Displacement Signedness (bit 19): The sign of the optional value displacement.

For a better understanding of the bit fields described above, the following code snippets show the symbolic code instructions and how they can be represented in c / assembler code:

Clear the protection label of variable bar:

```

1 int bar = 0x0;

\mathbf{2}

/*

3

* prot_set %eax, 0x0

4

5

-----SDispPValSDispPAddOp

6

=

7

* set protection label of address in %eax to value

8

* in %ebx

9

*/

10

11

asm volatile(

12

"movl %0, %%eax\n"

13

"movl %1, %%ebx\n"

14

"movl %2, %%cr7\n"

15

16

:

: "r" (&bar),

17

"i" (0x0),

18

"r" (0x00001801)

19

: "%eax");

20

```

Set the most significant bit of the protection label of variable **foo** indirectly using a pointer with displacement:

```

1 int foo = 0x0;

2 int *p_foo = &foo;

3 p_foo += 2;

4

5 /*

6 * prot_or -0x8(%ebx), 0x80000000

7 *

8 * i.e.

```

```

9

prot_or 0xffffff8(%ebx), 0x8000000

10

11

-----SDispPValSDispPAddMd

12

0x000034af = 0xb000000000000000000011010010101111

*

13

OR protection label of address Oxfffffff8(%ebx)

14

* with value in %esi

15

*/

16

17

asm volatile(

18

"movl %0, %%ebx\n"

19

"movl %1, %%esi\n"

20

"movl %2, %%cr7\n"

21

22

"r" (p_foo),

23

"i" (0x8000000),

^{24}

"r" (0x000034af)

25

: "%eax");

26

```

Clearly, changing an address' protection label requires high granularity protection for the page holding the address' memory. For this reason, the CPU will first check for the required level of protection. If this level is not present, a protection violation will allow the kernel to react appropriately.

#### Performance measuring extension

Measuring performance of an application or the whole operating system is a non-trivial task, in general. For this purpose, most processor architectures provide a set of instructions to accumulate certain events, like occurrences of page faults, instructions executed, and so forth. Qemu does not provide such a processor extension at the moment, however. But the performance impact introduced by our extended Mondrian memory protection, though not a primary issue in this thesis, is an interesting topic. We thus introduced a set of instructions that allow to monitor and document execution of certain code segments.

Bit 31 in Figure 4.1 enables this new *performance interface*. If a new value, having bit 31 set, is moved into CR7, the remaining bits are used as a command to the performance unit. A list of available commands is shown in Table 4.3.

| Value      | Bit mask                | Register included        |

|------------|-------------------------|--------------------------|

| 0x80000000 | $0x1000 \dots 00000000$ | New process created      |

| 0x80000001 | $0x1000 \dots 0000001$  | Process closing          |

| 0x80000002 | $0x1000 \dots 00000010$ | Thread scheduling        |

| 0x80000003 | 0x1000 00000011         | Report output activation |

Table 4.3: CR7 values activating the performance interface.

Every op-code expects an additional parameter in register EAX. This parameter is used as 32-bit key to allow the inspection of multiple processes simultaneously. As soon as the performance unit is activated, it counts

- the number of times the process was scheduled,

- the number of machine code instructions (supervisor and user) executed,

- the number of milliseconds the process was running (measured on the host system),

- TLB misses, i.e. the number of times the memory management unit had to navigate through the page hierarchy to resolve the physical address of a virtual page,

- TLB protection misses, i.e. the number of times the extended memory management unit had to navigate through the protection hierarchy to resolve the protection table entry of a virtual page,

- TLB protection hits, i.e. the number of times the extended memory management unit fetched the protection table entry from the TLB instead of navigating through the protection hierarchy, and

- the number of page faults and protection violations

that occurred during the execution of the process.

As soon as a monitored process stops execution (i.e. the *process closing* notification is triggered), Qemu prints a report to **stdout**. To limit the amount of output, all processes are inspected, but only data whose key has been *activated* through the *report output activation* notification is actually printed.

#### **Debugging extension**

Debugging an operating system's kernel is a cumbersome task, because most errors will inevitably lead to a complete system crash. This normally renders debugging output to logfiles or the system's console useless. To accommodate this situation, we have introduced two new *debugging interfaces* using bits 29 and 30 of the control register CR7 as shown in Figure 4.1.

The basic debugging interfaces (BDI) allows to send 29-bit debugging labels (bits 28 through 0 of the control register CR7) to the CPU. Qemu reacts to such an event and prints the label to stdout. This allows the programmer to track the control flow nicely and greatly improves error finding.

The *extended debugging interfaces* (EDI) works similar to the basic interface but allows up to 8 32-bit debugging labels to be passed simultaneously. Instead of passing the label to CR7 directly, they are taken from the processor's registers, depending on which of the 8 least significant bits of CR7 is set. Table 4.4 shows the mapping between CR7 bit-masks and registers used for debugging.

| Value      | Bit mask                       | Register |

|------------|--------------------------------|----------|

| 0x20000000 | $0x001000 \dots 000000$        | EAX      |

| 0x20000001 | 0x001000 000 <b>001</b>        | EBX      |

| 0x20000002 | 0x001000 000 <b>010</b>        | ECX      |

| 0x20000003 | $0 \times 001000 \dots 000011$ | EDX      |

| 0x20000004 | 0x001000 000100                | ESP      |

| 0x20000005 | $0x001000 \dots 000101$        | EBP      |

| 0x20000006 | 0x001000 000110                | ESI      |

| 0x20000007 | 0x001000 000111                | EDI      |

Table 4.4: CR7 values printing individual register values using the *extended* debugging interface.

### 4.2 Kernel adaptions

To allow the individual components of our extended architecture to provide the protection hierarchy to the CPU and synchronize executing threads with the protection tables, we had to hook several functions in the operating system. For this, we used the Linux kernel, since it allows easy inspection and modification of the source code.

Since compiling the whole kernel is a time consuming process, we did not include all of our extensions in the kernel's code directly. We rather decided to introduce a struct holding function pointers and a set of stub-functions that can be used to call these functions. By default, all function pointers dereference into an empty function. This leaves the original kernel intact, introducing only a negligible performance impact.

All code instrumenting our extended Mondrian memory protection was implemented inside a loadable kernel module. On module insertion, all necessary function pointers are redirected into appropriate functions inside the module. Likewise, all pointers are reset to their original value when the module is removed. This allows the code to be tested and exchanged easily without recompiling or restarting the whole system and thus greatly accelerates the development cycle.

Furthermore, the kernel internal structs task\_struct and mm\_struct were enlarged by two data pointers to let the protection system store thread- and task-specific data, respectively.

#### Task creation and destruction

The kernel uses four different routines to handle the creation and destruction of a process or thread: dup\_task\_struct (called by copy\_process during the fork or vfork system calls) calls the thread initialization routine for every thread created. A hook inside this function allows the protection module to allocate memory for the thread-specific data pointer stored inside task\_struct. Likewise, mm\_init calls the task-specific initialization routine, if the fork system call creates a new process (i.e. does not create a sub-thread for the current process).

free\_task and mmdrop call the functions freeing the respective memory structures. Note that despite what the names suggest, dup\_task\_struct and task\_struct are *thread*-specific, because in Linux every thread is a full standalone task that shares certain memory regions with other tasks. Thus, mm\_struct and mm\_init are *process*-specific.

#### **Process execution**

The execve system call can be used to start new applications. Linux does this by replacing the code section of the currently executing program and resetting all memory regions used by the process. During the call to execve, Linux internally calls the thread- and task-creation hooks. This manages the resetting of all memory regions automatically as described in the previous section.

In Section 6.1, we discuss the performance penalty introduced by the extended Mondrian memory protection. To minimize this overhead, the protection hierarchy is maintained but not activated (refer to Section 3.1 for protection activation), by default. During the *process execution* hook in our module, the binary's filename is used to determine if protection should be activated. More precisely, the protection is activated if the filename matches the simple "^.\*/detrace\$" regular expression. This allows us to use the extended Mondrian memory protection for targeted programs only by using a symbolic link named ./detrace connected with the real application's binary file.

Using the same filename-based activation logic, the kernel uses the process execution hook to *activate* Qemu's performance measuring extension. The location of the thread's mm\_struct structure is used as key, because it is shared by all threads of a process. Thus, Qemu is able to accumulate the statistics for a complete application.

A last operation done by this hook is to initialize protection of the process' stack by expanding its size from 0 to the stack's default size. Stack expansion will be described in more detail shortly.

### Thread scheduling

In the Linux kernel, the function \_\_switch\_to is used to change the currently executing process. A hook, placed inside this function, allows the module to load the correct protection hierarchy into memory and set control registers CR5 and CR6 and the read- and write-masks used for protection examination appropriately. The specific values set depends on what the protection system is currently being used for. In Chapter 5, we describe a few exemplary applications based on our generic framework and deal with how these registers and masks have to be set.

Similar to process execution, the thread scheduling hook notifies the perfor-

mance interface about the thread switch, also.

### Page allocation / deallocation

The Linux kernels offers two possibilities for user applications to allocate new memory pages: For one thing, the mmap system call can be used to allocate memory regions explicitly. For another, the kernel automatically expands an application's stack if insufficient memory was allocated previously.

Each page that is *mmapped* into the memory context of the running application invokes a function hook inside do\_mmap\_pgoff. The protection module will then insert the new page into the protection directory and protection table, appropriately. The new entry is marked to be using low granularity protection and its protection label is set to the value currently stored in control register CR5.

When an application pushes large amounts of data onto stack memory, the stack's base address is likely to exceed the pages that were allocated for this purpose. Since breaching this limit usually accesses an unmapped memory area, the CPU will, in turn, raise a page fault. Linux handles this situation by calling the expand\_stack function that simply allocates another page for stack memory and continues execution of the application. Similar to do\_mmap\_pgoff, expand\_stack uses a function hook to call the stack expansion code inside the protection module. The module will add all newly inserted pages between the previous and new stack base address into the protection hierarchy and initialize the protection table's entries.

Alike the explicit allocation of memory pages, the do\_munmap kernel function contains a hook to notify the protection module, as well. In contradiction to the allocation process, deallocation is a two-step process, however: In a first step, the kernel informs the module that a certain page is about to be removed. This step is necessary because some functions require to have memory pages mapped at a specific address. If this address, however, has previously been mapped by our module to hold protection information of a page using high granularity protection, mapping the address once again either fails or overwrites the stored protection labels.

To accommodate this situation, the protection module *relocates* the protection page by allocating a new page, copying its content to the new location, and adjusting the protection hierarchy accordingly. In the second step, the page is finally taken off the protection hierarchy and its protection page, if present, is freed.

#### System call interface

Our extended Mondrian memory protection adds a new system call to the Linux kernel. This sys\_prottable, with signature

```

1 long sys_prottable(

2    int mode,

3    int val1,

4    int val2,

5    unsigned long __user *ret);

```

uses the first parameter mode to provide a set of sub-functions using the multiplexer pattern. Amongst other functionality, commonly used during the debugging of our implementation, the system call offers the following functions:

SYS\_\_NOTIFY\_FREE: Allows to reset protection information of a range of addresses. A reset or *clear* protection label contains a special bitmask that will trigger a protection violation on the next access to the memory. The fault handler, described in the next section, can use this bitmask information and overwrite the protection label with the value currently stored in CR5.

**SYS\_\_NOTIFY\_TRANSFER\_OWNERSHIP**: Changes the protection labels of a range of addresses to a specified value.

**SYS\_\_NOTIFY\_COPY\_OWNERSHIP**: Copies the protection labels of a range of addresses to another range of addresses.

SYS\_\_NOTIFY\_RANGE\_DISABLE\_PROTECTION: Sets a special bitmask to the protection labels of a range of addresses. When the fault handler detects a protection violation on such a *disabled* address, the fault is ignored and access is granted.

SYS\_\_SET\_PROTECTION\_ATTRIBUTES: Allows to activate or deactivate the extended Mondrian memory protection on the currently executing thread or all threads of the currently executing process.

SYS\_\_NOTIFY\_LONGJMP: This function is used by the stack protection system described in Chapter 5. It works similar to SYS\_\_NOTIFY\_FREE but only manipulates certain bits of the protection label.

SYS\_\_GET\_PROTECTION\_LOG: This function is used by the race condition detection system described in Chapter 5. It copies certain data about the running process gathered by the kernel into a user provided memory region.

SYS\_\_NOTIFY\_LOCK: This function is used by the race condition detection system, also. It is used to notify the system about a change of an user-land synchronization object. To allow the notification of kernel synchronization objects, kernel code may use a lock notification hook.

Although some of these functions can be emulated by user code using the protection information manipulation instructions mentioned in Section 3.3, using a system call has two advantages: For one thing, handling protection information using CR7 manipulation is a non-trivial and error-prone job. The well-defined and tested interface facilitates this to a large extend. For another thing, the user-land code can only manipulate 4 bytes at a time. Besides being a much slower approach, it does not take into account the protection granularity of the page. If, for instance, the protection label of a whole page should be changed and the page uses low granularity protection, the SYS\_\_NOTIFY\_TRANSFER\_OWNERSHIP function can do this by changing the page's protection table entry only.

#### Protection fault handling

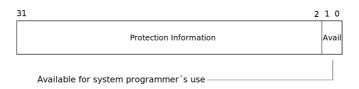

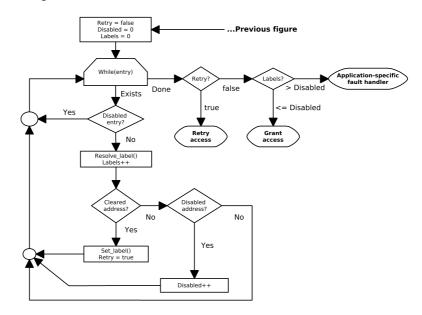

As can be seen in Table 4.2, our extended Mondrian memory protection uses bit 5 of the page fault error code to differential between casual page faults and protection violations. For this reason, the do\_page\_fault function, called by the *interrupt handler*, includes a hook calling the protection fault handler. This protection fault handler can be used to implement various protection schemes. However, every handler includes a base system that extracts information about the pending protection violation. Furthermore, it enforces certain mandatory constraints to ensure stability of the operating system. Figures 4.2 and 4.3 show the flow chart of this handler code. In the remainder of this chapter, we describe this common base system, whereas the individual application-specific fault handlers are described, along with their respective systems, in Chapter 5.

The first constraint, the base fault handler has to ensure, is that the kernel is not running in an atomic context. Code running in such a context may not

Figure 4.2: Upper half of the common protection fault base handler.

execute any functions that might cause the current thread to be suspended. Regardless of how the application-specific fault handler intends to react to the protection violation, the base handler immediately stops its execution in such a situation. Access to the memory is granted using the read-and-clear CPU flags introduced in Section 3.2. Thus, tough unlikely, it is possible that malicious code accesses protected memory regions while the kernel is running in an atomic context. Although this weakens our implementation of the memory protection architecture to a small degree, we accept this for the sake of maintaining the system's stability easily.

Next, the base fault handler checks if the protection violation is due to an unallowed user code manipulation of a protection label. As described in Section 3.1, the protection module can detain non-supervisor code from using the protection information manipulation instructions. Furthermore, every *direct* memory access to a protection page by code running in ring3 is handled as well. In both case of illegal access, the base fault handler stops the malicious process by causing a *segmentation fault*, without consulting the application-specific fault handler.

Figure 4.3: Lower half of the common protection fault base handler.

After ensuring that protection for the current thread is activated, the fault handler's base system fetches all protection table entries necessary for the protection examination. In case at least one entry indicates the use of low granularity protection, the system has the following three options:

- 1. If any entry's protection label indicates a *cleared* page, the protection label is set to the value stored in control register CR5 and the access is *retried*.

- 2. If *every* entry's label indicates that protection for the whole page should be *disabled*, the access is *granted* in the same manner as described for protection violations in an atomic context.

- 3. If none of the two previous options match, the low granularity protection of every accessed page is expanded into high granularity. There-

fore, a protection page is allocated, filled with the entry's protection label, entered into the protection hierarchy, and protected from direct accesses from user code. Eventually, the access is also *retried*.

Otherwise, if every page accessed has already been expanded to high granularity protection, the protection labels are loaded from the appropriate protection pages. The code can identify the number of protection labels necessary by looking at the address and error code provided for the protection violation: By default, only one protection label is resolved. However, both, having bit 6 of the error code set or an unaligned fault address requires an additional label to be examined. The predominant case only requires one single label, the maximum of three labels, on the other hand, is very rare. It can only happen when a protection violation is raised during an unaligned quad-byte access.

For every protection label, options 1 and 2 described above handling *cleared* and *disabled* memory addresses are checked once more. If neither of them can resolve the protection violation, the protection fault base handler has done its job and the application-specific fault handler is called.

## Chapter 5

# Application of extended Mondrian memory protection

We claim that our extended Mondrian memory protection architecture provides a versatile framework to implement different techniques that allow processes (and threads) to protect sensitive memory regions. These memory regions can be control data (such as return addresses), process management information, or thread-shared data buffers. To demonstrate the versatility of our system, we built three applications on top of the proposed architecture. More precisely, Sections 5.1 and 5.2 show how stack and heap areas can be protected against memory corruption attacks. In Section 5.3, we discuss how the architecture can be leveraged to implement a race condition detection system. While each system application is not novel *per se*, we show how easy each mechanism can be expressed in the context of our protection scheme. This should help the reader understand and appreciate the flexibility and expressiveness of our novel system architecture.

#### 5.1 Stack Protection

The problem of insufficient validation of user-provided input data has been known for a long time. Although many different techniques have been introduced to protect programs against memory corruption, buffer overflow and stack smashing exploits still belong to one of the most popular attack vectors. A possible way to leverage our architecture to protect against a buffer overflow that targets a return address on the stack is to make this address writeprotected. That is, the compiler can use our extended memory protection system to add code to the function prologue that sets the return address as read-only. Thus, when there is a vulnerability inside the body of the function, the attacker cannot overwrite the return address and hijack the control flow of the program. Of course, when the function returns, the memory location on the stack that stores the return address has to be unprotected (i.e., write access has to be enabled again).

In addition to protecting only the function return addresses, we can also add protection boundaries around each local buffer. Such protection boundaries (often called canaries [15]) are realized as write-protected words that are put around each local buffer. As a result, whenever the process attempts to access an out-of-bounds value directly before or after the buffer, the write-protected canary is accessed. This raises a protection fault. Canaries around a local buffer protect against overflows that do not attempt to modify the function return address, but that target another local variable that is adjacent to the exploited buffer.

To add the necessary code that uses our architecture to protect the return address and the local buffers, we have modified the code generation back-end of the tiny c compiler [9]. The protection code is quite straightforward. To ensure that a certain memory word (such as the return address or a boundary around a buffer) cannot be modified, we set the most significant bit of its protection label. Moreover, the kernel component sets the most significant bit of the write-mask and clears this bit of the control register CR5. Thus, every write access to a canary will lead to a mismatch of the protection and control tokens, causing a protection violation. Likewise, the most significant bits of the canary words are cleared on function exit, restoring the original protection label of the memory addresses.

To see an example for the way in which our protection works, consider the following source code fragment:

```

int function(char arg1, int *arg2)

{

char *p;

char buffer[128];

....

}

```

The symbolic machine code that is generated for this code can be seen below. Note that the compiler inserts 4-byte canary words before and after the buffer statically allocated on stack. Moreover, the function return address and the saved stack pointer (frame pointer) are write protected.

```

<function>:

1

; function prologue

\mathbf{2}

%ebp

push

3

mov

%esp, %ebp

4

$0x8c, %esp

sub

5

6

; protect function's return address

7

; and saved stack pointer

8

$0x8000000, %ebp + $0x4

prot_or

9

$0x8000000, %ebp

prot_or

10

11

; protect canaries around 'buffer'

12

$0x8000000, %ebp - $0x8

prot_or

13

$0x80000000, %ebp - $0x8c

prot_or

14

15

; original code of function

16

17

. . .

18

; unprotected canaries

19

prot_and $0x7fffffff, %ebp - $0x8c

20

prot_and $0x7fffffff, %ebp - $0x8

21

22

; protect function's return address

23

; and saved stack pointer

24

prot_and $0x7fffffff, %ebp

25

prot_and $0x7fffffff, %ebp + $0x4

26

27

; function epilogue

28

leave

29

ret

30

```

The memory layout on the stack generated by a regular compiler, a compiler that uses StackGuard (with a canary before the function return address), and our proposed technique are shown in Figure 5.1.

#### tcc stack protection extension

tcc is a compiler for the i386 CPU instruction set on Windows and Unix

| Stack memory    | Stack memory    | Stack memory    | Prot. page |

|-----------------|-----------------|-----------------|------------|

|                 |                 |                 |            |

| arg2            | arg2            | arg2            | r/w        |

| arg1            | arg1            | arg1            | r/w        |

| Return addr.    | Return addr.    | Return addr.    | read-only  |

| Saved esp       | Saved esp       | Saved esp       | read-only  |

| р               | Canary word     | р               | r/w        |

| buffer[124-127] | р               | Canary word     | read-only  |

|                 | buffer[124-127] | buffer[124-127] | r/w        |

| buffer[4-7]     |                 |                 |            |

| buffer[0-3]     | buffer[0-3]     | buffer[0-3]     | r/w        |

|                 |                 | Canary word     | read-only  |

|                 |                 |                 |            |

| (a)             | (b)             | (c)             |            |

Figure 5.1: Stack layouts with (a) no, (b) StackGuard [15], and (c) our extended Mondrian memory protection.

systems. Because it is very small<sup>1</sup>, it allows easy manipulation and extension of its source code. Furthermore, it is extremely fast[9] when compared with other compilers such as gcc [2].

To generate the output binary, the compiler uses a straight-forward one-time pass through the source code: Starting at the top of each input file, the parser generates a tree of *symbols* for a small block of input code and passes it to the code generator. Typically, such a small block consists of a single-line c instruction, a variable allocation, or a function head declaration. The code generator then traverses the generated symbol tree recursively and writes machine code directly to the output buffer.

If the compiler cannot resolve a reference (e.g. to a externally defined variable or function), the memory address for the variable, jump or function call is temporarily filled with a default value and its location in the output buffer is stored in a global *relocation list*. After all input files have been handled, the compiler uses this list to search for previously undefined references and overwrites the temporary values with the correct memory addresses found by the parser.

<sup>&</sup>lt;sup>1</sup>The whole source, including *lexer*, *parser*, code generator and *linker*, is only about 30000 lines of code.

Besides the necessity for a relocation list, this one-pass approach introduces another difficulty, that is particularly interesting for our stack protection extension: When generating code for a function prologue, the code generator does not have any knowledge about the amount of memory that should be allocated on stack for local variables in the function. This is due to the fact that the function body itself has not been analyzed by the parser. Consider the following, extended code snippet from before:

```

int function(char arg1, int *arg2)

1

{

^{2}

char *p;

3

char buffer [128];

4

5

6

. . . . .

p = buffer;

7

buffer[27] = 'c';

8

. . . . .

9

10

11

. . . . .

char c = arg1;

12

13

. . . . .

}

14

```

and the generated function prologue

| 1 | <fund< th=""><th>ctic</th><th>on &gt;</th><th>:</th><th></th><th></th><th></th><th></th></fund<> | ctic | on > | :  |    |    |      |             |

|---|--------------------------------------------------------------------------------------------------|------|------|----|----|----|------|-------------|

| 2 | 55                                                                                               |      |      |    |    |    | push | %ebp        |

| 3 | 89                                                                                               | e5   |      |    |    |    | mov  | %esp,%ebp   |

| 4 | 81                                                                                               | еc   | 88   | 00 | 00 | 00 | sub  | \$0x88,%esp |

| 5 | • •                                                                                              |      |      |    |    |    |      |             |

When the code for decrementing the stack pointer by 0x88 (128 byte for the array, 4 byte for the pointer, and another 1 + 3 byte for variable c and alignment) is generated, the local variable declarations have not been analyzed. Even if the parser continues to analyze the source code until the first non-variable declaration instruction is found before generating the function prologue, the declaration of variable c still remains hidden.