The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

DISSERTATION

## Heuristic Optimisation Methods for System Partitioning in HW/SW Co-Design

Conducted for the purpose of receiving the academic title 'Doktor der technischen Wissenschaften'

Submitted at Vienna University of Technology Faculty of Electrical Engineering and Information Technology

by

Dipl.-Ing. Bastian Knerr Talgasse 8/13, 1150 Vienna, Austria born in Püttlingen, Germany, September 3, 1976 Matriculation number: 0327662

Vienna, July 2008

.....

Advisor

Univ.Prof. Dipl.-Ing. Dr.techn. Markus Rupp Technische Universität Wien Institut für Nachrichtentechnik und Hochfrequenztechnik

Examiner

Univ.Prof. Dr.habil. Christoph Grimm Technische Universität Wien Institut für Computertechnik

### ABSTRACT

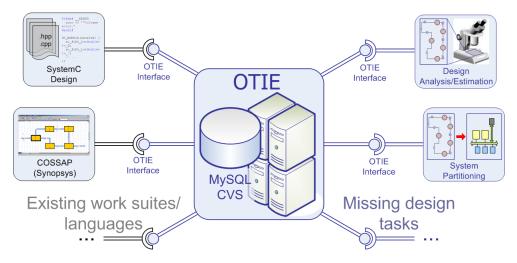

Nowadays, the design of embedded systems is confronted with the combination of complex signal processing algorithms on the one hand and a variety of computational intensive multimedia applications on the other hand, while time to product launch has been extremely reduced. Especially in the wireless domain those challenges are stacked with tough requirements on power consumption and chip size. Unfortunately, design productivity did not undergo a similar progression and therefore fails to cope with the heterogeneity of modern hardware architectures. Until now, electronic design automation do not provide for complete coverage of the design flow. In particular crucial design tasks as high level characterisation of algorithms, floating-point to fixed-point conversion, automated hardware/software partitioning, and automated virtual prototyping are not sufficiently supported or completely absent. In recent years a consistent design framework named Open Tool Integration Environment (OTIE) has been established to address the most crucial shortcomings of the wide spread design problems in this field. As integral part of the OTIE framework powerful tool chains exist that support high level estimation techniques for algorithm characteristics, static code analysis, automatic generation of virtual prototypes, floating-point to fixed-point conversion, and so forth. A very substantial ingredient of OTIE was missing until now: a rich library for architecture modelling of embedded system and algorithms for their precise partitioning and scheduling. Therefore, this thesis examines the research field of system partitioning of embedded systems in the wireless design domain.

This field started to find strong advertence of scientists about fifteen years ago. Since a multitude of formulations for the partitioning problem exist, the same multitude could be found in the number of strategies that address this problem. Their feasibility is highly dependent on the platform abstraction and the degree of realism that it features. This thesis identifies the most mature and powerful approaches for system partitioning and to some degree task scheduling in order to integrate them into the OTIE framework. The contribution of this work involves a detailed platform abstraction that combines a high degree of realism with the flexibility to compose arbitrary multi-core multi-bus structures and the theoretical underpinning of the system partitioning in wireless embedded system design as combinatorial optimisation problem. Eventually, the implementation and improvement of the most popular strategies, and the introduction of entirely new algorithms for the system partitioning and scheduling problem is accomplished.

### ZUSAMMENFASSUNG

Der Entwurf von eingebetteten Systemen ist heutzutage konfrontiert mit einer Kombination aus hochkomplexen Signalverarbeitungsalgorithmen und einer Vielzahl von rechenintensiven multimedialen Anwendungen. Erschwerend kommt hinzu, dass die Entwicklungszeit bis zum fertigen Produkt dramatisch verkürzt wurde. Besonders innerhalb der mobilen Sparte, die Mobiltelefone, PDAs, und Kameras umfasst, werden diese grundsätzlichen Widrigkeiten noch erschwert durch beträchtliche Anforderungen bezüglich Leistungsaufnahme und Baugröße. Leider konnte die Entwurfsproduktivität nicht mit den ansteigenden Anforderungen Schritt halten, und kämpft bis heute mit der Heterogenität moderner Hardwarearchitektur. Werkzeuge für die Entwurfsautomatisierung offenbaren breite Lücken in ihrer Abdeckung der Entwurfsabfolge, insbesondere wurden bisher folgende Aufgaben nicht zufriedenstellend gelöst: Algorithmencharakterisierung auf höchster Abstraktionsebene, Konvertierung von Fließkomma- zu Fixpunktdarstellung, Systempartitionierung, und Virtual Prototyping. In den letzten Jahren wurde im Christian Doppler Labor für Designmethodik von Signalverarbeitungsalgorithmen eine Entwurfsumgebung, OTIE, entwickelt, die in konsistenter Weise die kritischsten Mängel des Entwurfsprozesses in diesem Bereich zu beheben versucht. Bis auf eines wurden die zuvor genannten Aufgaben mit OTIE in bemerkenswerter Weise gelöst. Der fehlende Entwurfsschritt Systempartitionierung vereint mit einer flexiblen Architekturmodellierung stellt das Thema dieser Dissertation dar.

Systempartitionierung ist ein Forschungsgegenstand, der in den letzten 15 Jahren beträchtliche Aufmerksamkeit von Forschungsgruppen im elektronischen Systementwurf erhielt. Aus diesem Grund existiert eine ebenso große Anzahl spezifischer Problemformulierungen wie jeweiliger Lösungsstrategien. Ihre Anwendbarkeit variiert stark mit dem gewählten Abstraktionsgrad des Plattformmodells und dessen Wirklichkeitstreue. In dieser Arbeit werden die tauglichsten Ansätze für die Partitionierung von Prozessgraphen und in kleinerem Ausmaß jene für deren Ablaufplanung identifiziert, um diese dann in OTIE zu integrieren. Ein detailliertes Architekturmodell wird vorgestellt, das außergewöhnliche Wirklichkeitstreue mit großer Flexibilität vereint. Mit diesem ist es nun möglich beliebige heterogene Plattformstrukturen zu modellieren, in denen z.B. mehrere Prozessoren, FPGAs, und ASICs mittels mehrerer Busse oder anderer Datenkanäle verbunden werden. Basierend auf diesem Fundament wird das Partitionierungsproblem analysiert und als kombinatorische Mehrzieloptimierung definiert. Weitergehend werden jene Graphen, die für eingebettete Systeme typisch sind, analysiert und deren Eigenschaften herausgearbeitet. Mit Hilfe der erlangten Erkenntnisse werden in dieser Arbeit neue spezialisierte Algorithmen für Partitionierung und Ablaufplanung entwickelt und bestehende Konzepte und Techniken verbessert.

## ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor Professor Markus Rupp for his persistent encouragement, support, and understanding of my research. I also would like to thank Professor Christoph Grimm for accepting to act as the examiner and, of course, for his valuable comments that greatly improved the quality of this thesis.

Whenever you start thinking about doing research, writing theses, or discuss decent music and the passage of being, you will tremendously benefit from sharing your office with Dr Martin Holzer. Great friend, great colleague!

This work has been funded by the Christian Doppler Laboratory for Design Methodology of Signal Processing Algorithms.

# CONTENTS

| 1 | Intro<br>1.1<br>1.2<br>1.3               | Contril                                         | tion                                                                                                                                                                                                                                                                                                                                                                                                                              | 1<br>1<br>5<br>9                                                                                                                                                       |

|---|------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | -                                        | e of the<br>Target<br>2.1.1                     | Art in HW/SW Co-Design1Architectures in Embedded Systems1Platform Composition1                                                                                                                                                                                                                                                                                                                                                    | .1<br>.3<br>.3                                                                                                                                                         |

| 3 | Syste<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | 3.1.1<br>3.1.2<br>Classic<br>Flexible<br>System | I Graphs in Embedded System Design       2         Process Graphs       2         Synchronous Data Flow Graphs       2         al Platform Model for Hardware/Software Partitioning       2         e Platform Model for Heterogeneous Embedded Systems       2         a Graph Enrichments       3         m Formulation       3         The Classical Graph Partitioning Problem       3                                        | .9<br>20<br>21<br>23<br>25<br>26<br>30<br>22<br>33<br>4<br>9                                                                                                           |

| 4 | Algo<br>4.1<br>4.2<br>4.3                | Specifi<br>Algorit<br>4.2.1<br>4.2.2            | c Properties of Typical Process Graphs       4         hms for Scheduling       4         Classical Scheduling Techniques       4         Local Exploitation of Parallelism       4         hms for System Partitioning       5         Exhaustive Search       5         Gradient Search       5         Global Criticality/Local Phase (GCLP) Algorithm       5         Simulated Annealing       6         Tabu Search       6 | 1<br>2<br>6<br>7<br>8<br>4<br>6<br>7<br>8<br>4<br>6<br>7<br>8<br>4<br>6<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7<br>8<br>7 |

|    | 4.4                                                          | 4.3.7<br>4.3.8<br>4.3.9<br>Criticis                                  | Restricted Range Exhaustive Search                                                                                                                                                                                                                                                                                                                                                 | <br>    | . 87<br>. 92                                                |

|----|--------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------|

| 5  | Cond                                                         | clusions                                                             |                                                                                                                                                                                                                                                                                                                                                                                    |         | 99                                                          |

| Aı | open                                                         | dices                                                                |                                                                                                                                                                                                                                                                                                                                                                                    |         | 103                                                         |

| A  | The                                                          | Open T                                                               | ool Integration Environment                                                                                                                                                                                                                                                                                                                                                        |         | 105                                                         |

| В  | Typi<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8 | Genera<br>Digital<br>Microc<br>Applica<br>Field F<br>Applica<br>Comm | mples of Architectural Components         al-Purpose Processors         Signal Processors         controllers         ation Specific Instruction Set Processors         Programmable Gate Arrays         ation Specific Integrated Circuits         unication Infrastructure         mic and Commercial Co-Design Frameworks         Design Languages         Co-design Frameworks | · · · · | 109<br>111<br>112<br>113<br>114<br>114<br>114<br>116<br>116 |

| С  | C.1<br>C.2                                                   | Typica<br>Genera                                                     | mbedded System Design<br>I Graph Structures in Embedded Systems                                                                                                                                                                                                                                                                                                                    |         | . 128                                                       |

| D  | D.1<br>D.2                                                   | Multi-µ<br>Preced                                                    | e Algorithms and Optimality<br>processor Scheduling                                                                                                                                                                                                                                                                                                                                |         | 136                                                         |

| E  | Nota<br>E.1<br>E.2<br>E.3                                    | Notation<br>List of                                                  | ariables, and Acronyms<br>on                                                                                                                                                                                                                                                                                                                                                       |         | . 140                                                       |

# LIST OF FIGURES

| 1.1  | Algorithmic complexity gap and design productivity gap                                               | 2  |

|------|------------------------------------------------------------------------------------------------------|----|

| 1.2  | Evolution of the cost span over the development time [8]                                             | 3  |

| 1.3  | Partitioning: Map functionality to platforms                                                         | 4  |

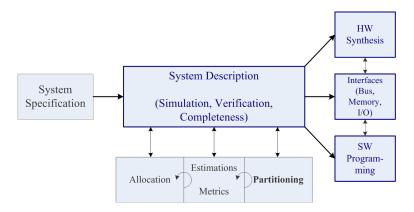

| 2.1  | Concept of System Level Design                                                                       | 12 |

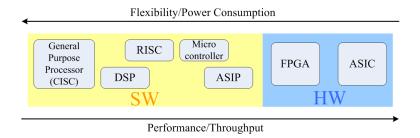

| 2.2  | Architectural components and their affiliation to hardware and software                              | 13 |

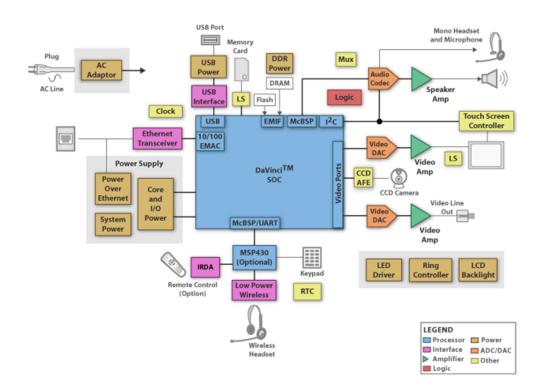

| 2.3  | Block structure of an System-on-Chip based design for a video phone [136]                            | 14 |

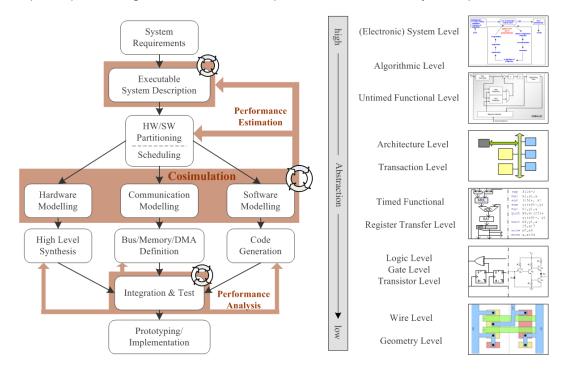

| 2.4  | Common abstraction levels and co-design flow for embedded systems                                    | 16 |

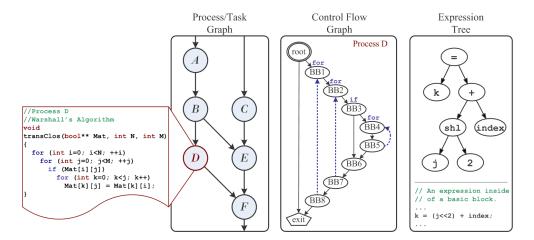

| 3.1  | System decomposed into hierarchical graph structures.                                                | 21 |

| 3.2  | Code fragment representation as parse and expression tree                                            | 23 |

| 3.3  | Example of a synchronous data flow graph and its decomposition into a single activation graph        | 24 |

| 3.4  | Common implementation architecture                                                                   | 25 |

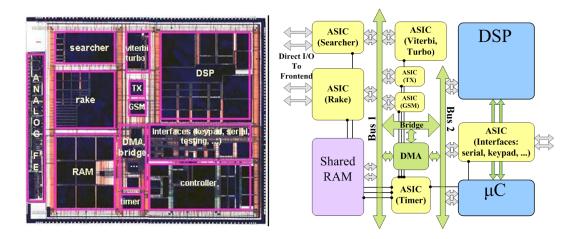

| 3.5  | UMTS+GSM baseband transceiver chip [53] and its platform abstraction                                 | 27 |

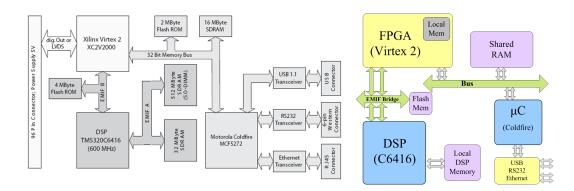

| 3.6  | Rapid prototyping board for MIMO OFDM channel emulation [103] and its platform abstraction.          | 28 |

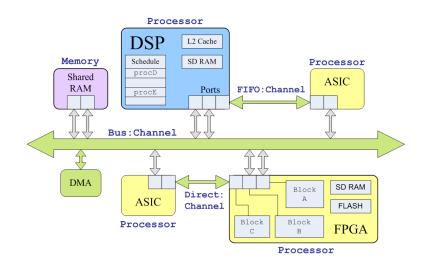

| 3.7  | Example of a heterogeneous architecture model                                                        | 30 |

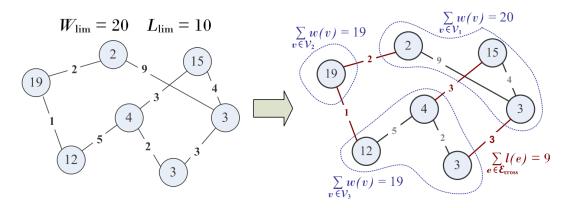

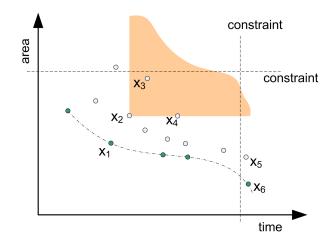

| 3.8  | Classical partitioning subject to constraints : $W_{\rm lim} \leq 20$ and $L_{\rm lim} \leq 10.~.~.$ | 33 |

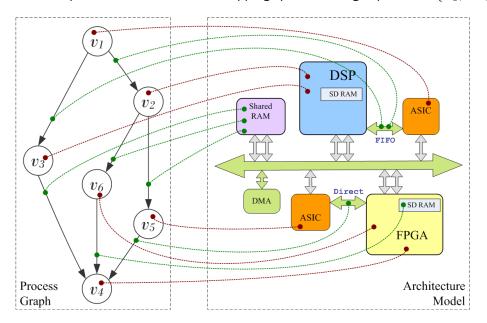

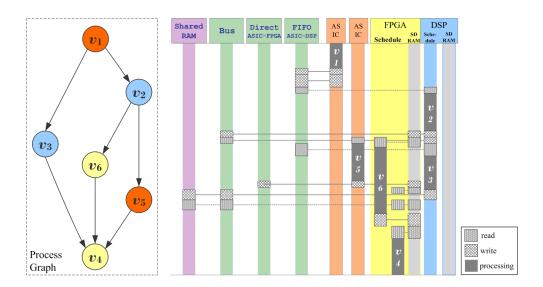

| 3.9  | Mapping between task graph and architecture model                                                    | 34 |

| 3.10 | Multi-resource schedule for a simple process graph                                                   | 40 |

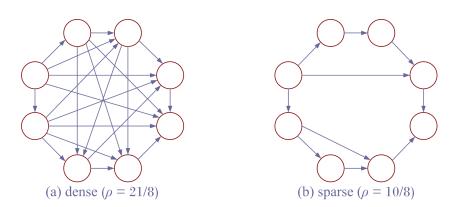

| 4.1  | Density of graph structures                                                                          | 43 |

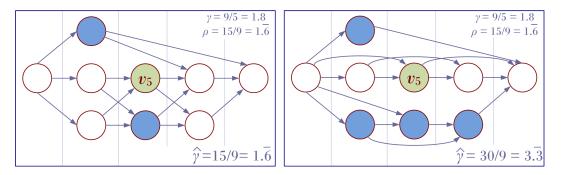

| 4.2  | Parallel vertices seen by vertex $v_5$                                                               | 44 |

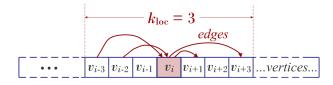

| 4.3  | The $k$ -locality graph property with $k_{ m loc}=3$ shown as vector                                 | 45 |

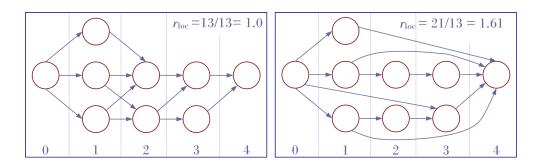

| 4.4  | Examples for the $\operatorname{rank}$ -locality of two different graphs according to (4.4)          | 46 |

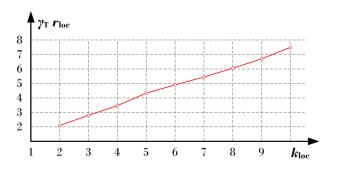

| 4.5  | Linear dependency between $\gamma_{ m T} r_{ m loc}$ and $k_{ m loc}$                                                               | 46 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

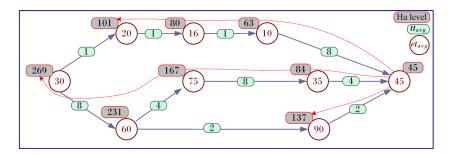

| 4.6  | Computation of Hu priority levels based on critical path analysis                                                                   | 47 |

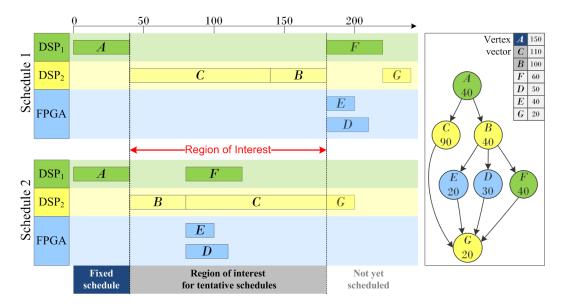

| 4.7  | LEP algorithm: two tentative schedules for the decision ${\cal B}$ first or ${\cal C}$ first                                        | 49 |

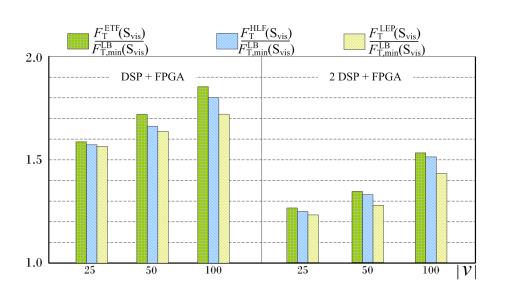

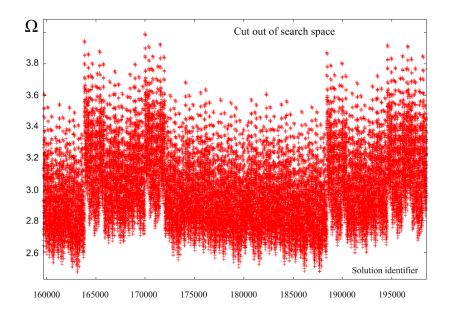

| 4.8  | Averaged global schedule lengths normalised to the global lower bound sched-<br>ule lengths over different mappings and graph sizes | 52 |

| 4.9  | Averaged global schedule lengths normalised to the global lower bound schedule length over degree of parallelism $\gamma_T$ .       | 53 |

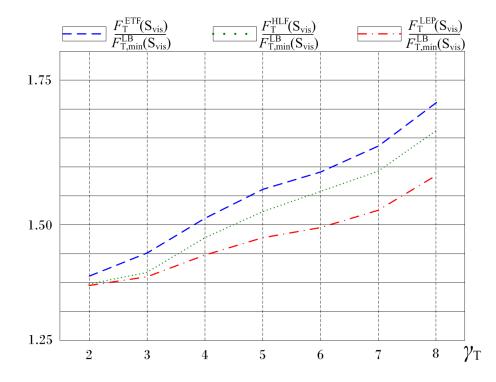

| 4.10 | A first impression of the multi-modality of the search space. $\hdots$                                                              | 55 |

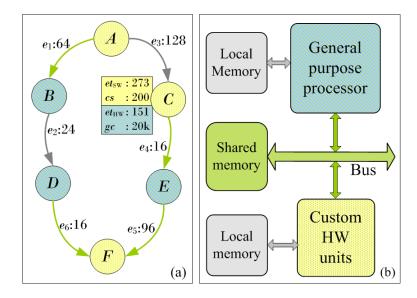

| 4.11 | (a) Process graph, annotated with characteristic values. (b) Typical platform model.                                                | 59 |

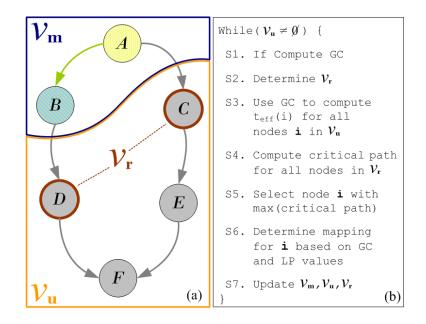

| 4.12 | (a) Process graph at a distinct stage of the GCLP algorithm. (b) Pseudo code for a single GCLP iteration.                           | 60 |

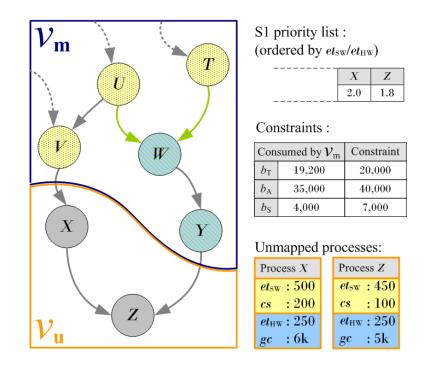

| 4.13 | Modification 2 (M2): Constructing the initial solution.                                                                             | 62 |

| 4.14 | Modification 3(M3): Precocious breaks.                                                                                              | 64 |

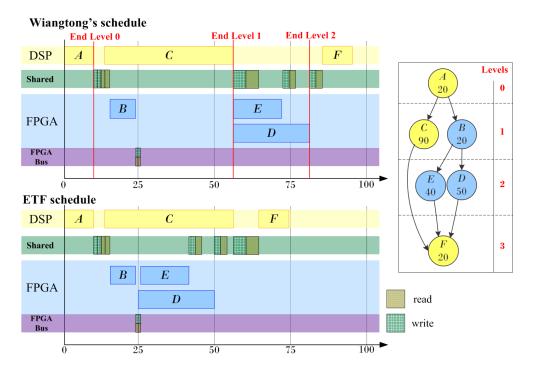

| 4.15 | Wiangtong's scheduling compared to a ETF                                                                                            | 69 |

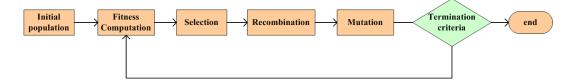

| 4.16 | 3-operator genetic algorithm                                                                                                        | 71 |

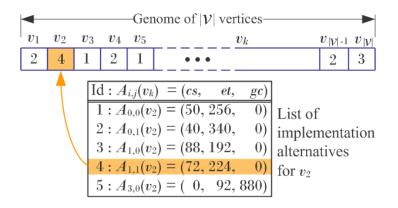

| 4.17 | Chromosome coding for the system partitioning problem                                                                               | 72 |

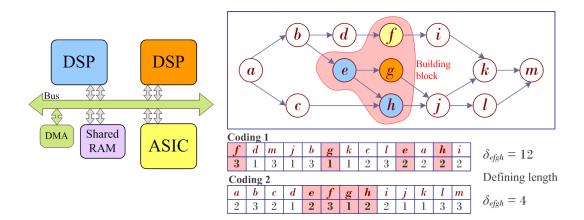

| 4.18 | Examples for bad (1) and good (2) chromosome codings                                                                                | 73 |

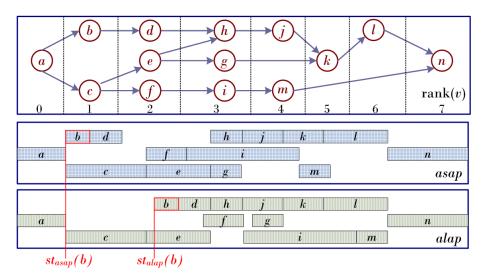

| 4.19 | Example graph with annotated ranks, $\operatorname{asap}$ and $\operatorname{alap}$ schedule. $\hdots$                              | 74 |

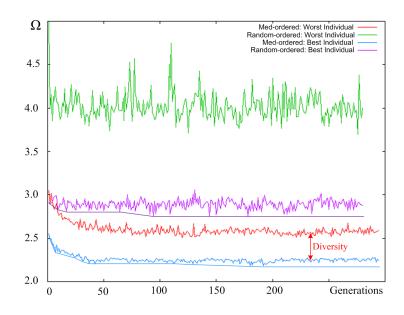

| 4.20 | Convergence behaviour for GAs with different genome codings                                                                         | 75 |

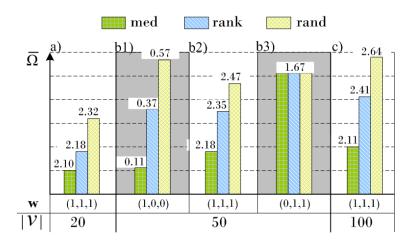

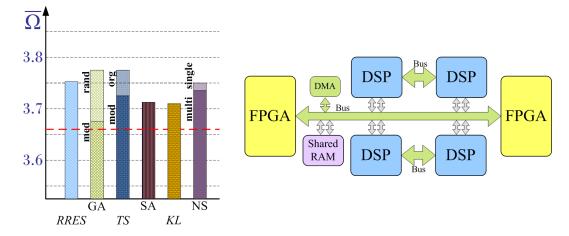

| 4.21 | Averaged cost $\overline{\Omega}$ for different genome codings on all graph sizes $ \mathcal{V}  = 20, 50, 100$                     | 76 |

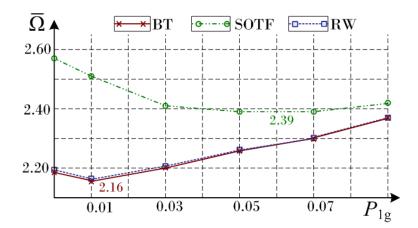

| 4.22 | Result for different selection schemes over varying mutation probabilities                                                          | 77 |

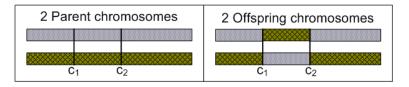

| 4.23 | Recombination via 2-point crossover with cut points $c_1, c_2, \ldots, \ldots$                                                      | 78 |

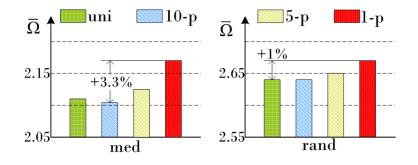

| 4.24 | Result for different recombination schemes for two genome orderings. $\ldots$ .                                                     | 78 |

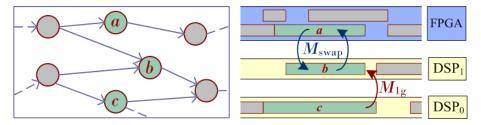

| 4.25 | Partial system graph and schedule: one-gene versus swap mutation. $\ldots$ .                                                        | 79 |

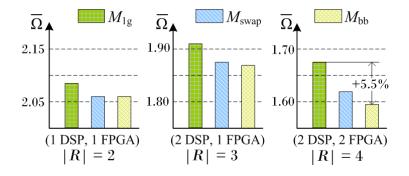

| 4.26 | Result for different mutation schemes $M_{1g}, M_{swap}$ , and $M_{bb}$ on three different platforms.                               | 80 |

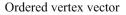

| 4.27 | Global optimality by locally optimal solutions                                                                                      | 81 |

| 4.28 | Moving window for the RRES on an ordered vertex vector                                                                              | 82 |

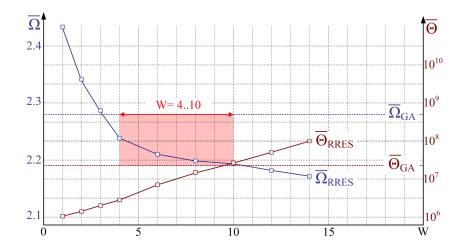

| 4.29 | Validity $\Psi$ , and cost $\overline{\Omega}$ for RRES and ES plotted over the window length $W.$                                  | 85 |

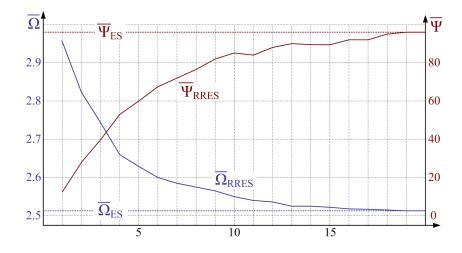

| 4.30 | Dependency between graph locality $k_{ m loc}$ (or $\gamma_{ m T} r_{ m loc}$ ) and performance for RRES.                           | 86 |

| 4.31 | Quality and run time of RRES and GA over window length for graphs with $ \mathcal{V}  = 100.$ | 88  |

|------|-----------------------------------------------------------------------------------------------|-----|

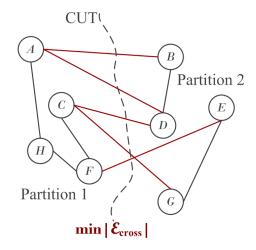

| 4.32 | Cut problem for a two-way partitioned graph.                                                  | 89  |

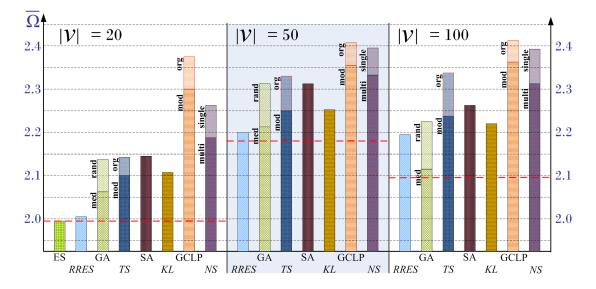

| 4.33 | Quality of all algorithms for different graph sizes for binary partitioning. $\ldots$         | 93  |

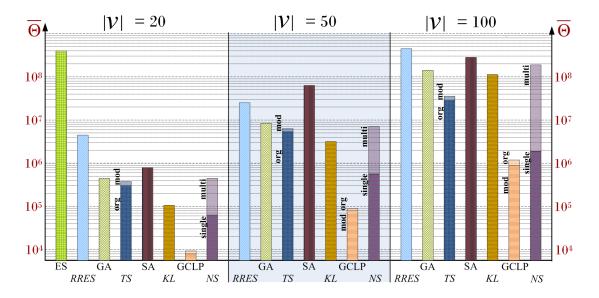

| 4.34 | Run time of all algorithms for different graph sizes for binary partitioning                  | 94  |

| 4.35 | Quality of all algorithms for different graph sizes for a heterogeneous platform.             | 95  |

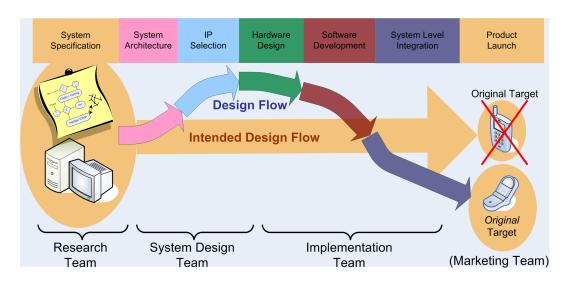

| A.1  | The meandering of the electronic design process.                                              | 106 |

| A.2  | The concept of the Open Tool Integration Environment (OTIE)                                   | 107 |

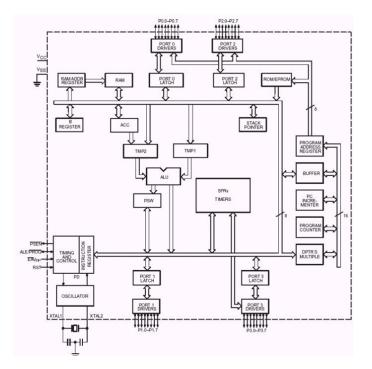

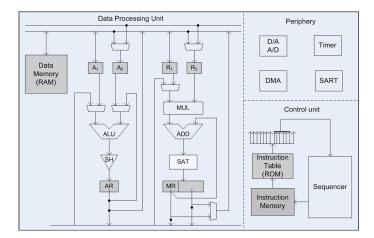

| B.1  | Block diagram of a state-of-the-art NXP 80C51 microcontroller [115]                           | 111 |

| B.2  | ASIP with Harvard architecture.                                                               | 112 |

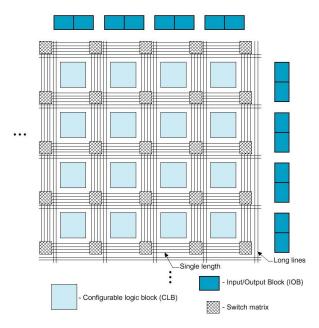

| B.3  | Structure of an FPGA.                                                                         | 113 |

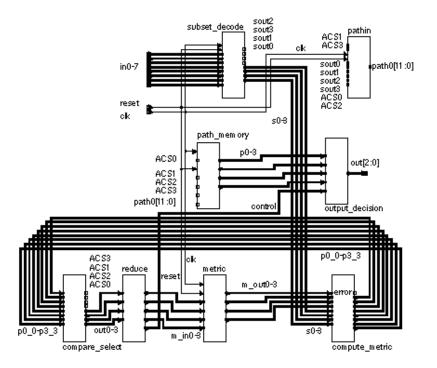

| B.4  | Core logic of an Viterbi decoder ASIC [128]                                                   | 115 |

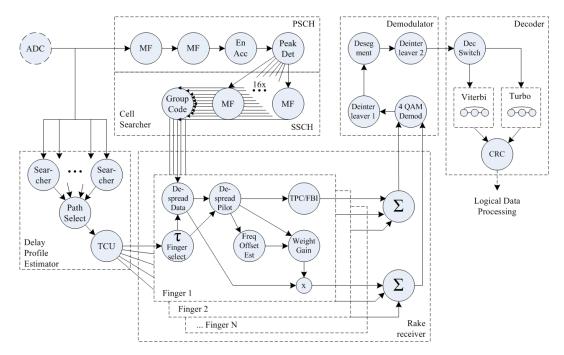

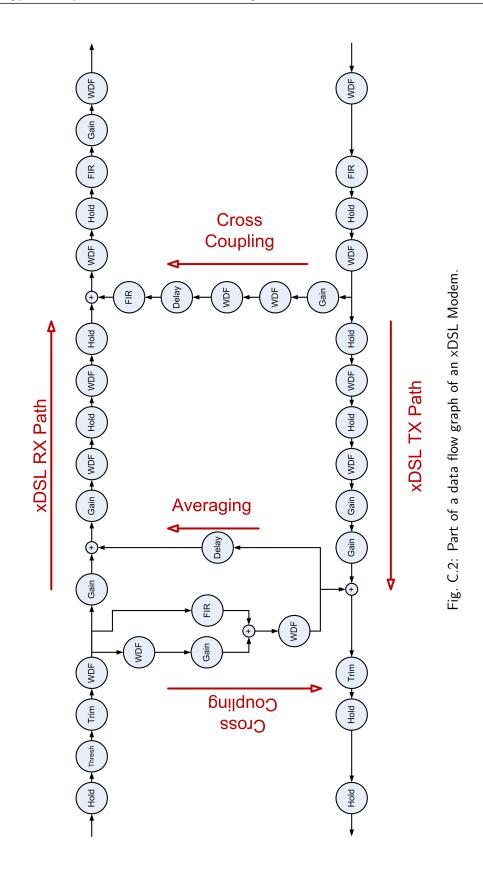

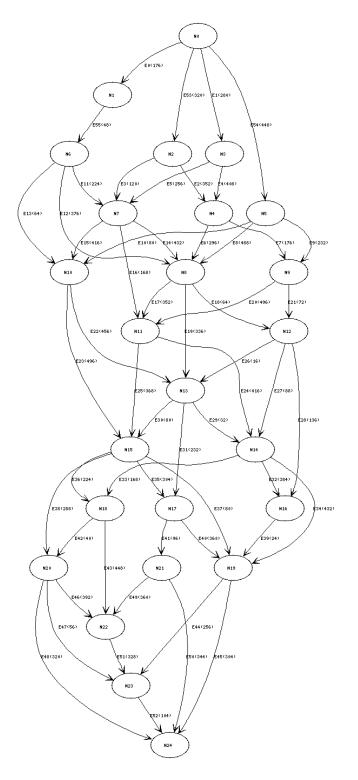

| C.1  | Part of the signal processing for an UMTS receiver                                            | 121 |

| C.2  | Part of a data flow graph of an xDSL Modem                                                    | 123 |

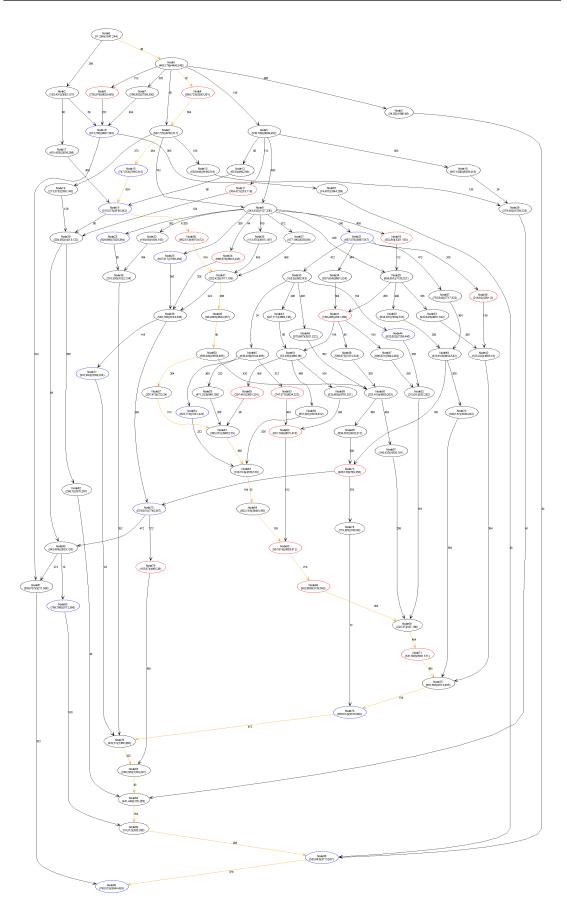

| C.3  | A realistic robot control process graph [79].                                                 | 125 |

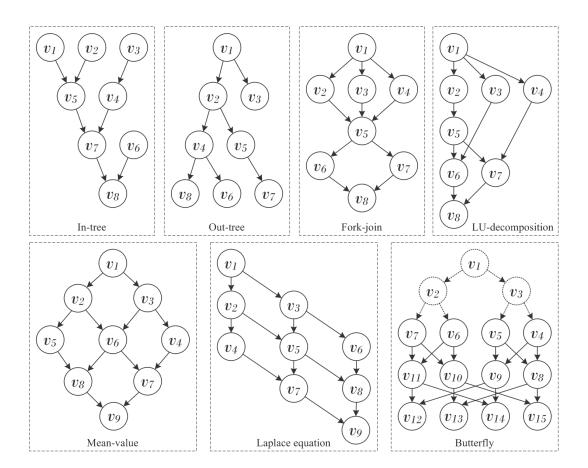

| C.4  | Seven task graph categories for signal processing defined in the literature [94, 142].        | 126 |

| C.5  | Acyclic $k$ -locality graph with $k_{\rm loc}=5,~ \mathcal{V} =25,~\rho=3$                    | 129 |

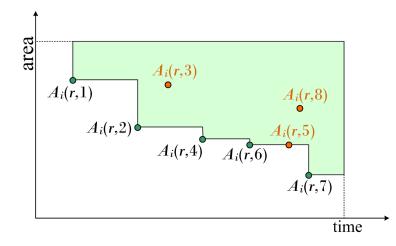

| C.6  | Pareto-optimal implementation alternatives of a process for a single resource $r$ .           | 131 |

| C.7  | SDF graph extensions                                                                          | 132 |

| D.1  | Pareto front for implementation alternatives with area-time trade-off                         | 137 |

# LIST OF TABLES

| 4.1  | Results obtained for exhaustive searches                                                      | 56  |

|------|-----------------------------------------------------------------------------------------------|-----|

| 4.2  | Results obtained for neighbourhood searches.                                                  | 58  |

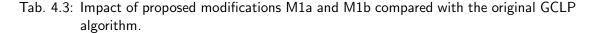

| 4.3  | Impact of proposed modifications M1a and M1b compared with the original GCLP algorithm.       | 62  |

| 4.4  | Impact on cost and validity percentage of M2                                                  | 63  |

| 4.5  | Effect of modification M3 on the run time                                                     | 65  |

| 4.6  | Impact of combined modifications M1a+M3 and M1b+M2 GCLP performance.                          | 66  |

| 4.7  | Results obtained for simulated annealing                                                      | 68  |

| 4.8  | Results obtained for tabu search, original and with LEP scheduling. $\ldots$ .                | 70  |

| 4.9  | Averaged cost $\overline{\Omega}$ obtained for RRES starting from different initial solutions | 84  |

| 4.10 | Results obtained for the RRES                                                                 | 87  |

| 4.11 | Results obtained for Kernighan-Lin                                                            | 92  |

| C.1  | Some characteristic values for the Cell Searcher                                              | 122 |

| C.2  | Some characteristic values for the Delay Profile Estimator                                    | 122 |

| C.3  | Typical cycle counts for filter code segments on a DSP                                        | 124 |

| C.4  | Possible ranges for process properties utilised in the graph generation engine.               | 130 |

### **1 INTRODUCTION**

On average every human being living in the industrialised world is almost permanently interacting with electronic systems and - usually - totally unaware of this fact. The last two decades of the past millennium witnessed an irresistible flood of electronics covering every aspect of modern life. Devices with a high visibility for the end user like notebooks, mobile phones, and PDAs mark only a small fraction of those electronic equipment the average person comes in touch with. Their overwhelming portion is represented by special purpose processors being embedded into larger devices, hence unifying omnipresence with invisibility. For example, the modern household is pervaded by processors controlling the dishwasher, the washing machine, the toaster, the vacuum cleaner, television, radio, etc. The proliferation of microelectronics in general, and embedded systems in particular, has percolated not only the personal but all commercial and industrial sectors, including logistics, communications, energy, transportation, security, mass media and others. As a result a multitude of design obstacles for embedded systems especially in the wireless domain popped up, persistently deeming their timely production an ordeal. The notion of the ubiquity of these devices shall facilitate the reader to comprehend the relevance of the design hurdles manufacturers usually encounter in the design process of embedded systems. This thesis deals with one of these obstacles, the system partitioning problem, and discusses how it can be overcome.

#### 1.1 Motivation

When scrutinising the evolution of modern electronic systems, it becomes apparent, that not only their circulation but also their complexity has undergone a tremendous growth and is still not losing steam. The next generation of mobile devices for 3G UMTS systems is expected to be based on processors containing more than 40 million transistors [55]. Hence, during a relatively short period of time of about 10 years, a staggering increase in complexity of more than six orders of magnitude has taken place [130].

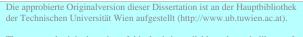

In comparison to this extremely fast-paced growth in algorithmic complexity, the concurrent increase in the complexity of silicon integrated circuits proceeds according to the well-known Moore's Law [109], famously predicting the doubling of the number of transistors integrated onto a single integrated circuit every 18 months. Hence, it can be concluded that the

growth in silicon complexity lags behind the extreme growth in the algorithmic complexity of wireless communication systems. This is also known as the *algorithmic complexity gap* depicted in Figure 1.1 on the left. The regularly published International Technology Roadmap

Fig. 1.1: Algorithmic complexity gap and design productivity gap.

for Semiconductors [74, 75] reported a growth in design productivity, expressed in terms of designed transistors per staff-month, of approximately 21% compounded annual growth rate, which lags behind the growth in silicon complexity. This is known as the *design gap* or *productivity gap* depicted in Figure 1.1 on the right. Thus, the abilities of underlying silicon platforms on which wireless communication systems are built have to be exploited with increasing efficiency, i.e. more functionality has to be gained from each individual transistor. In other words, the *quality* of the design process, i.e. effective functionality per unit of raw silicon achieved through both hardware and software parts of the system, needs to increase. From this it follows that it is increasingly difficult to design entire integrated circuits - although ever more transistors can be designed over some period of time, over the same period of time the total number of transistors in the circuit increases by an even higher factor. Hence, the *speed* of the design process has to increase significantly.

The existence of both the algorithmic and the productivity gap points to inefficiencies in the design process. At various stages in the process, these inefficiencies form bottlenecks, impeding increased productivity which is needed to keep up with the mentioned algorithmic demand. When putting the focus on the wireless systems domain, additionally the time-to-market for a new product dropped from about three years for the first GSM phones below 18 months for smart phones of the latest UMTS generations [10]. And in this domain launching a product six months early triples profits, whereas being six months late results in breaking even [11].

Naturally, the identification of inefficiencies and novel design strategies have been subject

to extensive research of the electronic design automation (EDA) industry in general and the Christian Doppler Laboratory for Design Methodology of Signal Processing Algorithms in particular. The major problems are the severe fragmentation of the design process [123], which is briefly surveyed in Appendix A, and the existence of *hard* design tasks, i.e. the hot spots of the design process [63, Knerr et al.]<sup>1</sup>, for which a feasible solution has not yet been integrated into any commercial EDA tool.

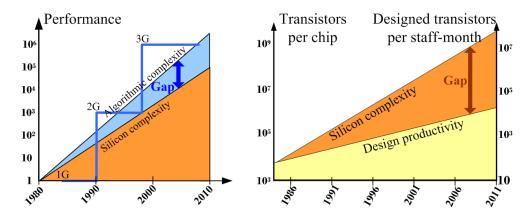

As a direct consequence of the steep requirements on the design cycle, the investigation of synthesised implementation alternatives is disqualified. A trial synthesis even for a small subset of the design would be far too time consuming, thus causing a strong bias in the importance of the design tasks towards those located in the early stages. Their relevance is even more emphasised by the impact on the final system performances. About 90% of the overall costs are determined in the first design stages [111]. Figure 1.2 illustrates the potential of the design decision to influence the cost while the development proceeds. The

Fig. 1.2: Evolution of the cost span over the development time [8].

most important design tasks located in the *early* region of the design process are system level analysis, system partitioning, floating-point to fixed-point conversion, high level synthesis, and virtual prototyping [16, 63, Knerr et al.].

Since system level analysis is a necessary prerequisite of system partitioning, it shall be briefly concretised. Ideally, crucial decisions are based on a profound knowledge about the intricacies of the design. As soon as the core algorithms, that make up a system's functionality, have been assembled, their internal structure has to be quantised and reliably extrapolated regarding the probable set of future implementation alternatives. For any part of the design a multi-dimensional design space is spanned, in which estimations of crucial design parameters

<sup>&</sup>lt;sup>1</sup> Cited work which I authored or co-authored is indicated as such by [#,Knerr et al.]

like timing, area, consumed power, throughput, latency, cost, signal-to-quantisation noise ratio, etc., are incorporated. System level analysis typically comprises a set of different tasks like static code analysis [1, 42], profiling [21], compiler optimisation [9], complexity analysis for verification [102], cost predictions [10], etc. These values serve as system graph enrichments with respect to the targeted platform abstraction, which will be explained in detail in Section 3.4.

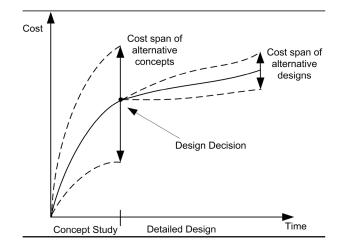

System partitioning can be considered as first *constructive* design task beyond pure analysis and characterisation. It consists in the component selection of the underlying platform carrying out the desired applications and the following binding of functional parts to these components. Hence, it constitutes the very core of hardware/software codesign. Its purpose is the identification of the optimal architecture out of many platform alternatives based on computation models for processing elements as general-purpose processors, DSPs,  $\mu$ Controllers, application specific instruction set processors (ASIPs), application specific integrated circuits (ASICs), networks, busses, memories, etc. In Figure 1.3 a small cut out from a data flow

Fig. 1.3: Partitioning: Map functionality to platforms.

oriented system graph from the cell searcher component of an UMTS receiver is depicted. It consists of matched filters (MF), energy accumulation (En Acc), peak detection (Peak Det), and the group code table (Group Code). On the right side some platform models are sketched. The decision which part of the functionality of the system graph is implemented on which resource is not straightforward. Although this graph seems rather simple, some constraints on available silicon area may exist that do not allow for a complete ASIC implementation, and some others e.g. on latency may hinder a complete software implementation on a DSP. The trade-off between competing objectives in larger scenarios with hundreds of communicating functional blocks represents the core of the partitioning problem. Hence, system partitioning is concerned with the formulation of such a multi-objective optimisation scenario, typically with many different objective functions that may comprise complex inter-

nal problems such as multi-resource scheduling with precedence constraints. The next section highlights the contributions that have been achieved in this field and that are demonstrated in this thesis.

#### 1.2 Contributions

The research work in the Christian Doppler Laboratory for Design Methodology of Signal Processing Algorithms addresses both recipes to overcome the fragmentation of the design process as well as the development of powerful integrated solutions for the aforementioned design tasks. Concretely, the work covered in this thesis is focused on the research area of system partitioning with respect to the wireless embedded system domain and is designed as integral part of the Open Tool Integration Environment (OTIE). For a brief overview of this environment refer to Appendix A. Although not mainly in the focus of this thesis, it has to be exposed, that significant efforts regarding floating-point to fixed-point conversion, automatic virtual prototyping, automatic verification, system level analysis, and scheduling of SDF graphs with multi-frequency domains have been undertaken in the context of OTIE:

- B. Knerr, P. Belanović, M. Holzer, G. Sauzon, and M. Rupp, "Design Flow Improvements for Embedded Wireless Receivers", in Proc. of the 12th European Signal Processing Conference (EUSIPCO), pages 2015 - 2018, Vienna, Austria, 2004.

- B. Knerr, P. Belanović, M. Holzer, G. Sauzon, and M. Rupp, "Advanced UMTS Receiver Chip Design Using Virtual Prototyping", in Proc. of the 2004 International Symposium on Signals, Systems and Electronics (ISSSE), Linz, Austria, 2004.

- P. Belanović, B. Knerr, M. Holzer, G. Sauzon, and M. Rupp, "A Consistent Design Methodology for Wireless Embedded Systems", EURASIP Journal on Applied Signal Processing, Vol. 2005(16), pages 2598 - 2612, 2005.

- B. Knerr, M. Holzer, and M. Rupp, "Task Scheduling for Power Optimisation of Multi Frequency Synchronous Data Flow Graphs", in Proc. of the 18th Annual Symposium on Integrated Circuits and System Design, pages 50 - 55, Florianapolis, Brazil, September, 2005.

- M. Holzer, B. Knerr, P. Belanović, and M. Rupp, Efficient Design Methods for Embedded Communication Systems, EURASIP Journal on Embedded Systems, vol. 2006, Article ID 64913, 18 pages, 2006. doi:10.1155/ES/2006/64913.

P. Belanović, B. Knerr, M. Holzer, and M. Rupp, A Fully Automated Environment for Verification of Virtual Prototypes, EURASIP Journal on Applied Signal Processing, vol. 2006, Article ID 32408, 12 pages, 2006. doi:10.1155/ASP/2006/32408.

The goal of this thesis is to present a set of strategies for the system partitioning problem as they typically appear in wireless embedded systems. This goal necessitates a solid base for the problem formulation that on the one hand accommodates a high degree of flexibility to be utilised in realistic scenarios and that on the other hand exhibits sufficient mathematical rigour to enable the applicability of powerful algorithmic concepts. The predominant contributions of this thesis in the research field of embedded system design can be grouped into three scientific claims as they are listed in the following enumeration:

- Claim 1: Analysis of the properties of typical system graphs in embedded systems. The variety of existing graph representations in the field is illuminated and the influencing factors, when a certain graph representation is considered to be beneficial, are distinguished. Common terms and definitions of general and applied graph theory are introduced. In this thesis a thorough revision of properties which are very typical for graphs describing signal-processing systems is undertaken. This deeper knowledge finally leads to improvements of existing optimisation methods and eventually to the development of entirely new strategies. The characteristics of these graph properties have been discussed (alongside new algorithms for system partitioning) in the following publications:

- B. Knerr, M. Holzer, and M. Rupp, RRES: A Novel Approach to the Partitioning Problem for a Typical Subset of System Graphs, EURASIP Journal on Embedded Systems, vol. 2008, Article ID 259686, 13 pages, 2008. doi:10.1155/2008/259686.

- B. Knerr, M. Holzer, and M. Rupp, "Novel Genome Coding of Genetic Algorithms for the System Partitioning Problem", Proc. of IEEE 2nd Int. Symposium on Industrial Embedded Systems (SIES), pages 134 - 141, Lisbon, Portugal, July, 2007.

- Claim 2: A flexible platform abstraction matching the heterogeneity of embedded systems.

The architecture model constitutes the first of the two necessary parts to assemble a system partitioning scenario. The thesis reviews classical and modern platform concepts and develops a flexible description that offers the designer a large degree of freedom in the number and type of architectural components. In opposite to existing partitioning approaches, an architecture library has been developed in this work that permits *arbitrary* platform compositions and a very detailed communication and processing model.

Such a flexibility is obligatory in the field of wireless embedded systems, since herein the heterogeneity and variety of architectures is protruding. The formulation of the platform abstraction allows for a non-ambiguous and distinct mapping of system graphs to the architecture models. The features and advantages of this very flexible framework have been discussed (alongside the automatic virtual prototyping framework and new algorithms for partitioning) in the following publications:

- B. Knerr, M. Holzer, and M. Rupp, "Extending the GCLP Algorithm for HW/SW Partitioning: A Detailed Platform Model and Performance Improvements", in Proc. IEEE Austrochip, pages 89 - 95, Vienna, Austria, 2006.

- M. Holzer, B. Knerr, P. Belanović, and M. Rupp, "Efficient Design Methods for Embedded Communication Systems", EURASIP Journal on Embedded Systems, 2006.

- Claim 3: Analysis and development of classical and new heuristic methods for the system partitioning problem.

The process of mapping the functional objects to the composed platform model constitutes the second part of the system partitioning problem and occupies the major portion of this thesis. Having analysed typical system graphs in this field and exploiting the high degree of detail of the newly developed platform abstraction, the partitioning problem can now be formulated in a very distinct manner that offers a higher degree of representativeness for wireless embedded systems than any approach before. On this level system partitioning is defined as combinatorial multi-objective optimisation problem and a variety of algorithmic strategies is evaluated with respect to their applicability. The thesis discusses, analyses, and tests deterministic and randomised algorithms based on classical and entirely new approaches that are outlined in the following list:

- exhaustive search,

- gradient search [68],

- global criticality/local phase algorithm [77] and a modified version with substantial improvements published in:

B. Knerr, M. Holzer, and M. Rupp, "Improvements of the GCLP Algorithm for HW/SW Partitioning of Task Graphs", in Proc. of the 4th IASTED Int. Conf. on Circuits, Signals, and Systems (CSS), pages 107 - 113, San Francisco, CA, USA, November, 2006.

- simulated annealing [7,82]

- penalty reward tabu search [142]

- genetic algorithm [35, 147] with a novel genome coding published in:

- B. Knerr, M. Holzer, and M. Rupp, "Novel Genome Coding of Genetic Algorithms for the System Partitioning Problem", Proc. of IEEE 2nd Int. Symposium on Industrial Embedded Systems (SIES), pages 134 - 141, Lisbon, Portugal, July, 2007.

- Kernighan-Lin min-cut [81, 140] and a modified version to be applicable for embedded system partitioning of which an early version has been published in:

B. Knerr, M. Holzer, and M. Rupp, "HW/SW Partitioning Using High Level Metrics", in Proc. of the Int. Conf. on Computing, Communications and Control Technologies (CCCT), pages 33 - 38, Austin, Texas, August, 2004.

- an entirely new heuristic: restricted range exhaustive search (RRES):

B. Knerr, M. Holzer, and M. Rupp, RRES: A Novel Approach to the Partitioning Problem for a Typical Subset of System Graphs, EURASIP Journal on Embedded Systems, vol. 2008, Article ID 259686, 13 pages, 2008. doi:10.1155/2008/259686.

B. Knerr, M. Holzer, and M. Rupp, "Restricted Range Exhaustive Search: A New Heuristic for HW/SW Partitioning of Task Graphs", in Proc. of XXII Conf. on Design of Circuits and Integrated Systems (DCIS), Sevilla, Spain, 2007.

- and a fast scheduling algorithm in comparison with two classical list scheduling techniques published in:

B. Knerr, M. Holzer, and M. Rupp, "A Fast Rescheduling Heuristic of SDF Graphs for HW/SW Partitioning Algorithms", in Proc. of COMSWARE, New Delhi, India, January, 2006.

#### 1.3 Outline

The thesis is structured as follows:

**Chapter 2** reviews the evolution and state-of-the-art in hardware/software codesign. General concepts and terms are introduced and a survey of the technological advances in this area is presented. The variety of existing tool sets is listed and the most significant commercial and academic approaches are outlined. Examples of industry-designed target platforms for modern signal-processing/multimedia systems in the wireless domain are discussed.

**Chapter 3** formulates the system partitioning problem as combinatorial multi-objective optimisation problem. The graph representations that are common in signal processing systems are reviewed and the general synchronous data flow graph calculus is highlighted. The architecture library to assemble arbitrary platform models, and the precise communication model is introduced. Then, the mapping problem between system graph and architecture subject to a set of objectives is formulated and cost functions and performance metrics to assess the quality for a feasible mappings are defined. Finally, the embedded multi-resource scheduling problem is briefly outlined.

**Chapter 4** deals initially with system graphs for wireless embedded systems with typical properties concerning sparsity, locality, parallelism, etc. It then describes the algorithms that address the system partitioning problem. A smaller part concerns itself with the inherent scheduling problem and two classical and a new technique to solve this problem efficiently. The major part comprises detailed descriptions of a variety of partitioning techniques, partly taken from the related literature and partly representing beneficial modifications and entirely novel approaches. Based on the task graph set the results obtained from extensive test runs of the implemented techniques are demonstrated. Their performance, robustness, and computation time is discussed. Judgements of the applicability of the specific approaches according to system graph properties are given.

**Chapter 5** concludes the thesis commenting on the probable impact of the obtained results, the evolution of underlying models of computation with respect to system representations as graphs, and gives perspectives to research fields still open to be investigated.

## 2 STATE OF THE ART IN HW/SW CO-DESIGN

This chapter reviews the evolution and current state of the embedded system design relating to typical target architectures. Recalling the technological developments mentioned in the introductory chapter, the design flow is compartmentalised and dedicated descriptions of the single components are given. Systems assembled by a technological mixture of hardware and software parts exist for more than 15 years. These scenarios occur in the context of general-purpose systems (PCs, workstations), in which the joint development of processor, compiler, and operating system is addressed. The instruction set selection, the exploitation of parallelism by pipelining and scalar units, and the implementation of different caching strategies are typical topics for these systems. A slightly different context is opened by embedded systems, which contains a similar component, namely the joint development of one ore more special-purpose processors and their respective compilers, whereas the other major component in co-design for embedded systems arises from the naturally strong dependency on its specific purpose that is captured in the system description. This description of the system's functionality drives the design process, hence the term system level design is often utilised in this field [118]. Focusing on the latter scenario a proper definition of the term embedded systems is mandatory. Although being around for more than 20 years, a unique, commonly accepted definition is very hard to find. Still recently, Henzinger and Sifakis felt hustled to publish a work about the 'embedded systems design challenge' [58], in which this term has been tried to be captured without losing generality:

"An *embedded system* is an engineering artifact involving computation that is subject to physical constraints. The physical constraints arise through two kinds of interactions of computational processes with the physical world: (1) reaction to a physical environment, and (2) execution on a physical platform."

This definition does not necessarily entail a better palpability of the matter, since it embraces any *built thing that computes*. Besides, this definition completely embezzles the very part of the term, which makes it distinguishable in the first place: *embedded*. Therefore, we adhere to the following definition.

**Definition 1** (Embedded System). An **embedded system** is a computing device in general subject to a specific purpose and its implementation is predominantly determined by this

purpose, usually entailing a complete encapsulation into the environment where this purpose is located at.

Unfortunately, even this description becomes blurry, as we explicitly included for instance PDAs and modern mobile phones in the aforementioned examples. To be precise these products are rather general-purpose devices, but on a smaller scale compared to desktop PCs. The design methodology for embedded systems is intended to offer efficient and comprehensive mechanisms to explore a variety of implementation alternatives. An executable description of the system's functionality is inherently capable to be simulated and to be formally verified. The description has to be complete, i.e. all relevant design traits have to be present at any stage of the design process.

As illustrated by Figure 2.1 the concept of system level design consists of strongly inter-

Fig. 2.1: Concept of System Level Design.

connected tasks. The allocation phase comprises the component selection being appropriate for the execution of the system, e.g. processors, memory units, ASICs, etc. Any of those is characterised by a multitude of parameters, e.g. consumed power, number of operations per second, size of the silicon, read and write access times for memory units, etc. Processor structures comprise DSPs, RISCs (reduced instruction set computer), ASIPs, or microcontrollers ( $\mu$ C). According to the simulated, measured, or estimated system characteristics the behavioural components are partitioned onto the chosen architectural components.

These tasks are strongly interleaved. As every specific allocation and partitioning solution generates a new implementation alternative of the system with a new set of mostly estimated characteristics featuring a higher degree of detail, the preceding assumptions have frequently to be reconsidered. Once the design decisions have reached a mature state, the synthesis of the hardware parts, of the software parts, and of the interfaces eventually begins.

The following section gives a more detailed view on a typical platform composition in embedded systems.

#### 2.1 Target Architectures in Embedded Systems

The most typical architectural structures for embedded systems concentrate essentially onto a range of processing units: relevant for software implementations are  $\mu$ Cs and DSPs, or even more specific ASIPs, typical candidates for hardware implementation are programmable logic and dedicated data-paths. A mixture of these components is either assembled onto a single chip for which the term System-on-Chip (SoC) has prevailed, or is composed by several chips onto a board system.

Figure 2.2 visualises the common notion of the trade-off between hardware and software

Fig. 2.2: Architectural components and their affiliation to hardware and software.

architectural components. From the left to the right the complexity of the underlying component is decreasing in terms of instruction set, sophisticated memory access, and pipelining strategies. This is counterbalanced by the increase of the computational speed towards ASICs, mostly measured in throughput or number of operations per time unit. The grouping of these processor classes into hardware and software systems has not been clearly defined but is generally understood [31, 118]. More detailed descriptions of the individual components are given in Appendix B.

#### 2.1.1 Platform Composition

The assembly of state-of-the-art systems from the range of available processing elements can be in general be separated in two categories: system-on-a-chip (SoC) and board-level (or multi-chip) system. Typical board-level systems are for instance desktop computers and laser printers. To be precise, SoCs do not comprise every single peripheral on one die, but nearly any portable wireless system encapsulates vital parts on a single silicon substrate, since then the advantages of minor size and low power consumption can be combined. Moreover, the reliability of the circuit benefits well from the assembly on a single chip, such that in many cases even analogue parts (sensor, actuator, power amplifier) are put onto the same chip.

Again a commonly acknowledged definition for SoC is hard to obtain. We adhere to the

Fig. 2.3: Block structure of an System-on-Chip based design for a video phone [136].

notion of very typical components, of which a selection is assembled on an SoC:

- At least one  $\mu P$  ( $\mu$ Controller, DSP, RISC, etc.).

- A selection of memory units (RAM, EEPROM, ROM, etc.)

- Serial and parallel ports and interfaces (UART, JTAG, USB, etc.)

- Analogue circuitry (phase locked loops, sensors, oscillators, etc.)

- Analogue interfaces as analogue-digital or digital-analogue converters.

- Power management circuitry (clock gating, voltage/frequency regulation).

- Internal busses (CAN, AMBA, etc.).

- Direct memory access (DMA) to disburden the  $\mu$ Processor.

In Figure 2.3 a block based structure of a state-of-the-art board level system containing a large SoC is depicted, which is comprised of a selection of components very typical for a modern video phone. The multiplicity of components integrated onto the same die is an immediate consequence from the dramatic advances in microelectronics. In consequence,

the non-recurring engineering costs for SoCs are much higher than for multi-chip (boardlevel) systems, whereas the production cost for SoCs is lower, once the floor planning is finalised. The overwhelming part of embedded systems in the wireless domain is built around System-on-Chips and in the following section the traditional design flow for such systems is described.

#### 2.2 Embedded Systems Design Flow

The flow of the overall embedded design process, starting with the initial conceptual idea of the system and finishing in the final product, is traditionally divided into a number of abstraction levels. Of the many design methodologies in existence, each prescribes a different set of abstraction levels to make up the design process. As a result, there is no clear and universally accepted division of the design process into a well-defined set of abstraction levels. Rather, there exists a great number of overlapping or even synonymous definitions of abstraction levels, some of which are broad in scope, while others cover small and very specific parts of the design flow, and again some of which enjoy wide recognition in academic and industrial circles, while others are referred to less commonly [45, 50, 75].

The right side of Figure 2.4 shows a collection of some of the most commonly used abstraction levels in academic literature and/or industrial practice, given in their relative order within the overall design process (from high to low level of abstraction). On the left side a co-design flow is depicted accordingly, as it is commonly described in embedded systems. On highest abstraction level an informal specification of the product is put together that does not contain any information regarding its realisation but only a rough sketch of the desired behaviour. Consequently, first refinements intend to identify algorithmic solutions for this functionality, for instance whether a complex computation *could* be performed and not how much resources the computation required. Exploration of different algorithmic variants with respect to precision, computational effort, and robustness is located here indicated by the cycle item in the co-design flow.

The next lower transaction/architecture level is typically occupied by platform modelling, the allocation of architectural components and the partitioning into hardware and software domains. Static code analysis, profiling and co-simulation deliver estimations of timing, silicon area, latency, throughput, regarding the chosen platform composition. Communication models for intra-platform data transfers are applied to simulate the behaviour of memory units and bus structures. According to the platform setup, interface functions are provided that handle the data transfers and transactions between architectural components. Within a single component usually untimed code, e.g. plain C is deployed, whereas the interface functions

modelling bus and memory accesses feature a more sophisticated, so called *bus-cycle true* behaviour. Performance estimations are fed back in the co-design flow to alter the platform setup, the partitioning or even fundamental parts in the executable system specification.

Fig. 2.4: Common abstraction levels and co-design flow for embedded systems.

The hardware assembly of ASICs, ASIPs and FPGA blocks is performed on register transfer level, for which hardware description languages (HDL) like VHDL [33] and Verilog [34] are vicarious. Exact, so-called *bit/cycle true* simulations are possible at this stage, hence is verification of the hardware behaviour. The software assembly onto chosen CISC, DSP, or RISC cores belongs to the same level of abstraction. Once assembly code for these cores exist, the software part does not undergo a further refinement in terms of abstraction levels, whereas the hardware described by VHDL or Verilog does so on its way to final synthesis (via the wire and the geometry level). The integration and verification of both hardware and software components is the final step towards manufacturing the product. In embedded systems it is in general not possible to revise upper levels in the design flow once the integration and verification stage below register transfer level has been reached, due to the harsh time-to-market requirements. Therefore, the performance analysis and verification step may only affect the immediate preceding implementation of the actual function block.

Such an iterative reduction of the abstraction level narrows the design space and increases the accuracy of the model. To avoid the introduction of malfunctions due to the perma-

nent transformation of the system description while decreasing the level of abstraction, the *correct-by-construction* paradigm [37, 125] is of major importance. Formal methods and automated synthesis have to be incorporated whenever possible. For the hardware synthesis from register transfer down to geometry, this goal has already been accomplished. Powerful synthesis tools exist, which enable the designer to automate the implementation process for VHDL/Verilog specified hardware blocks to a very large degree, e.g. Design Compiler from Synopsys [131], HDL coder toolbox from Matlab/Simulink [137], or proprietary tools of FPGA providers like Xilinx [145] and Altera [3]. This success in raising the *lowest* abstraction level to register transfer level by automation of the subsequent refinements is considered to be exemplarily for the future path of electronic system design [32].

With respect to the platform setup and partitioning stage a similar success has not yet been achieved. Paragraphs dedicated to related work in platform abstraction, problem formulation, and partitioning algorithms reside in their respective chapters. In Appendix B.8 a review of commercial and academic co-design frameworks and their respective design languages is given.

## **3 SYSTEM PARTITIONING**

In embedded system design the term *system partitioning* usually comprises the compound of two synthesis tasks: *allocation* and *mapping*. The selection of architectural components is meant by *allocation*, whereas the binding of the functional code of the system to these components is performed during the *mapping*. Note, that often *mapping* and *(system) partitioning* are used synonymously, when the architectural traits of the platform are fixed beforehand and are therefore not part of the optimisation. Usually a variety of constraints exists that aggravate the process of finding a suitable solution. Amongst others there are quantifiable properties for timing, power consumption, compiled code size, silicon area, throughput, latency, implementation cost, etc. and unquantifiable properties as flexibility, humble maintenance effort, testability, reusability, and many more. In general it can be stated that most formulations of this optimisation problem are marked by a huge solution space and analytically intractable relations between the characteristic values that influence the feasibility of a candidate solution.

The following chapter introduces classical graph concepts and fundamental terms. Specific graph structures that are commonly used to describe signal processing systems are surveyed with respect to hierarchy and granularity in Section 3.1. The classical platform model predominantly used for partitioning scenarios is surveyed in Section 3.2. How the underlying architecture for the allocation phase can be modelled to give consideration to modern heterogeneous architectures is described in Section 3.3. Herein, a detailed and flexible component library is introduced, which allows for arbitrary architecture composition, as they are typically found in embedded systems. Section 3.5 sketches the origin of the system partitioning problem in an NP-complete problem known from graph theory. Based upon these classical terms the problem is formulated to map the system graph to components from the new architecture library as a combinatorial multi-objective optimisation problem. Eventually, it is shown that this formulation accommodates an enclosed NP-complete problem in Section 3.5.3, namely the multi-resource scheduling problem.

## 3.1 Typical Graphs in Embedded System Design

System partitioning of a system relies on its representation in various graph forms. The following basic definitions prepare the ground for the further discussion of these forms.

**Definition 2** (Graph). A graph  $G(\mathcal{V}, \mathcal{E})$  is defined as an ordered pair of a set  $\mathcal{V} = \{v_1, v_2, \ldots, v_{|\mathcal{V}|}\}$  of vertices and a set  $\mathcal{E} = \{e_1, e_2, \ldots, e_{|\mathcal{E}|}\}$  of edges. The elements of the set  $\mathcal{E}$  correspond to unordered pairs of vertices. The vertices belonging to an edge are called endpoint or end vertex of the edge.

**Definition 3** (Directed Graph). A directed graph  $G(\mathcal{V}, \mathcal{E})$  is defined as an ordered pair of a set  $\mathcal{V} = \{v_1, v_2, \dots, v_{|\mathcal{V}|}\}$  of vertices and a set  $\mathcal{E} = \{e_1, e_2, \dots, e_{|\mathcal{E}|}\}$  of edges. Here,  $\mathcal{E}$  is defined as set of 2-tuples of vertices  $\mathcal{E} = \{(v, w) | v, w \in \mathcal{V}\}$ . The operation **beg** returns the source (tail) vertex, and the operation **end** returns the sink (head) vertex of an edge e as follows:  $\forall e = (v, w) \in \mathcal{E}$ : beg(e) = v, end(e) = w. The vertex v is called a direct predecessor of w and w is a direct successor of the vertex v.

**Definition 4** (Path/Simple Path/Cycle). A **path p** from a vertex v to a vertex w in a directed graph is a sequence of vertices  $v = s_1, s_2, \ldots, s_n = w$  that satisfies:  $\forall i, i = 2 \ldots n \exists (s_{i-1}, s_i) \in \mathcal{E}$ . The vertex  $s_1$  is the initial vertex of that path and  $s_n$  is the terminal vertex of the path. A **simple path**  $\mathbf{p}_s$  additionally fulfills the condition:  $\forall s_i, s_j \in \mathbf{p}, i \neq j$ :  $s_i \neq s_j$ . If the initial and the terminal vertices of a path are the same, that is,  $s_0 = s_n$ , then the path is called a **cycle**.

**Definition 5** (Directed Acyclic Graph). A **directed acyclic graph** (DAG) is a directed graph that does not contain any cycles. (Or equivalently, all possible paths of a DAG are simple paths.)

**Definition 6** (Indegree/Outdegree). The operation indegree(v) returns the number of incoming edges to the vertex  $v \in V$  of a directed graph. The operation outdegree(v) returns the number of outgoing edges from the vertex  $v \in V$  of a directed graph.

**Definition 7** (Rank). The operation rank(v) of a vertex  $v \in V$  in a directed graph  $G(V, \mathcal{E})$  is defined as:

$$\forall v \in \mathcal{V} : \operatorname{rank}(v) \triangleq \begin{cases} 0 & , \operatorname{indegree}(v) = 0\\ 1 + \max_{u} \operatorname{rank}(u) & , \operatorname{indegree}(v) > 0 \end{cases},$$

(3.1)

with  $u \in \mathcal{V}, e \in \mathcal{E} : u = beg(e) \land v = end(e)$ .

#### 3.1.1 Process Graphs

A common approach for reaching a high perceivability of the functionality within a large and complex system is to use a hierarchical decomposition together with graphical representation. Hierarchical decomposition into subsystems provides a structured view to the system for a group of different designers. In Figure 3.1 a common graphical representation for a system (e.g. in communications) is shown. This starts on the left with a process or task graph describing a modern signal processing system in dependence on its nature as data flow oriented system on a macroscopic level, in which vertices represent processes or functions and edges represent data transfers between them. Nearly every signal processing work suite offers a graphical block-based design environment, which mirrors the movement of data, streamed or blockwise, while it is being processed [12, 98, 133, 137].

**Definition 8** (Process or Task Graph). A **process** or **task graph** is a directed graph, in which the vertices represent functional elements performing data processing and in which the edges represent data transfers between those processing elements. The term process (or function) is used synonymously for the vertices of a process graph throughout the thesis.

Furthermore, a detailed view of one vertex may reveal several function calls, which can be assembled to a single larger process (or may be represented as access or call graph if necessary). By zooming in one of the processing vertices, a control flow graph is dismantled as shown in the middle of Figure 3.1, which is in turn assembled by so called basic blocks (Def. 10). And finally, within these basic blocks algebraic expressions are represented with a data flow graph on operational level, a so called expression tree on the right. Beside its purpose of

Fig. 3.1: System decomposed into hierarchical graph structures.

a structured view to a system, these graphs and subgraphs allow for automatic analysis in

order to derive characteristic properties and successively for automated partitioning as well. The definition of those graph structures is presented in the following paragraphs.

**Definition 9** (Control Flow Graph). A control flow graph (CFG) is a directed graph  $G(\mathcal{V}, \mathcal{E}, \text{root}, \text{exit})$ . It represents a notation of all paths that can be traversed throughout a process during its execution. The control flow of a process enters only at one vertex (root vertex) and leaves the process only at one vertex (exit vertex). The *root* vertex does not have any incoming and the exit vertex does not have any outgoing edge (indegree(root) = outdegree(exit) = 0).

**Definition 10** (Basic Block). A **basic block** (BB) is a vertex of a CFG and contains a sequence of data operations ended by a control flow statement as last instruction.

The statements implementing the control flow are for instance for C based languages if, case, goto, for, while, do, continue, and break. These statements divide the program flow into separable basic blocks and establish the control dependencies between them. Due to programming constructs like loops a CFG is in general not cycle-free. The middle part of Figure 3.1 depicts the resulting CFG structure from the three for-loops in process *D*.

Control flow graph analysis contains many more characteristic values like reducibility of loops, dominance trees [2], and loop cascading [102], feasibility of paths and linear independent paths [119], etc. Partitioning techniques working on these fine-grain graphs are less common, since basic blocks contain normally only a few operations, so that the superposed communication overhead to interconnect different partitions is very high. Still, some approaches exist that partition on CFG level [57].

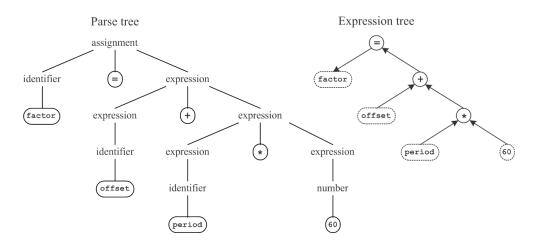

The sequence of data operations inside of one BB forms itself a data flow graph (DFG) or equivalently one or more expression trees (Figure 3.2 on the right). To briefly sketch how source code is transformed into these graph representations, consider the following example of a C-like expression: factor = offset + period \* 60;.

After lexical analysis, which generates a sequence of symbols and analyses their classification as identifier, operator, constant, expression, etc., a parse tree is assembled as in Figure 3.2 on the left. This parse tree corresponds to the more comprehensive expression tree in the same figure on the right. Usually within a BB more than one expression exists that reads from and writes to the variables. The assembly of all expression trees within a BB then forms a data flow graph on operational level. In such a DFG edges correspond to variables or constants holding information and vertices correspond to operations performed on these variables. For more detailed information on compiler techniques refer to the literature [2].

Fig. 3.2: Code fragment representation as parse and expression tree.

#### 3.1.2 Synchronous Data Flow Graphs

To be in accordance with most of the partitioning approaches in the field, a graph representation to be in the form of synchronous data flow (SDF) graphs can be assumed. This model of computation has been firstly introduced in 1987 by Lee and Messerschmitt [99] at UC Berkeley. This model established the backbone of renowned signal processing work suites, e.g. Ptolemy [98] or SPW [29]. SDF captures precisely multiple invocations of processes and their data dependencies and thus is very suitable to serve as a system model for data stream oriented signal processing systems. An indicator for the persistent relevance of the SDF graph representation is provided by the fact that SystemC and its most recent extensions natively support the SDF domain. For instance, the official analog mixed signal (AMS) extension of SystemC [135] just introduced a computation model now providing SDF computation models for all AMS modules.

**Definition 11** (Synchronous Data Flow Graph). A synchronous data flow (SDF) graph is a directed graph  $G(\mathcal{V}, \mathcal{E})$ . Any edge  $e_i \in \mathcal{E}$  is annotated with two numbers  $p_i, c_i \in \mathbb{Z}^+$ , of which  $p_i$  is assigned to the tail of  $e_i$ , and  $c_i$  to the head of  $e_i$ . The numbers  $p_i$  represent the number of samples produced per invocation of the vertex at the edge's tail,  $\operatorname{out}(e_i)$ . The numbers  $c_i$  indicate the number of samples consumed per invocation of the vertex at the edge's head,  $\operatorname{in}(e_i)$ .

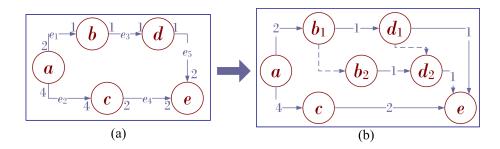

In Figure 3.3a, an example of an SDF graph  $G(\mathcal{V}, \mathcal{E})$  is depicted, composed of a set of vertices  $\mathcal{V} = \{a, .., e\}$  and a set of edges  $\mathcal{E} = \{e_1, .., e_5\}$ . According to the data rates at the edges such a graph can be uniquely transformed into a single activation graph (SAG) in Figure 3.3b. Every vertex in a SAG stands for exactly one invocation of the process,

Fig. 3.3: Example of a synchronous data flow graph and its decomposition into a single activation graph.

thus the complete parallelism in the design becomes now visible. Here vertex b and d occur twice in the SAG to ensure a valid graph execution, i.e. every produced data sample is also consumed.

An SDF graph can be formally described by a topology matrix  $\Gamma$ , in which any vertex is assigned to a column and any edge is assigned to a row:

$$\boldsymbol{\Gamma} = \begin{bmatrix} 2 & -1 & 0 & 0 & 0 \\ 4 & 0 & -4 & 0 & 0 \\ 0 & 1 & 0 & -1 & 0 \\ 0 & 0 & 2 & 0 & -2 \\ 0 & 0 & 0 & 1 & -2 \end{bmatrix} .$$

(3.2)

This matrix represents the topology matrix for the SDF graph in Figure 3.3 with the columns corresponding to the vertices in order a to e and the rows corresponding to edges in order  $e_1$  to  $e_5$ . This formalism allows for instance for the detection of inconsistent sample rates, when  $\operatorname{rank}(\Gamma) \neq |\mathcal{V}| - 1$ , and for periodic scheduling analysis [99]. Many partitioning approaches premise the *homogeneous* form of SDF graphs.

**Definition 12** (Homogeneous SDF Graph). A homogeneous SDF graph is an SDF graph, if  $\forall e_i \in \mathcal{E} : \operatorname{out}(e_i) = \operatorname{in}(e_i)$ , or equivalently, if the SDF graph and the single activation graph exhibit an isomorphic graph structure.

In this homogeneous form the connection to process or task graphs can be easily established, as a single activation graph is commonly considered as general process graph.

Although widely accepted for signal processing systems, SDF graphs are restricted to static dataflow behaviour. Therefore, modern SoC applications are often not completely amenable to SDF. Parameterised or cyclo-static dataflow provides for dynamic behaviour by means of structured, dynamic parameter changes in the base model that it is applied to. These modern approaches have not yet made their way into any academic or commercial EDA tool

and their integration into OTIE remains an open issue. A brief survey of these graphs can be found in Appendix C.3.

In this thesis the partitioning backbone supports both general process graph structures as well as general SDF graph representations. According to Lee's work [99], a calculus is provided that validates SDF graphs with respect to their consistency, that resolves feedback edges and multiple invocations and that performs the transformation into single activation graphs, which can be treated equivalently to process graphs. The granularity of the vertices adheres to the common notion of a *partitionable* size that covers the encapsulated functionality of FIRs, DCTs, quicksort, Walsh-Hadamard transform, or similar procedures in consideration of comparable work by other authors in this field [25, 35, 78, 142].

## 3.2 Classical Platform Model for Hardware/Software Partitioning

When the hardware/software partitioning problem came to be recognised as a hard optimisation problem being encountered in system design at the beginning of the last decade, the perception of such a hardware/software platform has been rather uniform throughout the following ten years.

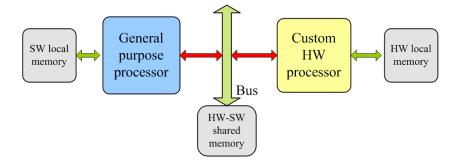

In 1993 Ernst and Henkel published an early work on the partitioning problem within the COSYMA system [39]. The underlying architecture model has been composed of a programmable processor core, memory, and customised hardware (Figure 3.4). Its composition

Fig. 3.4: Common implementation architecture.

entailed from the fundamental notion of the existence of two different processing elements: a programmable *software* processor that executes functional code sequentially and in a rather slow manner and a non-programmable *hardware* processor that allows for different function blocks to be carried out concurrently in a rather fast manner. In the beginning this setup was appropriate to excogitate fundamental strategies to cope with problems like minimising

execution time with limited silicon area. The distinction between local and shared memory resources with different access times according to the number of data being transferred offered a flavour of realism but completely neglected the occurrence of collisions on the system bus and the difference between on-chip and off-chip memory access. Still, this platform model was widely adapted by research groups around the world as it can be found by Kalavade et al. [77,78], Eles et al. [38], Vahid et al. [140], Chatha et al. [25], and Srinivasan [129]. However, the crudeness of the model prevented its deployment to any realistic scenario, since too many details affecting execution time and area through communication and control overhead had been neglected.

In the late nineties the first approaches were developed that spent more effort to model communication between processes and different resources more accurately. In 1997 Hardt and Rosenstiel modelled a Sparc CPU based architecture featuring a direct memory access (DMA) controller, cache structures and different execution times for load and store accesses on all communication links [54]. However, in their codesign approach the performance of a system executed on this architecture was crudely estimated, i.e. completely unaware of a possible concurrent process execution on different resources and unaware of colliding data transfers on communication links accessed simultaneously by different resources. In 2002 Wiangtong et al. [142] were one of the first authors that improved this model with a proper scheduling technique avoiding any packet collisions on the bus structures, but neglecting complexity in the variety of communication links, the bus arbitration schemes and the number of available resources.