Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology

FAKULTÄT FÜR **INFORMATIK**

# Implementation and Performance of Synchronization Methods for Dual-Core Engine Control-Systems

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

### **Computational Intelligence**

eingereicht von

### Christian Stoif

Matrikelnummer 0025375

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Betreuer: o. Univ.-Prof. Dipl.-Ing. Dr. techn. Herbert Grünbacher Mitwirkung: Univ.-Ass. Dipl.-Ing. Dr. techn. Martin Schöberl

Wien, 14. 11. 2008

(Unterschrift Verfasser)

(Unterschrift Betreuer)

## Chapter 2

## Background

### 2.1 Fundamentals

#### 2.1.1 Overview

In this section an overview of the most important terms used in this thesis is given. The depth of the background knowledge presented here should be enough for any reader to gain enough insight into the topic to interpret the results of this thesis.

Most elementary terms come from the field of operation systems and have their roots in single-processor systems. In many cases the terminology was just extended to cover also systems that allow concurrent processing. Nevertheless, *concurrency* itself introduces some new problems that are simply *inexistent* in a system with strictly sequential execution. This section covers the theory vital for this thesis by following this historical development from nonparallel to parallel systems.

#### 2.1.2 Atomicity

A sequence of commands is said to be executed *atomically* if they are executed as if they were a single instruction.

#### 2.1.3 Processes

According to [Sta01] the term *process* is used here as a synonym for a program in execution, that is all its data whether it is part of the program itself or the operating platform that executes that process. The system-dependent part of the process is called the *context* of the process, all the data regarding a process are the *working set* of this process.

# Implementation and Performance of Synchronization Methods for Dual-Core Engine Control-Systems

Multiple parallel processing cores are about to conquer embedded systems as well - the roadmaps of leading semiconductor companies certify this: it is not the question of whether they are coming but how the architectures of the microcontrollers should look in respect to the strict demands in the automotive sector. In this thesis the step from one to multiple cores is presented, establishing coherence and consistency for different types of shared memory by soft- and hardware means. Also support for point-to-point synchronization between the processor cores is realized implementing different methods. Though the theoretical approach using simulations is independent of the number of processing units, the practical examinations focus on the logical first step from single- to dual-core systems, using an FPGA-development board with two hard PowerPC - processor cores. Best- and Worst-case results, together with intensive benchmarking of all synchronization primitives implemented, show the expected superiority of the hardware solutions. It is also shown that dual-ported memory outperforms single-ported memory if the multiple cores use inherent parallelism by locking shared memory more intelligently using a locking-method developed in this thesis. Simple global locking of the whole shared memory alone prevents any parallel access on principle. In the worst case multiple-ported memory degenerates in performance to single-ported memory. However, the conditions that must be fulfilled for this worst case to occur do not seem to be realistic for practical applications in the field.

# Implementierung und Performanz von Synchronisationsmethoden für Antriebssoftware auf Zweikernsystemen

Mehrere parallele Prozessorkerne sind auch bei den eingebetteten Systemen im Anmarsch - die Pläne von führenden Halbleiterherstellern bezeugen dies: es ist nicht die Frage ob sie kommen sondern vielmehr wie die Architekturen der Mikrocontroller unter Berücksichtigung der strengen Anforderungen im Automobilsektor aussehen sollen. In dieser Diplomarbeit wird der Schritt von einem zu mehreren Prozessorkernen unternommen, unter Verwendung von Mechanismen in Software und Hardware wird Kohärenz und Konsistenz von unterschiedlichen Typen von geteiltem Speicher hergestellt. Auch Unterstützung für Punkt-zu-Punkt Synchronisation zwischen den Prozessorkernen wird durch verschiedene implementierte Methoden realisiert. Obwohl der theoretische Ansatz mithilfe von Simulationen unabhängig von der Anzahl der Prozessorkerne ist konzentrieren sich die praktischen Untersuchungen auf den logischen ersten Schritt von einem Ein- zu einem Zweikernsystem, unter Verwendung einer FPGA-Entwicklungsplatine mit zwei PowerPC-Prozessorkernen. Resultate des besten und schlechtesten Falles zeigen, zusammen mit intensiven Vergleichstests aller implementierten Synchronisationsprimitiven, die erwartete Überlegenheit der Hardwarelösungen. Es wird auch gezeigt wie ein Speicher mit zwei Ports einem Speicher mit nur einem Eingang überlegen ist, falls die mehreren Prozessorkerne inhärente Parallelität unter Verwendung einer in dieser Diplomarbeit vorgestellten Methode zur Speicherreservierung intelligenter nutzen. Allein eine simple globale Reservierung des gesamten geteilten Speichers verhindert eine parallele Nutzung grundsätzlich. Im schlimmsten Fall degeneriert die Performanz eines Speichers mit mehreren Ports zu der eines Speichers mit nur einem Eingang, doch die Bedingungen die zu diesem schlimmstmöglichen Fall führen scheinen für Anwendungen in der Praxis nicht realistisch zu sein.

## Contents

| Contents |                    |                         |                                                 | iv            |

|----------|--------------------|-------------------------|-------------------------------------------------|---------------|

| Li       | List of Figures    |                         |                                                 | vii           |

| Li       | st of              | Tables                  | 3                                               | ix            |

| 1        | <b>Intr</b><br>1.1 | <b>oducti</b><br>Outlin | on<br>le of Thesis                              | <b>1</b><br>2 |

| <b>2</b> | Bac                | kgrour                  | nd                                              | 3             |

|          | 2.1                | Funda                   | mentals                                         | 3             |

|          |                    | 2.1.1                   | Overview                                        | 3             |

|          |                    | 2.1.2                   | Atomicity                                       | 3             |

|          |                    | 2.1.3                   | Processes                                       | 3             |

|          |                    | 2.1.4                   | Resources                                       | 4             |

|          |                    | 2.1.5                   | The Memory Hierarchy, Caches                    | 4             |

|          |                    | 2.1.6                   | Process Interaction                             | 5             |

|          |                    | 2.1.7                   | Mutual Exclusion on Single-Cores                | 6             |

|          |                    | 2.1.8                   | From Multiprogramming to Multiprocessing        | 6             |

|          |                    | 2.1.9                   | Synchronization                                 | 7             |

|          |                    | 2.1.10                  | Mutual Exclusion using Locks                    | 8             |

|          |                    | 2.1.11                  | Semaphores                                      | 9             |

|          |                    | 2.1.12                  | Event Synchronization by Barriers               | 9             |

|          |                    | 2.1.13                  | The Parallel Random Access Machine (PRAM) Model | 9             |

|          |                    | 2.1.14                  | Real-Time Systems (RTS)                         | 10            |

|          |                    | 2.1.15                  | Fault-Tolerant Systems (FTS)                    | 11            |

|          |                    | 2.1.16                  | Architectures of Multiprocessor Systems         | 11            |

|          |                    | 2.1.17                  | Caches                                          | 12            |

|          |                    | 2.1.18                  | Coherence                                       | 13            |

|          |                    | 2.1.19                  | Consistency                                     | 13            |

|          |                    | 2.1.20                  | Scalability                                     | 15            |

|          |                    | 2.1.21                  | Transactional Memory (TM)                       | 15            |

|          | 2.2                | Relate                  | d Work                                          | 17            |

|   |      | 2.2.1   | Mutual Exclusion                                      |  |

|---|------|---------|-------------------------------------------------------|--|

|   |      | 2.2.2   | Event Synchronization                                 |  |

|   |      | 2.2.3   | Transactional Memory (TM)                             |  |

|   |      | 2.2.4   | A Glance at Scalable Multiprocessors                  |  |

| 3 | Soft | tware s | Synchronization 25                                    |  |

|   | 3.1  | The H   | Iardware Platform    26                               |  |

|   | 3.2  | Low-L   | Level Coherence                                       |  |

|   | 3.3  | Coher   | rence by Locking                                      |  |

|   | 3.4  | Extern  | nal Bus-Slaves as Locks                               |  |

|   | 3.5  | Event   | Synchronization                                       |  |

|   | 3.6  | Lockii  | ng Performance                                        |  |

|   |      | 3.6.1   | Direct Access to the Lock                             |  |

|   |      | 3.6.2   | Locking, Best Case                                    |  |

|   |      | 3.6.3   | Locked Single Access, Best-, Worst- & Average-case 39 |  |

| 4 | Har  | dware   | e Synchronization 43                                  |  |

|   | 4.1  | The P   | Problems                                              |  |

|   |      | 4.1.1   | PLB- and OPB-Lock, no Hardware Support 44             |  |

|   |      | 4.1.2   | BRAM-Lock, no Hardware-Support                        |  |

|   |      | 4.1.3   | PLB- and OPB-Lock, Hardware-Support                   |  |

|   | 4.2  | The R   | Roots of the Problems                                 |  |

|   | 4.3  | From    | SW- to HW-Synchronization                             |  |

|   | 4.4  | The C   | OCM-Access-Controller                                 |  |

|   |      | 4.4.1   | Features                                              |  |

|   |      | 4.4.2   | Description and Programming                           |  |

|   |      | 4.4.3   | Structure and State Machine                           |  |

|   |      | 4.4.4   | Coherence Ensurance - Implicit Locking in Hardware 59 |  |

|   |      | 4.4.5   | Consistency Ensurance -                               |  |

|   |      |         | Explicit Spin-Free Global Locking by Hardware 65      |  |

|   |      | 4.4.6   | Event Synchronization - Simple Barrier                |  |

|   |      | 4.4.7   | Event Synchronization - Extended Simple Barriers 67   |  |

|   |      | 4.4.8   | Event Synchronization - Complex Barriers              |  |

|   |      | 4.4.9   | Precision of Event Synchronization                    |  |

|   | 4.5  | Worst   | Case Performance                                      |  |

|   |      | 4.5.1   | Direct-Access Performance                             |  |

|   |      | 4.5.2   | Prevention of Starvation in the Worst-Case            |  |

|   |      | 4.5.3   | Conclusion                                            |  |

| <b>5</b>                  | Ben   | nchmarking                                              | 77  |

|---------------------------|-------|---------------------------------------------------------|-----|

| 5.1 Worst-Case Benchmarks |       |                                                         | 77  |

|                           | 5.2   | Non-Worst-Case Benchmarking                             | 79  |

|                           |       | 5.2.1 Benchmark System Configuration                    | 80  |

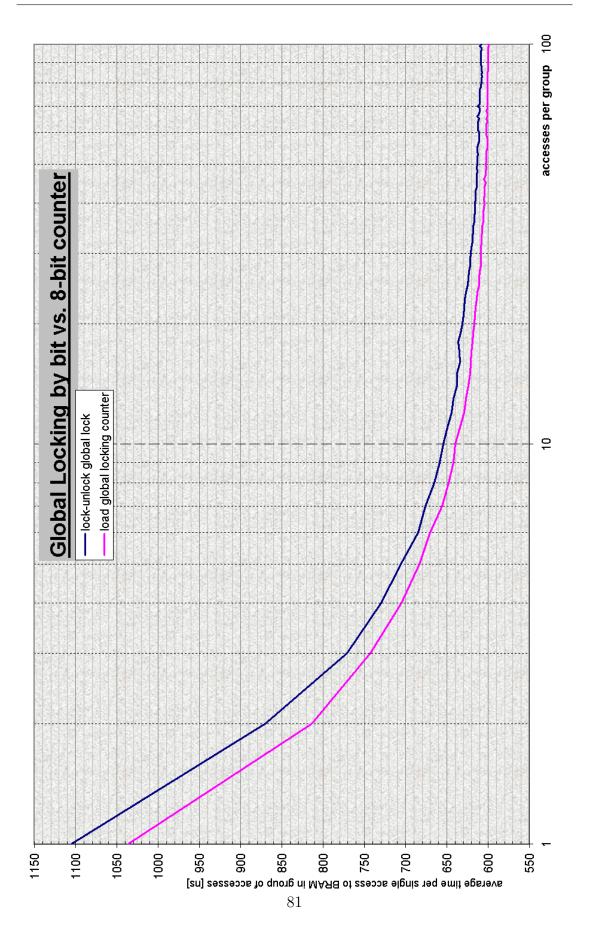

|                           |       | 5.2.2 The Global Locking Counter                        | 80  |

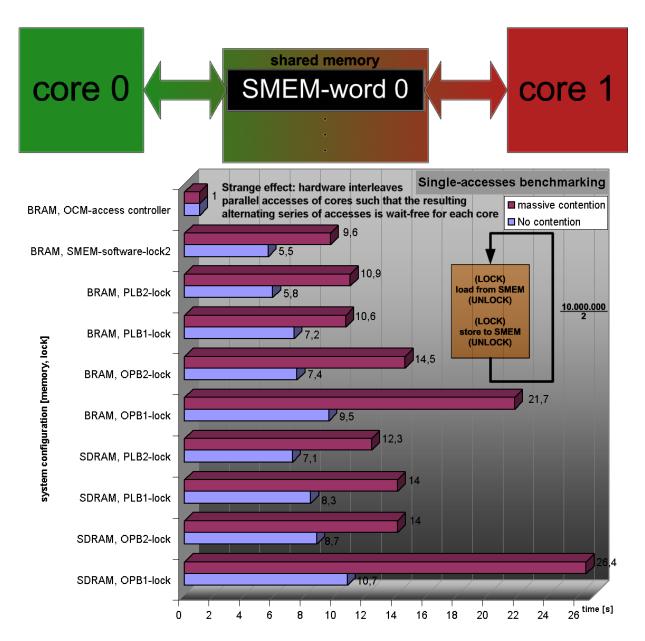

|                           |       | 5.2.3 Heavy-Load Single Access Benchmark                | 82  |

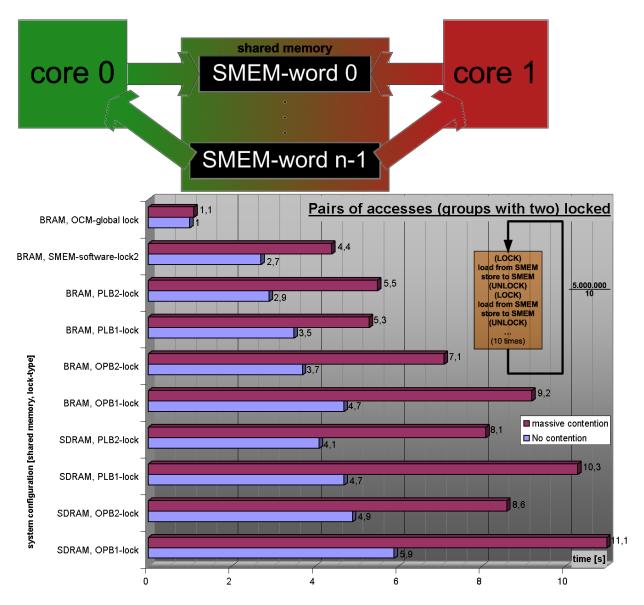

|                           |       | 5.2.4 Heavy-Load Paired Access Benchmark                | 83  |

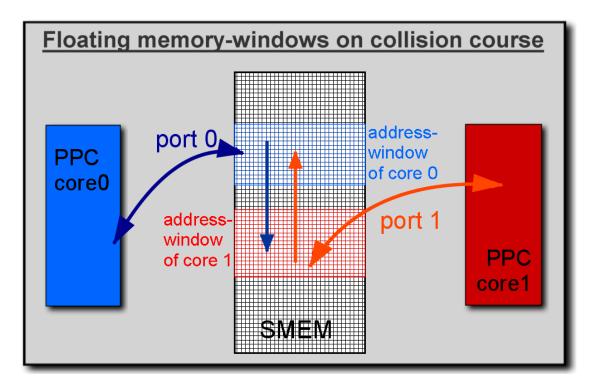

|                           |       | 5.2.5 Heavy-Load Floating Windows Benchmark             | 84  |

| 6                         | Con   | nclusion                                                | 88  |

|                           | 6.1   | Summary                                                 | 88  |

|                           | 6.2   | Future Work                                             | 90  |

|                           | 6.3   | Acknowledgement                                         | 92  |

| $\mathbf{A}$              | Dig   | ital Flow                                               | 93  |

|                           | A.1   | The Xilinx Development Board ML410 and the Xilinx FPGA  |     |

|                           |       | Virtex-4 FX60                                           | 94  |

|                           | A.2   | Hardware Flow                                           | 95  |

|                           |       | A.2.1 Setup of a Multi-core System with Xilinx EDK 9.2i | 96  |

|                           |       | A.2.2 Adding Individual IPs in Xilinx EDK               | 103 |

|                           |       | A.2.3 Adding Individual IPs Manually: from EDK to ISE 1 | 104 |

|                           | A.3   | Software Flow                                           | 110 |

|                           |       | A.3.1 Using the Xilinx Microprocessor Debugger (XMD) 1  | 11  |

|                           |       | A.3.2 Upload of Applications to the PowerPC Cores 1     | 113 |

|                           |       | A.3.3 The Xilinx Software Development Kit (SDK) 1       | 113 |

|                           |       | A.3.4 Single-Core Application-Management by the SDK 1   | 117 |

|                           |       | A.3.5 The Usage of Assembler                            | 119 |

|                           |       | A.3.6 The Directory-Structure                           | 120 |

| Re                        | efere | nces 1                                                  | 22  |

#### vi

# List of Figures

| 2.1  | Architectures of multiprocessor systems, simplified                    | 11 |

|------|------------------------------------------------------------------------|----|

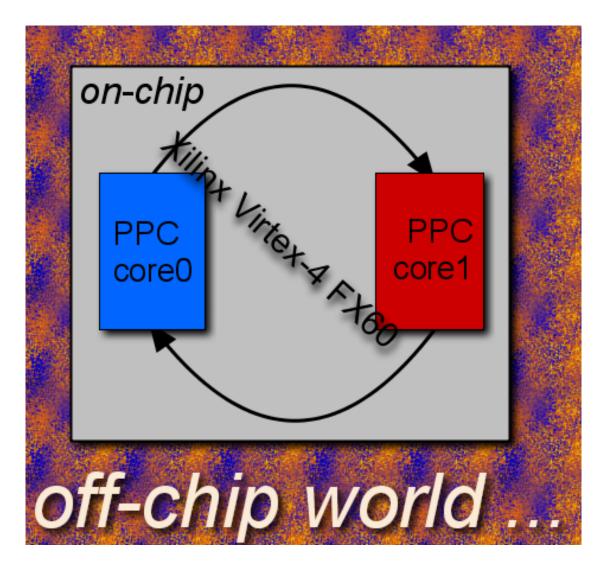

| 3.1  | Ideal communication stays on-chip                                      | 26 |

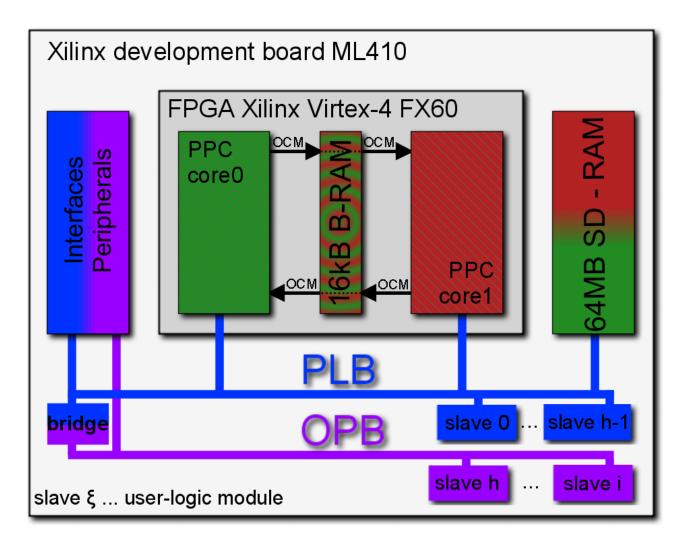

| 3.2  | Architecture of present dual-core system                               | 27 |

| 3.3  | Dual-ported B-RAM without low-level coherence                          | 29 |

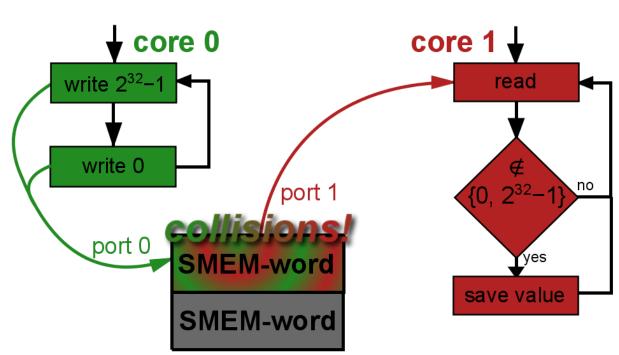

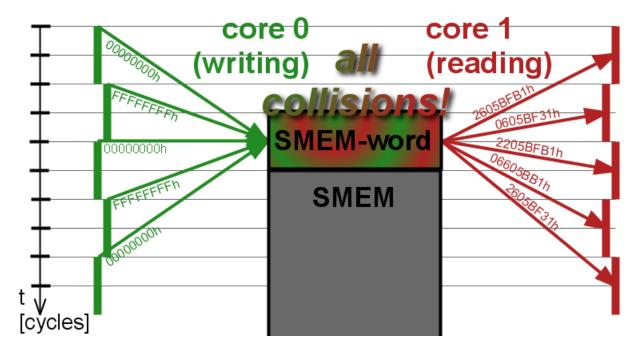

| 3.4  | Worst-case non-coherent access: no single correct value read           | 30 |

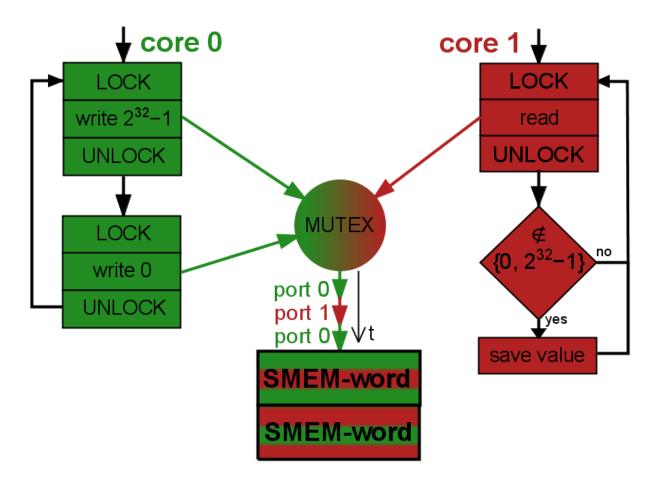

| 3.5  | Atomic access by locking                                               | 31 |

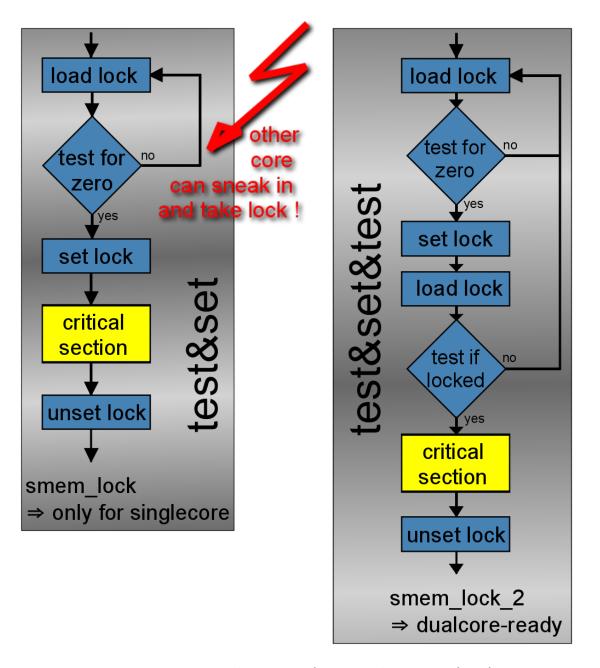

| 3.6  | From non-coherent test&set to coherent test&set&test                   | 33 |

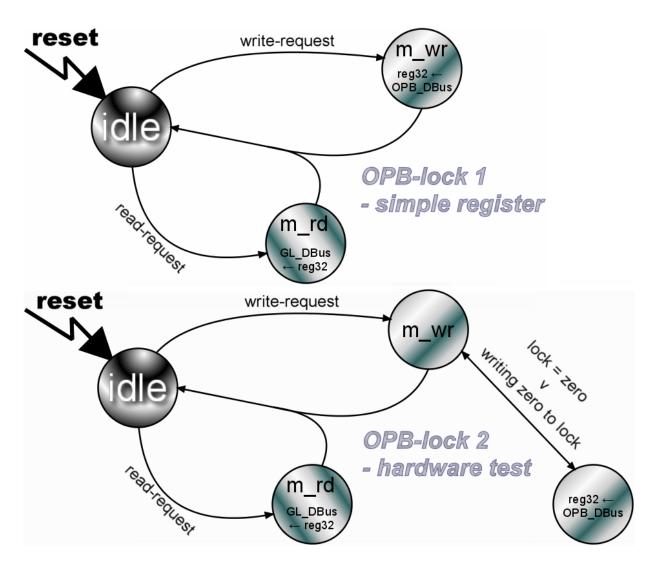

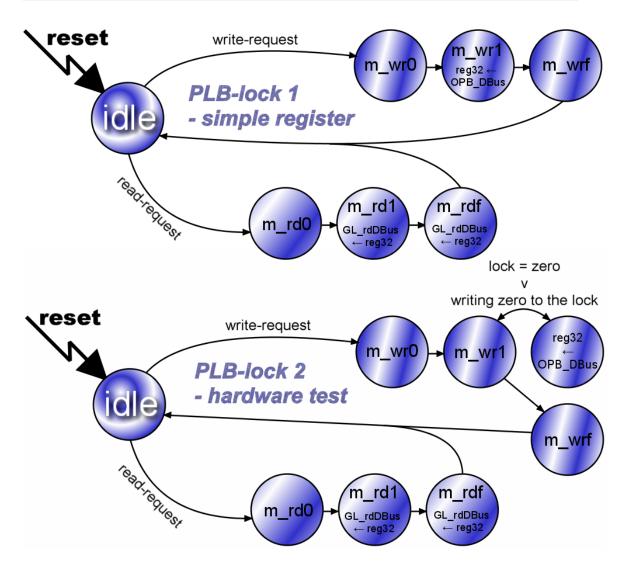

| 3.7  | State machines of both OPB-locks 1 and 2                               | 34 |

| 3.8  | State machines of both PLB-locks 1 and 2                               | 36 |

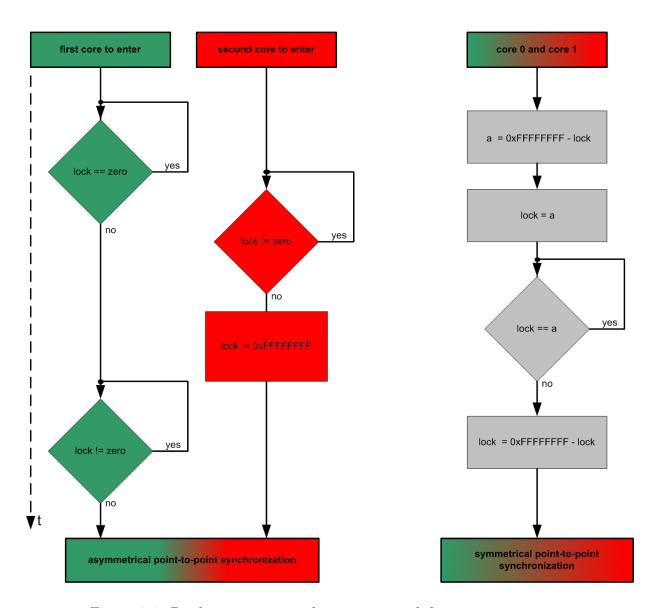

| 3.9  | Dual-core event synchronization with busy-waiting                      | 37 |

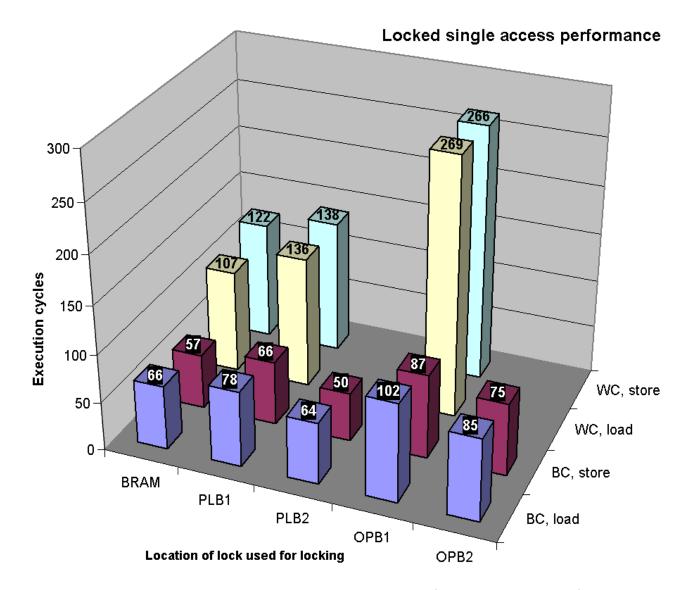

| 3.10 | Single access performance using spinning locks (no values: starvation) | 40 |

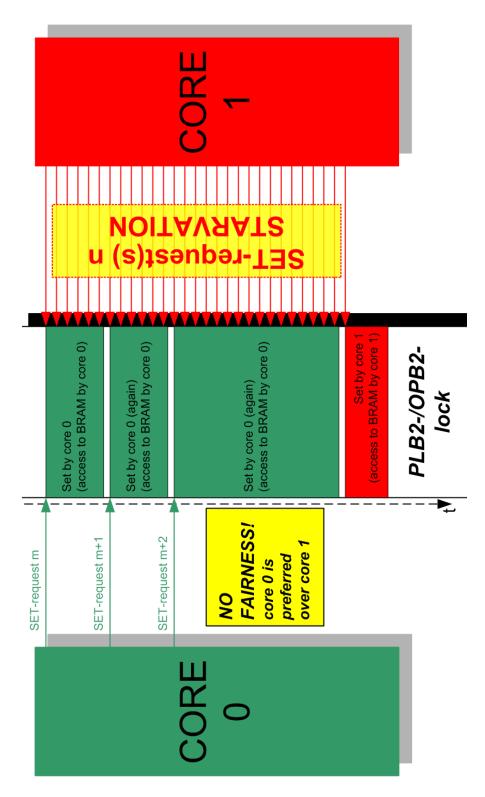

| 3.11 | Unfairness in relaying requests for the lock causes starvation: stores |    |

|      | to locked lock are ineffective                                         | 42 |

| 4.1  | Broken chain of control over accessing bus-slaves                      | 45 |

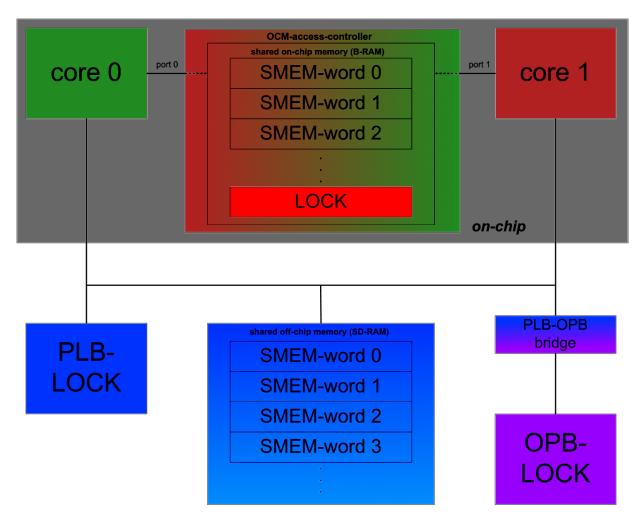

| 4.2  | The OCM-access-controller takes control over the BRAM                  | 46 |

| 4.3  | The OCM-access-controller delays requests for the BRAM if necessary    | 47 |

| 4.4  | Core-side addressing of the OCM-access-controller                      | 49 |

| 4.5  | Explicit locking, principle                                            | 50 |

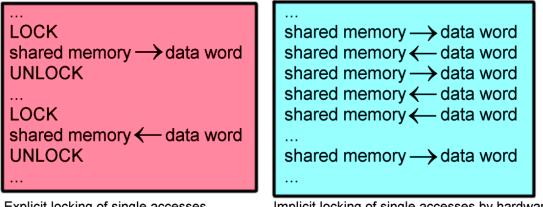

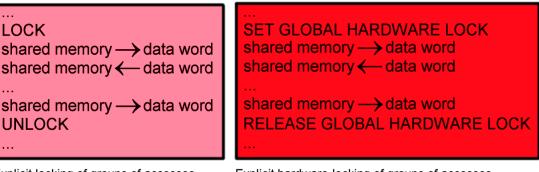

| 4.6  | Pseudo-code of explicit software vs. implicit hardware locking         | 50 |

| 4.7  | Pseudo-code for global locking                                         | 51 |

| 4.8  | Control- and Status-register of the OCM-access-controller              | 51 |

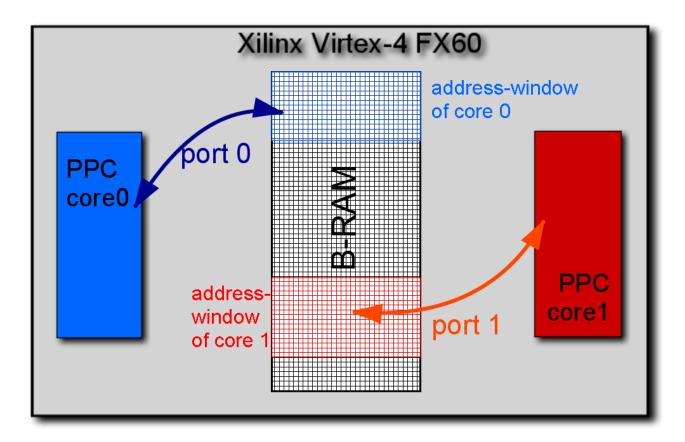

| 4.9  | Concurrent access by disjunctive shared memory windows                 | 52 |

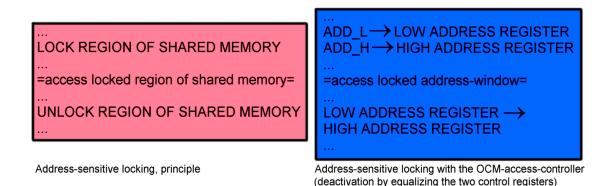

|      | Pseudo-code for locking an address-window                              | 54 |

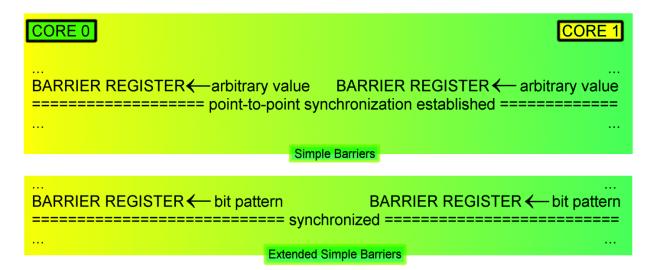

|      | Event-synchronization by hardware-barriers                             | 54 |

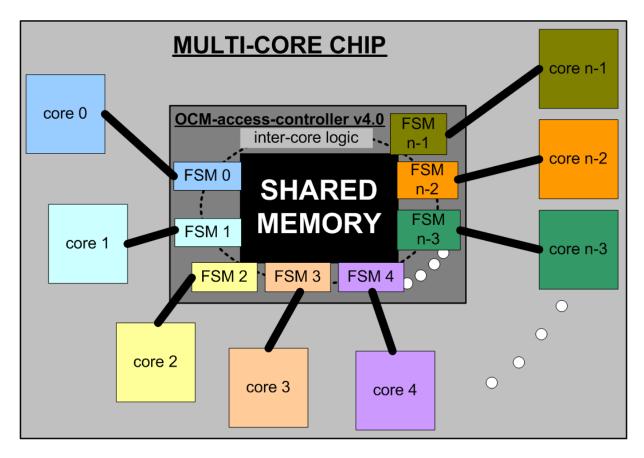

|      | Abstracted schematic of OCM-access-controller v4.0 for multiple cores  | 56 |

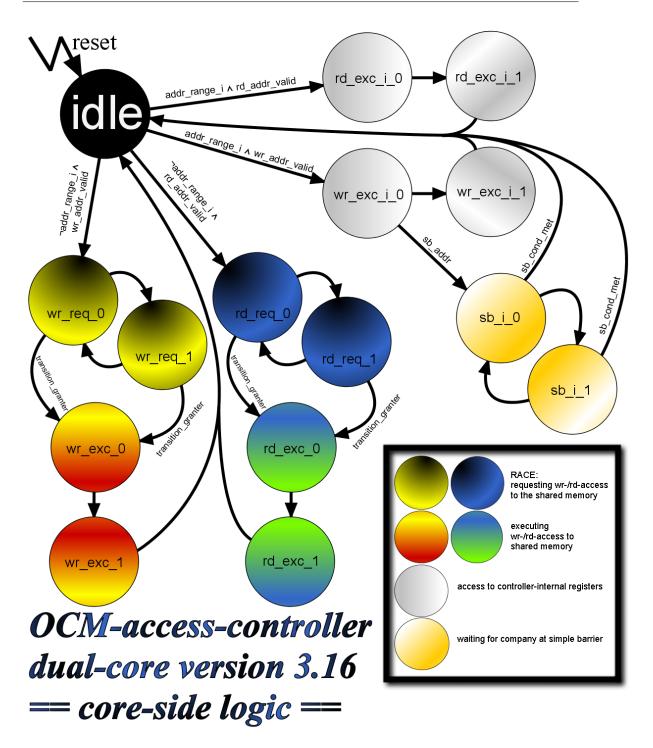

|      | Core-side state machine of OCM-access controller v3.16                 | 57 |

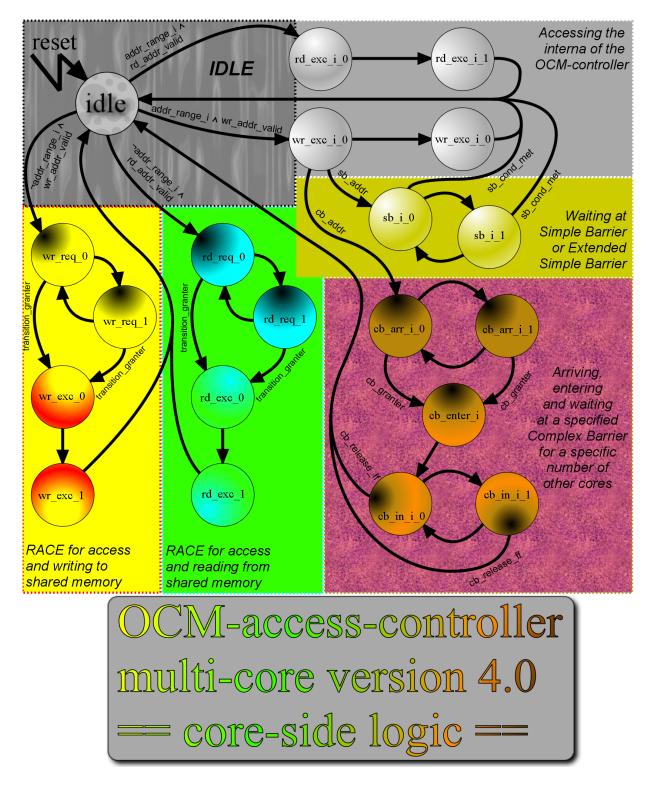

|      | Core-side state-machine for the beyond-dual-core case $(v4.0)$         | 58 |

| 4.15 | Principle of a fair and efficient race for access                      | 60 |

|      | Worst-case race                                                        | 60 |

|      | Fixed priority scheme: slices of an invariable register                | 61 |

| 4.18 | Variable Priority Scheme: Slices of a rolling register                 | 62 |

|      | Detailed single-access race for the shared memory using core-priorities     | 63  |

|------|-----------------------------------------------------------------------------|-----|

| 4.20 | Race for the global lock of the OCM-access-controller                       | 64  |

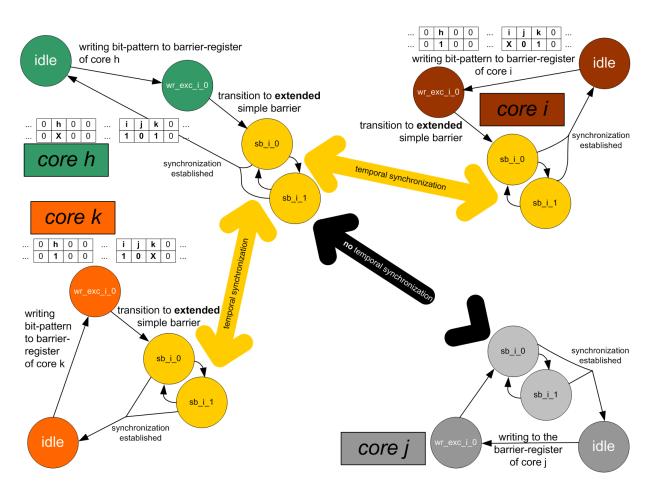

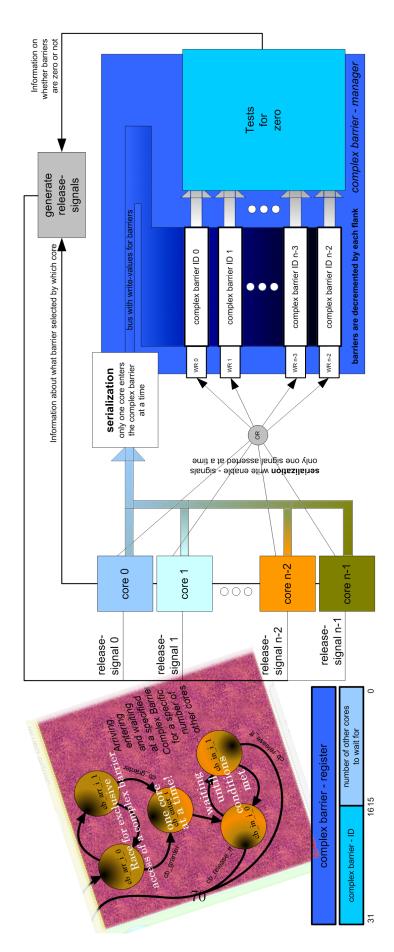

|      | Simple Barrier, principle: two cores synchronize temporally                 | 66  |

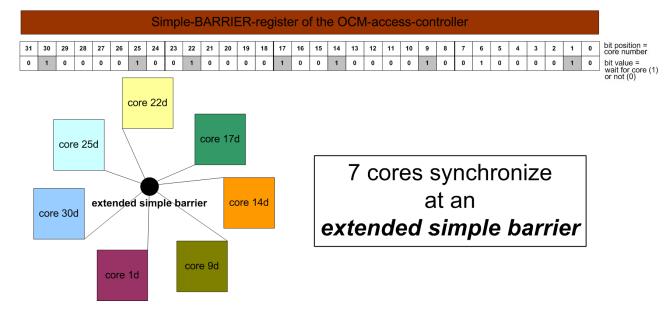

|      | Generation of the transition signal $sb\_cond\_met$ to leave simple barrier | 66  |

|      | Multiple selective synchronization at extended simple barrier               | 67  |

|      | Multiple cores synchronize by extended simple barrier                       | 68  |

|      | Generation of the release-signal for extended simple barriers               | 69  |

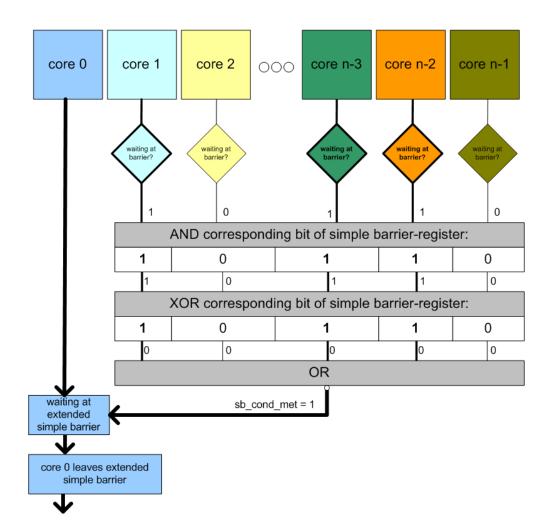

|      | Complex Barrier Implementation, abstracted                                  | 70  |

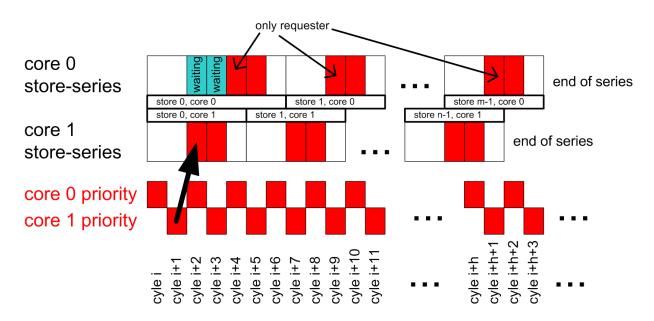

|      | Temporal overlapping of worst-case store-accesses                           | 73  |

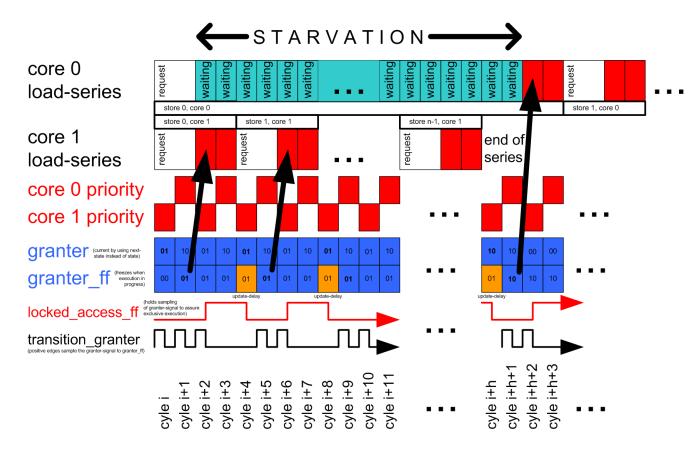

| 4.28 | Analysis of starvation caused by dual-core worst-case                       | 74  |

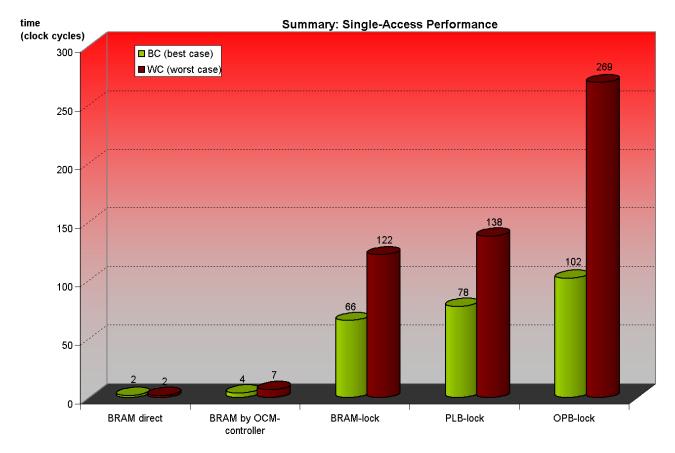

| 5.1  | Performance of single accesses to the BRAM using all methods                | 78  |

| 5.2  | All modules available for system benchmark configuration                    | 79  |

| 5.3  | Benchmarking: single accesses (no contention: only one core active)         | 82  |

| 5.4  | Benchmarking: paired accesses (no contention: only one core active)         | 83  |

| 5.5  | Benchmarking by moving memory-windows on a collision course                 | 85  |

| 5.6  | Results of benchmarking with floating windows                               | 86  |

| A.1  | High-level block diagram of the Xilinx ML410, taken from [Xil07e] .         | 94  |

| A.2  | Virtex-4 FX family, partial overview, taken from [Xil07h]                   | 94  |

| A.3  | Picture of the Xilinx ML410, from [Xil07e]                                  | 95  |

| A.4  | Creating a new project in the EDK                                           | 96  |

| A.5  | Enabling debugging over JTAG for one core                                   | 97  |

| A.6  | draft of basic system-architecture                                          | 97  |

| A.7  | deactivate port-filtering in the EDK                                        | 98  |

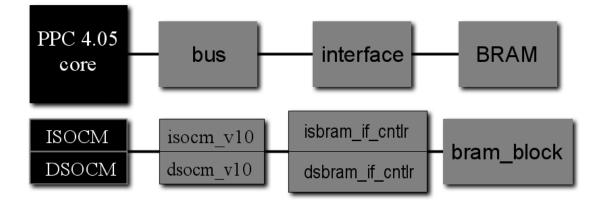

| A.8  | OCM-chain of IPs                                                            | 98  |

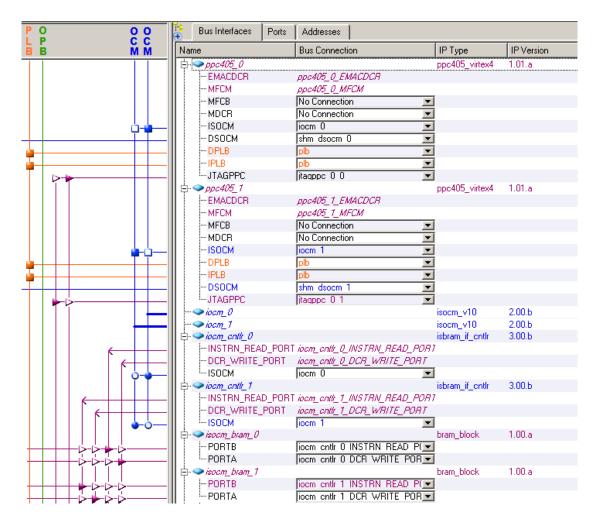

|      | ISOCM-chain, core-private                                                   | 99  |

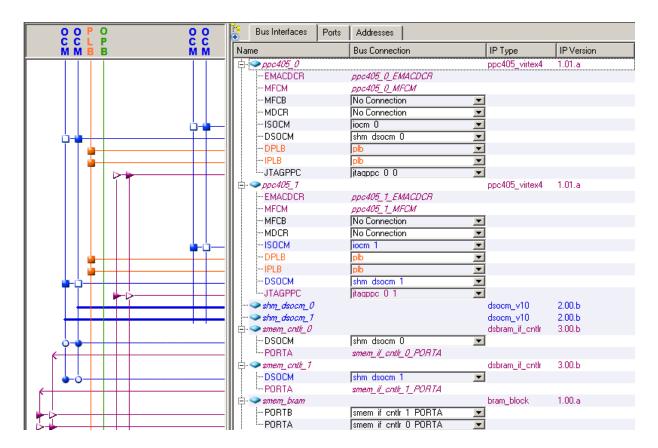

|      | DSOCM connections creating shared memory!                                   |     |

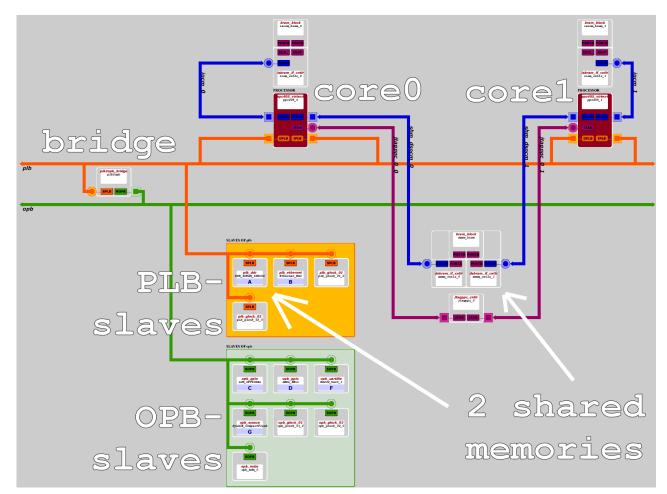

|      | Complete shared-memory system configuration                                 |     |

|      | address-ranges of all IPs in design                                         |     |

|      | The EDK peripheral wizard                                                   |     |

|      | Xilinx ISE                                                                  |     |

| A.15 | Synthesis of <i>IP ocm_access_cntrl</i> using XST                           | 106 |

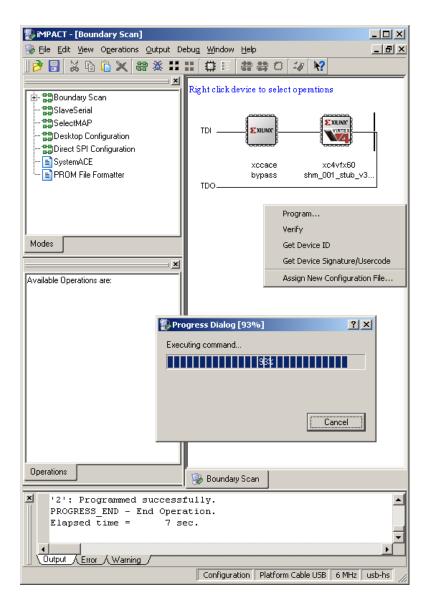

|      | Programming FPGA with iMPACT                                                |     |

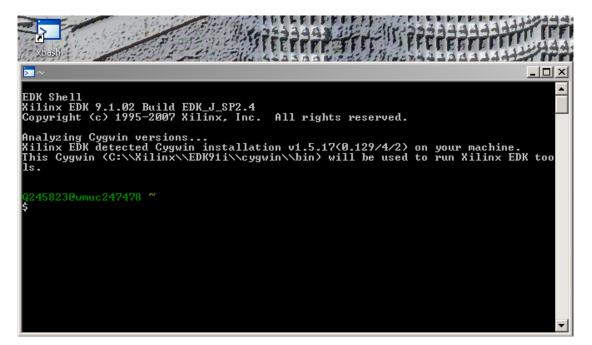

|      | <i>xbash</i> -prompt as universal tool to work with                         |     |

|      | Connect to dual-core design using XMD                                       |     |

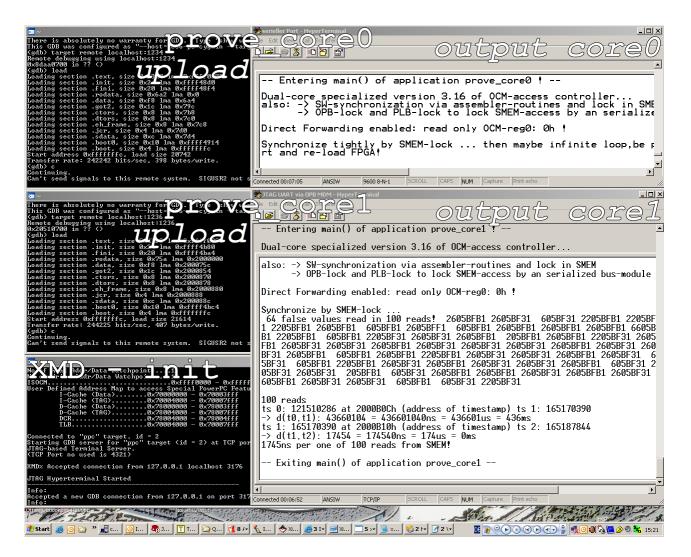

|      | Essential dual-core working environment                                     |     |

|      | Working environment of the Xilinx SDK                                       |     |

|      | References essential to core0- and core1- programs                          |     |

|      | Important project-properties for core0 and core1                            |     |

|      | Generation of a linker script in the SDK                                    |     |

|      | Asymmetrical linker scripts for core 0 and core 1                           |     |

|      | Run-configuration of the SDK (only for single-core applications)            |     |

| A.26 | The final directory structure evolved over this thesis                      | 121 |

## List of Tables

| 3.1 | Time for direct access to different lock-locations [clock-cycles]                                                         | 38 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Theoretical <i>best case</i> (contention-free) locking results [clock cycles].                                            | 39 |

| 3.3 | WC single locked accesses - code structure                                                                                | 39 |

| 3.4 | Spinning and locked single-access performance                                                                             | 40 |

|     | Core-Priorities determined by significance of single set bit Access-performance for single accesses in the dual-core case |    |

|     | Benchmarking: single accesses, exact values                                                                               |    |

# Chapter 1 Introduction

Parallelism is a rising star in the automotive sector, its advent is inevitable and is happening right now. The road map of leading semiconductor companies shows that multi-core chips will be introduced within the next couple of years. It is almost certain that in the next decade vehicles will be controlled by multi-core microcontrollers following the development of microprocessors in other areas.

The subject for this thesis originates in the growing demand for resources in the automotive sector. Electronic architectures in automobiles face a continuous increase in functionality, and the correspondingly increasing code requires additional memory. To handle the new functions in time, additional computational power is needed too. Single-core solutions are now the standard in automobiles, but due to the stringent environmental conditions the electronics must fulfill, increasing the core frequency of the processor cores is much more limited than in other fields.

In this thesis we gather information on the performance of multi-core architectures that seem usable for microcontroller designs in the automotive field. With the results, not only is judging conventional architectures easier, but it is also possible to interpret the results to suggest new hardware designs. Of course it is clear that the most efficient hardware architecture might not be the cheapest one. But since the issue here concerns safety-critical systems, cost will or should not be the sole criterion when looking at the results. Architectures that are quite common in the commercial field might not yield enough improvement in performance to give a significant advantage over a single-core system. Exploiting inherent parallelism in the current engine control software for single-cores is a promising possibility to improve the computational power. However, the complexity of today's engine control software makes it difficult to give an accurate estimate about the improvement to expect. The change from single- to multi-core is not without pitfalls and requires prudence. With an automobile being a safety-critical system, the testing alone may prove tedious and unveil unexpected problems.

The advent of parallelism is notoriously renowned in the field of computer science and there are enough examples that show how parallelism - in all its undeniable benefit - introduces totally new kinds of problems which, unfortunately, are nontrivial in the majority. However, with ever increasing miniaturization, introducing parallelism is a natural next step in the evolution of any microprocessor architecture (e.g. leading from the UltraSPARCI in 1995 to the dual-core 64b UltraSPARC in 2003 [ea04c]).

### 1.1 Outline of Thesis

We explain the background including all relevant basic concepts and give a broad overview of research done in the field of multiprocessing in chapter 2.

In chapter 3 the hardware platform used for this thesis is described briefly, then our system is supplemented by *software synchronization*. We then try to improve efficiency by using bus-slaves in hardware and analyze the results.

In the chapter 4 we complement the PowerPC dual-core system at hand with hardware facilities to improve synchronization. The benchmarking results and their interpretation is presented in chapter 5. A conclusion is given afterwards to sum up the results and usefulness of this thesis' results.

The appendix covers the vendor-specific step-by-step guide of the developed and used digital flow both for the hardware and software.

Please note here that none of the ANSI C-, Assembler- nor VHDL-code is printed in this thesis due to size limitations.

#### 2.1.4 Resources

In any computer system there are resources that are needed by processes to execute until their completion. Any operating system acts essentially as a *resource controller*, managing the resources of a given system to guarantee correct operation. The resources that must be managed are

- processor time

- memory

- devices

Also in systems that have only one processor there may be more than one process at a time to use the time the processor must wait for relatively slower operations like input-/output(i/o)-operations carried out by i/o-devices. The method that introduced the sharing of the resources of as system between more than just one process at a time is known as *multiprogramming*. With more than one program in execution on a single processor the complexity of the operating system increases significantly. The operating system must cope now with newly arisen problems ( $\rightarrow 2.1.6$ ), even though the system still has only one processing unit that must be switched between the active processes.

#### 2.1.5 The Memory Hierarchy, Caches

The term *memory hierarchy* comes from the fact that a system normally comprises different types of memory where the fastest memory coincides with the highest costs and thus smallest amount ([Sta01], 1.5). Due to today's high memory requirements there is almost always a high-capacity but slow memory present. The slower the memory accessed the longer the waiting time introduced by *waiting cycles*. To avoid such time-consuming access a small but faster memory called a *cache* is used to buffer read values for further accesses or even buffer writes (*writeback* cache) to the slower memory. Caches improve the average performance of a system significantly. The reason for this is the inherent locality of data due to the structure of the data used in programs (*spatial locality*) and the iterative, step-wise nature of programs (*temporal locality*).

To learn more about locality and the memory-hierarchy see [Sta01].

#### 2.1.6 Process Interaction

Processes that are active at the same time might not be aware of each other. According to [Sta01] this makes them simply competitors for the available resources. Coexistent processes can also be aware of each other, either because they were originally meant to cooperate directly to achieve their goals or because one process depends on the results of another. Due to the new situation coexistent processes create in a system, the operating system faces the following new control problems:

- Mutual Exclusion Resources that cannot be used by an arbitrary number of processes at the same time are commonly called *critical resources*, the section in the code of a program that accesses this resource is called a *critical section*. The problem of how to guarantee exclusive access to a resource is a new problem simply inexistent to systems where only one process is allowed to be active.

- **Deadlock** A *deadlock* is a very uncomfortable situation where at least one process cannot proceed its execution and is *stuck*. The processes in a deadlock are waiting for resources that are not just currently but indefinitely unavailable. It usually arises when process requests for critical resources are granted incrementally instead of granting all needed resources at once, avoiding the possibility of another process to snap up a still missing resource. But if the competitor never releases the resource (maybe because this process is also waiting for a resource before proceeding, or because of a failure) - we are in a deadlock. This problem is also possible if only one process can run at a time - but more processes may be active ( $\rightarrow$  multiprogramming): so one process can block all others and therefore the whole system.

- Livelock We speak of a *livelock* if mutual exclusion is guaranteed but the relative speed between processes can lead to sequences of actions that block each involved process. If processes are executed concurrently and are they are both releasing and obtaining a resource that each other wants, and this happens in a timely fashion that both of them cannot get the wanted resource each time they want it - then it is said that there is a livelock. A livelock may not go on forever, different relative speeds of execution can lead to a break of this sequence of actions. An easy example would be two processes that both set and reset their corresponding flags at the same time. Then the two processes also always test the others flag at the same time, always coming to the conclusion the opponent is in the critical section - and both resetting their flag without entering the critical section (s. [Sta01], section 5.2).

• Starvation In the case of *process-priorities* regarding resources it could happen that higher prioritized processes continuously access critical resources, preventing a process with a lower priority to get its turn. Also in the case that no priorities are present starvation might occur, due to unfairness, different access-frequencies, failures (e.g. *babbling idiot*), etc..

#### 2.1.7 Mutual Exclusion on Single-Cores

One common method of enforcing mutual exclusion on critical resources is by *implicit synchronization* ([Kop97], ch. 10) of the processes: the execution of the active processes is organized such that no process is interrupted when accessing a critical resource (simplest achieved by disabling interrupts [Sta01]). This requires off-line analysis of the processes to generate a flawless schedule, then, since there is only one processor, there cannot occur any conflicts at all. This method has the obvious drawback of limited flexibility: the operating system cannot interrupt a currently executing process at any arbitrary time.

A dynamic alternative to off-line analysis would be *priority inheritance protocols* like the *priority ceiling protocol* for real-time systems. It avoids deadlocks despite incremental requests for resources by elevating the priority of processes that are in a critical section (s. [Kop97], ch. 11).

Another solution are *locks*: the interruption of processes is possible with the risk that a currently locked resource is unavailable until the continuation of its locker.

#### 2.1.8 From Multiprogramming to Multiprocessing

A computing system that contains more than one simultaneously working processing unit is called a *multiprocessor* in case the processors all have access to a commonly shared memory (key property of a multiprocessor according to [TvS02]). In the case the processing units are even located on the same chip, today's term for this is a *multi-core processor* or *chip-level multiprocessor* (CMP). A processor with only one processing unit is called a *single-core processor*.

On the other hand, a *multicomputer* is a system that interconnects physically separated computer systems where each computer has its own private memory, leading to the field of *distributed systems* (see [TvS02] for details on remotely connected systems). The focus here as in this thesis lies on the current modern variant of multiprocessors, the multi-core processors.

With multiple processing units available it is possible to execute more than just one active process at a time, generating even more new problems, for instance: • Data coherence & consistency If processes are not just competing for resources but also *share* them (like possibly memory), then the processes must rest relaxed that the shared resource is always in a correct state. Coherence is assured as long as there is only one processing unit present in a system, but with more processes concurrently accessing a shared resource that allows this it might happen that the shared resource is not consistent with the view of the accessing processes, that is, the shared resource is not in a coherent, a correct state.

#### 2.1.9 Synchronization

With truly parallel execution on multiprocessors and multi-core processors, implicit ordering of the execution paths is not enough (s. next section). As in dynamically scheduled uniprocessor systems it is necessary to provide ([CS99], 1.3)

- data synchronization  $\Rightarrow$  mutual exclusion

- event synchronization ⇒ informing other processes that a certain point of execution is reached

In analogy, parallelism in problems themselves can be exploited using *temporal* parallelism or data parallelism. An example for the former would be pipelining, in the latter the data is split into independent parts. See [RM06] for more about how to solve problems in parallel.

There are three major components of a synchronization event:

- 1. Acquire synchronization method

- 2. Waiting algorithm for the synchronization to become available

- 3. Release synchronization method, enabling other processes to proceed pas a synchronization event

Waiting can be of type *busy-waiting* or *blocking*, whereas locking by busy-waiting is not a preferred locking technique. From [CS99], 5.5.1:

Busy-waiting avoids the cost of suspension but consumes the processor and cache bandwidth while waiting. Blocking is strictly more powerful than busy-waiting because, if the process or thread that is being waited upon is not allowed to run, the busy-wait will never end. Busy-waiting is likely to be better when the waiting period is short, ... According to [CS99] and [Her88], a shared data structure is said to be *lock-free* if the operations defined on it do not require mutual exclusion over multiple instructions. If the operations on the data structure guarantee that some process will complete its operation in a finite amount of time, even if other processes halt, the data structure is *nonblocking*. If it can be guaranteed that every process will complete its operation in a finite amount of time, the data structure is *wait-free*.

#### 2.1.10 Mutual Exclusion using Locks

With multiple physical processors *explicit synchronization* is needed to enforce mutual exclusion when accessing critical resources. One common synchronization mechanism is a *lock*. Critical resources may be protected by their corresponding locks. A lock is *taken* by a process if that process successfully acquires it, giving it the exclusive access to work with the resource corresponding to this lock. The lock is said to be *owned* by that process. A lock is *free* if no process currently owns it. Processes possessing a lock must release this lock as soon as they leave their critical resource, otherwise other processes may starve or deadlocks might occur.

There are software algorithms to achieve mutual exclusion, mainly Dekker's Algorithm and Peterson's Algorithm. They both have in common the continuous looping until it is assured that the critical section can be entered exclusively. This busy-waiting named looping is not very efficient, even more the first algorithm is quite complex. Even worse, some prerequisites must be fulfilled by the underlying memory-subsystem to guarantee the correctness of the algorithms, that is: a sufficiently strong consistency model (s. 2.1.19). Also, the algorithms mentioned in the previous paragraph work with dedicated flags to achieve mutual exclusion. Those flags indicate whether one process has the right to enter its critical section or not. Hence a kind of locking is achieved by the algorithms, but there is no explicit single lock - all flags together represent the lock.

Hardware support for mutual exclusion is given primarily by special machine instructions that allow to manage a single memory cell to represent a single lock for a given critical resource. According to the hierarchy introduced in [Her88], atomic operations are ranked depending on their relative power (listed in ascending order):

- 1. atomic *load/store*

- 2. atomic Test and Set, Fetch and Store, Fetch and Add, Exchange

This means that *atomic* read/write registers that are *safe* (coherent), are less powerful and therefore less useful in the construction of lock-free data-structures than, for instance, the *Test and Set* instruction. Queues, lists etc. using primitives of lower power would be considered in this ranking to be even more "powerful".

#### 2.1.11 Semaphores

A breakthrough in coping with concurrent processes was the introduction of semaphores with Dijkstra's treatise in 1965 [Dij65]. A semaphore is an *abstract structure* that contains an integer value. Processes can cooperate with each other by using a semaphore and issuing two kinds of signals to it:

a *test-* and an *increment-*signal. Both signals must be handled atomically. The test-signal corresponds to a request, the targeted semaphore decrements its value. The requesting process is blocked in case the semaphore's value is negative. Leaving a critical section a semaphore receives an increment-signal, resulting in an increment to be applied to the semaphore-value. The greater the initial value of a semaphore, the more processes can signal a test without being blocked. A semaphore that implements a fair first-in-first-out (FIFO) queue for handling the processes waiting for it is called a *strong semaphore* [Sta01].

The simplest type of semaphore is the *binary semaphore* - it corresponds with the lock described in the previous section. However, one should not misunderstand a semaphore for a lock - semaphores are not concerned with consideration of blocking or busy-waiting. Semaphores introduce an additional level of abstraction, in principle the signalling avoids busy-waiting and makes much more efficient scheduling mechanisms possible (blocked processes could be easily detected and put into a queue by the operating system). Nevertheless, in reality semaphores happen to be implemented using locks and hardware-primitives like the test-and-set operation. Of course this implementation is hidden from the applications using a semaphore.

#### 2.1.12 Event Synchronization by Barriers

Event synchronization forces processes to come together at a certain point of execution. They *enter* the barrier, *wait* for the other processes and then all processes *leave* the barrier together. Barriers can be used to separate distinct phases of computation. However, according to [CS99], p.358 barriers are normally implemented without special hardware-support, using locks and shared memory instead.

#### 2.1.13 The Parallel Random Access Machine (PRAM) Model

There exist some *abstract models* that can be used for designing parallel algorithms without the need to concern about the underlying implementation of a given system. Parallel algorithms are a major application for parallel systems. In accordance with [RM06] we look at the PRAM-model as an abstraction of a parallel system, consisting of N identical processors, a shared memory and a *memory*-

*address unit* (MAU) that allows all processors to access this shared memory. The following acronyms are stated here for further usage in this thesis:

... a problem might arise when more than one processor tries to access the same memory location at the same time. The PRAM model can be subdivided into ... categories based on the way simultaneous memory accesses are handled.

Exclusive Read Exclusive Write (EREW) PRAM In this model, every access to a memory location (read or write) has to be exclusive. This model provides the least amount of memory concurrency and is therefore the weakest. Concurrent Read Exclusive Write (CREW) PRAM In this model, only write operations to a memory location are exclusive. Two or more processors can concurrently read from the same memory location. This is one of the most commonly used models.

Other models exist, but are irrelevant considering the practical nature of this thesis. It is pointed out here that the EREW model does not take any advantage of a multi-ported memory - like on a bus, all accesses are exclusive and thus serialized.

#### 2.1.14 Real-Time Systems (RTS)

Referring to [Kop97], if the *correctness* of a system not only depends on the correct resulting values but also of their deliverance *in time*, then such a system is called a *real-time system*. The time when a result must be available is called a *deadline* (*completion deadlines*). The problem of ordering the execution of processes in a way that all deadlines are met is called the *scheduling problem* and is nontrivial. In order to give any guarantees about the correct function of a real-time system the execution time of processes must be known in advanced, or more precise: the longest execution time. This time is commonly referred to as the *worst-case execution time* (WCET). Computing this time becomes more complicated the more abstract the definition of the processes is. Speculative enhancements of designs (caches, speculative execution, ...) increase *unpredictability* and result in relatively rough estimates for the WCET. The WCET is an important area of research, an introduction in the subject as well as a broad overview is given in [Sto06].

Many systems that are *safety-critical* are real-time systems per definition (e.g. processes in nuclear plants, aeroplanes etc.). An automobile must also meet some stringent timing requirements in order to react to its user's input *in-time*, for instance the *break-* or *steer-by-wire* units.

#### 2.1.15 Fault-Tolerant Systems (FTS)

Closely related to RTS are fault-tolerant systems, introducing or using present *redundancy* in resources to be able to handle errors (the results of faults) that might lead to failures of a system. The seriousness of errors that might be tolerated by a given FTS depends on the amount of redundancy and the mechanisms used.

Fault tolerance is not a focus in this thesis. It is mentioned here for completeness and to point out alternative usages of multiple processing cores in this field. Refer to [TvS02] for fault-tolerance in distributed systems and [Kop97] for fault-tolerance regarding real-time systems.

#### 2.1.16 Architectures of Multiprocessor Systems

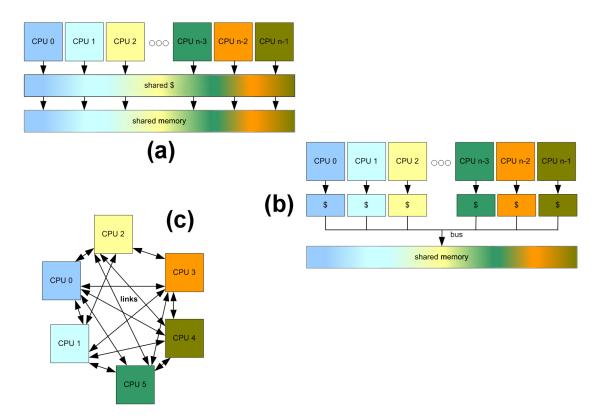

Figure 2.1: Architectures of multiprocessor systems, simplified

In accordance with [CS99] common types of small- to medium-scale multiprocessor system-architectures are presented in figure 2.1. These architectures provide a global physical address space, access to all of main memory is possible from any processor. Such a system is often called a *symmetric multiprocessor* (SMP).

Non-symmetric architectures are not considered here since they are irrelevant regarding this thesis.

Architecture of figure 2.1 (a) can make sense for a multi-core chip where the cores would *share* an *on-chip first-level cache*. Besides that this architecture was used mainly in the mid-1980s when it was typical to connect a low number of processors on one motherboard. More common today is to have local first-level caches and shared second-level caches.

Architecture of figure 2.1 (b) is the most common form for up to 20, 30 processors. A *bus* shared amongst the processors connects them to the shared memory. The number of processors to connect is limited by the bandwidth of the shared bus and the efficiency of the local caches that decrease the average-case load on the bus.

Simplicity is supported by using a bus, but for a massive parallel systems containing many processors a single shared bus might significantly limit performance. Hence, to efficiently connect a large number of processors the bus must be replaced by more efficient means of interconnections, typically a scalable point-to-point interconnection network. In figure 2.1 (c) such an interconnection network is given by links between each pair of processors. A *link* is a direct connection between any two processors. With the number of links necessary for full point-to-point connections in networks being a square function, pure linking can become too costly. A *switching network* allows to connect any two processors in a network, but it is possible that a connection cannot be established until other connections and hence resources are released. This depends on the amount of communication and the design of the switching network. Look into [CS99], chapter 10 for in-depth information on interconnection network design.

The discrepancy between using a bus and using links or switches is quite apparent. The results of this thesis make this difference also quite obvious.

#### 2.1.17 Caches

Local caches reduce the *average load* on the bus, therefore increasing the number of processors that can be connected. Still the worst-case would be to assume all caches to be invalid, leading to a bus-load the interconnection network might be unable to handle. But caches not only add unpredictability (which makes them quite unattractive for real-time systems), they also introduce a new problem in parallel systems called *cache coherence*. Burdened with these disadvantages, caches become very uncomfortable in respect to real-time systems and are thereby often avoided as a whole. As an example ([CS99]) the second-level cache of all the 2048 alpha-processors of the CRAY T3D were deactivated simply to avoid the longer accesses to shared memory introduced by cache-misses. A very comfortable by-product: *no cache, no cache-coherence* to cope with.

#### 2.1.18 Coherence

The term *coherence* was already mentioned briefly in section 2.1.8. Coherence in the uniprocessor case is a property that simply states that a read returns the *last* value written. In the parallel case this gets more complicated since there are parallel programs interacting such that a location in memory can be accessed concurrently by different processes on different processors.

From [CS99] we take the definition of a *coherent multiprocessor system*:

... we say that a multiprocessor system is coherent if the results of any execution of a program are such that, for each location, it is possible to construct a hypothetical serial order of all operations to the location ... that is consistent with the results of the execution and in which

- 1. operations issued by any particularly process occur in the order in which they were issued to the memory system by that process, and

- 2. the value returned by each read operation is the value written by the last write to that location in the serial order.

With this definition it is clear that all memory-accesses themselves must be *atomic*; if they were not, reading a currently written memory location can result in an arbitrary bit-value. Clearly, such a scrambled bit-value is not the result of any total ordering of the processes involved. It is interesting to add here that a bus simplifies this problem by its inherent property of *serialization*: only one action can be done on the bus at one time (assuming a one-channel bus).

It should be obvious by now how caches complicate things by introducing *cache-coherence*. Additional complex measures like *bus-snooping* (MESI, Dragon - s. [CS99]) are necessary to guarantee coherence for the more complex caching-methods as write-back caches. This additional overhead can be avoided by simply using no caches, it eases the handling of real-time systems greatly ( $\rightarrow 2.1.14$ ).

#### 2.1.19 Consistency

In essence, coherence says that a written value will eventually become visible to another processor core or other cores. But what is not defined is when this written value becomes visible. In parallel programming it is often desired to establish an order between reads and writes of a single and multiple programs or processes, in more detail taken from [CS99] again: ... Coherence says nothing about the order in which writes to different locations become visible. ... A *memory consistency model* for a shared address space specifies constraints on the order in which memory operations must appear to be performed (i.e., to become visible to the processors) with respect to one another. This includes operations to the same locations or to different locations and by the same process or different processes, so in this sense memory consistency subsumes coherence.

Strict consistency is the most strict kind of consistency ([TvS02]:

The most stringent consistency model is called **strict consistency**. It is defined by the following condition:

Any read on a data item x returns a value corresponding to the result of the most recent write on x.

Since time is unambiguous in uniprocessor systems strict consistency is normally present there. But in the multiprocessor case this consistency model might be far too restrictive, maybe even severely limiting average performance. But it may well be applicable for multi-core systems due to the common clocking on one chip-die.

As a form of weaker consistency sequential consistency is quite common for multiprocessor systems (also called *linearizability*). Weakening consistency even further we go toward distributed systems with *causal consistency*, *FIFO consistency*, *release consistency* etc., for details on those also called *data-centric* as well as also *client-centric consistency models* please look into chapter 6 of [TvS02].

Referring to the sufficient conditions for preserving sequential consistency in [TvS02] it is easy to see that using a bus for interconnecting our processor cores simplifies achieving this type of consistency by its inherent serialization. Still the consistency model has to be guaranteed by the bus protocol itself. One must be aware that it is *easy to violate such a strict consistency model*. For instance, priorities assigned to different processor cores may lead to older requests for access to be carried out after more recent accesses with a higher priority. So *starvation* is also a *clear violation of strict consistency*. Even worse, if a compiler rearranges the order of accesses to memory, consistency is violated before the hardware gets involved. Hence it might be necessary to prevent such optimizations, e.g. by using the keyword *volatile* when programming in ANSI-C.

#### 2.1.20 Scalability

Since this thesis is concerned only with small- to medium-scale multiprocessor systems, large-scale multiprocessor systems may not seem important at all. Still, looking at scalability may uncover some of the bottlenecks also present in smallscale multiprocessor systems. For instance, looking at bus-based multiprocessor systems it is stated in [CS99] that extending a bus increases the latencies, resulting in lower usable bandwidth and thus lower maximum frequencies. More processors or nodes connecting to the bus also degrade the signal quality and hence performance. Clearly a bus-based system is not scalable over a certain technology-specific point.

A glimpse at the early attempts to scale bus-based multiprocessor systems is given in [ea93]:

The performance of earlier bus-based multiprocessor machines had demonstrated performance degradation with more than four processors connected to the bus. Cache coherence traffic and bus contention made more processors counterproductive.

It becomes obvious by studying the results of this thesis (s. chapter 5), the limitations introduced by a bus are relevant also with only a few processor cores present, in particular when performance is time-critical.

#### 2.1.21 Transactional Memory (TM)

Transactions are a very useful abstraction, grouping a series of actions and executing them with the following properties holding ([TvS02]):

The all-or-nothing property of transactions is one of the four characteristic properties that transactions have. More specifically, transactions are:

- 1. Atomic: To the outside world, the transaction happens indivisibly.

- 2. Consistent: The transaction does not violate system invariants.

- 3. Isolated: Concurrent transactions do not interfere with each other.

- 4. Durable: Once a transaction commits, the changes are permanent.

These properties are often referred to by their initial letters, ACID.

In addition we state from [TvS02]:

A transaction that completes successfully *commits* and one that fails *aborts*. ... we will call this property *failure atomicity* to distinguish it from a more expansive notion of atomic execution, which encompasses elements of other ACID properties.

Transactions originate from database-design in the world of business where series' of operations must be executed as a whole or none at all (like transfers on accounts). The power of using transactions comes from the fact that if any action of the transaction fails, the whole transaction has no side effect.

Transactional memory (TM) offers a modern and comfortable solution to introduce more abstraction at the software designer's level. As is written in [LR07]:

The basic idea is very simple. The ACI properties of transactions provide a convenient abstraction for coordinating concurrent reads and writes of shared data in a multi-threaded or multi-process system. Accesses to shared data originate in computations executing on concurrent threads that run on one or more processors. ... Today, this coordination is the responsibility of a programmer, who has only low-level mechanisms, such as locks, semaphores, mutexes, etc., to prevent two concurrent threads from interfering. ... Transactions provide an alternative approach to coordinating concurrent threads. A program can wrap a computation in a transaction. Failure atomicity ensures the computation completes successfully and commits its result in its entirety or it aborts. In addition, isolation ensures that the transaction produces the same result as it would if no other transaction were executing concurrently. ... If a programmer's goal is a correct program, then consistency is important, since transactions may execute in unpredictable orders. It would be difficult to write correct code without the assumption that a transaction starts executing in a consistent state. Failure atomicity is a key part of ensuring consistency.

Despite today's hype for transactional memory consider this ([TvS02]):

Transactions are not a panacea. It is still (all too) easy to write an incorrect concurrent program, even with transactional memory.

The concept and idea of transactional memory and the related work done in this field (essentially hardware-acceleration, s. more in the succeeding section 2.2.3) heavily influenced the development of this thesis.

### 2.2 Related Work

A rough overview about the research and related work that is more or less related to this thesis is given in this section. It must be noted here that general design practice is mentioned along with references of concrete related work. An interesting fact to point out is that in parallel systems *performance is not always the main concern*. As can be seen in [ea04a], research is also concerned about how to *reduce* die area and thus *costs* in parallel systems by let adjacent processor cores share their resources (even caches, floating point units etc.) while trying to keep the performance degradation as low as possible.

#### 2.2.1 Mutual Exclusion

The criteria against which to judge any locking mechanism are [CS99]:

- low latency

- low traffic

- scalability

- low storage cost

- fairness

If the underlying hardware has no support for mutual exclusion, locking must be done by software alone. Still, improving efficiency beyond the level pure **software approaches** can offer needs support by an atomic *test&set-*, *exchange-*, *swap-*, *fetch&op-* or *compare&swap-instruction* provided by the hardware. The atomicity condition for these instructions must be fulfilled regarding all processors in the system, not for one alone (chapter 3 shows what happens if this is violated).

According to [CS99] it becomes more common to implement a pair of **special instructions** to access a *synchronized variable* instead of a single read-write-modify instruction as mentioned in the previous paragraph. From [CS99]:

The first instruction, commonly called *load-locked* or *load-linked* (LL), loads the synchronization variable into a register. It may be followed by arbitrary instructions that manipulate the value in the register - that is, the modify part of the read-modify-write. The last instruction of the sequence is the second special instruction, called a *store-conditional*. It tries to write the register back to the memory location (the synchronization variable) if and only if no other processor has written to that location (or cache block) since this processor completed its LL. An example for a processor architecture that uses such a pair of special instructions is the Power PC 405 used in this thesis ([IBM05] and [Xil07g], appendix D).

Some first implementations of **locks in hardware** used a set of *lock lines* on the bus interconnecting the multiple processors. A processor that wanted to lock asserted a free locking line, a *priority circuit* elected the winner in case of multiple concurrent requestors [CS99]. Clearly such a hardware approach was inflexible since the number of locks and the waiting algorithm is fixed. Providing more locks could only be accomplished by the overlaying operating system that used these hardware mechanisms.

A similar implementation was realized in the **CRAY X-MP** [ea89]: a set of *lock* registers was shared by the processors and even allowed to be assigned to certain processes. But with only a small fixed number of shared registers this approach needed the operating system to make use of this underlying hardware to provide the software with a variable number of higher-level locks in memory.

About the **performance** of such software locking methods based on a special atomic instruction is said in [CS99]:

Consider the atomic exchange or test&set lock. It is very low latency if the same processor acquires the lock repeatedly without any competition, since the number of instructions executed is very small and the lock variable will stay in that processor's cache. However, we have seen that it can generate a lot of bus traffic and scales poorly as the number of competing processors increase.

So, with increasing competition for a critical resource the above busy-waiting scheme for a lock might lead to overloading the bus and *thrashing* ([Kop97]) of the overall multiprocessor system. A way to prevent the overhead in communication to explode by increased contention is by using the advanced *ticket locking* algorithm as described in [CS99]:

Every process wanting to acquire the lock takes a ticket number and then busy-waits on a global **now-serving** number ... until the **now-serving** number equals the ticket number it obtained. To release the lock, a process simply increments the **now-serving** number so that the next waiting process can acquire the lock.

Advanced lock algorithms like the TICKET-LOCK described previously prevent all cores to rush for a lock when it is released and therefore avoid starvation with the one-way cycling of the ticket (like a token) between the processors. For further information on advanced locking algorithms see [CS99], 5.5.3. [MS95] starts with a somewhat theoretical approach toward the question which of the atomic primitives test & set, ... to implement in hardware - and where: in the cache- or the memory-controller. It is also asked which coherence policy should be used for atomically accessed data and different answers to those general questions are examined, resulting in some experimental results. The paper can be recommended as an advanced reading on atomic primitives. In this context [CL97] is interesting in the aspect that it shows how cooperation between a compiler and a memory coherence protocol is able to improve the performance of Fortran programs running on distributed shared memory systems.

In [ea90] the architecture of a **RISC-based multiprocessor** is described. The goal was to bring many processors on one chip. In that perspective the paper is describing an approach for a multi-core chip, although the term is not used yet. Each processor has *12 channels* to send data to the other processors, 4 bytes can be sent on a channel without blocking the sending processor. In a multi-core chip these channels between the processors can be easily provided on-chip as well. With *compiler-support* the channels are used to coordinate the processes running on the different processors:

The channels are used to execute parts of the program which are inherently sequential and only contain instruction level parallelism. The use of channels allows processors to drift in relation to each other ... The execution of operations on different processors is scheduled by the compiler. ... Compiler techniques for efficiently allocating a fixed number of channels have already been developed.

An important work with respect to this thesis is [NP00] where the frequent synchronization primitives locks, barriers and lock-free data structures are the focus of attention. The classical implementations of those primitives are compared against **hybrid synchronization primitives** that use hardware support and also the caches (implementation on a cache-coherent system) to improve efficiency and scalability of the primitives. To state a result from [NP00], the hybrid test&set locking is over twice as fast as the classical one without hardware support.

An example for a **specialized multi-core chip** is the HiBRID-SoC architecture from [ea02]. A DSP-, RISC- and VLIW-core are connecting to all their *common interfaces* by a 64-bit AMBA AHB bus. One of those interfaces connects them to the external SD-RAM. For *fast inter-core synchronization* each pair of the three cores share a block of *dual-ported memory on-chip*. Caching is not done for the on-chip but for the off-chip SD-RAM. This configuration shows some relevance regarding the hardware configurations used for this thesis (s. section 5.2.1).

#### 2.2.2 Event Synchronization

In multiprocessor systems **interrupts** can be used to signal events between processors, maybe by using a dedicated shared memory region to convey data ([CS99]). **Barriers** are normally implemented using locks, shared counters or flags. A barrier for an arbitrary number of processors is called a *centralized barrier* when it uses only one counter, one lock and a single flag. When barriers are implemented using locks the barrier algorithms have the same problem as locking algorithms:  $\Rightarrow$  all the processors that want to block at a barrier contend for the same lock.

One way to circumvent this bottleneck is to equip the system with **hardware barriers**. Barriers between an arbitrary number of processors can be realized using a *separate synchronization bus*. A simple wired-AND line is enough - all processors reaching a barrier assert their signal at this line. As soon as all processors are arrived the signal line yields 'high', releasing the waiting processors all at once. [ea90] explains the drawback of the *idle time* of a processor waiting at a barrier

and shows how compiler-support can help to improve this using **fuzzy barriers**:

The waiting of processors at barriers is reduced by using compiletime techniques to find useful instructions such that can be executed by a processor after it is ready to synchronize. ... If processors reach the barrier at different times they are less likely to stall at a fuzzy barrier than at a fixed barrier. ... The fuzzy barrier makes the system tolerant of drift in the progress of individual instruction streams.

The code that is to be executed while waiting at a fuzzy barrier is called *barrier* region and is generated by code reordering and other program transformation techniques. Such transformations can make the programs quite large ([ea90]) and even more: a reordering of code may not be adequate for all applications.

In [CS93] an in-depth analysis of how to provide an efficient synchronization by barriers on a shared memory multiprocessor with a shared multi-access bus interconnection (like CSMA/CD) is given. Some applicable algorithms are presented together with their performance-results.

An innovative - if not unorthodox - **alternative to ordinary barriers** (hardware barriers or mapped onto locks) is given in [ea05b]: the waiting of a thread is forced by *continuous invalidation* of the respective I-line *of the instruction-cache*. Additional logic in the second-level instruction cache ensures that such artificial cache-misses are kept from the out-chip bus by ignoring it. As soon as all threads that are needed at this synchronization point have joined the waiting thread the caches resume normal operation. A big advantage here is the fast continuation since the threads resume operation instantly when the next instruction is given by the first-level cache (which got it by the second-level cache on barrier-release).

#### 2.2.3 Transactional Memory (TM)

Hardware-TM (HTM) originated in the quest for programs that are not concerned about explicit locking. The research in the field of HTM shows some very interesting developments in adding hardware-support for transactions - mainly to simplify programming and improve performance. Many concepts are not inevitably tied to TM and may give inspiration for non-TM architectures as well.

The works presented in this section are a selection that seemed most related to the work done in this thesis, an extensive survey (50 sources) of transactional memory (as well as an attempt to categorize its implementations) can be found in [LR07].

The work of Jensen et al. ([ea87]) from 1987 describes how to use architectural support for writing **lock-free program code**, avoiding the performance degradation that is most severe *when locking only single instructions* (benchmarks supporting this statement are given in chapter 5). Support from the coherence protocol and the compiler are needed - the mostly complex details are left out here but can also be found in [LR07].

The paper [SS93] describes an extension of Jensen et al. such that not just a single but a *bounded number of memory locations can be locked by hardware support*. To accomplish this, new instructions operating on new reservation-registers were implemented. With this extension it is possible to access multiple memory locations using lock-free code. A similar approach is made in [HM93]. The goal is the same: to develop lock-free data structures. This time a **transactional cache** was used to monitor and buffer accesses regarding transactions. Still, the size of the transactional cache represented a bottleneck severely limiting the size of the transactions. This paper used and therefore coined the term transactional memory.

Referring to [LR07] the first industrial implementation of transactional memory in hardware is the IBM 801 storage manager system from 1988 [CM88]. Hardware support was added by *additional registers to keep track of ongoing transactions* and, most importantly, *associating a lock to each page of memory* (extension of page table entries and translation look-aside buffers). By collecting the locks of all data involved in a transaction the transaction could be executed, if some of the locks are already occupied hardware exceptions call some routines to resolve the matter (like waiting for the missing locks).

An interesting approach is done in [RG01]: the main idea here is that a processor does not need to get a lock but only needs to monitor it during executing a critical section, thus saving the need to set and release a lock. This is of course a kind of speculation and is called **speculative lock elision (SLE)**. Hardware support for the speculative execution of a critical section is used: the processor executes it as if the lock were not present - the lock elision is done by the hardware. In case of a conflict the hardware resets execution with restoring the original data. After multiple failed speculations or with the critical section being too extensive to be supported in hardware, the processor does not speculate and acquires the lock explicitly. For all this to work a tight dependency between hard- and software is unavoidable (a downside of more complex hardware support).

The concept of transactions is taking over in [ea04b], defining a shared memory model where **all operations execute inside transactions**. In this transactional coherence and consistency model, a transaction is a basic unit of work which leads to a simplification of parallel programming in comparison with conventional synchronization. Transactions are executed speculatively, in case of conflicts only one transaction is allowed to commit system-wide (determined by a global token).

Interesting in [ea06] is that tracking data conflicts does not depend on caches and coherence or consistency protocols (like most other approaches for HTM). Instead, **address-information is sent when a transaction is ready to commit**, revealing address-conflicts. The implementation is called *Bulk*. Address-conflicts can be detected word-precise, the compressing of transaction-addresses into so-called *signatures* is done by the hardware. Such signatures represent a compressed superset of all the read- and write-addresses comprising a transaction (this can lead to *false conflicts* due to the compression).

Summing up this section, some main ideas influenced by HTM came up during this thesis as well. Still, there is a main difference to be aware of: transactions may not commit even if executed. In this thesis such an approach to redo a block of executions is out of the question, as *roll-backs* are in general considered of limited utility regarding safety-critical systems where time is not to be wasted and actions already done may be irrevocable (s. also [Kop97], chapter 1).

#### 2.2.4 A Glance at Scalable Multiprocessors

Most of the more recent designs extending shared memory systems into large-scale multiprocessor systems use **distributed memory schemes**, leaving the classical shared memory architecture due to the difficulty implementing a shared memory for many processors. What is left is the *notion of a shared memory by* keeping a *shared address space*. Sharing a physical address space among processors of a large-scale multiprocessor system enables the usage of *simple load/store-instructions* to invoke network-operations. Without a shared physical address space it is necessary to use dedicated *message passing facilities* to communicate. The nCUBE/2 is an example for only private memories, the CRAY T3D on the other hand has a shared physical address space. Both systems are described in some more detail in the following.

The nCUBE/2 is a rather old but still presentable representative for a multiprocessor system. The area of the 2,048 VAX-based processor nodes (hypercube configuration, build in 1991) that would have normally be used for the cache was occupied by diverse communication logic. Only a small code and an even smaller first-level data cache was available to each processor (128 to 64 bytes [CS99]). 14 channels are used as *unidirectional links* between the processors and can be used for synchronization. Each processor connects directly with *local SD-RAM*. This system has a shared address space, but no physically shared memory.

Yet another example, the **CRAY T3D** is a parallel system containing of 2,048 DEC Alpha 21065 microprocessors with up to 64 MB *private memory* each. Interestingly the second level cache of all processors (512kByte each) is deactivated to reduce the main memory's access time (cache-misses cost an additional clock cycle). The T3D has a special global AND- and global OR-network to support synchronization (primarily for barriers). A broad perspective can be gained in [CS99], 7.6. A compiler-perspective on how to work with the CRAY using the parallel extension of ANSI-C, Split-C is given in [ea95].

The highly parallel system **KSR1** from Kendell square research described in [ea93] has large local caches for each processor and achieves synchronization by hardwaresupport of the memory subsystem. This architectural technique is called *ALL*-*CACHE*. A shared physical address space mapped on devices is present, *locking is accomplished by putting memory pages into an atomic state*. A page in the atomic state is the only valid page throughout all local memories, the memory subsystem ensures invalidation of all other pages. A processor that successfully locks a memory page (make it atomic) automatically gets the page moved into its local memory where it can be used directly.

The **major bottleneck** for highly-parallel systems is the connection of the processors to the memory. In [SZ02] the insufficient performance of parallel systems built from commercial off-the-shelf components for programs with low locality is unveiled. So instead of using already available commercial modules as parts for a parallel system, further integration presents the possibility to *locate memory together with the executing cores on one chip*. This field of research focused on overcoming the interconnection bottleneck is known also as the area of **processorin-Memory architectures (PIM)** and gives quite some insight into the new perceptions in this field. Like the results of this thesis the work of [SZ02] helps in gaining additional insight into how to judge a given multiprocessor architecture in respect to different types of parallel applications it is intended to host. The **IBM BlueGene/L** team goes another way to weaken the bottleneck of the processor-memory interconnection, as well as other disadvantages in traditional massively parallel SMPs. [Tea02]:

To scale the next level of parallelism, in which tens of thousands of processors are utilized, the traditional approach of clustering large, fast SMPs will be increasingly limited by power consumption and footprint constraints. ... In addition, due to the growing gap between the processor cycle times and memory access times, the fastest available processors will typically deliver a continuously decreasing fraction of their peak performance ... The approach taken in BlueGene/L (BG/L) is substantially different. ... The design point of BG/L utilizes IBM PowerPC embedded CMOS processors, embedded DRAM, and systemon-a-chip techniques that allow for integration of all system functions ... Because of a relatively modest processor cycle time, the memory is close, in terms of cycles, to the processor.

The BlueGene/L interconnects its highly-integrated nodes (having a large local memory) by a 3-dimensional torus network for point-to-point communication. One additional network is a global barrier- and interrupt network for event synchronization.

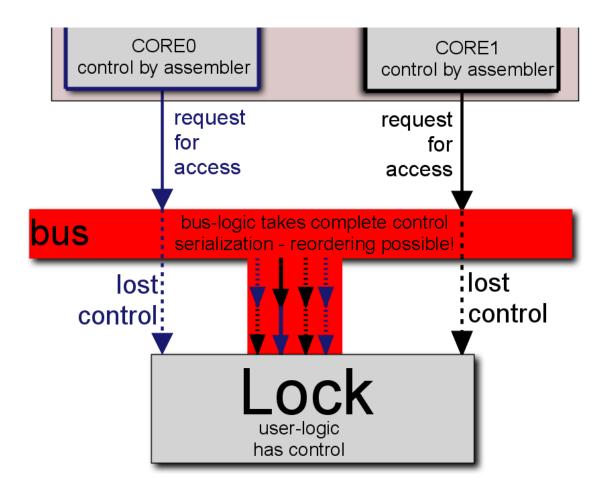

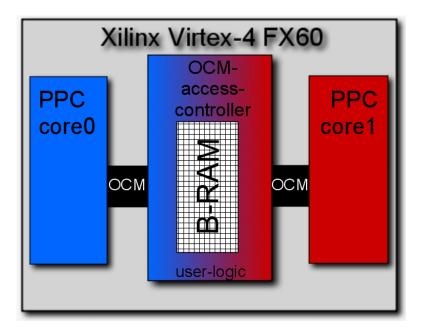

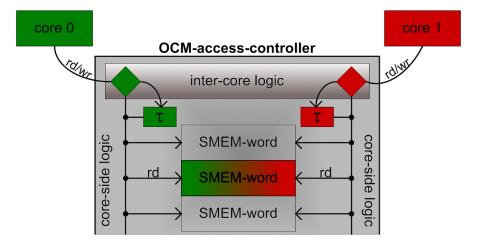

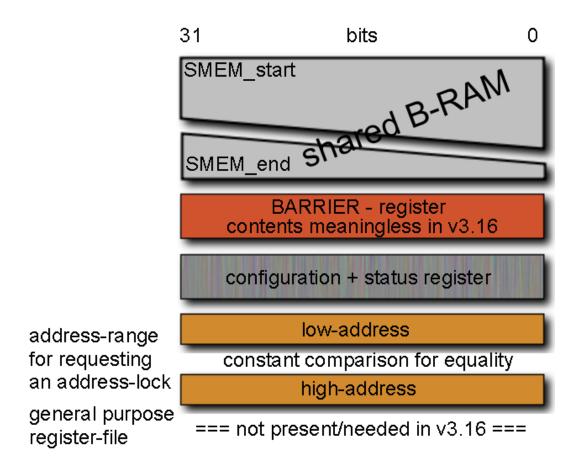

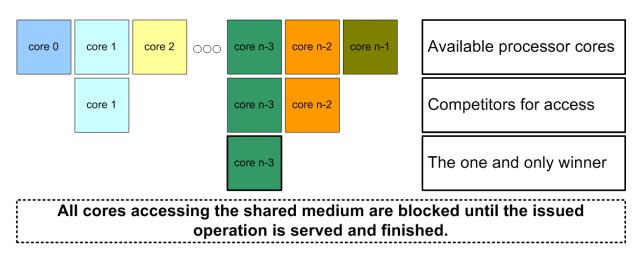

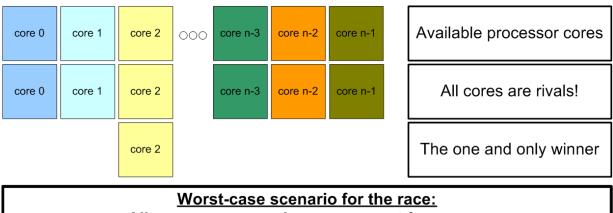

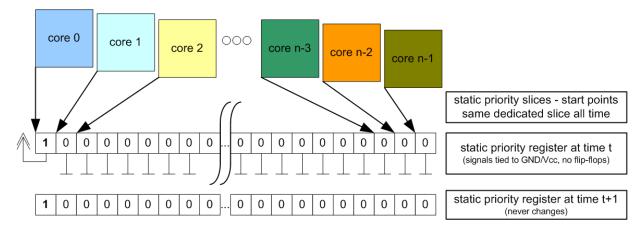

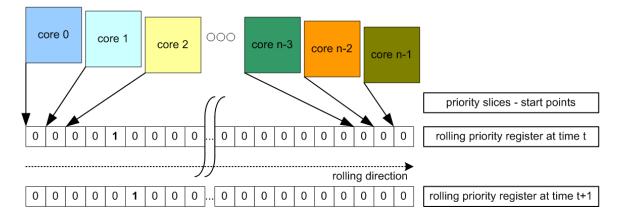

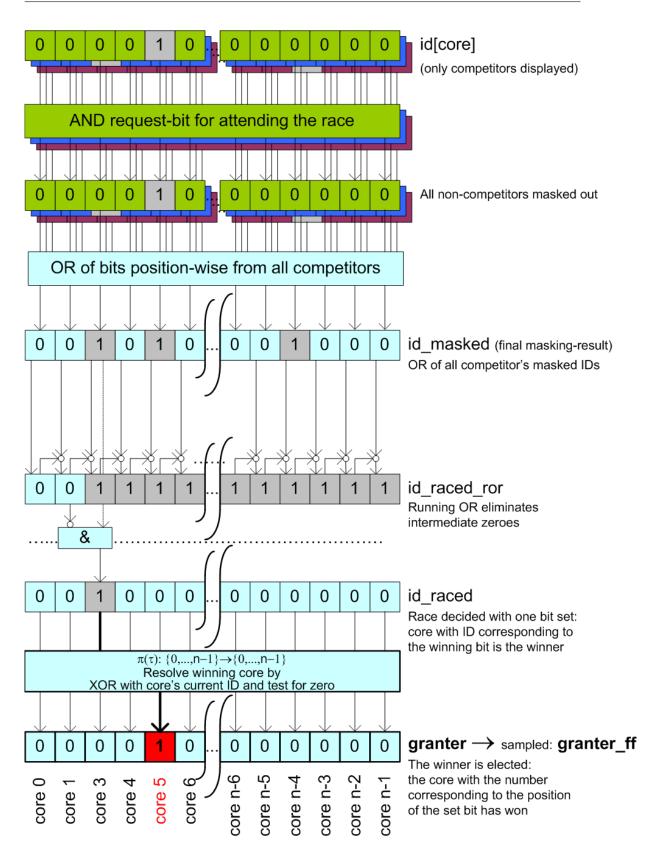

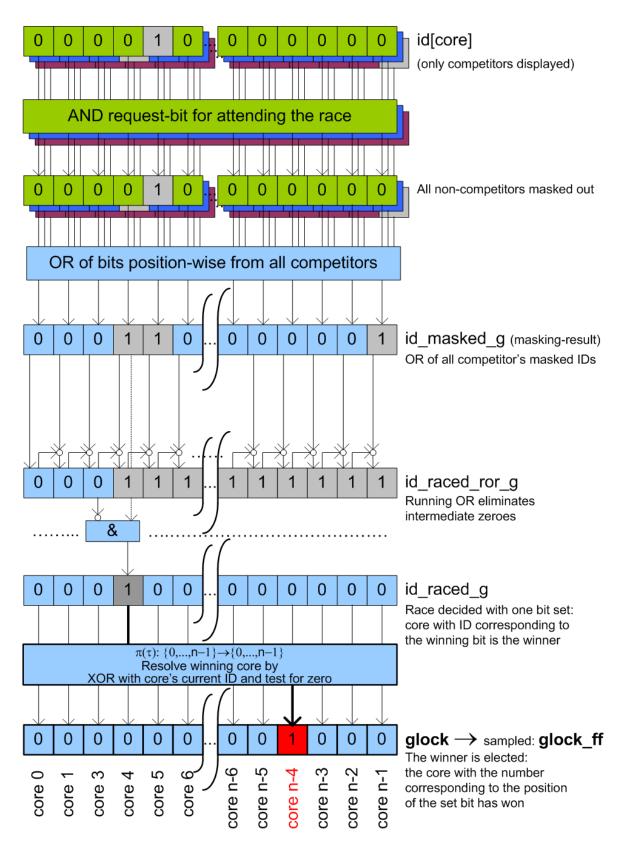

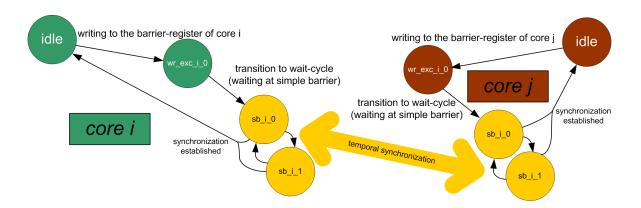

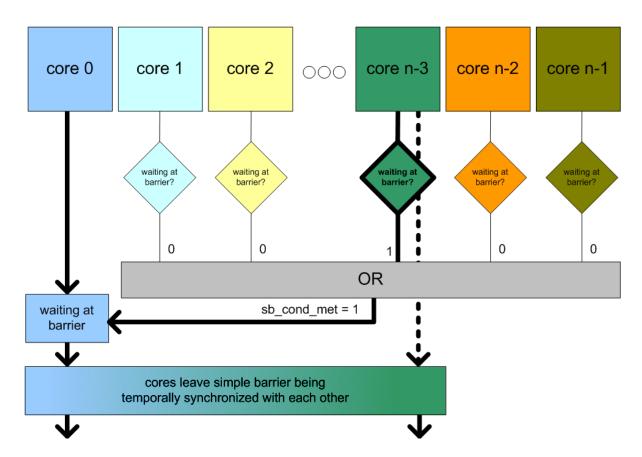

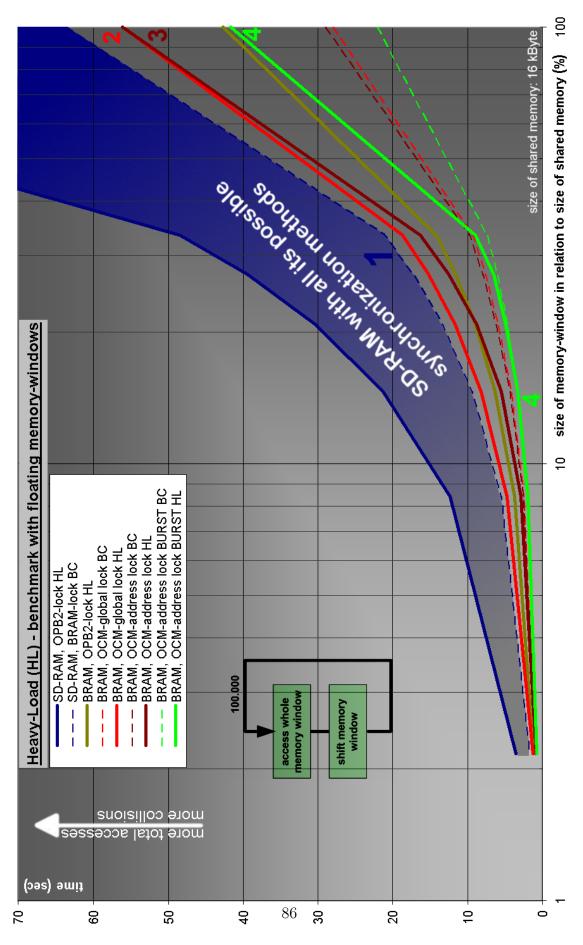

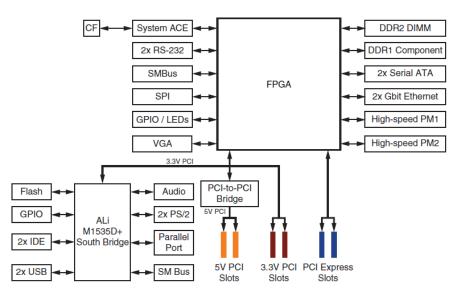

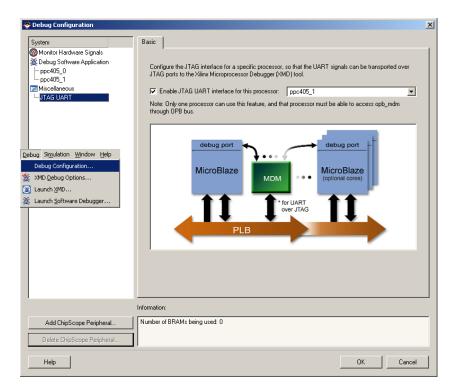

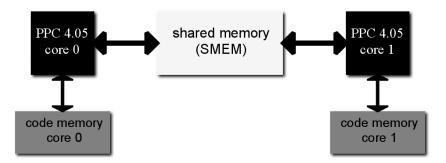

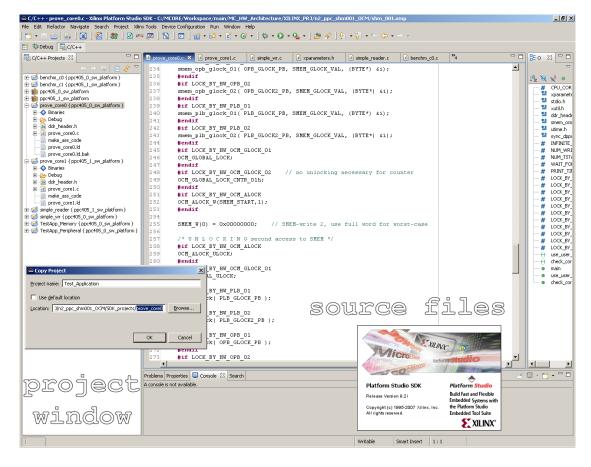

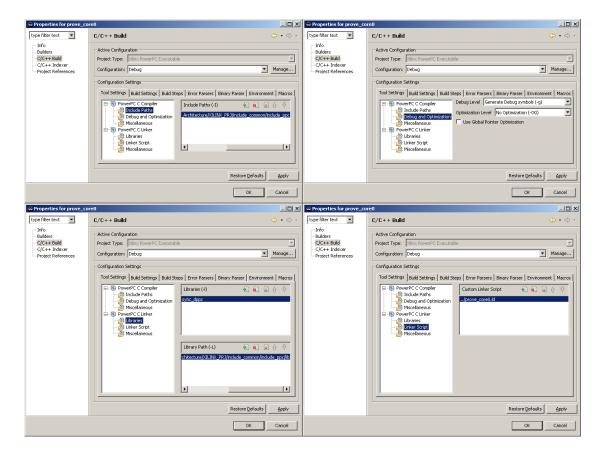

Since we are not concerned about large-scale multiprocessor systems we conclude this section here, but not without emphasizing that the hardware support and high-scale integration of such systems might be relatively advantageous for smalland medium-scale parallel systems as well.