Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

DIPLOMARBEIT

### Design and Implementation of a Bus-Switching Unit for a High-Speed Peripheral Card

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Diplom-Ingenieurs unter der Leitung von

O. UNIV. PROF. DIPL.-ING. DR. TECHN. DIETMAR DIETRICH und UNIV. ASS. DIPL.-ING. DR. TECHN. THILO SAUTER und DIPL.-ING. PATRICK LOSCHMIDT als verantwortlich mitwirkenden Assistenten

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik Institut für Computertechnik, Inst.-Nr. E384

von

FELIX RING Matr. Nr. 9925202 Bachackergasse 35, 2380 Perchtoldsdorf

Perchtoldsdorf, 7. Mai 2009

#### Kurzfassung

Diese Diplomarbeit befasst sich mit der Weiterentwicklung einer Ethernet Netzwerkkarte für hochgenaue Uhrensynchronisation. Um die Genauigkeit der Uhrensynchronisation bis zu Standardabweichungen im Subnanosekundenbereich verbessern zu können, soll die Eignung von neuen Übertragungsmedien für Uhrensynchronisation untersucht werden. Die vorliegende Arbeit beschreibt die Entwicklung einer dafür notwendigen Netzwerkkarte, die die Durchführung von Uhrensynchronisation sowohl in optischen als auch in kabelbasierten Gigabit Ethernet Netzwerken ermöglicht. Als Grundlage dafür wird eine bereits verfügbare Hardwarearchitektur für hochgenaue Uhrensynchronisation verwendet, die auf einer Evaluierungsplattform für optisches und kabelbasiertes Gigabit Ethernet implementiert werden soll. Da nur Evaluierungsplattformen mit PCI Express Anbindung erhältlich sind, muss die bisherige PCI basierte Hardwarearchitektur in eine PCI Express basierte Hardwarearchitektur übergeführt werden. Dieser Umbau erfordert die Entwicklung einer Einheit, die unterschiedliche Bussysteme miteinander verbinden und deren Pakete auf die verschiedenen teilnehmenden Knoten entsprechend verteilen kann. Es handelt sich dabei um mehrere AHB Knoten, die mit dem PCI Express Bus verbunden werden müssen. Das vorliegende Dokument behandelt ausführlich die Anforderungen für eine solche Einheit und die dabei auftretenden Hürden, die es zu meistern gilt. Im Zuge dessen werden gut erforschte Techniken für vergleichbare Fragestellungen aus unterschiedlichen Anwendungsgebieten beleuchtet. Die dort gewonnenen Erfahrungen werden auf den vorliegenden Fall angewendet, und darauf basierend werden verschiedene Lösungansätze dargestellt. Desweiteren werden während der Entwicklungsarbeiten aufgetretene Schwierigkeiten beschrieben und analysiert, um daraus Hilfestellungen für zukünftige Projekte abzuleiten. Die aus den gewonnenen Erfahrungen erwachsenen Vorschläge für strukturiertes Vorgehen sollen helfen, mögliche Entwicklungsfehler zu vermeiden. Schließlich wird beschrieben, wie zwei auf grundsätzlich unterschiedlichen Ansätzen basierende Simulationsumgebungen verwendet werden, um durch die Durchführung automatischer und halbautomatischer Tests die entwickelte Einheit zu verfizieren. Als Ergebnis dieser Arbeit können durch den Einsatz mehrerer Einheiten der entwickelten Hardware Testnetzwerke aufgebaut werden, die ein tieferes Verständnis von hochgenauer Uhrensynchronisation in Gigabit Ethernet Netzwerken ermöglichen.

#### Abstract

This diploma thesis is about the evolvement of a high-precision clock synchronization enabled Ethernet Network Interface Card (NIC). To further improve the precision of the clock synchronization system to sub-nanosecond standard deviation, investigations on the suitability of new media for clock synchronization have to be made. The present work describes the necessary development of an evaluation network interface card for clock synchronization over copper- and optical fibre based Gigabit Ethernet. Therefore, an existing hardware design for high-precision clock synchronization has to be implemented on an evaluation board supplying Gigabit Ethernet physical layer connectors. As such evaluation boards are only available with PCI Express connectors, the existing Peripheral Component Interconnect (PCI) based system has to be transferred to a PCI Express based system. The transformation requires the development of a bus-switching and translation unit to interconnect multiple instances of Advanced High-Performance Bus (AHB) interfaces to the PCI Express connection interface. This document provides a thorough explanation of the requirements and challenges of such a unit, investigating theoretical approaches and utilising knowledge of similar problems in different, well understood application fields. Moreover, traps and pitfalls that came up during the design and implementation process are presented and analysed to derive hints and suggestions for future projects, in order to use the gained experience to optimise the design methodology and avoid mistakes. The design is verified by using two developed, fundamentally distinct simulation environments and applying a variety of test cases for automated and semi-automated verification. The resulting system is a powerful means to gain deeper knowledge of high-precision clock synchronization in Gigabit Ethernet based networks by setting up and measuring test networks using multiple instances of the developed hardware.

#### Acknowledgements

A lot of people contributed to this diploma thesis by encouraging words, helping hands and good ideas here and there, and even more people contributed to the long way it took me to get to this point of my studies. It is not possible to mention all but a small number I am grateful for. Still, honour, to whom honour is due. Most of all I am grateful that God, whom I may call my father, brought me this far. After him, I sincerely have to thank my parents for providing everything I needed to finish my studies. I also want to thank all my dear friends who supported and encouraged me during this long time, before all others my long-time study companion Lukas Riegler for almost adopting me in his family during the many hours spent studying together.

I am also very grateful for all of my colleagues at work, who also supported me during the development of this diploma thesis, and who helped me out with ideas and advice in one or the other fruitful discussion and conversation. For my supervisor Patrick Loschmidt, I would need an extra page to thank him for all he has done for me, not only during the writing of this thesis, but also for providing a superb working environment together with Georg Gaderer and Thilo Sauter, and for holding my back free to be able to concentrate on writing my thesis. I also want to specially thank my supervisors for correcting and evaluating the thesis on such short notice, even late at night. Further thanks go to my grandmother, Josefine Thurner, and my friends, Ilse und Andreas Schmaranzer, for letting me retreat to their houses for quiet and concentrated writing, and to my aunt Judith Thurner for lending me her car to get there. Finally, my special thanks for editing, go to my dear friend, J. Steven Ramey, my brother, Stefan Ring, and to the most wonderful person I have ever met, Leslie Kidd, who I want to thank for more than I can ever express.

# Contents

| 1        | ion                      | 1                   |                                       |                 |  |  |  |

|----------|--------------------------|---------------------|---------------------------------------|-----------------|--|--|--|

|          | 1.1                      | ation               | 2                                     |                 |  |  |  |

|          | 1.2                      | Task                |                                       | 6               |  |  |  |

|          | 1.3                      | Relate              | ed Work                               | 7               |  |  |  |

|          | 1.4                      | Docun               | nent Structure                        | 10              |  |  |  |

| <b>2</b> | Tec                      | Technology Overview |                                       |                 |  |  |  |

|          | 2.1                      |                     |                                       |                 |  |  |  |

|          |                          | 2.1.1               | Ethernet                              | 13              |  |  |  |

|          |                          | 2.1.2               | Advanced High-Performance Bus         | 17              |  |  |  |

|          |                          | 2.1.3               | PCI Express                           | 21              |  |  |  |

|          |                          | 2.1.4               | Altera PCI Express Interface          | 25              |  |  |  |

|          |                          | 2.1.5               | Precision Time Protocol               | 27              |  |  |  |

|          | 2.2                      | Typica              | al Application                        | 29              |  |  |  |

| 3        | s and Possible Solutions | 31                  |                                       |                 |  |  |  |

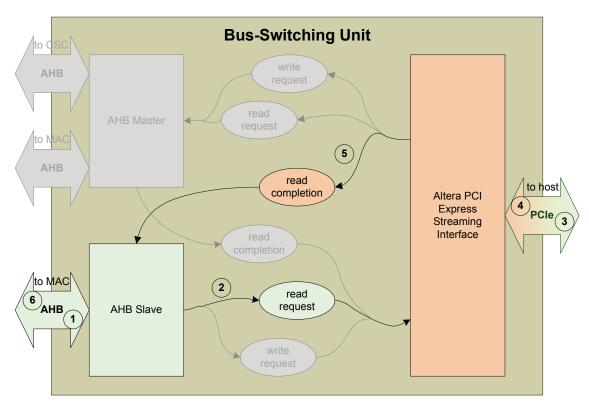

|          | 3.1                      | -                   | ple of Operation                      | 32              |  |  |  |

|          | -                        | 3.1.1               | Register Operations                   | 32              |  |  |  |

|          |                          | 3.1.2               | Burst Direct Memory Access Operation  | 34              |  |  |  |

|          | 3.2                      | Challenges          |                                       |                 |  |  |  |

|          |                          | 3.2.1               | Protocol Translation                  | 39              |  |  |  |

|          |                          | 3.2.2               | Packet-Switching                      | 40              |  |  |  |

|          |                          | 3.2.3               | Bus Arbitration                       | 42              |  |  |  |

|          |                          | 3.2.4               | Rate-Matching                         | 42              |  |  |  |

|          |                          | 3.2.5               | Prevention of Data Loss               | 43              |  |  |  |

|          | 3.3                      | Possib              | le Bus-Switching Architectures        | 43              |  |  |  |

|          |                          | 3.3.1               | System on a Programmable Chip Builder | 43              |  |  |  |

|          |                          | 3.3.2               | Bus Arbitration Considerations        | 44              |  |  |  |

| 4        | Dev                      | elopm               | ent System                            | 46              |  |  |  |

| -        | 4.1                      |                     |                                       |                 |  |  |  |

|          | 4.2                      |                     |                                       |                 |  |  |  |

|          | 4.3                      |                     | e Driver Operation                    | $\frac{48}{50}$ |  |  |  |

|          |                          | 1                   |                                       |                 |  |  |  |

| <b>5</b> | Design and Implementation   |                     |                                                 |    |  |  |  |

|----------|-----------------------------|---------------------|-------------------------------------------------|----|--|--|--|

|          | 5.1                         | Desigr              | 1 Work Flow                                     | 53 |  |  |  |

|          | 5.2                         | Hardware Transition |                                                 |    |  |  |  |

|          |                             | 5.2.1               | FPGA Device Specific Alterations                | 55 |  |  |  |

|          |                             | 5.2.2               | Board Specific Alterations                      | 56 |  |  |  |

|          |                             | 5.2.3               | Configuration of the PCI Express Endpoint       | 59 |  |  |  |

|          |                             | 5.2.4               | Reset Circuit for the PCI Express Endpoint      | 59 |  |  |  |

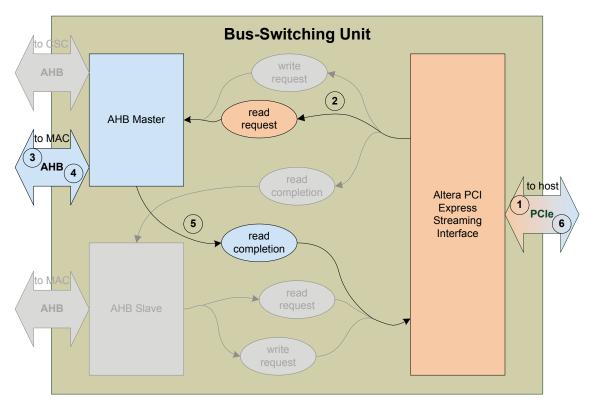

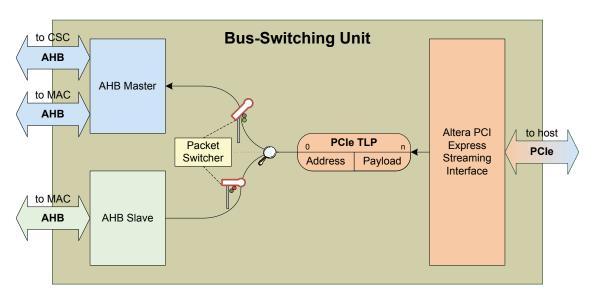

|          | 5.3                         | Archit              | ectural Structure of the Bus-Switching Unit     | 60 |  |  |  |

|          |                             | 5.3.1               | Receive FIFO Memory                             | 62 |  |  |  |

|          |                             | 5.3.2               | Transmit FIFO Memory                            | 64 |  |  |  |

|          |                             | 5.3.3               | Header Decoder                                  | 65 |  |  |  |

|          |                             | 5.3.4               | Address Decoder                                 | 68 |  |  |  |

|          |                             | 5.3.5               | AHB Master – Register Operations                | 70 |  |  |  |

|          |                             | 5.3.6               | AHB Slave – Direct Memory Access Burst Transfer | 73 |  |  |  |

|          | 5.4                         | Pitfall             | s During Development                            | 76 |  |  |  |

|          |                             | 5.4.1               | Evaluation Board Errors                         | 76 |  |  |  |

|          |                             | 5.4.2               | Hardware Design Errors                          | 77 |  |  |  |

| 6        | Simulation and Verification |                     |                                                 |    |  |  |  |

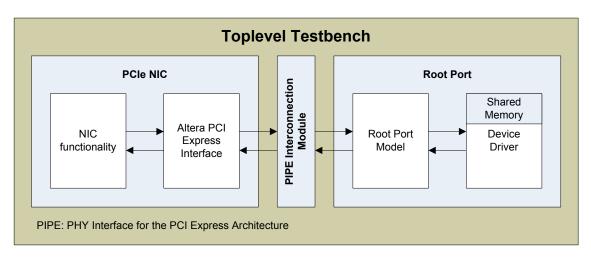

|          | 6.1                         | Accura              | ate Altera PCI Express Simulation               | 81 |  |  |  |

|          | 6.2                         |                     | PCI Express Emulation                           | 83 |  |  |  |

|          | 6.3                         |                     | ation                                           | 86 |  |  |  |

|          |                             | 6.3.1               | Verification by Simulation                      | 86 |  |  |  |

|          |                             | 6.3.2               | Hardware Testing                                | 94 |  |  |  |

| 7        | Conclusion                  |                     |                                                 |    |  |  |  |

|          | 7.1                         | Lessons Learned     |                                                 |    |  |  |  |

|          | 7.2                         | Outlook             |                                                 |    |  |  |  |

### Chapter 1

# Introduction

Moore's law [1] has accurately predicted the development of the complexity of integrated electronic systems for approximately the last forty years [2]. Moore's prediction was the doubling of the complexity of Integrated Circuits (ICs) every two years, which proved to be a very good estimation of the past development. This rapid increase in complexity allows the integration of more and more functional components up to complete systems on a single chip. Not only because of the increase in complexity, but also because of more efficient and faster transistor and circuit designs computational power increases even faster than the mere number of transistors on a chip. In order to use the available high computational power, most applications demand high performance data connections to provide and receive the data that is to be processed.

Despite the possibility to integrate a high number of functions on a single chip, there will always be a need for additional peripheral components which have to be connected to the main unit. The advantages of peripheral components are rooted in the advantages of modularity, which are mainly flexibility, changeability, and reusability. To allow several modules to interact with each other and with the main unit, a communication system is required. In order to satisfy the needs for constantly increasing data rates, the interconnection systems for peripheral components have to be continuously adapted and improved. Therefore, scalability is a very important requirement to keep the need for architectural changes of the interconnection systems at a minimum. In recent years a transition from Peripheral Component Interconnect (PCI) systems to the faster and highly scalable PCI Express (PCIe) systems has taken place in the area of consumer PCs.

The steady development of more complex ICs with higher processing power and higher interconnection data rates continuously straightens the path to new application fields. The improvement and evolvement of industrial electronics, especially together with the trend to distributed computing and control, leads, amongst others, to the requirement for high-precision clock synchronization. In networking systems a strong trend towards packet-switched networks can be observed. Therefore, during the last years many efforts were taken to provide high-precision clock synchronization over packet-switched networks,

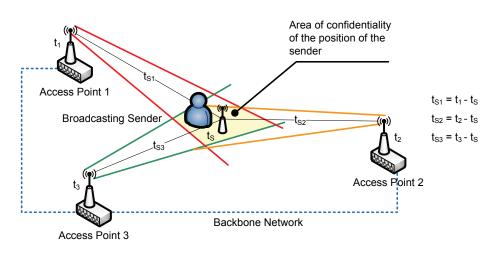

Figure 1.1: Basic localisation concept

e.g. over Ethernet. A dedicated working group was created at IEEE to define a standard for clock synchronization, the IEEE 1588 standard [3].

#### 1.1 Motivation

All of the above considerations together with the desire for wireless communications are driving key factors for the FIT-IT project Embedded Position Determination and Security in Wireless Fidelity networks ( $\varepsilon$ -WiFi). The aim of the project is to offer position information to services in Wireless LANs (WLANs) without the need to modify the node to be located.

To show the basic idea of localisation in wireless networks, figure 1.1 depicts a standard approach to localisation by measuring the signal propagation delays from a mobile client node to geographically distributed, positionally defined access points. With these measured propagation delays and the knowledge that WLAN packets travel at the speed of light the distance of the mobile node to each Access Point (AP) can be calculated. With the known distances, in the two-dimensional case the mobile node can be localised via triangulation.

#### **Position Detection**

In  $\underline{\varepsilon}$ -WiFi a more sophisticated approach for localisation has to be used, but the basic idea stays the same. The  $\underline{\varepsilon}$ -WiFi project aims at localising any standard mobile node with a WLAN interface. No specific hardware, software or drivers are installed on the mobile nodes. Therefore, the transmission time of the packet originating at the mobile node cannot be known, since no clock synchronization can be implemented with appropriate accuracy. And even if the clock was accurate, without a dedicated software the node does

not include the transmission times in its transmitted packets. To still be able to perform localisation the Time Difference of Arrival (TDoA) of the WLAN packets has to be used. The mathematical background for a technique using TDoA for localisation is described in [4].

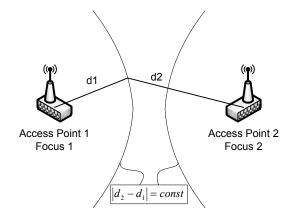

The concept is based on the idea that all wireless signals are inherently broadcast transmissions. Therefore, all access points receive the same signal at a different instant of time, depending on the distance of the mobile node to the respective access point. As the access points can communicate with each other, the time difference, and only the time difference of the arrival of a packet at two distinct access points is known. With two access points this calculated difference corresponds to the difference of the distance of the node to the first access point (d1) and the distance of the node to the second access point (d2). This known difference (d2 - d1) is the only position determining information available. Mathematically, in two-dimensional space, a function with a constant difference of the distance of a variable point to two distinct focal points is a hyperbola, as depicted in figure 1.2. In the three-dimensional space from the time difference of arrival of the packet at the two different nodes a hyperboloid with the access points being the focal points can be drawn. The mobile node can be anywhere on the hyperboloid, as the difference of the distance of all points on a hyperboloid to the focal points is constant. When a third access point is added, the node can be determined to be on the intersecting ellipses of the hyperboloids. A fourth access point is needed to limit the node's location to two points, and five access points are needed to get a unique point (as long as the access points are not all on the same plane).

Figure 1.2: Hyperbola defined by two access points

To get accurate localisation results, the measured differences of time have to be very precise. In order to achieve such high precision, the clocks of the access points have to be well synchronized. The clock synchronization of the access points is performed over the wire-based backbone network. Therefore, the project consortium of the  $\underline{\varepsilon}$ -WiFi project aims at further improving the precision of this wire-based synchronization. As previous projects led to a deep understanding and remarkable results in the field of clock synchro-

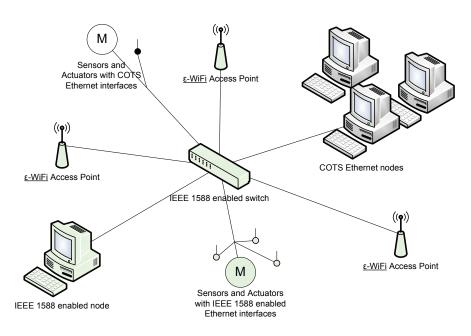

Figure 1.3: Example network for clock synchronization

nization over Fast Ethernet (100 MBit/s), new transmission media and technologies are investigated for their suitability as base-networks for high-precision clock synchronization.

#### **High-Precision Clock Synchronization**

Figure 1.3 shows several Ethernet nodes which are interconnected in an example network. The nodes in light green are equipped with Ethernet Network Interface Cards (NICs) that are specifically designed for high-precision clock synchronization, while the other nodes have Commercial Off-The-Shelf (COTS) Ethernet network interfaces. The interconnecting Ethernet network is a standard network with no limitations. The clock synchronization enabled NICs are capable of participating in normal Ethernet activities, and additionally use standard Ethernet frames for communicating their specific messages needed for clock synchronization. Those messages are part of the Precision Time Protocol (PTP), which is a protocol for high-precision clock synchronization defined in the IEEE 1588 standard. Therefore, the specific nodes in the figure are also labeled "IEEE 1588 enabled". The PTP uses Ethernet as a base-network to transmit specific messages for clock synchronization. It is described in more detail in section 2.1.5. Undisturbed Ethernet traffic and high-precision clock synchronization can co-exist even in an existing COTS Ethernet network.

For Ethernet-based clock synchronization, a crucial factor is the accurate delay measurement of packets as they travel from the source node to the destination node. The high-precision clock synchronization enabled network nodes perform such measurements at the Media Independent Interface (MII) level (the connection between the Ethernet Physical Layer (PHY) and the Ethernet Media Access Control (MAC) unit during normal operation). Any jitter of these measurements, as well as any asymmetric, direction

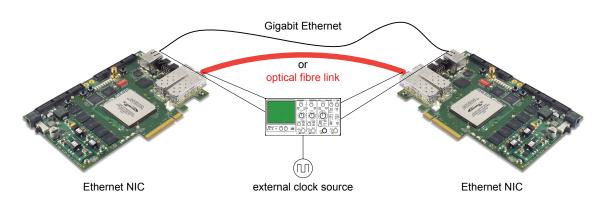

Figure 1.4: Example setup for delay measurements

dependent delay difference deteriorates the precision of the clock synchronization system. To get an impression of the precision which can be expected, the jitter and asymmetric delay properties of Gigabit Ethernet over copper and optical fibre links have to be investigated.

#### **Required Measurements**

Figure 1.4 shows an example setup for direct-link measurements concerning the mentioned delay and jitter properties. The used Ethernet NICs are not required to support clock synchronization, any network card with physically accessible MII signals can be used. However, it is advisable to measure the properties of the Ethernet PHYs which will be used later for clock synchronization, as different PHYs have different jitter properties.

To minimise the number of influencing factors, such as added jitter by switches or high traffic load, first measurements have to be done on a direct-link basis. With direct-link measurements it is possible to focus on the influence of the clock recovery circuitry and the clock transitions of the PHYs, which are the main sources for delay jitter. Asymmetric line delays also deteriorate the achievable precision of clock synchronization and can be observed by the direct-link measurements as well. As Gigabit Ethernet over copper uses all available four twisted-pair lines for both directions of data transmission, in contrast to Fast Ethernet which uses two dedicated pairs for each direction, a reduction of the asymmetry is expected for Gigabit Ethernet. The measurements are needed to verify or falsify this expectation.

The small depicted oscilloscope in the figure symbolises the measurement equipment. In contrast to Ethernet-based clock synchronization, the measurement equipment can sample the transmission time and reception time based on an external reference clock. Therefore, jitter of the one-way delay, as well as an asymmetry of the delay in one direction compared to the delay in the other direction can be measured. To get meaningful results, care has to be taken to use absolutely identical measurement cables to not distort the measurement by unequal signal propagation delays from the nodes to the measurement equipment.

The just mentioned measurements are required to estimate the theoretically achievable precision of a clock synchronization system using the measured components. However, measurements of an operational test network performing clock synchronization over Gigabit Ethernet have to be made to get real numbers of the standard deviation of the clocks of different nodes. Additionally, the nodes can be used to evaluate clock synchronization for systems with long distances between the individual nodes, e.g. measurement stations at the particle accelerator at CERN. Therefore, it is important to provide network nodes that are capable of participating in clock synchronization over Gigabit Ethernet copper and optical fibre networks, which leads to the task requirement of this diploma thesis.

#### 1.2 Task

The task of this diploma thesis is to develop an evaluation system that enables clock synchronization related tests and measurements with Gigabit Ethernet over copper and optical links. The work of this thesis is to be understood as part of the  $\varepsilon$ -WiFi project<sup>1</sup> by providing the necessary hardware to perform the tests and investigations.

To be able to perform tests and measurements with the new media an appropriate test platform has to be created. In order to keep the development effort for such a test platform as low as possible, commercially available evaluation boards shall provide the base framework. An FPGA based evaluation platform shall be chosen to allow tests with the following transmission standards [5]:

- 10BASE-T (two pairs of twisted-pair copper, data rate is 10 MBit/s)

- 100BASE-TX (two pairs of twisted-pair copper, data rate is 100 MBit/s)

- 1000BASE-T (four pairs of twisted-pair copper, data rate is 1000 MBit/s)

- 1000BASE-LX (point-to-point link over one single-mode optical fibre, data rate is 1000 MBit/s)

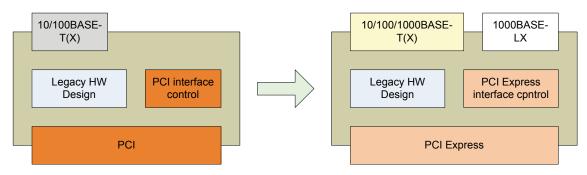

Evaluation boards providing connectors for these standards are only available with a PCI Express connection for host PC communication. To be able to use the existing hardware design for the clock synchronization enabled Ethernet NIC, which is the outcome of previous projects, the modules responsible for host communication have to be re-developed. Figure 1.5 sketches out the basic function blocks and supported communication standards of the existing NIC. It also shows the desired new NIC system with the unchanged legacy hardware core, the additional interfaces and the required change from a PCI to a PCI Express based system.

<sup>&</sup>lt;sup>1</sup>The work presented in this thesis is partly funded by the FIT-IT Project  $\underline{\varepsilon}$ -WiFi -Embedded Position Determination and Security in Wireless Fidelity Networks, grant number 813310

Figure 1.5: Evolution of hardware

The legacy hardware core is maintained by a third party and must not be altered, even though the source code is available. The interface on the legacy hardware side which has to be connected to the PCI Express system is an Advanced Microcontroller Bus Architecture Advanced High-Performance Bus (AMBA<sup>TM</sup>AHB) [6] system. The bus system consists of two AHB slave interfaces and one master interface. The interfaces do not have to be connected to each other, only communication with the device driver in the host PC is required. For this communication transfers with a data width of 32-bit—a Double Word (DW)—have to be supported. The existing device driver requires the hardware to support the reception and handling of single DW read and write requests, as well as the independent generation of burst read and write requests for Direct Memory Access (DMA) with a configurable length in multiples of a DWs. Furthermore, the interface has to be able to generate an interrupt signal for hardware-to-software communication triggering.

A simulation environment shall be provided to be able to simulate the data-flow and operation of the whole NIC architecture. The simulation environment is intended to be a means of basic verification in the development phase. For the intended usage of the evaluation board in an IEEE 1588 clock synchronization test network, it is not required to optimize the design for high performance and high throughput.

#### 1.3 Related Work

The given task addresses a couple of known problems which are treated in scientific literature and papers. Addressed topics are e.g. packet-based clock synchronization in Gigabit Ethernet over copper and optical fibre networks, PCI Express to AHB interfacing, on-chip packet switching and buffering techniques for packet-switching. This section gives an overview of approaches found in literature regarding the mentioned topics and shows where experiences and results from different application fields can be used.

#### **Clock Synchronization**

Concerning the main system topic, the high-precision clock synchronization for packet switched systems, a large number of publications is available. On the hardware side for example in [7] an Ethernet NIC together with a dedicated switch for clock synchronization is presented. A novel concept for enhancements to the IEEE 1588 version 2 standard [3] master/slave based clock synchronization for fault tolerance is extensively discussed in [8]. The main influences on jitter in timestamping and resulting theoretical limits for high-precision clock synchronization accuracy over packet-based networks are discussed in [9]. The  $\varepsilon$ -WiFi project embodies the knowledge and considerations of the mentioned work. Additionally, to be able to calculate the theoretical limits presented in [9] the delay jitter of the physical layer has to be known. In [10] delay measurements and delay jitter measurements for 10BASE-T and 100BASE-TX PHY devices and cables are presented. Precise delay jitter measurements for 1000BASE-T and 1000BASE-LX physical layers currently are not available and have to be made to be able to adjust the clock synchronization algorithm, as described in [9], to get as close as possible to the theoretical accuracy limit.

#### **PCI** Express

The diploma thesis of Nassar [11] deals with the generally connection of some registers to a host PC using the PCI Express connection technology. Though this diploma thesis deals as well with the connection of hardware using the PCI Express interface, the work of Nassar has a completely different objective. It describes the PCI Express architecture in more detail with an emphasis on helping users with their first experiences with PCI Express. An example design is also included, demonstrating read and write operations of single DWs. In contrast, this diploma thesis focuses on the design and the theoretical principles of a more complex communication model in the context of an existing hardware environment. While in the work of Nassar the registers can be directly connected to the PCI Express protocol core, in this diploma thesis the PCI Express packets have to be switched and translated to AHB nodes. Further, this diploma thesis has a focus on the practical design and implementation work with all the occurred traps and pitfalls.

#### **Packet-Switching**

The problem of packet-switching is inherent to all direct-link, packet based communication systems with more than two participants. Therefore, it is a very well understood topic with a vast number of available optimisation proposals for different cases of application. For example, [12] proposes a general packet switching methodology for intra-chip architectures. Although this and similar approaches have proved to be useful for systems with a large number of inputs and outputs at very high data-rates, it is not reasonable for this diploma thesis, as the general problem here appears in a very simplified environment with only one input and two output ports. Still, the basic requirements stay the same. The incoming packets arrive on one port, they carry some kind of address information and they have to be forwarded to an outgoing port according to the address information. Therefore, similar techniques as in the well known field of Ethernet switching can be used. Hein [13] presents fundamental considerations concerning the switching fabric and the switching technique. Two fundamentally different approaches for the switching fabric are discussed, Space Division Switching (SDS) and Time-Division Switching (TDS). SDS uses geometrical structures to interconnect all input ports to all output ports. Those geometrical structures need space, hence the name. A crossbar switch, which connects m inputs to n outputs with a  $m \times n$  matrix of crossing points is a well known example for space division switching. In contrast to SDS, with TDS not all inputs have a direct connection to an output. The switching rather is realised by using a shared resource. Circuit switched networks where a fixed slot time corresponds to a specific route from a specified input port to a specified output port employ TDS as well as packet-based switches with shared memory. With these switches the switching algorithm has to take care that each input can write to the shared memory when a packet arrives on a port, and to prevent that two inputs get simultaneous access to the same memory, as the data would be destroyed. Depending on the destination, the respective output port gets read access to the shared memory and thus can forward the packet to its intended destination.

For Ethernet switches Hein [13] also distinguishes between cut-through and store-andforward switching. Cut-through switching takes advantage of the fact that the destination address of Ethernet packets is at the very beginning of a frame. Therefore, a switching decision can already be made as soon as the destination address has been read and thus the introduced delay of the packet transmission is kept low by the switch. Furthermore, less resources are needed as only a small part of a frame has to be stored at a time. Store-and-forward switching stores a complete frame upon reception, and only after the frame is verified to be correct by calculating the frame check sequence of the received frame and comparing it with the Frame Check Sequence (FCS) field of the frame it is forwarded to the intended destination. This switching technique requires more resources in the switch, as each arriving frame has to be stored and verified. It is especially useful for low performance, low quality networks with a high amount of broken frames. By sorting out the broken frames and not forwarding them, unnecessary network load is avoided.

The specific characteristics of the mentioned techniques of Ethernet packet switching are compared to the needs for the application of this diploma thesis, considering the comparably low throughput and the low number of ports that have to be interconnected.

#### **Buffer Strategies**

Switching almost always leads to the need of buffers. Buffers might only be omitted if a specific application scenario enables the switching fabric to always perform nonblocking packet forwarding, and if not more sources address the same destination port simultaneously than the destination port can handle at once. As these very specific requirements are seldom met, various buffering methods exist and are well understood.

Hluchyj [14] describes and compares four different buffering techniques, namely input queuing, input smoothing, output queuing and completely shared buffering. With input

queuing, each input of the switch has a separate buffer. If the addressed output port of a specific packet temporarily is not accessible, the incoming packet is stored in the input buffer. Input smoothing takes advantage of the statistical distribution of packet destinations by buffering all input during a certain time in all input buffers. All received packets are then released simultaneously from all input ports into the switching fabric (which is enlarged, compared to input buffering), thus smoothing the needed paths through the switching fabric over all available paths. With output queuing all packets are routed immediately to the intended output port and are queued there if more than one packet is routed to the same port at the same time. Completely shared buffering basically uses output buffering as well, but all outputs share one bigger buffer. Additionally, the switching fabric has to be enlarged to allow packets to be routed to the shared buffer if the intended output temporarily is not accessible.

Theoretical considerations lead to the conclusion that pure input queuing by using First In First Out (FIFO) structures reduces the maximum data throughput. As a packet is queued when its destination cannot be reached, a consecutive arriving packet might also be queued behind the first packet, although the destination of the second packet would be reachable. The paper also concludes that the use of completely shared buffering is most efficient in terms of required buffers to achieve a given error rate of dropped packets. This efficiency in terms of buffers is traded off with a higher complexity of the switching fabric, which has to include additional output ports to the buffers.

#### 1.4 Document Structure

This document is intended to provide a thorough presentation of the work that was done to develop a system which fulfils the requirements of the given task. This diploma thesis is embedded in a long term project of packet-based clock synchronization. Although a clear focus is set on the description of the actual work, a brief overview of the Syn1588 clock synchronization project is provided as well.

The basic structure of the main part of this document, chapter 3 to chapter 5, can be compared to a top-down approach, while chapter 2 builds the knowledge base for the work. Beginning with the requirements arising from the surrounding and previously existing hardware units, the challenges are identified and theoretical approaches are discussed and evaluated for the use in the system. Then the design decisions for the actual hardware are presented and discussed in detail. The top-down nature of the description can be found in the gradually increasing level of detail, according to the more general presentation of the required functionality in the beginning, down to the very detailed description of the individual realisation of the functional requirements in the end. In the following, a more detailed description of what can be expected in each chapter is given.

Chapter 2 gives an overview of the already existing technologies which were used and needed for the design of the required hardware. From the task description of this diploma

thesis it becomes clear that protocols and their respective differences are of great importance for the actual work. Therefore, this chapter first gives a brief overview of the used protocols, but also describes the specific details which are important to know for the development of the bus-switching unit, the unit which combines the different bus interfaces. The section about the protocol description might be skipped by experts on the field of the mentioned protocols. Furthermore, a brief description of the Precision Time Protocol (PTP) is given, as well as a short presentation of an application example of the developed bus-switching unit together with the clock synchronization enabled NIC design.

In chapter 3 a functional overview of the complete NIC is given. Based on the functional requirements the main challenges are identified and listed. For all identified challenges the theoretical background is discussed and possible approaches are presented. Well known techniques for generalised problems are considered, and it is investigated whether they can be applied to the present problem or not. Approaches and experiences of similar challenges in different system and application environments are also considered, and conclusions are drawn whether those approaches are suitable for the design of this diploma thesis or not.

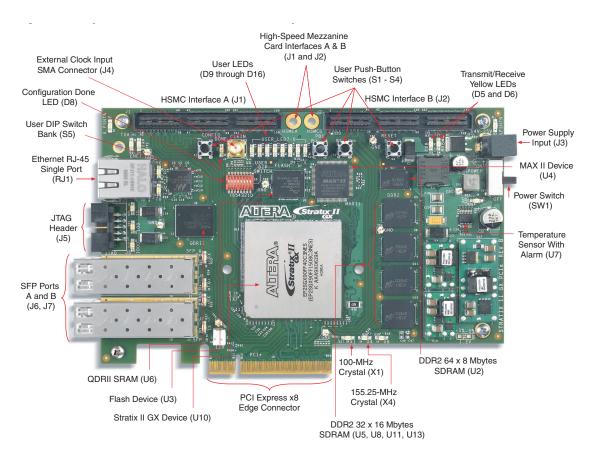

Chapter 4 presents all of the existing hardware that surrounds the bus-switching unit. First, the hardware platform itself, the chosen evaluation board is described. Then the required interconnection of the different units with their individual interfaces is presented.

Chapter 5 describes the actually used methods to develop the required functionality of the evaluation board. The transition from the old to the new hardware platform is described, mentioning some difficulties which came up during the transition as well as some hints to prevent unnecessary errors. Then the bus-switching unit is reviewed, describing each module in detail with regards to the functionality, the respective realisation and the reasons for the chosen realisation. This chapter also gives an insight into the detailed information flow during operation of the bus-switching unit. Finally, some pitfalls that occurred during the development are described, reasons are given why they could occur and hints state how to avoid similar errors in the future.

Chapter 6 describes two distinct simulation environments which were developed for testing and verifying the hardware design. The simulation environments are very different in nature, and therefore they are both explained. Reasons are given why two different environments are needed after all, and what their respective strength and weaknesses are, as well as for which test cases which environment was needed and used.

The last chapter finally concludes this document, recapitulating the major challenges and issues of the design process. Results are presented in a sense of lessons learned about a hardware design which is embedded in an existing system environment. Also, perspectives are given on how the resulting hardware evaluation board can be used, as well as which enhancements and improvements can be performed in the future.

## Chapter 2

# **Technology Overview**

This chapter will present a knowledge base of the technologies in the hardware system that were used. The bigger picture of clock synchronization will also be drawn to understand the intended application of the developed hardware. The bus-switching unit is the main part which has to be developed. It concerns itself about the interconnection of the units with different bus interfaces, translates the protocols and controls the information flow of the interfaces. To understand its operation and the challenges of the development, the protocols in use must be known and understood. Therefore, this chapter presents an overview of the used protocols, giving details only when necessary to understand the hardware design.

#### 2.1 Protocol Overview

In the task description three main protocols were listed which are involved in the system: Ethernet, Advanced High-Performance Bus (AHB) and PCI Express. All three are of different nature, as they are designed for different purposes. Despite their differences they have to be interconnected and data has to be passed from one protocol to the other. This

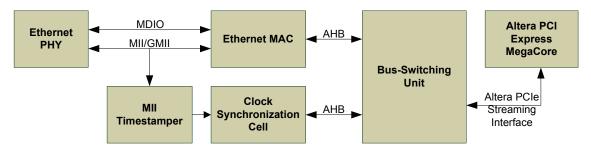

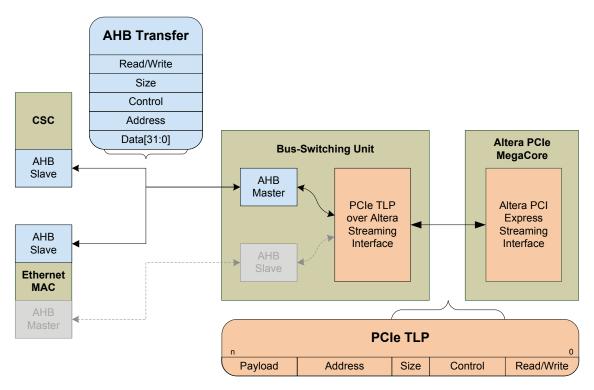

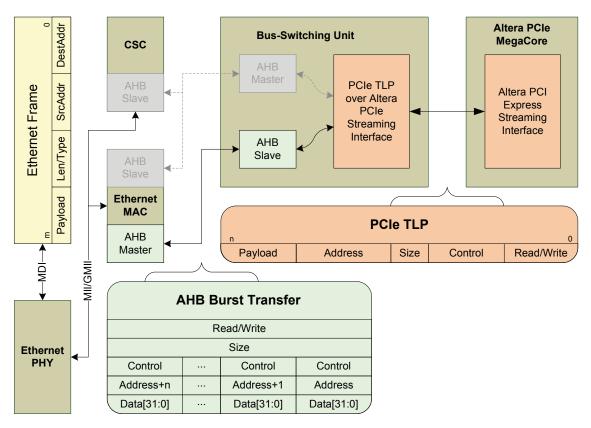

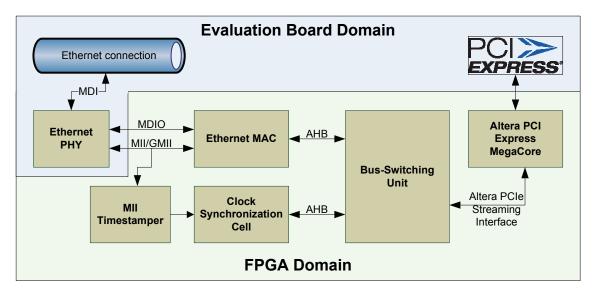

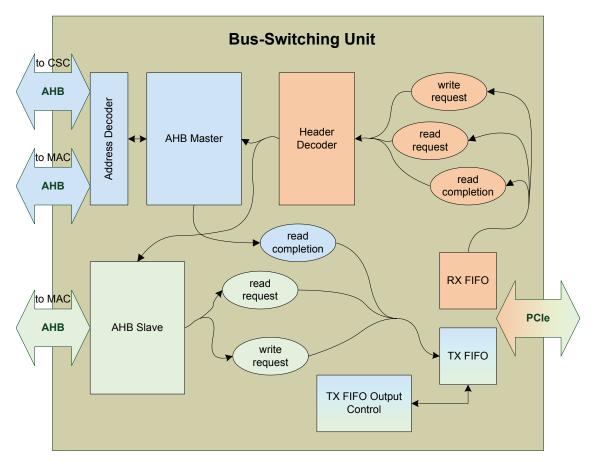

Figure 2.1: Overview of the NIC architecture

raises some questions and challenges which are discussed in the following chapters. Therefore, a description of the protocols in use is given here. Figure 2.1 shows the individual connections of the different units and components of the hardware architecture.

Although the Ethernet protocol is not directly involved in the design of the bus-switching unit, it is still an important part of the overall system and therefore is described here. As the system itself is an Ethernet network interface card, the main task is to process Ethernet traffic. The MAC unit of the existing hardware core processes the Ethernet frames and translates them to AHB transfers and vice versa. Therefore, the bus-switching unit is not directly involved in the handling of Ethernet traffic. Still, the data it must process results from Ethernet frames.

The MII is the data connection between the Ethernet PHY and the MAC. This interface is important for the hardware support for clock synchronization as well as for the simulation environments. The MII management interface is a simple two wire serial interface for the management connection between the Ethernet PHY and the MAC. It consists of the Management Data Clock (MDC) and the Management Data Input/Output (MDIO) signals. It is described because some problems arose with this interface during the hardware transition to the new evaluation board.

The AHB protocol is a high-speed intra-chip bus protocol which is used by the Clock Synchronization Cell (CSC), the unit for the hardware support for clock synchronization, as well as by the MAC. Those two units have to be connected to the PCI Express link, which is depicted on the right side of the figure. The corresponding traffic from and to the PCI Express protocol core interface must be switched and translated. This is the task of the bus-switching unit, and therefore these two protocols are laid out in more depth. Because of the three layered architecture and the complex structure of PCI Express, not the whole PCI Express protocol is explained; only the transaction layer, the highest layer of the PCI Express protocol stack, is reviewed in more detail.

#### 2.1.1 Ethernet

Ethernet, as defined in the IEEE 802.3 standard [5], is a standard for connecting devices in a Local Area Network (LAN) or Metropolitan Area Network (MAN) over a shared medium using the Carrier Sense Multiple Access/Collision Detection (CSMA/CD) access method. Though most office networks use Ethernet in full duplex mode with pointto-point connections where no contention of the shared medium can occur and thus the CSMA/CD mechanism is not used, it still is an important and integral part of the Ethernet protocol. On the one hand many requirements are derived from the necessities for the CSMA/CD access method, e. g. the minimum frame length, and on the other hand classical CSMA/CD implementations are still used in industrial environments.

CSMA/CD access method means that all participants on the shared medium observe the carrier for activity. If there is no activity sensed, each participant is allowed to start the transmission of a packet at any given point in time. If an activity is sensed, the

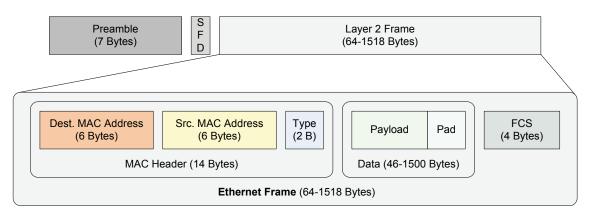

Figure 2.2: Structure of a standard Ethernet packet neglecting extensions

participant has to wait until the shared medium is found to be idle again. After sensing the transmission line to be idle, it has to wait for the time specified by the interframe gap, which is 96 bit times long. Because of the signal propagation delay it might happen that two participants correctly start the transmission of a packet which will collide when they have propagated over the network. In this case, all participants back off and try to retransmit the frame after a random backoff time, with the length of the backoff time being generated randomly, with the maximum duration depending on the number of previously failed transmissions.

#### 2.1.1.1 Ethernet Packets

Ethernet is a packet-based transmission protocol defining two layers according to the ISO Open Systems Interconnection (OSI) reference model [15]. An Ethernet packet on the physical layer consists of a layer two frame plus the preamble and the Start-of-Frame Delimiter (SFD). The structure of a packet and a frame is depicted in figure 2.2. A packet starts with the preamble, which is a sequence of seven times an octet of the hexadecimal value 0x55, which is used for the PHY to synchronize on the received packet. The SFD is an octet of the hexadecimal value 0x5D and indicates the start of a frame.

The SFD is followed by the actual frame which starts with the destination MAC address. The destination address being at the beginning of the frame allows for a quick decision whether the frame is intended for the actual receiver or not, as well as for quick routing decisions in a switch. Moreover, because of the network byte order of Ethernet being big endian and the multicast identification being contained in the first byte of the destination address, a quick decision for multicasts can be performed. The following source address indicates the sender of the frame. The length/type field specifies either a registered Ethernet frame type (values  $\geq 0x600$ ), or it specifies the length of the payload (values  $\leq 0x5DC$ ). The payload field holds the data and is followed by an optional padding field to extend the length of the payload field to the minimum amount of 46 bytes if necessary. The four bytes of the FCS are the last bytes belonging to a frame and contain the value

Figure 2.3: MII signals

of a Cyclic Redundancy Check (CRC), which is computed as a function of all frame fields except for the FCS field itself, thus containing all fields from the destination address to the optional padding field.

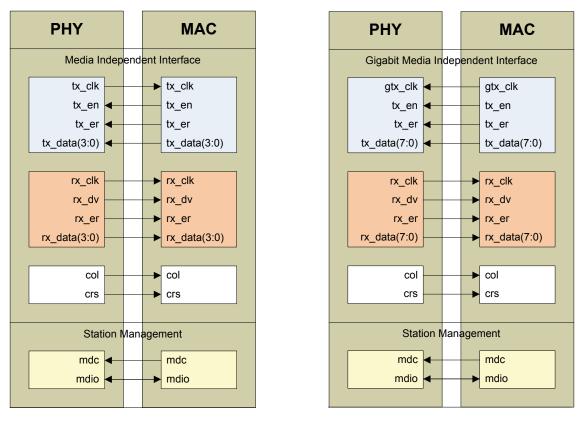

#### 2.1.1.2 PHY to MAC

The Ethernet PHY is on one side connected to the physical medium, the cable. On the other side it is connected to the MAC unit. For this connection two different interfaces are used, the Media Independent Interface (MII) and the MII management interface. All Ethernet data is transmitted over the MII link. The MII basically consists of parallel data lines for the actual Ethernet data, as well as of clock signals and some control signals, while the MII management interface consists of a dedicated clock line and a bidirectional data line, which is called the MDIO signal line.

#### Media Independent Interface

Figure 2.3 shows the various signals of the MII connection between the PHY and the MAC. The data lines (rx\_data and tx\_data) always carry four bits of data in parallel. While the coding and clock frequency of the physical link from one Ethernet node to

another depends on the used medium, the protocol of the MII is independent of the used transmission medium, hence the name. Because of the four parallel data lines the clock frequency for MII is the fourth part of the bit rate. For a 10 Mb/s link the MII clock rate is 2.5 MHz, for 100 Mb/s links the clock rate is 25 MHz. Both, the receive  $(rx\_clk)$  as well as the transmit clock  $(tx\_clk)$  are sourced by the PHY. While the receive clock is derived from the received data, the transmit clock is sourced by a local oscillator. The rest of the signals are control signals which are used to indicate the reception and transmission of a frame  $(rx\_dv \text{ and } tx\_en)$ , for error propagation and detection at the PHY level  $(tx\_er and rx\_er)$  and to propagate a busy line (crs) and the detection of a collision (col).

#### Gigabit Media Independent Interface and Further Derivatives

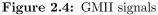

For Gigabit Ethernet the MII is no longer used, but the definition is enhanced to the Gigabit Media Independent Interface (GMII) protocol which is very similar to MII. Figure 2.4 shows the signals of the GMII connection. In comparison to MII, only the data lines are doubled to eight data lines per direction, and the transmit clock (gtx\_clk) is not sourced by the PHY but by the MAC. Because of the increase of the parallel data lines the clock frequency is no longer the fourth part of the bit rate, but the eighth part, thus being 125 MHz for Gigabit Ethernet.

Further derivatives of the MII and GMII definitions with reduced pin counts exist, though they are not covered by the IEEE 802.3 standard specification. Reduced Media Independent Interface (RMII) [16] instead of MII, and Reduced Gigabit Media Independent Interface (RGMII) [17] instead of GMII are de-facto standards proposed by special working groups. Both use less sideband signals and use only half of the data pins than the original definition, but operate at a doubled clock rate. For RMII this means only two data lines at a clock frequency of 5 MHz for 10 Mb/s operation and 50 MHz for 100 Mb/s operation. RGMII uses four data lines and keeps the original clock frequency of 125 MHz, but reacts on both, rising and falling edges of the clock signal and thus doubles the actual data rate.

#### **MII Management Interface**

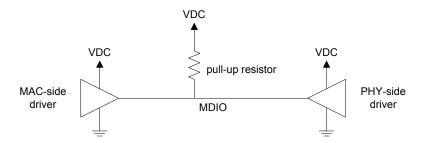

The MII management interface is common to all versions of MII and its derivatives. It consists of two wires, the MDC and the Management Data Input/Output (MDIO), as defined in IEEE 802.3 clause 22. It is a serial interface to transport management frames between the MAC and the PHY. The PHY is requested to have a basic management register set which can be written and read using the MII management interface.

The MDC signal is an aperiodic clock source for the management data frames, which has a minimum period of 400 ns, corresponding to a frequency of 2.5 MHz. The duration of the high and low times must be at least 160 ns each and have no upper bound. The MDIO signal is a bidirectional line which requires both sides to have tri-state drivers and needs a pull-up resistor to pull the bus high in idle state. The structure and timing of the

Figure 2.5: Timing and structure of a MDIO frame

management frames is depicted in figure 2.5. Special to a tristated bus is the turnaround phase. When a read operation is performed, first the MAC drives the MDIO line to initiate the read transfer. In the turnaround phase control is handed over to the PHY to transmit its response using the same MDIO line that the MAC used before. Therefore, the MAC shall change to high impedance state during the first bit time of the turnaround phase while the PHY still stays in high impedance state. During this first bit time both drivers are disabled to prevent a short circuit of the drivers. Only during the second bit time the PHY drives the MDIO line with a zero bit, and thus takes over control of the MDIO signal line.

#### 2.1.2 Advanced High-Performance Bus

The Advanced High-Performance Bus (AHB) protocol [6] is part of the Advanced Microcontroller Bus Architecture (AMBA) specification and is designed as a high-speed intrachip bus for the interconnection of different hardware cores. It is specifically designed for synthesizable, high performance and high clock-rate designs. It is a master-slave architecture, using a non-tristate implementation, supporting pipelined burst transactions and variable data widths from 8 to 1024 bits. Out-of-band control signals together with pipelining enable high performance with very low control overhead. Two different transfer types are supported, non-sequential transfers and burst transfers.

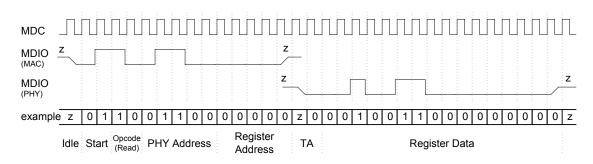

The AHB master slave architecture is designed to support multi-master multi-slave configurations with an address decoder, a dedicated bus arbiter module and the support for split burst transactions to allow optimal resource usage of the shared bus medium. In the course of this diploma thesis only a single-master system is used with no need for an AHB bus arbiter or the support of split transactions. Such a system is also called an AHB lite system [18]. The master and slave bus interfaces are depicted in figure 2.6.

#### 2.1.2.1 Control and Slave Response Signals

The control signals are sourced by the master interface to control the individual AHB transfers. The **trans** signal indicates the type of transfer and encodes either one out of

Figure 2.6: AHB lite master and slave interface signals

four possible transfer types, *idle* (00), *busy* (01), *non-sequential* (10), or sequential (11). The write signal indicates the direction of the transfer. If it is asserted, data is written from the master to the slave. If it is deasserted, data is read from the slave to the master. The size signal specifies the used data width with a valid range from 8 to 1024 bits, where the three bits of the size signal encode an offset of a power of two. An encoded zero of the size signal corresponds to  $2^3 = 8$ , an encoded one corresponds to  $2^4 = 16$ , and the highest encoded value seven corresponds to  $2^{10} = 1024$ . The prot signal is an optional signal for protection control and is not used in the design of the diploma thesis. The same holds true for the lock signal, which can be used in multi-master systems to indicate indivisible transfers.

The address is a byte address (a change of the least significant bit changes the addressed memory by one byte) and is encoded by the 32 available address bits. Their timing is exactly the same as the timing of the control signals, which is depicted and explained in the following sections. An address decoder, usually a simple combinatorial decoder of the high-order address signals, takes care of selecting the addressed slave by asserting the corresponding sel signal. As the minimum memory space that can be mapped to an AHB slave is 1 kB, no burst must cross a 1 kB address boundary in order to prevent transfers to exceed the address range of a slave.

The slave response signals are the **ready** signal and the **resp** signal. The **ready** signal is used to indicate the readiness of the slave. For write transfers this means that the slave indicates by the assertion of the **ready** signal that it is ready to receive data in the next clock cycle. For read transfers the assertion of the **ready** signal indicates valid data on the slave's rdata lines. When the master issues an *idle* transfer, the slave must respond with the ready signal asserted. Therefore, the slave usually can not prevent the master from initiating a transfer, but it can insert wait states until the next data is presented. The response (resp) signal for an AHB lite slave can be either one of two possibilities, okay(0) or error(1). On any kind of error the slave is expected to respond with an error response, which is a two-cycle response. In the first cycle the resp signal has to be asserted to indicate an error, while the ready signal has to be deasserted. In the subsequent cycle the resp signal still stays asserted and the ready signal is asserted as well. A two-cycle response is needed because of the pipelined nature of AHB, to allow the master to cancel a potentially new transfer that has already been issued. A transfer with an error response is shown in figure 2.7b.

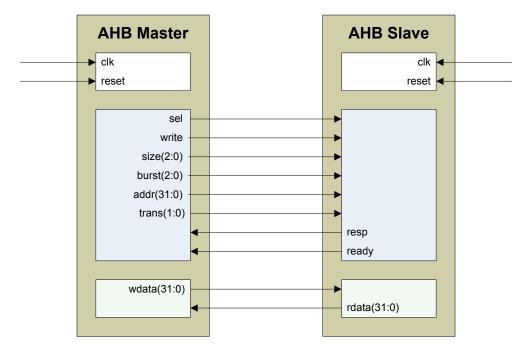

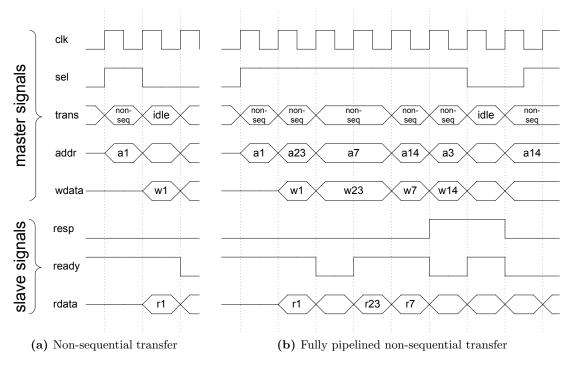

#### 2.1.2.2 Non-Sequential Transfer

The basic transfer type of AHB is the non-sequential transfer. Its duration is two clock cycles, and it consists of two phases, one phase per clock cycle. The first phase is the address phase, where all control signals are asserted according to the intended transfer. A non-sequential transfer consists of exactly one data phase with the duration of one clock cycle. During the data phase the data is presented on the respective data bus, either on rdata for read transfers, or on wdata for write transfers. By using two distinct data buses a two directional bus can be implemented without the need for tristate drivers. The maximum transmittable data during a non-sequential transfer is limited by the data width. Figure 2.7a shows the timing of a typical non-sequential transfer.

For non-sequential transfers one clock cycle is needed for the address phase and one clock cycle for the data phase. This results in an overhead of 50%, which is not acceptable for a high-speed, high-performance bus architecture. Therefore, AHB provides the possibility for pipelining transfers. The first transfer needs a separate address phase, indicating the address and the transfer type for the first data transfer. During the next clock cycle the data is presented, but the address and control lines are not required anymore for the first transfer. They can already be used to initiate the next transfer, with the corresponding data being presented in the subsequent clock cycle. In other words, the data phase of a transfer can simultaneously be used as address phase for the next transfer. Figure 2.7b shows an example for pipelined, non-sequential transfer. The address numbers are chosen arbitrarily to indicate the arbitrary, independent nature of addressing with non-sequential transfers. By pipelining the only remaining protocol overhead is one clock cycle at the beginning, reducing to zero for all subsequent transfers, which makes the protocol perfectly suitable for high-performance applications.

To be able to utilise the full benefit of pipelining both endpoints of the bus have to be fast enough to handle the data within one clock cycle. Not all endpoints are at all times capable of such a high-speed data processing. Therefore, both sides of the AHB protocol are allowed to insert wait states. If the master is not ready to immediately initiate a new

Figure 2.7: Non-sequential AHB transfers

transfer it can simply issue *idle* transfers until it is ready for the next transfer. If the slave is not ready to immediately handle new data it can deassert the **ready** signal and thereby force the master to remain in the current state until the **ready** signal is asserted again, as also shown in 2.7b.

#### 2.1.2.3 Burst Transfer

A burst transfer is very similar to a series of fully pipelined non-sequential transfers, it even starts with a non-sequential transfer. As the name indicates, the important difference to non-sequential transfers is the sequential nature of addresses in a burst transfer. In contrast to non-sequential transfers, where each transfer can have an arbitrary address, independent of the previous transfer, burst transfers have to follow a strict addressing scheme.

The **burst** signal specifies the nature of the burst. It can be either incrementing with an unspecified length, incrementing with a specified length or a wrapping burst of specified length. Specified length transfers can be either one of 4, 8, or 16 beat length, while a beat corresponds to a data cycle. Thus, the number of beats has to be multiplied by the data width to get the actual amount of data which is transferred during a burst transfer.

All addresses within a burst transfer must be aligned to the address boundary which is specified by the size signal. Therefore, all 32 bit transfers must be aligned to 32 bit

Figure 2.8: Example topology of a PCI Express architecture

boundaries (the two least significant bits of the address have to be both zero), all 64 bit transfers must be aligned to 64 bit boundaries (requiring the three least significant bits to be zero). For all incrementing bursts, the address in a subsequent clock cycle must be the address of the previous clock cycle incremented by the size transferred at each beat, specified by the **size** signal. Incrementing bursts with an unspecified length have no further restriction than not to cross a 1 kB address boundary. Wrapping transfers are basically of incremental nature as well, but if they are not started at an address aligned to the total number of bytes transmitted in the burst, they wrap at the boundary of this total number of bytes.

Burst transfers also allow both, slaves and masters to insert wait states. The master can insert *busy* transfers, while the slave again uses the **ready** signal to stall the master. The advantage of burst transfers is the fixed addressing scheme. Many applications and devices need more time to handle a random access transfer than a sequential transfer. Examples are Random Access Memory (RAM) modules which can handle sequential transfers on the same memory page much faster than if the page has to be switched, but also applications which can pack sequentially addressed data into a single container structure.

#### 2.1.3 PCI Express

The PCI Express protocol specification [19] describes PCI Express as a third generation I/O interconnect. It is an advancement of the PCI protocol, intended to stay compatible with PCI concepts such as the load-store architecture and the enumeration process, allowing legacy PCI drivers to work unmodified with a PCI Express design.

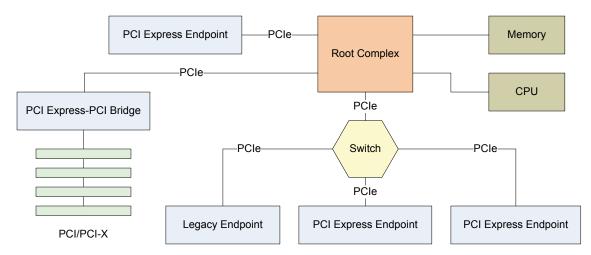

PCI Express is a packet-oriented, switched point-to-point protocol, using a highly scalable, serial differential electrical interface, providing means for e.g. power management, quality of service, data integrity and error handling. Figure 2.8 shows a typical architecture of

Figure 2.9: Three layered architecture of PCI Express

a PCI Express system. It consists of several point-to-point links of the root complex to multiple endpoints, which are I/O devices. The root complex connects the CPU/memory subsystem to the I/O components. The endpoints can be legacy endpoints, which use the PCI Express protocol, but are required to work with a legacy PCI device driver which uses functions supported only for PCI compatibility. Standard PCI Express endpoints use only the semantics specified for pure PCI Express endpoints, and PCI Express-PCI Bridges connect PCI hierarchies to the PCI Express fabric.

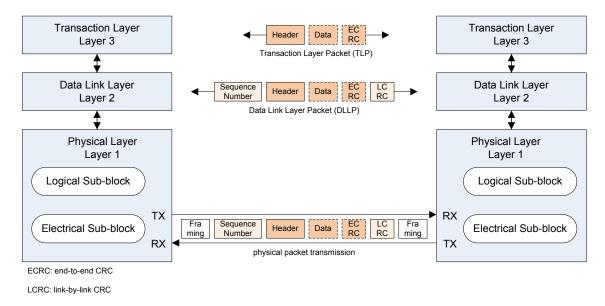

PCI Express is a three layered architecture, specifying a physical layer for the interconnection of the components, a data link layer for link management and data integrity, and a transaction layer to assemble read and write Transaction Layer Packets (TLPs) and for credit-based flow control. Figure 2.9 gives an idea of the data-flow and the respective packet formats through the layers.

#### 2.1.3.1 Transaction Layer

For this diploma thesis only the transaction layer is relevant. The transaction layer of an endpoint communicates with the transaction layer on the other side of the link using transaction layer packets. These packets are of different types and can be addressed to one of four address spaces: memory mapped, I/O mapped, configuration and message. Memory mapped read and write transactions are the standard transaction type for PCI Express endpoints. I/O mapped transactions are only supported for legacy device drivers which require their use. Configuration transactions are used to access the configuration registers of PCI Express devices and are primarily used during the initialisation phase. Message transactions can be viewed as virtual wires which take over all protocol messaging tasks which were previously signalled by out-of-band signal lines, e.g. interrupts, flow control management and power management.

Generally, except for messages, there are two types of transactions, read and write. TLPs which initiate a transaction sequence are called requests. If they operate in the memory mapped address space, they are called memory read and memory write requests, respectively. Memory write requests are posted requests, which means that they don't require an answer from the receiver. Memory read requests are non-posted requests. Read transactions are split transactions, requiring the receiver to send a completion TLP back to the requester which initiated the transfer. To do so, all requests are tagged to be uniquely identifiable, so that the interconnect fabric can route them appropriately to the initiator of the transaction.

#### 2.1.3.2 Transaction Layer Packets

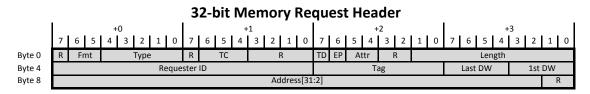

Depending on the address range of an endpoint, Transaction Layer Packets (TLPs) basically consist of a four Double Word (DW) long header for 64-bit addressing, and of a three DW long header for 32-bit addressing plus the data payload and an optional end-to-end CRC field. Figure 2.10 and 2.11 depict the header formats for requests and completions. All fields marked with an R are reserved for future use and must not be used.

The first DW of the header is common to all TLPs. The format field (Fmt) specifies the length of the header (three DW or four DW) and whether data is included in the packet or not. The Type field specifies the type of the TLP. The basic types are read and write, and the type field also defines the address space. Therefore, memory mapped requests have a different type than I/O requests and messages. The fourth type of TLPs are completion as response to previous read requests. Further sub-types are available for locked transfers and special message routing information.

Bits four to six of byte one specify the traffic class (TC) which is used for Quality of Service (QoS). All three bits being zero corresponds to best effort traffic. If the TLP Digest (TD) bit is set, the TLP includes an 32-bit end-to-end CRC (ECRC) field after the data payload. If the error forwarding by data poisoning (EP) field is set, it is indicated that some component along the path of the TLP has found the data to be poisoned. The Attr field contains two bits for optimised traffic handling, the no snoop and relaxed ordering attribute. Finally, the Length field specifies the length of the payload in DWs.

#### Memory Request TLP

Memory request TLPs can be initiated by all participants in the PCI Express complex. They are used to perform read and write transactions on memory mapped devices. The header of memory requests has five additional fields to the common header fields. The **Requester ID** holds the unique number of the requesting PCI Express component. This Identification (ID) is formed by the bus number, device number, and function number.

Figure 2.10: Header format of PCI Express memory requests

The bus and device number of an endpoint might change during operation and have to be tracked. Together with the tag field, which identifies a read request within an endpoint, a unique identifier in the PCI Express system is associated with each request.

Usually, it is sufficient to use only the five least significant bits of the tag field, which corresponds to 32 possible uncompleted requests. The requester is responsible for keeping track of the uncompleted requests and must not have more than 32 outstanding requests at a time. However, the nodes can be configured to use all eight bits of the tag field if required, allowing for 256 concurrently outstanding requests. As write requests are posted requests and do not need a completion, the tag field for write requests is unspecified and may have an arbitrary value.

The Last DW and 1st DW fields specify the valid data bits for payload that is not quadword (64-bit) aligned. The four bits of the 1st DW field correspond to the first four bytes of the data payload, indicating whether a byte contains valid data or not. The four bits of the Last DW specify the usage of the last four bytes of the data payload. The Address field finally stores the full byte address of the transaction and can be 32 bits or 64 bits long, depending on the address range of the PCI Express node. All transactions performed on addresses below four Gigabyte must use a 32-bit address.

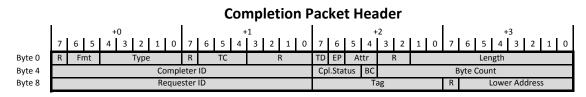

#### Completion TLP

A completion TLP is always the response to a previous non-posted request. It is the second and final part of a split transaction and either returns some data, or in the case of I/O transactions informs the initiator about the completion of the transaction. Figure 2.11 depicts the header format of a PCI Express completion TLP. A completion header has several specific fields in addition to the common header fields. Most of them are used for the correct correlation of a completion to the corresponding read request.

Figure 2.11: Header format of PCI Express completions

The traffic class and attribute field of the common header part have to match the values of the corresponding request. The **Completer ID** specifies the ID of the completing component. The **Cpl Status** field holds information about the completion status of the completer. Currently supported completion states are successful completion, unsupported request (e.g. wrong or unsupported message for a message transaction), configuration request retry status and completer abort, which is used if an endpoint does not support a specific request, although it would be allowed by PCI Express (e.g. read of an unreadable address).

The BC field is a field for legacy PCI-X components and indicates that the byte count has been modified. It is possible to use multiple completions of smaller size to complete a single read request. For this case, the Byte Count field exists and indicates how many bytes still have to be transferred to complete a read request. The Requester ID and Tag field must have the same values as stored in the corresponding read request. These fields are used for routing by the PCI Express complex, to return the completion to the correct requester. Finally, the Lower Address holds the seven least significant bits of the address of the first enabled byte of the read request.

#### 2.1.4 Altera PCI Express Interface

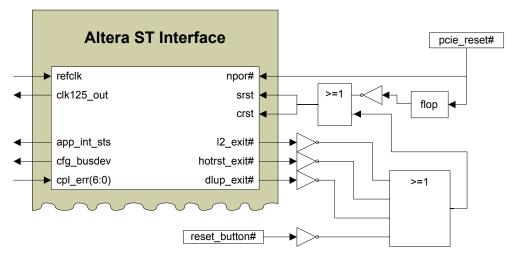

Figure 2.12: Signals of the Altera MegaCore PCI Express Avalon Streaming interface

The Altera<sup>®</sup> MegaCore PCI Express Interface is the interface used between Altera's PCI Express hardware core and the application hardware as described in [20]. A fully featured

PCI Express endpoint embodying the functions of all three layers is quite a complex piece of hardware. Altera offers a ready made solution as part of their MegaCore library, offering an interface to the transaction layer of the PCI Express endpoint. The interface requires the user application to handle data in the form of PCI Express TLPs.

The interface basically consists of an adapted Avalon<sup>®</sup> bus interface for the transmission of TLP data plus additional control and information signals. Figure 2.12 shows the signals of the Avalon bus and important control signals. The Avalon bus is adapted for a direct point to point connection transmitting PCI Express TLPs only. Therefore, no address signals are included and the read and write indicating signals are omitted as well, because the corresponding information is contained in the TLP.

The ref\_clock signal must be sourced by the 100 MHz reference clock of the PCI Express connector. The reference clock line is not allowed to source any other unit than the Altera interface. The transceiver module of the Field Programmable Gate Array (FPGA) device transforms the 100 MHz input clock to a 125 MHz output clock, which can be used as clock source for the application. The assertion of the app\_int\_sts signal triggers the Altera core to generate a PCI Express message TLP and send it upstream, which corresponds to a legacy PCI interrupt. All signals on the right side of the white block in the figure are reset signals and are used for different levels of reset.

The transmission of a TLP always starts with the assertion of the Start Of Packet (SOP) signal line  $(rx\_sop \text{ and } tx\_sop)$  during the first data cycle. Simultaneously with the assertion of the SOP indicator the data valid signals  $(rx\_valid \text{ and } tx\_valid)$  are asserted together, indicating that the data lines contain valid information. The ready signal is used by the receiving side to insert wait states, but in contrast to the AHB the transmitting side only needs to react on a change of the ready signal within three clock cycles. The valid signals must stay asserted throughout the whole transmission, except for a three clock cycles delayed reaction on a change of the ready signal. They must not be used to insert wait states by the transmission side. Actually, there are no means at all for the transmission side to stall a transmission by inserting wait states. The transmission is finished when the End Of Packet (EOP) signal is asserted during the clock cycle when the last data is transmitted. After this last data cycle all signals are deasserted again and the transmission is finished.

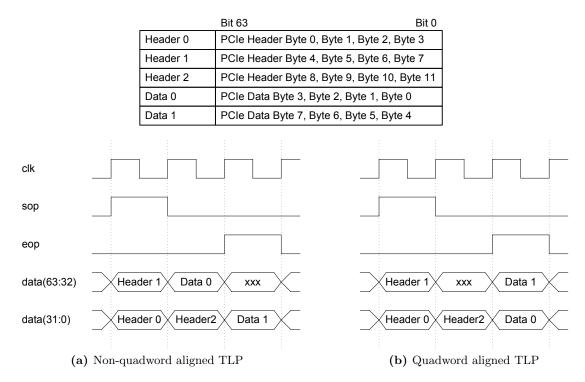

The interface is responsible for the transmission of TLPs between the PCI Express core and the application hardware. The TLP information simply is transferred using the 64-bit wide data lines of the Avalon interface. But the mapping of TLP payload to the Avalon bus depends on the address alignment of the TLP. Figure 2.13 shows the difference between non-quadword and quadword aligned addresses. For non-quadword aligned addresses the first DW of payload data directly follows the header data, while the data of quadword aligned addresses only starts with the next full quadword and leaves the upper DW after the header data unused.

The rest of the signals concern configuration specific information, e.g. the bus device number (cfg\_busdev) or the addressed memory bar (rx\_bardec), depending on the real

Figure 2.13: Mapping of 32-bit addressed PCI Express TLP to Avalon ST bus

address assigned to the PCI Express node during initialisation. Further signals are used for different levels of reset, for interrupt generation, and error reporting.

#### 2.1.5 Precision Time Protocol

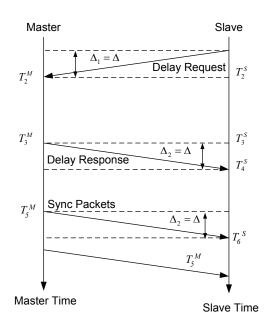

The Precision Time Protocol (PTP) is a standardised protocol for clock synchronisation in packet-oriented, distributed network architectures such as Ethernet. It is defined in the IEEE 1588 standard [3], a standard for precise synchronization of clocks in measurement and control systems.