Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DIPLOMARBEIT

# Upgrade Studies for the Belle Silicon Vertex Detector

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Diplom-Ingenieurs unter der Leitung von

Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Karl Riedling E366 Institut für Sensor- und Aktuatorsysteme

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Christian Irmler Fritz-Kandl-Gasse 5/6/3 A 1210 Wien Matr.Nr. 9126972

Wien, 19. August 2008

Christian Irmler

# Kurzfassung

Silizium-Mikro-Streifen-Detektoren sind heutzutage von sehr großer Bedeutung für die Hochenergiephysik, da sie in nahezu allen Experimenten zur Messung der Spuren elektrisch geladener Teilchen, welche bei der Kollision von Teilchenstrahlen in Beschleunigeranlagen entstehen, verwendet werden. Ein Beispiel ist der Belle-Detektor, der sich um den Kollissionspunkt des Elektron-Positron-Beschleunigers der High Energy Accelerator Research Organization (KEK) in Tsukuba, Japan, befindet.

Der derzeit im Belle-Experiment installierte Silicon Vertex Detector (SVD) leidet unter der immer größer werdenden Occupancy (darunter versteht man den Anteil der Streifen, die zu einem beliebigen Zeitpunkt ein Signal ungleich Null liefern) der innersten Lage. Diese Diplomarbeit beschäftigt sich mit Methoden zur Reduktion der Occupancy von Silizium-Detektor-Systemen. Um dies zu erreichen, besteht eine Möglichkeit darin, die Streifenlänge und somit die sensitive Fläche der Silizium-Sensoren zu reduzieren, was aber zwingend zu einer Erhöhung der auszulesenden Kanäle führt. Ein anderer Ansatz ist es, die derzeitige Ausleseelektronik durch ein System mit kürzerer Integrationszeit zu ersetzen, wodurch das sensitive Zeitfenster verringert wird.

In dieser Arbeit wird gezeigt, wie der schnelle und moderne Auslesechip APV25, welcher ursprünglich für den Silicon Strip Tracker des Compact-Muon-Solenid-Projekts (CMS) am CERN (Geneva, CH) entwickelt wurde, unter den Bedingungen des Belle-Experiments eingesetzt werden kann. Im Gegensatz zu CMS, wo einseitige Sensoren verwendet werden, arbeitet der Belle-SVD mit doppelseitigen Silizium-Streifen-Detektoren (DSSD), was umfassende Änderungen des Auslesesystems erfordert.

Die Hauptaufgabe des Projekts bestand darin, einen Prototypen einer solchen Ausleseelektronik zu entwerfen und die Software zur Datennahme und -analyse an die neuen Erfordernisse anzupassen. Weiters wurde eine verbesserte Methode der Datenauswertung unter Verwendung des APV25 in die Software implementiert, welche es ermöglicht, den wahren Durchtrittszeitpunkt eines Teilchens mit bisher nicht erreichter Genauigkeit zu rekonstruieren.

Abschließend wurde die Funktion des Protoypen, der Software und der modifizierten Datenanalyse durch mehrere Messreihen in Teilchenstrahlen (Beam Tests) am KEK und am Paul Scherer Institut (PSI, Villigen, CH) evaluiert. Die dabei gewonnen, hervorragenden Ergebnisse waren ausschlaggebend dafür, dass bereits an einer Implementierung des Nachfolgers des derzeitigen Belle-SVDs gearbeitet wird, wobei der APV25 und andere Teile des neu entworfenen Auslesesystems zum Einsatz kommen werden.

Diese Diplomarbeit umfasst nur die Anfänge meiner im Jahr 2004 begonnenen Tätigkeit für das Institut für Hochenergiephysik der Österreichischen Akademie der Wissenschaften (HEPHY). Weiterführende Themen werden im Kapitel "Summary and Outlook" kurz vorgestellt. Da die Entwicklungsarbeit zu diesem Projekt weiterläuft, kann zum jetzigen Zeitpunkt noch kein abschließender Bericht verfasst werden.

Stichworte: Siliziumdetektor, Streifendetektor, Vertexdetektor, Ausleseelektronik, Verstärker, APV25, Belle, SVD, KEK, Upgrade, Occupancy

# Abstract

Today silicon microstrip detectors are very important for the research of high energy physics, because in virtually every experiment they are used to measure the tracks of charged particles which are produced by colliding particle beams. Such an experiment is the Belle detector, which is located around the collision point of the electron positron accelerator of the High Energy Accelerator Research Organization (KEK) in Tsukuba, Japan.

The currently installed Silicon Vertex Detector (SVD) of the Belle experiment suffers from the increasing occupancy (fraction of hit channels with non-zero signal at any random moment) of its innermost layer. This diploma thesis describes methods to reduce the occupancy of such a detector system. One possible improvement is to shorten the strips of the silicon sensors and thus reduce their active area, but this implies an increase of the total number of readout channels. Another method is to replace the currently installed readout electronics by one with a shorter integration period, which reduces the sensitive time window.

It will be shown how the fast and modern readout chip APV25, which was originally developed for the Silicon Strip Tracker of the Compact Muon Solenoid (CMS) project at CERN (Geneva, CH), can be used in the environment of the Belle experiment. In contrast to CMS, which uses single-sided sensors, the Belle SVD employs double-sided silicon strip detectors (DSSDs) which require significant modifications to the readout system.

The main task of this thesis was the development of a prototype of such a readout system and the revision of the data acquisition and analysis software to meet the new requirements. Furthermore, an advanced data processing method which can be applied using the APV25 was implemented into the software. With this method it is possible to reconstruct the time when the particle traversed the sensor with unprecedented precision.

Finally the readout system, the software and the improved data acquisition method were evaluated in several particle beam tests at the KEK and the Paul Scherer Institut (PSI, Villigen, CH) with excellent results. Since the requirements are easily met, it was decided to initiate the replacement of whole the Belle SVD, using the APV25 and other components of the new readout system.

This thesis covers only the earlier part of my work for the Institute of High Energy Physics of the Austrian Academy of Sciences (HEPHY), which i started in 2004. Additional topics are briefly introduced in the chapter "Summary and Outlook". As work is ongoing, it is too early to give a final report.

**Keywords:** silicon detector, strip detector, silicon vertex detector, occupancy, readout electronics, amplifier, APV, Belle, SVD, KEK, upgrade

# Contents

| 1. | Intro | oduction                                                                                                                                                        | 1 |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 1.1.  | The KEK B-Factory                                                                                                                                               | 1 |

|    | 1.2.  | The Belle Experiment                                                                                                                                            | 3 |

|    | 1.3.  | Belle Detector                                                                                                                                                  | 6 |

|    |       | 1.3.1. Silicon Vertex Detector                                                                                                                                  | 6 |

|    |       | 1.3.2. Central Drift Chamber                                                                                                                                    | 7 |

|    |       | 1.3.3. Silica-Aerogel Cherenkov Counter (ACC)                                                                                                                   | 7 |

|    |       | 1.3.4. Time-of-Flight Counters (TOF)                                                                                                                            | 7 |

|    |       | 1.3.5. Electromagnetic Calorimeter (ECL)                                                                                                                        | 8 |

|    |       | 1.3.6. Kaon and Muon Detection System (KLM)                                                                                                                     | 8 |

|    |       |                                                                                                                                                                 | 8 |

| 2. | Silic | on Detectors and Readout                                                                                                                                        | 9 |

|    | 2.1.  | Silicon Detector                                                                                                                                                | 9 |

|    |       | 2.1.1. Energy Loss                                                                                                                                              | 9 |

|    |       | 2.1.2. Charge Collection $\ldots \ldots \ldots$ | 0 |

|    | 2.2.  | Detector Design                                                                                                                                                 | 6 |

|    |       | 2.2.1. Strip Detectors                                                                                                                                          | 6 |

|    |       | 2.2.2. Pixel Detector                                                                                                                                           | 9 |

|    | 2.3.  | Readout Electronics                                                                                                                                             | 0 |

|    |       | 2.3.1. Front-End Electronics                                                                                                                                    | 1 |

|    |       | 2.3.2. Back-End Electronics                                                                                                                                     | 2 |

|    | 2.4.  | Noise                                                                                                                                                           | 3 |

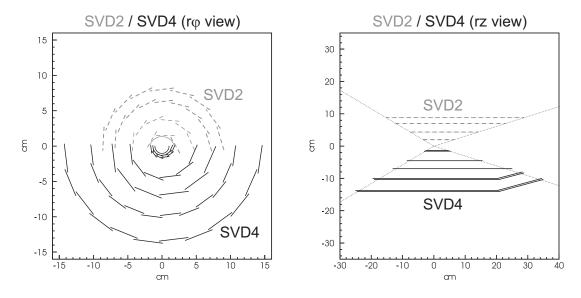

| 3. | Bell  | e Silicon Vertex Detector 20                                                                                                                                    | 6 |

|    |       | History                                                                                                                                                         |   |

|    | 3.2.  | Current State                                                                                                                                                   |   |

|    |       | 3.2.1. Silicon Sensors                                                                                                                                          |   |

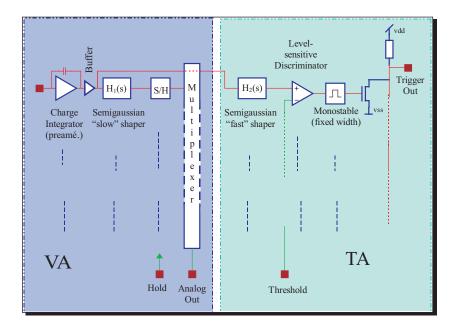

|    |       | 3.2.2. VA1TA                                                                                                                                                    |   |

|    |       | 3.2.3. Readout System                                                                                                                                           |   |

|    | 3.3.  | Limitations of the SVD2                                                                                                                                         |   |

|    |       | 3.3.1. Occupancy                                                                                                                                                |   |

|    |       | 3.3.2. Dead Time                                                                                                                                                | 5 |

| 4. |       | upancy Reduction 30                                                                                                                                             |   |

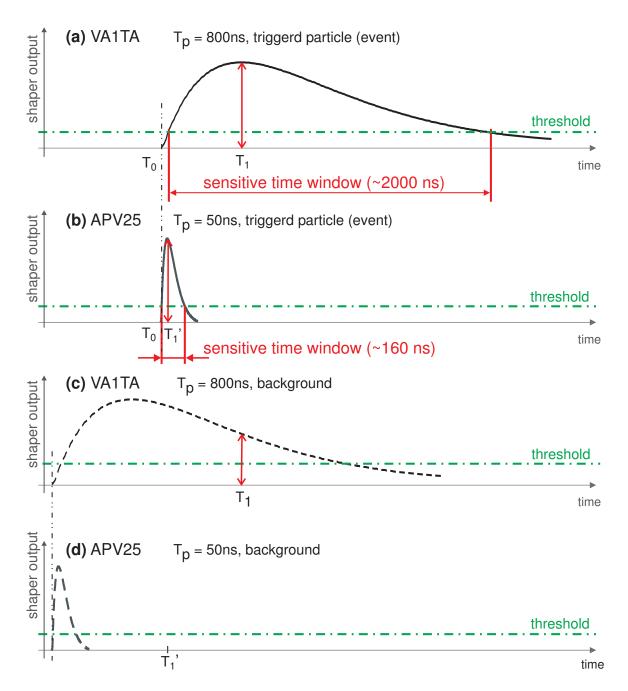

|    |       | Shaping Time Reduction                                                                                                                                          |   |

|    |       | Hit Time Reconstruction                                                                                                                                         |   |

|    | 4.3.  | Sensor Geometry                                                                                                                                                 | 9 |

| 5. |       | Upgrade 4                                                                                                                                                       | - |

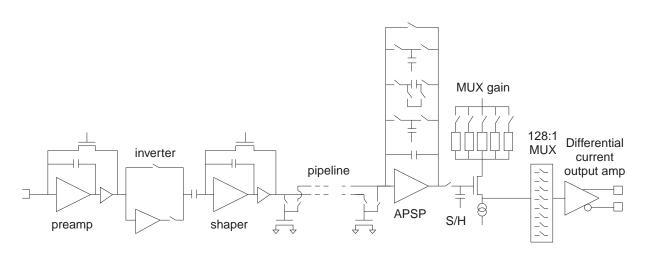

|    | 5.1.  | APV25                                                                                                                                                           | 1 |

|     |                                 | 5.1.1.       Operation Modes      | $\frac{43}{45}$ |  |

|-----|---------------------------------|-----------------------------------|-----------------|--|

|     |                                 | 5.1.2. Inpenne                    | 45<br>45        |  |

|     |                                 | 1                                 | 45<br>46        |  |

|     | 5.2.                            | 1                                 |                 |  |

|     | 0.2.                            | UV sensor                         | 47              |  |

| 6.  | ΑΡ\                             | /DAQ Test System                  | 49              |  |

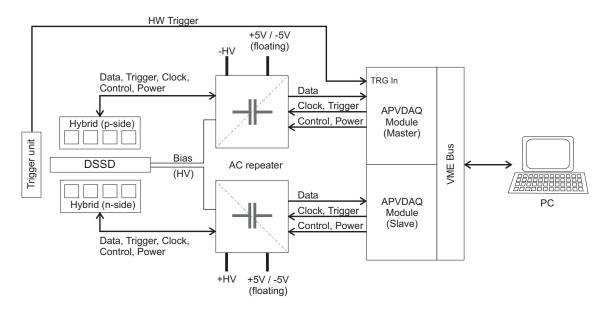

| •.  | 6.1.                            | Overview                          | 49              |  |

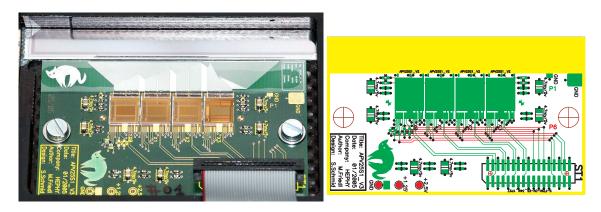

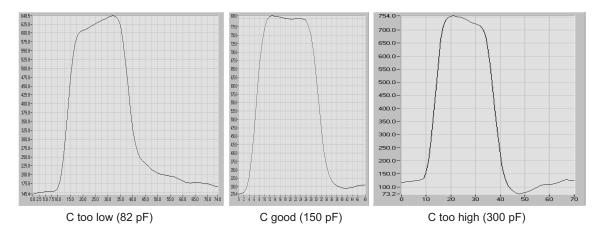

|     | 6.2.                            | APV25 Hybrid                      | 50              |  |

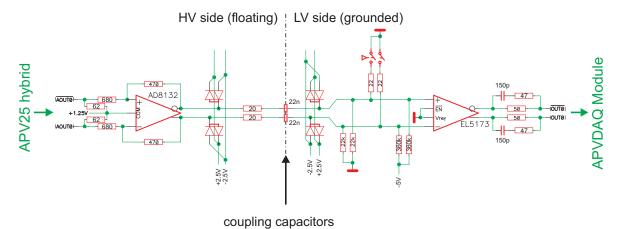

|     | 6.3.                            | AC Repeater                       | 51              |  |

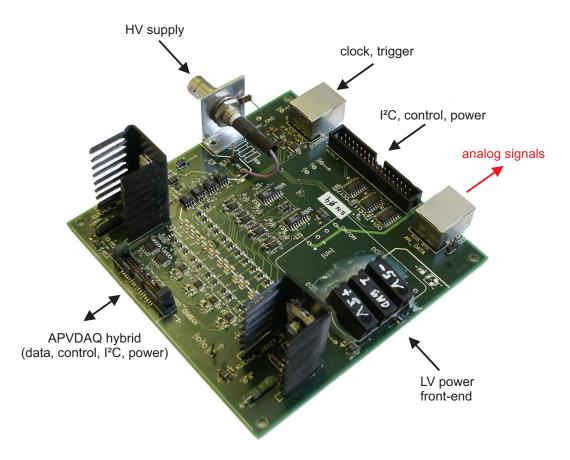

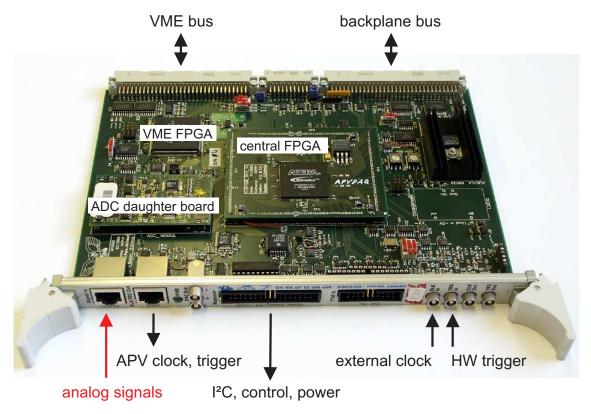

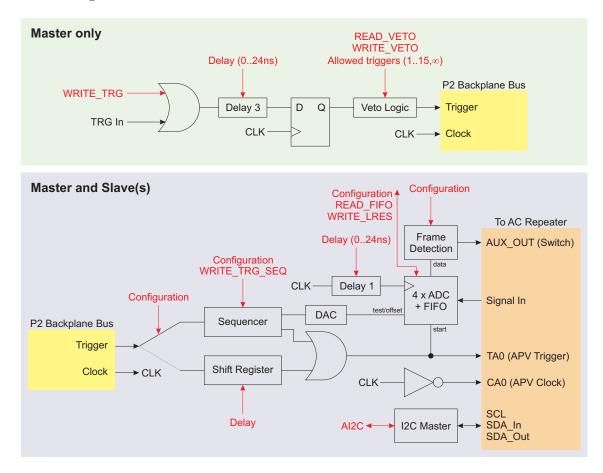

|     | 6.4.                            | APVDAQ VME Module                 | 53              |  |

|     |                                 | •                                 |                 |  |

|     | 6.5.                            | Cabling                           | 56              |  |

|     |                                 | 6.5.1. Hybrid - Repeater          | 56              |  |

|     |                                 | 6.5.2. Repeater - APVDAQ module   | 56              |  |

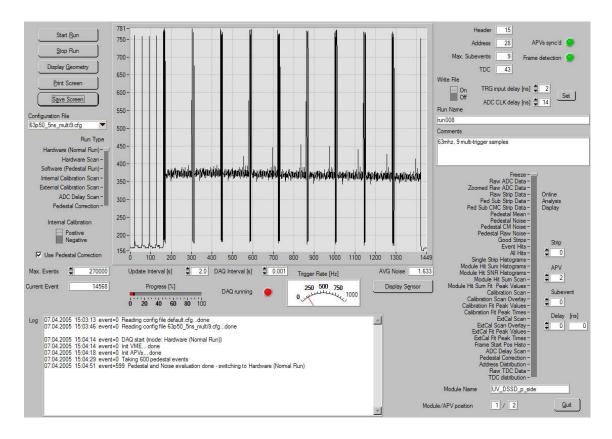

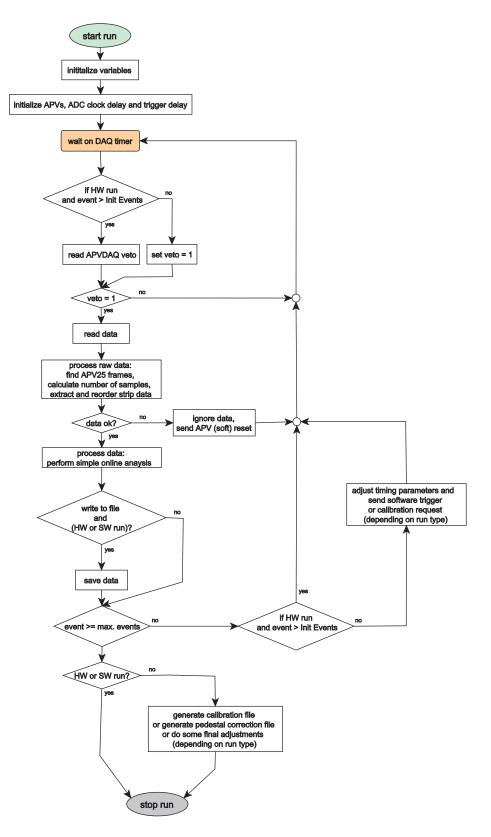

|     | 6.6.                            | Data Acquisition Software         | 57              |  |

|     |                                 | 6.6.1. Run Types                  | 59              |  |

|     |                                 | 6.6.2. Data Acquisition Procedure | 62              |  |

| 7   | Moo                             | surements and Results             | 65              |  |

| 1.  |                                 |                                   | <b>6</b> 5      |  |

|     | 1.1.                            | 0                                 | 65              |  |

|     |                                 | 1                                 |                 |  |

|     |                                 |                                   | 67              |  |

|     | 7.2.                            |                                   | 69              |  |

|     | 7.3.                            | Beam Test Setup                   | 71              |  |

|     |                                 | 7.3.1. Time to Digital Converter  | 72              |  |

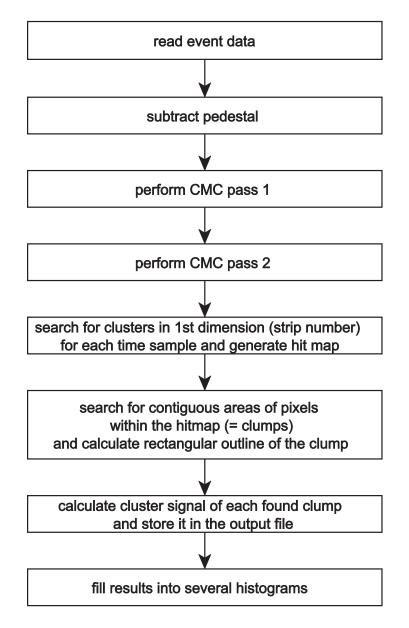

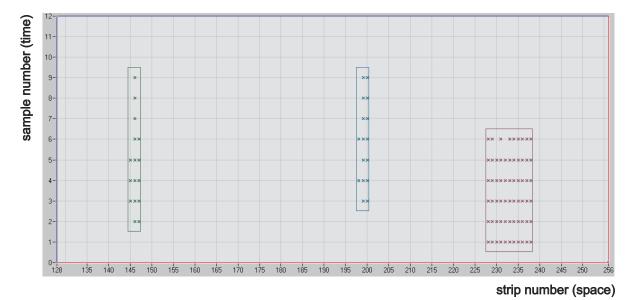

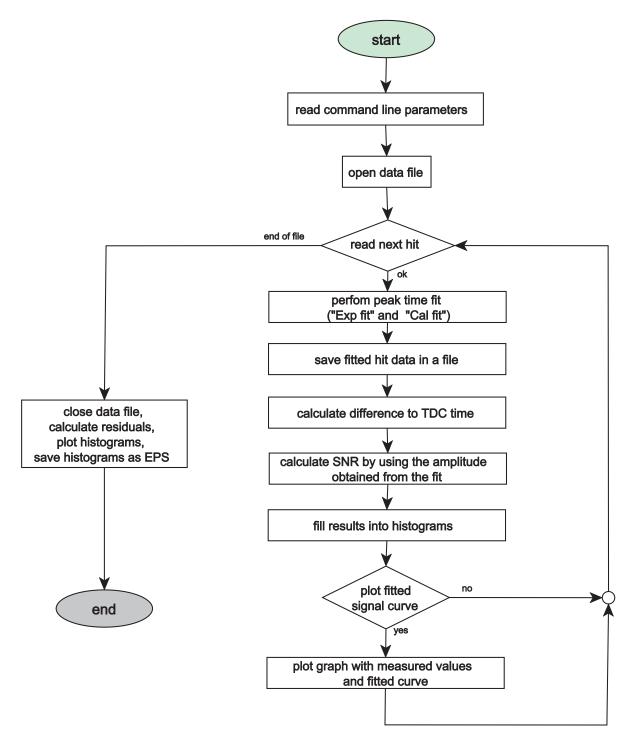

|     | 7.4.                            | Analysis Software                 | 73              |  |

|     |                                 | 7.4.1. Overview                   | 73              |  |

|     |                                 | 7.4.2. Analysis Procedure         | 74              |  |

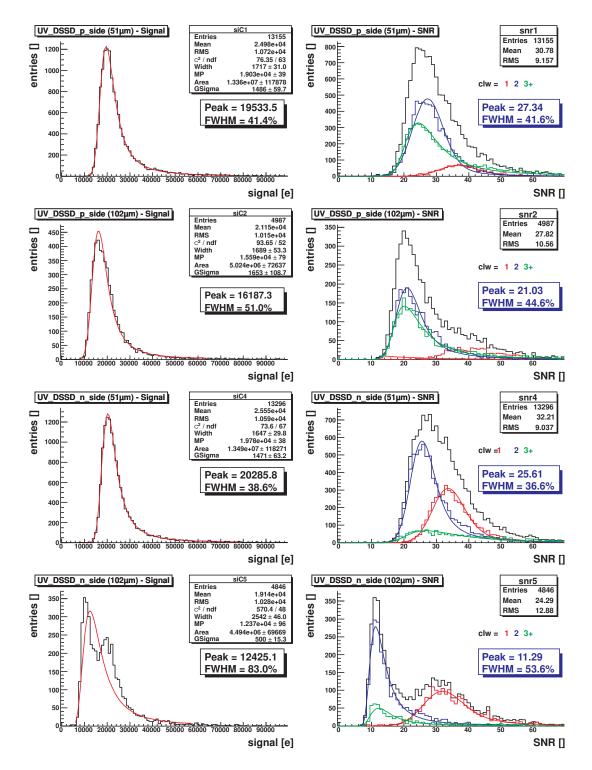

|     | 7.5.                            | System Performance                | 77              |  |

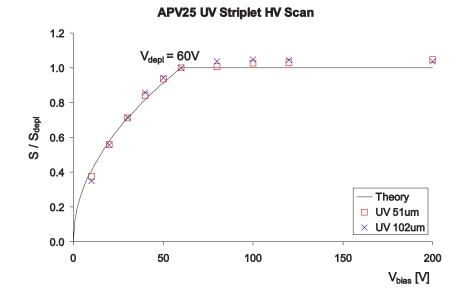

|     |                                 | 7.5.1. HV Scan                    | 79              |  |

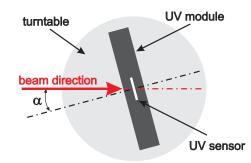

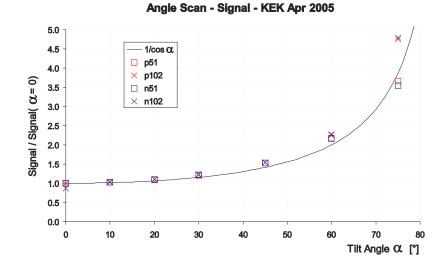

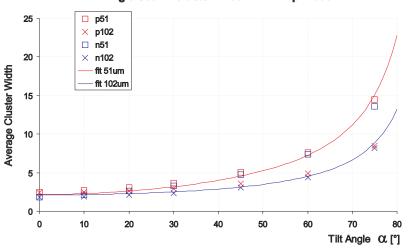

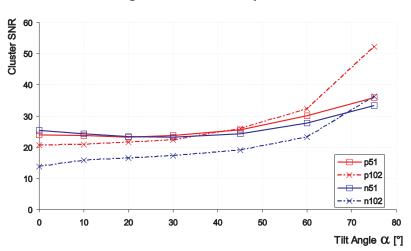

|     |                                 | 7.5.2. Angle Scan                 | 80              |  |

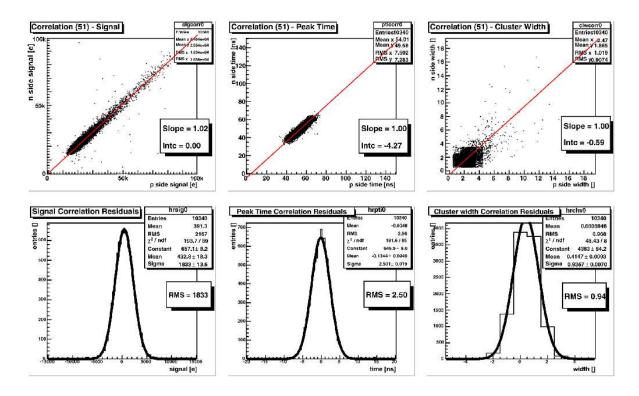

|     |                                 | 7.5.3. UV Correlation             | 82              |  |

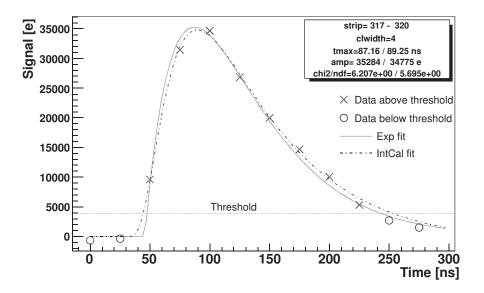

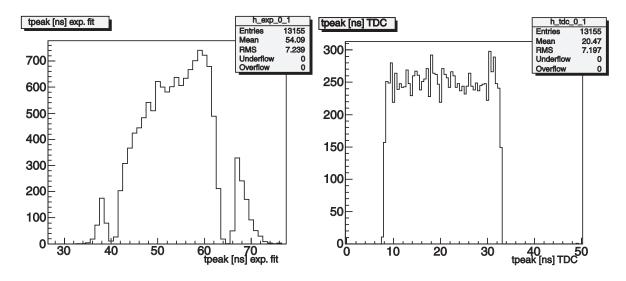

|     | 7.6.                            | Hit Time Reconstruction           | 84              |  |

|     |                                 | 7.6.1. Fitting Methods            | 86              |  |

|     |                                 |                                   | 86              |  |

|     |                                 |                                   | 88              |  |

|     |                                 |                                   |                 |  |

|     |                                 | 7.6.2. Time Resolution $\ldots$   | 89              |  |

| 8.  | Sum                             | mary and Outlook                  | 92              |  |

|     |                                 |                                   | <u> </u>        |  |

| Ac  | know                            | vledgements                       | 95              |  |

| Ар  | Appendix 96                     |                                   |                 |  |

| Α.  | A. APVDAQ Configuration File 97 |                                   |                 |  |

| Bil | Bibliography 101                |                                   |                 |  |

# 1. Introduction

A lot of new phenomena and principles were discovered by particle physicists in the last century. They established a sophisticated theory called "Standard Model" (SM) of particle physics, describing elementary particles, which are the building blocks of matter and the universe, and their interactions. Even tough the SM was very successful, several open issues remained and have to be investigated.

Therefore, large-scale accelerators are used to generate highly energetic beams in opposite directions and bring them to collision in order to produce and study a variety of particles that are not available in nature today. Physicists are interested to observe these new particles because they help to understand the conditions of the universe shortly after the big bang.

### 1.1. The KEK B-Factory

KEKB is an asymmetric electron-positron collider located at the High Energy Accelerator Research Organization (KEK) in Tsukuba, Japan. Asymmetric means that the two beams of the collider are operated at different (kinetic) energies. It is a B-factory aiming to produce copious B and  $\bar{B}$  meson<sup>1</sup> pairs from the  $\Upsilon(4S)$  resonance at a center of mass energy ( $E_{CM}$ ) of 10.58 GeV. The  $\Upsilon(4S)$  is a meson which contains a b-quark and a b-antiquark and immediately decays into a B<sup>0</sup> $\bar{B}^0$  pair with a very high probability [1]. The physics goal of KEKB is to study decays of such B<sup>0</sup> $\bar{B}^0$  pairs and will be described in detail in section 1.2.

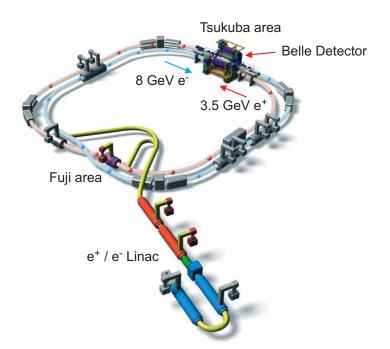

The construction of the collider was started in April 1994 and completed in November 1998 [2]. It has two rings of 3016 m circumference, the high energy ring (HER) for 8 GeV electrons and the low energy ring (LER) for 3.5 GeV positrons installed side by side in a tunnel 11 m below ground level. Fig. 1.1 shows the schematic layout of the KEKB collider. A linear accelerator system generates and injects both beams directly into each ring at full energies. The rings cross at the interaction point in the so-called Tsukuba experimental hall where the electrons and positrons are brought to collision. At this location, the Belle experiment<sup>2</sup> (see section 1.2) with its particle detector is installed around the interaction point. To get equal circumferences of both rings, a second crossing is situated opposite to the collision point in the so-called Fuji hall where the two rings pass each other at different heights without interaction.

The rate R of reaction in a collider is defined by

$$R = \sigma \mathcal{L} \tag{1.1}$$

where  $\sigma$  is the cross section of the interaction region at the collision point and  $\mathcal{L}$  is called the luminosity, usually expressed in cm<sup>-2</sup>s<sup>-1</sup>. In a system with two oppositely directed

<sup>&</sup>lt;sup>1</sup>Mesons are non-elementary particles composed of an even number of quarks and antiquarks. The B meson consists of a b-antiquark and either an u- or d-quark. Its antiparticle, the  $\bar{B}$  meson, is made of a b-quark and an u- or d-antiquark.

<sup>&</sup>lt;sup>2</sup>In terms of High Energy Physics, "experiment" is often used synchronously to "detector".

Figure 1.1.: Schematic layout of the KEKB collider with the LER colored in red and the HER colored in blue, respectively.

beams of particles traveling in bunches it can be expressed by

$$\mathcal{L} = fn \frac{N_1 N_2}{\sigma_x \sigma_y} \quad . \tag{1.2}$$

In eq. 1.2 f stands for the revolution frequency, n is the number of bunches present in the rings,  $N_1$  and  $N_2$  are the number of particles in each bunch and the product  $\sigma_x \sigma_y$  describes the cross sectional area  $\sigma$  of the beams [1].

Due to the aims of Belle the collider was originally designed to obtain a luminosity of more than  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> which is more than one order of magnitude higher than the maximum ever achieved by other electron-positron colliders [3]. The design beam currents in the rings are 1.1 A in the HER and 2.6 A in the LER carried by approximately 5000 bunches with 0.6 m bunch spacing. In November 2006, a peak luminosity of  $1.712 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> was reached and is aimed to be even further increased in the future.

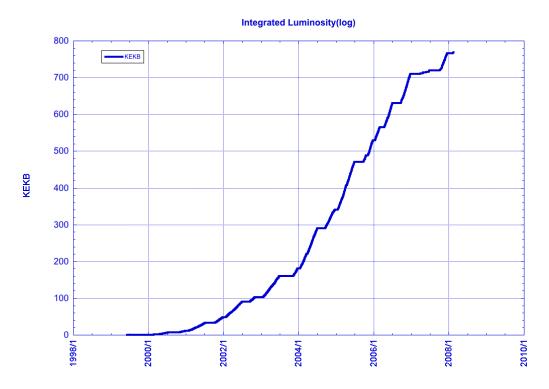

An important value to characterize the performance of an accelerator is the integrated luminosity, which is the integral of the luminosity with respect to time. Its unit is  $m^{-1}$ , but in terms of particle physics, it is usually expressed in inverse Barn (b<sup>-1</sup>), where 1 b =  $10^{-28}$  m<sup>2</sup>. Since the commissioning of KEKB an integrated luminosity of 771296 pb<sup>-1</sup> was achieved, which approximately corresponds to 771 M BB pairs. Fig. 1.2 illustrates the history of the total integrated luminosity.

Another interesting feature of the KEKB collider is the finite-angle crossing at the interaction point, which means that the electron and positron bunches collide at an angle of  $\pm 11$  mrad. Using this scheme, parasitic collisions are reduced and furthermore no separation dipole magnets are necessary such that the interaction region is much simpler than in systems with head-to-head collision. [4]

Figure 1.2.: Integrated luminosity history of KEKB since the commissioning in 1998.

### 1.2. The Belle Experiment

Physicists suppose that the very young universe consisted of equal amounts of matter and antimatter. Today's world is entirely made of matter, while antimatter can only be artificially produced in laboratories. What is the reason of this fact? Why has matter become dominant to antimatter? This is one of the unsolved questions in physics for which scientists try to find an answer. One explanation of this phenomenon can be found in the violation of the Charge-Parity (CP) symmetry, also called CP violation. The CP transformation describes a combined inversion of charge (C) and parity (P) of particles. In detail, the C operation reverses all quantum numbers like electric charge, lepton number, strangeness, etc., which means the transformation of a particle into its antiparticle, for instance an electron into a positrons. The P conversion revolves the direction of all coordinates of the position vector and corresponds to a reflection in a plane mirror, followed by a rotation by 180° [5].

For a long time it was commonly assumed that the CP is conserved. However, in 1964 the physicists Christenson, Cronin, Fitch and Turlay detected a violation of the CP symmetry at the decay of neutral K mesons [6]. Since then, CP violation has been measured and confirmed in several experiments. Until recently, it was only possible to observe a very small effect in the decay rates of K mesons.

A theoretical explanation of the CP violation within the SM was given by Makoto Kobayashi and Toshihide Maskawa in the year 1973 [7]. They published a complex unitary 3 x 3 matrix, later called Cabibbo-Kobayashi-Maskawa-Matrix ( $V_{CKM}$ ), which was derived from Nicola Cabibbos work [8] by adding a third, at this time still undiscovered, generation<sup>3</sup> of quarks. The matrix describes the mixing between different quark

$<sup>^{3}</sup>$ Quarks of different generations only differ in their mass, all other interactions and quantum numbers are identical. In the SM there are three generations with two quarks in each, one with -1/3 e charge

generations and is given by

$$\begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix} = \begin{pmatrix} d' \\ s' \\ b' \end{pmatrix} \quad .$$

(1.3)

On the left side of eq. 1.3 the CKM matrix is multiplied with a vector of flavor<sup>4</sup> eigenstates of the quarks and on the right are the mass eigenstates of the quarks, which are a linear combination of them. Kobayashi and Maskawa further postulated that the phenomenon of CP violation is only possible in accordance with the SM when the elements  $V_{ub}$  and  $V_{td}$  have a complex phase. There are several parameterizations of the CKM. Using the Wolfenstein parameterization [9], the matrix can be expressed by

$$V_{CKM} = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3 \left(\rho - j\eta\right) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3 \left(1 - \rho - j\eta\right) & -A\lambda^2 & 1 \end{pmatrix} , \qquad (1.4)$$

where the imaginary term  $\eta$  is the so called Kobayashi-Maskawa phase and A,  $\rho$  and  $\lambda$  are real numbers. The unitarity of the CKM determines

$$\sum_{i} V_{ij} V_{ik}^* = \delta_{jk} \quad \text{and} \quad \sum_{j} V_{ij} V_{kj}^* = \delta_{jk} \quad , \tag{1.5}$$

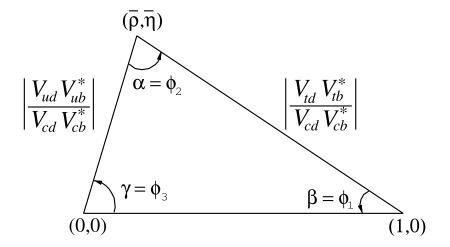

and the six resulting combinations can be represented as triangles in a complex plane, each of which is called an unitary triangle. Their shapes are in general very different, but they all confine the same area, which is related to the CP violation phase. The most commonly used unitary triangle derives from

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0 (1.6)$$

by dividing each side by the best-known one,  $V_{cd}V_{cb}^*$ . The aim of physicists is to determine

Figure 1.3.: Sketch of the unitary triangle derived from eq. 1.6 [10]

the sides and the three angles  $(\phi_1, \phi_2, \phi_3)$  of the unitary triangle by measurements in

<sup>(</sup>down-type) and the other with +2/3 e charge (up-type).

<sup>&</sup>lt;sup>4</sup>Flavor is a quantum number of elementary particles related to their weak interactions.

large-scaled experiments. Such a dedicated experiment is Belle<sup>5</sup>, located around the interaction point of the KEKB accelerator (see 1.1). The primary motivation of Belle is to measure CP violating effects in neutral B meson decays to get direct information on the angles of the unitary triangle.

One of these effects is the time-dependent CP asymmetry [11, 12] of neutral B decays given by

$$a\left(\Delta t\right) = \frac{\Gamma\left(B^{0}_{\text{phys}}\left(t\right) \to f\right) - \Gamma\left(\bar{B}^{0}_{\text{phys}}\left(t\right) \to f\right)}{\Gamma\left(B^{0}_{\text{phys}}\left(t\right) \to f\right) + \Gamma\left(\bar{B}^{0}_{\text{phys}}\left(t\right) \to f\right)} = \sin\left(2\phi_{1}\right)\sin\left(\Delta m\Delta t\right) \quad , \qquad (1.7)$$

where  $B_{phys}^0$  and  $\bar{B}_{phys}^0$  are pure  $B^0$  and  $\bar{B}^0$  mesons at t = 0, f denotes a final decay state,  $\Delta m = 0.463 \pm 0.018 \text{ ps}^{-1}$  is the  $B^0 - \bar{B}^0$  mass difference,  $\Delta t$  is the difference in decay time between the two and  $\phi_1^{\ 6}$  is one angle of the unitary triangle shown in fig. 1.3.

The goal is to observe  $B^0$  and  $\bar{B}^0$  decays that fit the conditions of eq. 1.7, measure  $\Delta t$ and determine the angle  $\phi_1$ . The required integrated luminosity for this measurement is estimated to be between 30 and 100 fb<sup>-1</sup> [4], which corresponds to the data of about  $30 \cdot 10^6$  to  $100 \cdot 10^6$  B-meson decays. At Belle the luminosity continuously increased since operation started in 1999 and reached the world's highest value of  $1.712 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> in November 2006. The decay time difference between  $B^0_{phys}$  and  $\bar{B}^0_{phys}$  is just about few

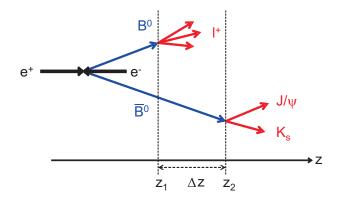

Figure 1.4.: Schematic depiction of a  $B^0\bar{B}^0$  event. At z1 the  $B^0$  decays into one hadron  $(l^+)$ and other particles, while at position z2 the  $\bar{B}^0$  decays into a  $(J/\Psi K_s)$  pair. The distance between those decay  $(\Delta z)$  is of interest at the Belle experiment.

picoseconds and thus cannot be measured directly. As mentioned in section 1.1, the KEKB produces copious B<sup>0</sup> and  $\bar{B}^0$  meson pairs from the  $\Upsilon(4S)$  resonance at a center of mass energy of 10.58 GeV. Moreover the collider works with asymmetric energies of 8 GeV and 3.5 GeV for electrons and positrons, respectively. This leads to B<sup>0</sup> $\bar{B}^0$  pairs with a boost factor  $\beta \gamma = 0.42$  and thus a center of mass moving in the labsystem. Hence the mesons decay at different locations in z direction<sup>7</sup>, depending on their lifetime. The distance  $\Delta z$  of the two decay vertex positions is related to  $\Delta t$  via

$$\Delta z = \beta \gamma c \,\Delta t \quad , \tag{1.8}$$

where  $\beta = \frac{v}{c}$ , v is the center of mass velocity, c the speed of light and  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$ .

<sup>&</sup>lt;sup>5</sup>The name Belle is derived from the French word for beauty. Without a B, Belle is reduced to the T-reversal-invariant palindronomic French pronoun elle.

<sup>&</sup>lt;sup>6</sup>Also named  $\beta$  in literature.

$<sup>^{7}</sup>z$  is the coordinate which coincides with the beam axis.

Since  $\Delta z$  is only about 200  $\mu$ m, it is required to use silicon strip detectors (see section 2.1) with a resolution of less than 100  $\mu$ m for an accurate measurement. Fig. 1.4 illustrates an e<sup>+</sup>e<sup>-</sup> collision where  $\Delta z$  is the interesting distance between the decay vertices of the B<sup>0</sup> and  $\bar{B}^0$  mesons.

The B physics of Belle is not only restricted to the measurement of the angle  $\phi_1$ , also various other parameters of the unitary triangle and thus the CKM matrix are of interest. Further information about the work of the collaboration and publications of their results can be found at the project's web site [13].

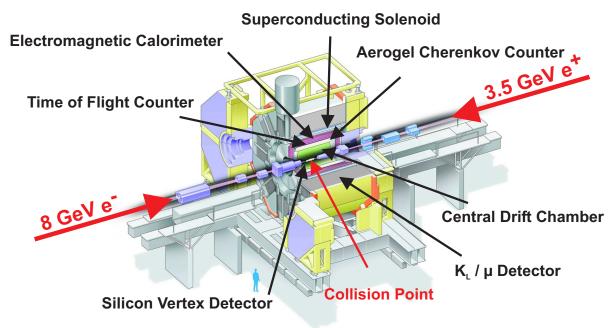

## 1.3. Belle Detector

The Belle detector is composed of various types of subdetectors which are arranged cylindrically around the beam pipe at the interaction point in the Tsukuba hall. A cross section of the detector is shown in fig. 1.5. From inside to outside those subdetectors are the Silicon Vertex Detector (SVD), the Central Drift Chamber (CDC), the Aerogel Cherenkov Counter (ACC), the Time-of-Flight counters (TOF), the Electromagnetic Calorimeter (ECL), surrounded by the superconducting solenoid and the  $K_L^0$  Meson and Muon detector (KLM) [14]. The whole detector has an octagonal-prism shape with a circumference and a length both about 8m. In the Belle experiment, a cylindrical coordinate system is used to appoint any position inside the detector. The z axis is defined in the direction of the electron beam and the r- $\phi$  plane is orthogonal to this axis. All subdetectors are designed to cover a  $\theta$  region extending from 17° to 150°, where  $\theta$  is the polar angle relative to the z-axis with the interaction point as the origin.

Figure 1.5.: Cross section of the Belle detector.

#### 1.3.1. Silicon Vertex Detector

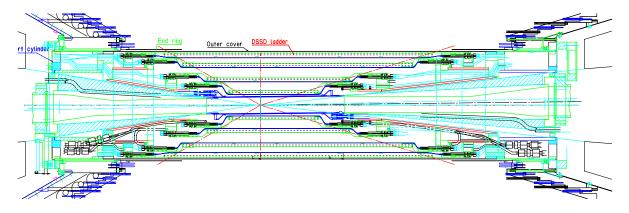

The SVD is the innermost system of the Belle detector and currently consists of four layers of double-sided silicon sensors which are described in sections 2.1 and 2.2 in detail.

It is used to measure the vertices of the two B meson decays (see 1.2) with a position resolution of less than 100  $\mu$ m and it also plays an important role for track reconstruction. A more detailed description of the SVD design is given in section 3.

#### 1.3.2. Central Drift Chamber

The Central Drift Chamber<sup>8</sup> (CDC) is intended to measure the tracks left by charged particles and to determine their momenta as well as the sign of their charge. It consists of 50 cylindrical layers and a total number of 8400 drift cells. The length of the CDC is 2400 mm and its inner and outer radii are 83 and 874 mm, respectively. A mixture of 50% helium and 50% ethane, with a radiation length of about 640 m and a drift velocity that saturates at 4 cm/ $\mu$ s is used. The sense wires are made of gold-plated tungsten with 30  $\mu$ m diameter. These sense wires are surrounded by 126  $\mu$ m thick aluminum field wires to produce a proper electrical field. Overall there are 8400 readout channels and 24944 field wires installed.

The CDC provides a position resolution of few millimeters in z and about  $130\mu$ m in r- $\phi$  direction and its momentum resolution is about  $0.19p_t \oplus 0.30/\beta \%$  [15], where  $p_t$  denotes the traverse momentum. Furthermore, the particle tracks found by the CDC are extrapolated inwards to the SVD where they are used as a starting point to determine the vertices of the B meson decays.

#### 1.3.3. Silica-Aerogel Cherenkov Counter (ACC)

The ACC is placed around the CDC and is used for particle identification, in particular to distinguish between pions and kaons. A Cherenkov detector is a particle detector which utilizes the effect of the mass-dependent threshold energy of Cherenkov radiation. Each material has its specific velocity of propagation of light, which is always significantly lower than the speed of light in vacuum c. Cherenkov radiation is emitted, when a charged particle passes through a material at a velocity exceeding the speed of light in that medium. This radiated light is transformed into an electrical signal and amplified by photomultiplier tubes, which are attached to the aerogel modules. For the Belle ACC aerogels with a refractive index between 1.01 and 1.028 where chosen so that pions emit Cherenkov light, while kaons stay below the threshold. The covered momentum range of identified particles is between 1.2 GeV/c and 3.5 GeV/c [16]. The ACC is composed of two parts, the barrel and the forward endcap. The barrel consists of 960 counter modules, segmented into 60 cells in  $\phi$  direction. The endcap is arranged in five concentric layers with a total of 228 counter modules.

#### 1.3.4. Time-of-Flight Counters (TOF)

The TOF is composed of 128 plastic scintillaters read out by 256 photomultipliers tubes. It is used to identify particle types by measuring their velocity. Therefore the detector

<sup>&</sup>lt;sup>8</sup>In a drift chamber many parallel wires (sense wires) are arranged as a grid and put on high voltage, with the metal casing or field forming wires being on ground potential. The chamber is filled with gas and a particle traversing it leaves a trace of ions and electrons, which drift toward the nearest sense or field wires, respectively. By labeling the wires with a current signal it is possible to measure the track of the traversing particle. In a drift chamber also the timing of the pulse and thus the drift time of the charges is measured, which improves the resolution within the cell.

determines the time of flight of these particles from the collision point to the counter with an accuracy of about 100 ps. In addition to particle identification the TOF also provides fast timing signals for the trigger system to generate gate signals for other subsystems like the CDC or the SVD.

#### 1.3.5. Electromagnetic Calorimeter (ECL)

The ECL is intended to detect photons from B meson decays with high efficiency and good resolution in energy and position. It consists of a highly segmented array of thallium-doped cesium iodide crystals (CsI(Tl)). When a charged particle enters the calorimeter its whole energy is deposited in the crystals whereby light is emitted. The intensity of this emitted light is measured with photodiodes.

Most of the particles that should be detected are products of cascade decays and thus have relatively low energy, hence the ECL is designed to have a good performance below 500 MeV [17].

#### 1.3.6. Kaon and Muon Detection System (KLM)

The KLM is the outermost subsystem of the Belle detector. It is designated to detect muons, which penetrate through most materials, and  $K_L^0$  mesons, which are electrically neutral and thus are not seen by any other subsystem. It consists of alternating layers of charged particle detectors and 4.7 cm thick iron plates. Glass-electrode-resistive plate counters (RPCs) are used for the charged particle detectors. Those are two parallel plate electrodes with high bulk resistivity ( $\geq 10^{10} \Omega$ ) separated by a gas-filled gap. An ionizing particle initiates a local discharge of these plates, which is limited by the high resistivity of the plates. The location and the time of this local ionization is detected by external pickup strips.

The neutral kaons, as well as the muons, interact with the iron plates and initiate a local shower of ionizing particles, which are detected by the sensitive planes. The multiple layers of charged particle detectors and iron allow the discrimination between muons and kaons, since muons travel much farther than kaons [14].

#### 1.3.7. Superconducting Solenoid

The superconducting solenoid provides a homogeneous magnetic field of 1.5 T in the central volume of the Belle detector which is about 3.4 m in diameter and 4 m in length. All subdetectors are located inside this magnetic field except the KLM which is integrated into the iron structure of the solenoid, providing the return path of the magnetic flux as well as the overall support for the detector components. It consists of a fixed barrel part, which includes the plates of the KLM and two movable end-caps to allow access to the inner components of the detector for maintenance. The coil wire is made of a superconducting alloy of Niobium-Titanium. It is operated in a superconducting condition, cooled down to 5 K using liquid helium.

The magnetic field is used to determine the momentum of charged particles from the bending of their trajectories as well as to minimize the background of low energetic charged particles, which are also produced by the collisions but are not of interest.

# 2. Silicon Detectors and Readout

In high energy physics several types of particle detectors are commonly used. A very important family are the so called ionization detectors, which utilize the ionizing effect when charged particles traverse matter. One type of this concept is gaseous ionization like drift chambers, proportional counters and Geiger-Müller tubes, which were most widely used in the 1970s. Nowadays, they are often superseded by the more sophisticated semiconductor detectors. The main base material of such sensors is silicon, but germanium and diamond are also used in specific applications. An advantage of silicon microstrip sensors is that the well known technology of integrated circuit production provides the ability to manufacture high-density micron-scale electrodes on large wafers, offering an excellent position resolution. Furthermore the low ionization energy of silicon results in sufficient signals with active layers of typically 300  $\mu$ m thickness.

In this chapter the design and the basic functionality of silicon particle sensors are discussed. Furthermore an overview about the components of the readout electronics for such detectors is given.

### 2.1. Silicon Detector

#### 2.1.1. Energy Loss

When a charged particle traverses a solid state detector it loses energy due to the generation of free electron-hole pairs. This energy loss is described by an equation published by H.A.Bethe and F.Bloch [10], hence also known as Bethe-Bloch equation.

$$-\frac{1}{\rho}\frac{dE}{dx} = Kz^{2}\frac{Z}{A}\frac{1}{\beta^{2}}\left[\frac{1}{2}\ln\frac{2m_{e}c^{2}\beta^{2}\gamma^{2}T_{\max}}{I^{2}} - \beta^{2} - \frac{\delta\left(\beta\gamma\right)}{2} - \frac{C}{Z}\right]$$

(2.1)

Eq. 2.1 represents the differential energy loss per mass surface density in units of  $[\text{MeV} (\text{g cm}^{-2})^{-1}]$ , where  $K = 4\pi N_A r_e^2 m_e c^2$ ,  $N_A$  is Avogadro's number, Z and A are the atomic number and the atomic mass of the traversed material,  $r_e$  is the classical electron radius  $\left(\frac{e^2}{4\pi\epsilon_0 m_e c^2}\right)$  and  $m_e$  its mass, ze is the charge of the incident particle,  $T_{\text{max}}$  is the maximum kinetic energy which can be imparted to a free electron in a single collision, I is the mean excitation energy,  $\beta = v/c$  and  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$ . In comparison to the original Bethe-Bloch formula which describes the energy loss of particles traversing gases eq. 2.1 includes two additional terms.  $\delta(\beta\gamma)$  is a correction for the shielding of the particle's electric field by the atomic electrons, the density effect caused by atomic polarization. The second correction term C considers that the basic assumption of atomic electrons is violated at very low incident particle energies.

Anyway, in thin layers like silicon detectors with a typical thickness of 300  $\mu$ m a fraction of the lost energy is carried off by high energetic knock-on or  $\delta$  electrons, which have enough energy to produce, themselves, additional electron-hole pairs while traversing the

medium (secondary ionization). These considerations lead to the restricted energy loss, which is expressed by an additional term in the Bethe-Bloch equation [18],

$$-\frac{1}{\rho}\frac{dE}{dx} = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[\frac{1}{2}\ln\frac{2m_e c^2 \beta^2 \gamma^2 T_{\text{upper}}}{I^2} - \beta^2 \left(1 + \frac{T_{\text{upper}}}{T_{\text{max}}}\right) - \frac{\delta\left(\beta\gamma\right)}{2} - \frac{C}{Z}\right] \quad (2.2)$$

where

$$T_{\rm upper} = \min\left(T_{\rm cut}, T_{\rm max}\right) \tag{2.3}$$

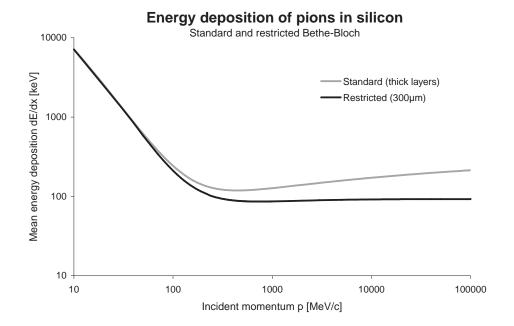

with  $T_{\rm cut}$  depending on the material and the incident particle momentum. Fig. 2.1 shows the comparison of the Bethe-Bloch equation to the restricted form for a pion traversing 300  $\mu$ m of silicon. There is no difference between the standard and the restricted form

Figure 2.1.: Comparison of the standard Bethe-Bloch equation to the restricted form for a pion traversing  $300 \,\mu\text{m}$  of silicon [18].

at low energies, because in this region the production of  $\delta$  electrons is very unlikely. However, at momenta higher than 100 MeV/c a significant deviation of the curves is evident. The relativistic rise of the restricted form is quite flat because energy is carried off by  $\delta$  electrons. Furthermore the energies of a minimum ionizing particle (MIP), that match the minima of each curve, are different. They are about 450 MeV/c for the original equation and 750 MeV/c for the restricted version, respectively.

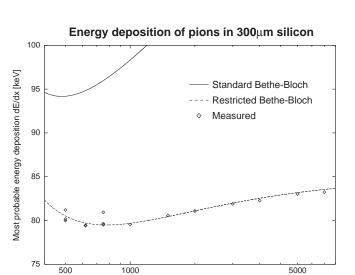

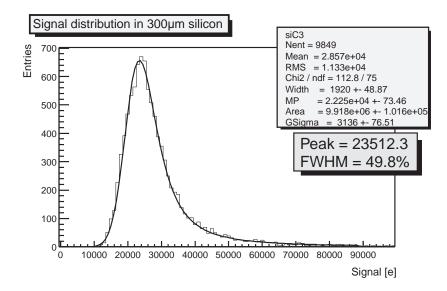

In practice, the model of the restricted energy loss has been confirmed by countless experiments and beam tests with silicon sensors. One example is shown in fig. 2.2 for pions in a silicon detector of  $300 \,\mu\text{m}$  thickness where an excellent match of the measured data and the restricted model is obvious.

#### 2.1.2. Charge Collection

As described in the last section, the energy deposition of a traversing particle in a detector material leads to the production of free electron-hole pairs. Without any electric field these carriers will recombine after a while. To move this carriers out of the sensor

# Figure 2.2.: Restricted model of energy loss of pions in a silicon detector of $300 \,\mu\text{m}$ thickness, compared to the measured most probable value and the standard Bethe-Bloch theory [18].

Incident momentum p [MeV/c]

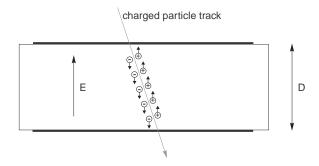

and thus being able to measure them, an electric field is necessary between two electrodes which are placed on the surface of the detector. Fig. 2.3 shows the principle configuration of such a detector with opposite electrodes.

Figure 2.3.: The electric field between two electrodes drains the electron-hole pairs, which are created along the track of a traversing particle [18].

The number n of carrier pairs is given by the quotient of the total energy loss  $E_{\text{loss}}$  of the incident particle and the ionization energy  $E_{eh}$ , which is required for the pair production,

$$n = \frac{E_{\text{loss}}}{E_{eh}}.$$

(2.4)

Due to  $E_{eh} = 3.6 \text{ eV}$  in silicon, the most probable charge for a MIP in a standard silicon sensor with a thickness of 300  $\mu$ m is about n = 22500 pairs. The measured energy loss of MIPs for such a detector is subjected to statistical fluctuations which are described by the convolution of a Gauss and a Landau distribution. The typical shape of such a distribution is shown in fig 2.4 in terms of the collected charge. An important property of the Landau distribution is its asymmetric form, caused by the long upper tail which is a result of the rare but high energetic  $\delta$  electrons. An ideal Landau distribution has a range that extends to infinite energies, but due to limitation of the measurement the

Figure 2.4.: Measured MIP signal distribution in a silicon detector of  $300 \,\mu\text{m}$  thickness [18].

curve is always truncated in real systems. The edges are given by the pedestal threshold for the lower one and the dynamic range of the readout electronics for the upper one, respectively. As a result of the asymmetry, the mean energy loss is typically about 1.2 to 1.3 times higher [19] than the most probable (MP) charge, which is represented by the peak of the distribution. Moreover the MP signal can be obtained more accurate from a measured distribution than the mean value, because cuts on either end of the curve only affect the mean, but not the MP.

The electric field between the electrodes causes the carriers to move according to

$$v = \mu E \quad , \tag{2.5}$$

where is v is the mean carrier drift velocity,  $\mu$  the carrier mobility and E the electric field. The mobilities and also the drift velocities of electrons and holes are different and depend on the material. The linear relation of eq. 2.5 is only valid for weak electric fields. At high field strength the increasing number of collisions between the carriers and the crystal lattice has to be considered, which results in a saturation of the average drift velocity. Empirical functions describing both linear and saturation ranges for silicon are given by eq. 2.6 and eq. 2.7 for electrons and holes, respectively [20].

$$v_e = \frac{\mu_e E}{\sqrt{1 + \left(\frac{\mu_e E}{v_{e, \text{sat}}}\right)^2}} \tag{2.6}$$

$$v_h = \frac{\mu_h E}{1 + \frac{\mu_h E}{v_{h, \text{sat}}}} \tag{2.7}$$

The saturation velocities  $v_{e,sat}$  and  $v_{h,sat}$  used in these equations are in the order of  $10^7 \text{ cm/s}$ , corresponding to an electric field in the order of  $10^5 \text{ V/m}$ .

Because of the moving charges inside the detector material a current is induced in the electrodes, no matter whether the carriers finally reach the electrodes or not. This current i is caused by both electrons and holes and is proportional to the sum of all carrier velocities as shown in eq. 2.8

$$i = \frac{q_e}{D} \left( \sum v_e + \sum v_h \right) \qquad , \tag{2.8}$$

where  $q_e$  is the elementary charge and D the sensor thickness [21]. The total collected charge  $Q_c$ , which is usually measured with integrating amplifiers, results from the integration of i using

$$Q_c = \frac{q_e}{D} \int \left( \sum v_e + \sum v_h \right) dt \quad . \tag{2.9}$$

The generated electrons move to the positive electrode while the holes move to the negative electrode. This means that if no charges are trapped, the total travel distance of each pair equals the thickness of the sensor. With  $v = \frac{ds}{dt}$  the integral term in eq. 2.9 results to nD and thus the total collected charge is obviously

$$Q_c = n e \quad . \tag{2.10}$$

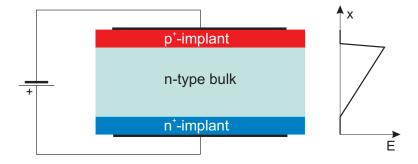

In pure silicon, the number of thermally created carriers is many order of magnitude higher than the charge produced by a MIP. This means that it is impossible to use silicon as a detector material in this way. The charge collection area has to be depleted from these intrinsic carriers, which can be achieved by a reverse-biased pn-junction. Therefore on one surface of a homogeneously doped silicon a thin layer with high doping concentration of the other type is applied. Fig. 2.5 shows the principal layout of a silicon detector based on n-type bulk. The highly doped  $n^+$ -implant on the second surface is known as backplane and creates an Ohmic contact to the electrode.

Figure 2.5.: Schematic cross-section of a silicon detector with n-type bulk. The implantation zones are shown much thicker than they are in reality. The electric field to the right is shown at the depletion voltage.

With increasing reverse bias voltage a zone without free carriers, the depletion zone, grows from the pn-junction toward the electrodes. It reaches the electrodes when the bulk is totally depleted at the so called depletion voltage  $V_{depl}$ . At this state only the core excess charges of donors and acceptors remain and the charge densities of bulk ( $\rho_d$ ) and the p<sup>+</sup> implant ( $\rho_a$ ) are

$$\rho_{\rm d} = e N_{\rm d} \quad \text{and} \quad \rho_{\rm a} = -e N_{\rm a} \quad ,$$

(2.11)

where  $N_{\rm d}$  is the density of donors and  $N_{\rm a}$  of acceptors, respectively. The charge density is constant over the full width of the bulk and the charges are

$$Q_{\rm d} = d_{\rm d} \,\rho_{\rm d} \quad \text{and} \quad Q_{\rm a} = d_{\rm a} \,\rho_{\rm a} \quad ,$$

(2.12)

where  $d_{\rm d}$  and  $d_{\rm a}$  are the width of the space charge areas. At equilibrium, the global charge has to be balanced  $(Q_{\rm d} + Q_{\rm a} = 0)$  and  $d_{\rm a}$  can be expressed by

$$d_{\rm a} = d_{\rm d} \frac{N_{\rm d}}{N_{\rm a}} \quad . \tag{2.13}$$

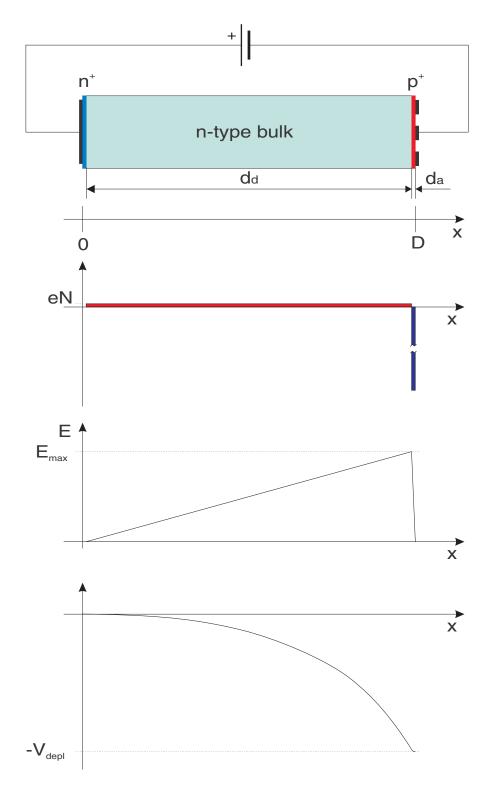

Figure 2.6.: Charge density, electric field and potential of a simplified model of a silicon detector at full depletion [18].

The relation between the charge density  $\rho$  and the electrical field strength is given by the one-dimensional Poisson equation

$$\frac{dE}{dx} = \frac{\rho}{\epsilon} \quad , \tag{2.14}$$

with the dielectric constant  $\epsilon$ . Integration of the Poisson equation leads to an electric field of triangular shape as shown in fig. 2.6. It starts from zero at the backplane, rises to its maximum

$$E_{\rm max} = \frac{\rho_{\rm d}}{\epsilon} d_{\rm d} = \frac{\rho_{\rm a}}{\epsilon} d_{\rm a} \tag{2.15}$$

at the pn-junction and quickly falls down to zero again in the p<sup>+</sup> implant. The electric potential  $\varphi$  is defined by

$$\varphi = -\int E \, dx \tag{2.16}$$

and the difference of the potential at the electrodes is the voltage V applied to the sensor. By using above equations and considering that the the p<sup>+</sup> and n<sup>+</sup> regions are very thin and thus can be neglected compared to the bulk thickness ( $d_{\rm a} \ll d_{\rm d}$  and  $d_{\rm d} \approx D$ ), the depletion voltage becomes

$$V_{\rm depl} = \frac{eN_{\rm bulk}D}{2\epsilon} \tag{2.17}$$

with  $N_{\text{bulk}} = N_{\text{d}}$ . As described before, the electrical field extends over the whole bulk and is of triangular shape in case of full depletion ( $V_{\text{bias}} = V_{\text{depl}}$ ). A bias voltage higher than  $V_{\text{depl}}$  adds an additional but constant offset to the field, which results in an approximately constant field at very high voltages ( $V_{\text{bias}} \gg V_{\text{depl}}$ ). On the other hand, when the supplied voltage is below the depletion voltage, the field still is triangular with its maximum at the junction, but it does not reach the edges and only a part of the bulk is depleted. This leads to an inefficient charge collection with an active collection distance given by

$$d_c = D_{\sqrt{\frac{V_{\text{bias}}}{V_{\text{depl}}}}} \quad . \tag{2.18}$$

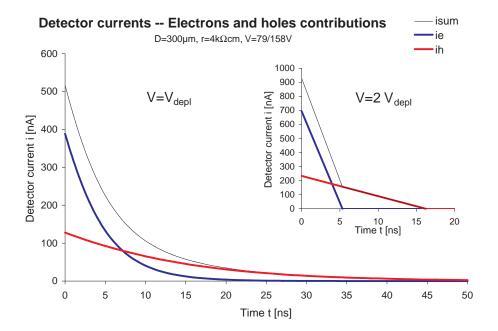

In a fully depleted silicon detector all carriers induced by a traversing particle move towards the electrodes due to the electrical field where they are drained until all charges are gone. As shown in eq. 2.5 the mobilities of electrons and holes are different, thus the resulting current is a superposition of two pulses with different slope, but equal area as shown in fig. 2.7. At  $V_{\text{bias}} = V_{\text{depl}}$  the shape of both currents is exponential, but it becomes more and more linear with increasing bias voltage. A more detailed discussion about the detector currents can be found in [18, 22].

Figure 2.7.: Shape of the electron and hole currents in a standard silicon detector with a thickness of 300  $\mu$ m at depletion voltage and at ( $V = 2V_{depl}$ )) [22].

### 2.2. Detector Design

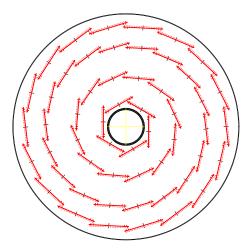

The main purpose of silicon detectors in High Energy Physics is to measure the track of particles which are for instance the result of colliding particle beams. Therefore several detectors are placed in multiple layers around the interaction point of the collider. A segmented design of the electrodes is essential to achieve spatial information from silicon sensors. The two commonly used layouts are strips and pixels.

#### 2.2.1. Strip Detectors

On strip detectors at least one of the electrode surfaces is made up of long thin lines with a typical spacing between 50  $\mu$ m and 250  $\mu$ m, while the second is either segmented in orthogonal direction or made of a single plate covering the entire sensor (backplane). The distance between two strips is also known as pitch and is an important parameter for the spatial resolution. The size of such sensors is primarily limited by the dimension of the silicon wafer from which they are cut out. Today wafers with a diameter of 4" or 6" are used and thus sensors of up to  $10 \times 10$  cm<sup>2</sup> can be produced in a single piece. For larger detectors, two or more strip detectors have to be electrically and mechanically ganged to enlarge the total strip length. The outer layers of the Belle detector (see section 3), as an example, use up to three daisy-chained sensors.

As the signals of the sensors are very small, special readout chips with integrated low-noise amplifiers (see section 2.3.1) are used for signal processing. The common electromechanical technique for the connection between sensor and amplifier chips is wire bonding<sup>1</sup>. In general the pitch of the sensors strips is not equal to the bonding pad spacing on the readout chip and a so called pitch adapter has to be placed between

<sup>&</sup>lt;sup>1</sup>Wire bonding is a method to make an interconnection between microchips and other electronics using thin wires with a diameter of typically 25  $\mu$ m. This is done with a special machine (bonding station) by welding the wire onto the contacts with ultrasonic power.

them.

Usually, each strip of a detector is connected to a separate channel of the front-end chip. Sometimes only every second strip is read out and the remaining are terminated with high impedance. Such strips are called intermediate strips. Signals on these intermediate strips are partially transferred to the readout strips by capacitive coupling. This method has the advantage that the number of amplifier channels can be reduced. The performance of such a sensor is worse than with full readout, but still better than without intermediate strips [23].

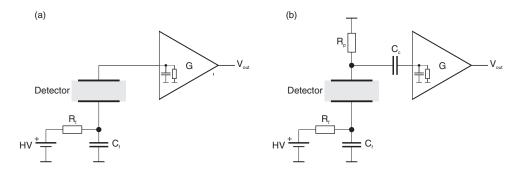

Figure 2.8.: The two possible connection scheme for a single channel of a silicon strip detector: DC coupling (a) and AC coupling (b) [18].

From the electrical point of view there a two possible coupling methods. The first one is to join each strip directly with its corresponding amplifier input (DC coupling). In that case the signal and also a fraction of the leakage current flows into the amplifier. Depending on the applied bias voltage, the sensor geometry and the radiation damage this leakage current varies in a wide range and can be higher than the signal itself. It is difficult to build amplifiers that are able to handle such a large range of input currents. The second method is to place a capacitance between the strip and the amplifier input and to bypass the DC leakage current over a resistor. Then only the AC part of the signal is seen by the readout chip and it does not have to provide a wide input range. Today, AC coupling is the preferred technique for silicon detectors. Fig. 2.8 shows the two possible coupling schemes of a single channel of a silicon detector.

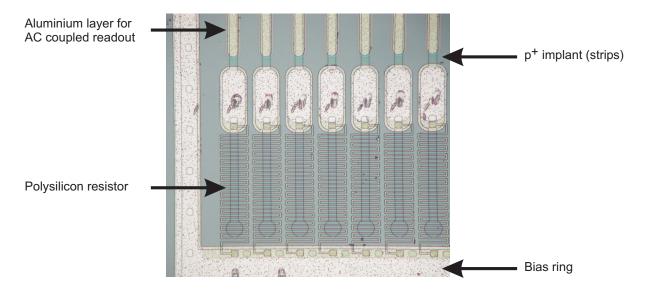

Normally, the coupling capacitor is implemented by an additional aluminum layer on the top of the sensor. A thin silicon oxide film between the strips and the aluminum provides the required isolation. The implementation of the bias resistor is typically done by a polysilicon meander structure. Fig. 2.9 shows a magnified view of a such a silicon strip detector with n substrate and  $p^+$  implants (strips), where the meander of the polysilicon is clearly displayed. In case of AC coupling all polysilicon resistors are connected to a common bias ring, so that the bias voltage can easily be applied to the sensor with a single contact. Furthermore a, RC filter is normally foreseen to decouple the bias voltage and thus reduce the noise.

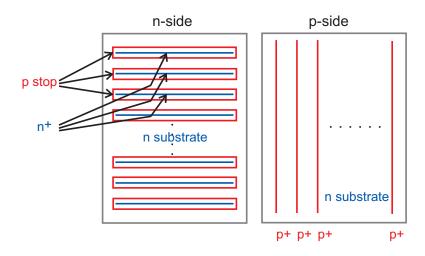

Sensors which have a single backplane also called single-sided, because only one electrode is made up of thin lines and thus just a single coordinate can be measured. In order to get more information, one possibility is to design both electrodes as thin lines but with orthogonal orientation. Such sensors are called double-sided strip detectors (DSSD). The layout of the electrode of the second side is more complicated, because the strips have the same doping as the substrate and would be shorted without any additional measures. Nowadays, n doped silicon is commonly used as substrate for sil-

Figure 2.9.: Magnified part of a silicon strip detector with n substrate, p<sup>+</sup> implants and an aluminum layer for AC coupled readout.

Figure 2.10.: Layout scheme of a DSSD based on a n-doped substrate with n<sup>+</sup> readout strips and atoll type p stops on n-side and p<sup>+</sup> readout strips on p-side, respectively.

icon strip detectors. In that case the design of the electrodes which are made up of  $p^+$  implants is very easy, because the strips are automatically isolated against each other by the substrate. However, on the second side the electrodes are of  $n^+$  doped silicon and additional  $p^+$  implants, so-called p stops, are required between the strips to avoid short circuits. A typical strip layout of such a DSSD using so-called atoll type p stops, where each  $n^+$  strip is surrounded by a floating p atoll, is displayed in fig. 2.10. Various p-stop types are compared in [24]. It was shown, that the atoll type has a lower interstrip capacitance and detector noise at the cost of slight charge losses.

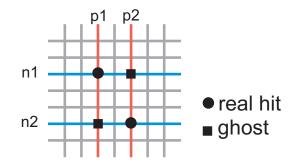

Such double sided sensors provide two-dimensional information, which may be ambiguous in case of two or more particles traversing the sensitive area at the same time. Assumed that there is just a single hit, only one or a small group of neighboring strips, which is also called a cluster, on each side carry a signal from this event. As the strips on both sides are orthogonal, the traversing point can be extracted from the crossing of the involved channels. Fig. 2.11 illustrates the situation when two particles traverse the

Figure 2.11.: Ambiguous hit positions in case that two particles traverse a DSSD.

detector at the same time. Then there are two real hits at positions p1/n1 and p2/n2, respectively, which lead to a signal on those four strips. Trying to reconstruct the real hits from the strip information is ambiguous: In addition to the real hit points, there are two more possible hits at the crossing of p1/n2 and p2/n1, commonly named ghosts. The true hit points have to be reconstructed by combinatorics using data from several layers of silicon detectors.

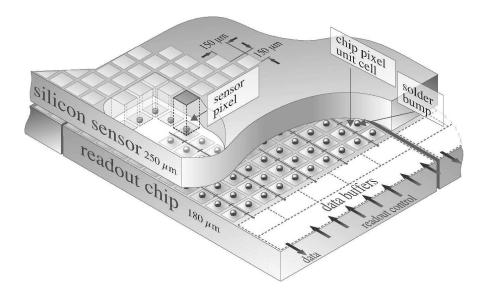

#### 2.2.2. Pixel Detector

One electrode can be divided into square pads with a dimension of about  $50 \times 50 \,\mu\text{m}^2$  to achieve higher resolution and solve the ambiguity problem of DSSDs (see above). Such pads are called pixels and the charge is collected at the pixel where the particle traverses the sensor. A pixel detector provides a two dimensional hit information, even though the second electrode is manufactured as a common backplane as it is done on single sided strip detectors. The advantage of such a sensor is that it allows a very accurate determination of the hit position at the cost of a complicated structure. In contrast to strip detectors the connection between the pixels and their corresponding amplifier inputs cannot be done by wire bonding, because the pads are distributed in a twodimensional array and wire bonding is restricted to only one dimension. One solution is to route all pads to a single row of bonding pads on one edge of the sensor, but this is only suitable for sensors with large pixels and it reduces the signal quality. The more sophisticated method is to place the readout chip directly onto the sensor in a sandwichlike compound as shown in fig. 2.12. An advanced bonding method called bump bonding is used to connect the pixels with the input channels of the amplifier. Thereby small solder bumps, which are for instance made of Indium, are deposited onto the pads, then parts are brought together and treated thermally. This method was recently used and enhanced by the Paul Scherer Institut (PSI), Villigen, Switzerland, for the production of the CMS<sup>2</sup> pixel detector modules with a pixel size of  $100 \times 150 \mu m$ . A detailed description of this technique can be found in [26, 27]. As this is a very complicated technique one may ask why the amplifier is not be integrated onto the same wafer as the sensor, because both are made of silicon? The reason is that the requirements in doping concentration, purity and operating voltage for silicon detecors and electronic circuits are quite different. However, the research on such detectors is in progress and a promising candidate is the Monolitic Active Pixel Sensor (MAPS) [28, 29]. Conventional

<sup>&</sup>lt;sup>2</sup>The Compact Muon Solenoid (CMS) experiment is one of two large general-purpose particle physics detectors being built at the proton-proton Large Hadron Collider (LHC) at CERN in Switzerland.

Figure 2.12.: Sketch of a pixel detector, bump-bonded onto the readout chip [25].

detectors use high-resistivity silicon as active volume which is optimized for the charge collection efficiency, but require a dedicated fabrication process. In case of the MAPS a lightly doped undepleted epitaxial layer is used for charge collection and thus those chips can be manufactured using a standard, cost-effective and easily available CMOS process, integrating the readout chip on the same wafer.

## 2.3. Readout Electronics

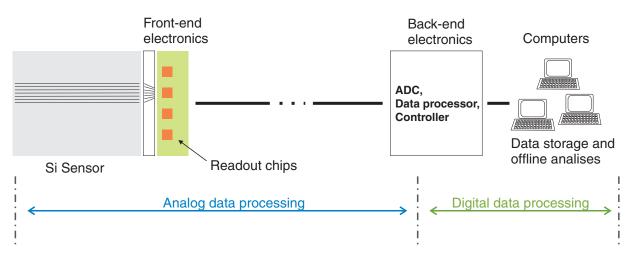

A MIP traversing a  $300\mu$ m thick silicon detector produces a most probable charge of about 22500 electrons, with a pulse duration of only few nanoseconds. Thus the signal has to be amplified before it can be transmitted and processed. As readout chips with an integrating preamplifier and a CR-RC shaper are used in most present silicon detector systems, this type will be described here. The structure of a typical readout system

Figure 2.13.: Basic scheme of a readout system for silicon detectors.

is shown in fig. 2.13. It usually consists of a front-end and a back-end part. The first one is always situated as close as possible to the sensor to minimize noise, thus inside the interaction region where high radiation may occur. Hence radiation hard design is required for all of its components. It commonly includes the readout chips, drivers and some control and monitoring devices, such as thermal and voltage sensors. The back-end is placed in some distance to the detector, mostly in a separate room. It is used to collect, digitize, preprocess and finally transmit the data of the readout chips to a computer or rather a computer farm where the data are stored for offline analysis. Depending on the speed and distance between those two subsystems the data transmission can either be done by conventional copper cables (with twisted pairs) or if necessary by more expensive and more sophisticated fiber optics.

#### 2.3.1. Front-End Electronics

The most important function of the front-end electronics is to amplify the sensor signal. Nowadays, detectors with a huge number of strips are used in high energy physics experiments, therefore amplifiers with high integration are required. Most present readout chips contain 128 input amplifier channels as well as sample/hold circuits, the dedicated control logic, sometimes also an analog pipeline storage for each channel and a multiplexed output stage. In most cases the output of the readout device is an analog sequence of the sampled signal of all channels, but some types also include a digitization circuit.

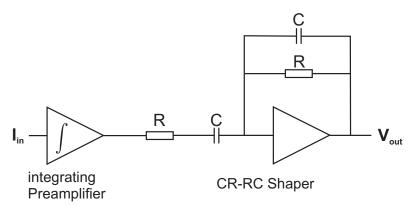

As semiconductor detectors provide a current signal the input of the amplifier has to be of low resistance. The actual shape of the current pulse depends on the applied bias voltage and is impossible to measure directly at room temperature due to noise. Anyway, it is more convenient to measure the integrated current which corresponds to the collected charge. Hence, the first stage of the amplifier is implemented as an integrator, followed by a special filter (shaper) in the second stage to reduce the noise and form the pulse to a defined shape. Fig. 2.14 shows the scheme of such an amplifier

Figure 2.14.: Typical amplifier scheme for silicon detector readout with a integrating preamplifier followed by a CR-RC shaper.

composed of a integrating preamplifier together with a CR-RC shaper, named after the components arranged around the amplifier. The basic function of the shaper is a combination of a high-pass and a low-pass filter which leads to a semi-Gaussian output signal. When equal resistors and capacitances are used the system has only one time constant  $T_p = RC$ . In that case the transfer function in the Laplace domain is given by

$$\frac{V_{out}(s)}{I_{in}(s)} = \frac{AT_p}{(1+sT_p)^2}$$

(2.19)

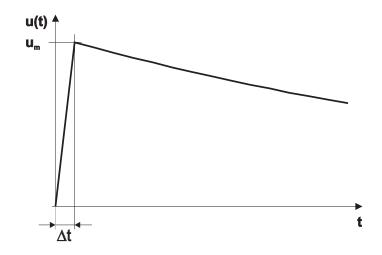

with the factor A determined by the preamplifier.  $T_p$  is called shaping time which extends from 25 ns to 10  $\mu$ s, depending on the application. Since the current pulse of a silicon detector is always much shorter than  $T_p$  it can be approximated by a Dirac- $\delta$ pulse weighted with the collected charge  $Q_c$ . Using eq. 2.19 the amplifier response to such an input signal in the time domain is

$$v_{out}(t) = AQ_c \frac{t}{T_p} e^{-\frac{t}{T_p}} \quad .$$

(2.20)

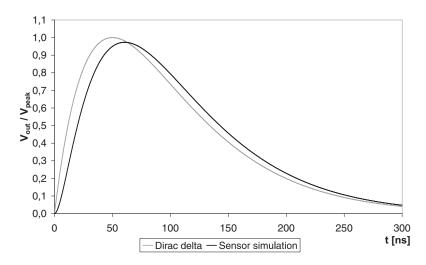

In fig. 2.15 the shaper output voltage resulting from a Dirac- $\delta$  pulse is compared to the one obtained by a simulation of the actual silicon detector signal (see fig. 2.7) [22]. Because the absolute voltage depends on the gain of the preamplifier both curves are normalized to the peak voltage  $V_{peak}$  of the Dirac- $\delta$  answer. One noticeable difference between the two curves is that the Dirac- $\delta$  answer reaches its maximum at  $t = T_p$ , also called "peaking time", while the signal coming from the sensor simulation is slightly delayed.

Figure 2.15.: Shaper output ( $T_p = 50$ ns) with a signal coming from a silicon detector (simulation) and a ideal Dirac- $\delta$  pulse [18].

#### 2.3.2. Back-End Electronics

The back-end electronics is the second stage in the data processing chain of the detector readout system. Its primary purpose is to collect and (pre)process the data of the frontend units before they are sent to the final storage devices, but it also has to take care of the required control signals such as clock and trigger to ensure a synchronized readout of the amplifiers. In practice the silicon sensor is only one part of a High Energy Physics experiment, thus the back-end also needs interfaces to the global control and trigger systems.

Since the readout chips usually provide an analog output signal the back-end system includes one analog to digital converter (ADC) per readout chip. It further contains several amplifiers, FIFO<sup>3</sup> buffers and control electronics. Concerning the data flow,

<sup>&</sup>lt;sup>3</sup>FIFO is the abbreviation for first-in, first-out and describes the principle of a queue behavior. Data are always read from the output of a FIFO buffer in same order as they were written into its input before.

the back-end is the boundary between analog and digital data processing. State of the art back-end systems often contain programmable logical devices (FPGA<sup>4</sup>) which make them suitable to implement some advanced processing features like data compression and correction procedures. Furthermore, FPGAs have the advantage that it is possible to implement the same logic circuit many times with a minimum need of hardware and space. Thus, the data stream of many input channels can be handled in parallel, which is very important to ensure fast online data processing. The output of the back-end is then transmitted to a computer farm where high level processing is done before the data are stored for off line analyses.

### 2.4. Noise

Considering the noise is very essential in silicon strip detector applications since the signal is very low. Even though every electronic component in the data processing chain contributes to the total noise, the detector itself and the input transistor of the preamplifier are the most critical sources. The electronic noise of a silicon sensor systems is commonly given in terms of equivalent noise charge (ENC) referred to the amplifier input and thus directly related to the measured signal charge.

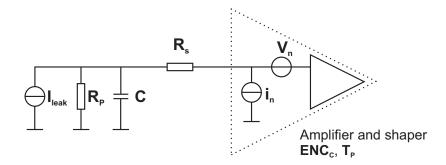

Figure 2.16.: Noise sources of a silicon stip sensor and its amlifier.

Fig. 2.16 displays all noise related components of a typical AC coupled silicon detector configuration with a polysilicon bias resistor. In this scheme the noise sources of the sensor are the fraction of the sensor's leakage current seen by one strip  $I_{leak}$ , the bias resistance  $R_p$  and the line resistance of the strip  $R_s$ . The influence of the AC coupling capacitance can be neglected. In a system with an integrating amplifier followed by a CR-RC shaper as it is described in section 2.3.1, the noise contributions of the sensor can be expressed by

$$ENC_{Ileak} = \frac{e}{2} \sqrt{\frac{I_{leak} T_p}{q_e}} , \qquad (2.21)$$

$$ENC_{Rp} = \frac{e}{q_e} \sqrt{\frac{kTT_p}{2R_P}}$$

and (2.22)

$$ENC_{Rs} = \frac{e}{q_e} C \sqrt{\frac{kT R_s}{6 T_P}}$$

(2.23)

<sup>&</sup>lt;sup>4</sup>A field-programmable gate array (FPGA) is a semiconductor device containing programmable logic components (logic blocks) and programmable interconnects. They allow to implement complex logical combinations. Many types also includes predefined memory blocks and advanced logic elements.

with ENC the number of electrons, the elementary charge  $q_e$ , the Euler number e, the Boltzmann constant k and the integration time  $T_p$  [30, 31]. The equations show that ENC<sub>Ileak</sub> and ENC<sub>Rp</sub> rise with increasing peaking time while ENC<sub>Rs</sub> behaves opposite.

However, the most important noise source is the input stage of the amplifier, which can be modeled by a voltage source in series and a current source in parallel to the input as shown in fig. 2.16. Due to the integrating preamplifier the parallel noise current  $i_n$  results in a constant value while the voltage source leads to a noise charge which increases with the capacitive load C of the input.

$$ENC_{C} = a + bC \quad , \tag{2.24}$$

Both a and b are parameters of the used amplifier and depend on its implementation. C represents the sum of the capacitive load present at the amplifier input. Often, the sensor is the dominant capacitive contribution, but sometimes long pitch adaptors or bond wires have to be considered, too, adding up to the total capacitance as seen by the amplifier.

As all contributions can be considered statistically independent and thus uncorrelated, the total noise is given by the square sum of them.

$$ENC = \sqrt{ENC_{Ileak}^2 + ENC_{Rs}^2 + ENC_{Rp}^2 + ENC_C^2}$$

(2.25)

To give an example for the order of magnitude of individual noise components they are calculated for the future Belle detector in combination with the APV25 readout chip as amplifier, which will be described later in section 5.1. In tab. 2.1 the basic parameters of the DSSD are listed for both p-side and n-side. The resulting noise contributions are shown in tab. 2.2. It can clearly be seen that the amplifier chip is the dominant noise source for both sides of the detector.

| Belle SVD3   | p-side      | n-side |      |

|--------------|-------------|--------|------|

| strip width  | $[\mu m]$   | 10     | 24   |

| strip length | [mm]        | 77.7   | 25.6 |

| pitch        | $[\mu m]$   | 51     | 152  |

| С            | [pF]        | 15.1   | 5.1  |

| $R_{S}$      | $[\Omega]$  | 110    | 15   |

| $R_P$        | $[M\Omega]$ | 10     | 10   |

| $I_{leak}$   | [nA]        | 0.86   | 0.86 |

Table 2.1.: Sensor parameters of the future Belle DSSD for both sides of the sensor.

On the p-side the line resistance  $R_s$ , which primarily depends on the length and the width of the strip metalization, is also a significant noise source. In comparison to the n-side the strips on the p-side are three times longer and only half as wide due to the narrow pitch. This results in a ENC<sub>RS</sub> which is considerably higher than the contributions of the other sources but still negligible compared to the noise caused by the amplifier input.

| Noise                           |     | p-side | n-side |

|---------------------------------|-----|--------|--------|

| ENC <sub>C</sub>                | [e] | 792    | 435    |

| $ENC_{RS}$                      | [e] | 163    | 60     |

| $ENC_{RP}$                      | [e] | 54     | 54     |

| $\mathrm{ENC}_{\mathrm{Ileak}}$ | [e] | 22     | 22     |

| ENC <sub>total</sub>            | [e] | 811    | 443    |

APV25:  $ENC_{C} = 250 + 36C$

Table 2.2.: Noise values resulting from the sensor parameters given in tab. 2.1 using the APV25 amplifier. The total noise in the bottom row is calculated using eq. 2.25.

# 3. Belle Silicon Vertex Detector

### 3.1. History

The initial version 1 of the Belle silicon vertex detector (SVD1) was installed in 1999 and was used for four years. It was composed of three cylindrical layers of 102 DSSDs in total and had a polar angle coverage of  $23^{\circ} < \theta < 138^{\circ}$ . The radii of the three layers were 30, 45.5 and 60.5 mm. Each layer was constructed from 8, 10 and 14 independent ladders with two, three and four DSSDs for the first, second and third layers, respectively. The sensors were manufactured by Hamamamatsu Photonics and had a sensitive area of  $57.5 \times 33.5 \text{ mm}^2$ , a thickness of 300  $\mu$ m and a pitch of 50  $\mu$ m in r- $\phi$  and 84  $\mu$ m in z direction [32]. There were 640 strips on each side which were read out by VA1 front-end chips produced by IDE AS, Norway. This chip was manufactured in a 1.2  $\mu$ m CMOS process and featured a limited radiation tolerance of about 200 krad. Since the actual radiation dose was higher than expected in the design stage, parts of the SVD1 and its readout chips had to be replaced repeatedly.

Another problem was the long dead time of about 128  $\mu$ s during the readout of the VA1 chips, because they were arranged in groups of five daisy-chained chips and read out serially using a single readout line.

Moreover the sensor bias voltage was separated from the grounded front-end electronics by the AC coupling capacitance of the sensor. This led to the loss of some ladders due to shorts created by pinholes on the sensor which broke down the AC coupling and caused the bias voltage being applied to the VA1 chip.

# 3.2. Current State

The SVD in operation is the SVD2, an improved design that addresses all the issues of SVD1. Its installation was in summer 2003 and since then it has been working without any serious problems. Not only the electrical components were upgraded, also the mechanical structure was revised to achieve a better vertex resolution and tracking efficiency.

#### 3.2.1. Silicon Sensors

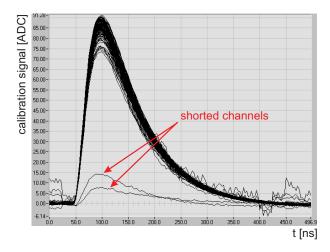

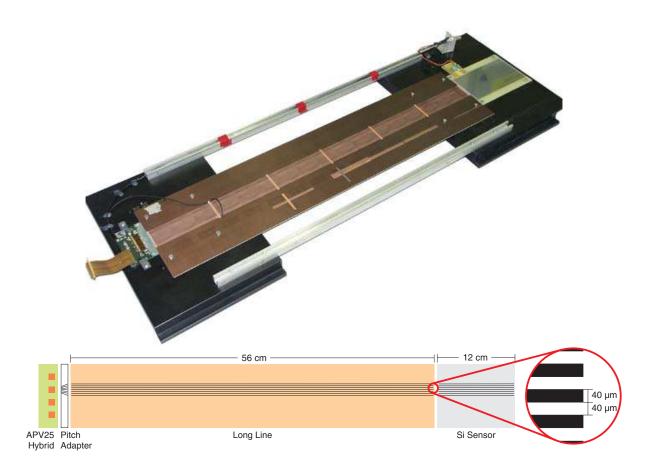

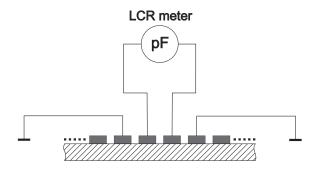

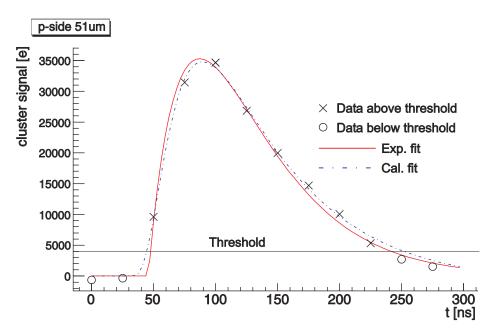

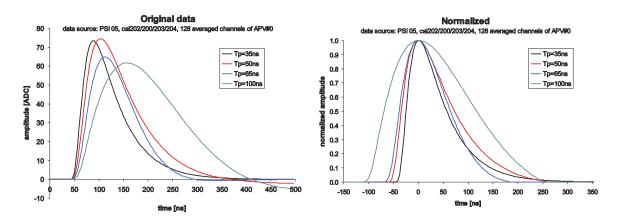

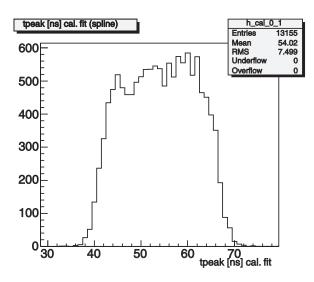

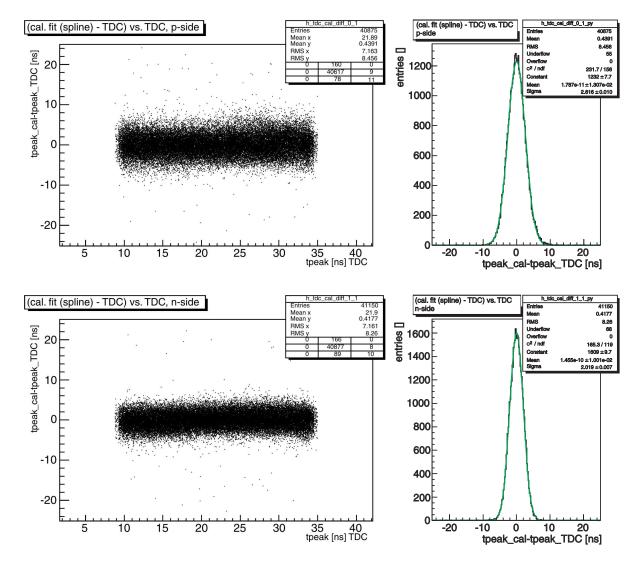

The SVD2 consists of 246 DSSDs arranged in four layers, read out by VA1TA chips (see 3.2.2), which permit an operation to at least 20 Mrad. Furthermore, the power scheme of the front-end chips was replaced by a floating one, where the VA1TA low voltage potential sits on the top of the bias voltage levels of the sensor connected with them. The voltage decoupling between front-end and back-end electronics and the translation of the signals are now performed by subsequent optocouplers. In this configuration only negligible current can flow into the input of the readout chip in case of a pinhole on the sensor. However this current is some order of magnitude higher than the signal