The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# High-κ/metal-gate devices for future CMOS technology

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften von

Dipl. Ing. Stephan Abermann

Mat.-Nr.: 9735151 Erdbergstrasse 116/51 1030 Wien

an der Technischen Universität Wien Fakultät für Elektronik und Informationstechnologie Institut für Festkörperelektronik, E 362

unter der Leitung von

O. Univ. Prof. Dr. Emmerich Bertagnolli

Wien, im Juni 2007

.....

I declare in the lieu of oath that I did this dissertation in hand by myself using only literature cited at the end of this volume.

Vienna, June 2007

.....

### Acknowledgement:

**O.** Univ. Prof. Dr. Emmerich Bertagnolli, for supervising, guiding, and reviewing this thesis. His boundless scientific- and administrative support, as well as human encouragement, are highly acknowledged.

**Ao. Univ. Prof. Dr. Christian Teichert** from the Institut für Physik, Montanuniversität Leoben, for reviewing this thesis, as well as for occupational- and personal relationship beyond "University-borders".

**Dr. Max Lemme**, **DI Johnson Efavi**, **DI Heiner Gottlob**, and **DI Mathias Schmidt** from AMO GmbH, Aachen, for *Joint processing*- and *characterization activities*, and for scientific support and cooperation.

**Dr. Gustaf Sjöblom** from Uppsala University, for *Joint processing*- and *characterization activities*, and for scientific support and cooperation.

**DI Christian Jordan** and **Dr. Michael Harasek** from the ICE, TU Wien, for simulation and modelling, and scientific cooperation.

**Dr. Wolfgang Brezna**, and **Ao. Univ. Prof. Dr. Jürgen Smoliner** for AFMmeasurements and scientific cooperation.

**Dr. Jan Kuzmik**, **Dott. Gianmauro Pozzovivo**, and **Dr. Sebastian Golka** for scientific support and cooperation.

**DI Markus Karner** from the IME, TU Wien, for computational simulation and scientific cooperation.

**Dr. Alois Lugstein** for scientific support, and even more for human encouragement.

Dr. Heinz Wanzenböck, Dr. Werner Schrenk, Ao. Prof. Dr. Gottried Strasser, and Ao. Prof. Dr. Gerhard Hobler for scientific support.

DI Markus Fischer for walking most of this way by my side, DI Christoph Schöndorfer for sitting by my side, and DI Mathias Steinmair, DI Andreas Steiger-Thirsfeld, DI Erwin Auer, DI Matthias Schramböck, DI Youn-Joo Hyun, DI Gottfried Hochleitner, Dipl.-Phys. Ole Bethge, and DI Stephan Müller for stopping by.

Silvia Pflug and Christine Brendt for administrative support, Ing. Elvira Dzigal, Ing. Erich Riegler, Ing. Peter Kröll, Helmut Schenold, Ing. Markus Schinnerl, and Ing. Johannes Prinzinger for technical assistance, as well as all other people at the FKE.

**Dr. Stefan Harasek** for scientific support, especially within the first months of this work.

**Dr. Johannes Bernardi** in representation for the USTEM, TU Wien, for TEMmeasurements, and **Christian Tomastik** from the IAP, TU Wien, for Augermeasurements.

**Everyone** that is not mentioned here explicitly, but still feels addressed by this acknowledgement.

### Abstract

For almost forty years technological progress and economic benefit drives the scaling of CMOS-technology. The use of silicon dioxide as the gate dielectric on one hand, and highly-doped poly-silicon as the gate electrode on the other hand, offers several simplifications in processing, while maintaining excellent device characteristics. However, the continuative scaling by using this material combination leads to quantum-mechanical effects that result in dramatically increased gate leakage currents. By the implementation of new materials with a high dielectric constant – if necessary in combination with metal-gate electrodes instead of poly-silicon electrodes – this problem can be preliminary solved and ongoing scaling of CMOS-devices can be enabled.

The present work addresses the investigation of high- $\kappa$  dielectrics and their applicability in CMOS-devices, using metal-gate electrodes. The contents firstly include the deposition of zirconium dioxide and hafnium dioxide from the gas phase, using organometallic precursors, and their physico-chemical characterization. In the following, MOS-capacitors are fabricated by the selective deposition of gate electrodes made from aluminium, molybdenum, nickel, or titanium-nitride, and characterized regarding their electrical behaviour. Furthermore, these material systems are investigated regarding their thermodynamical stability.

Results within this work demonstrate that well balanced and correctly applied annealing of the devices clearly improves electrical behaviour. not oxides do exhibit However, the processed the necessary thermodynamical stability in contact with silicon, which limits the achievable "electrical thickness". Nickel, molybdenum, and titanium-nitride behave as mid-gap metals regarding to silicon. We attribute these metals high potential to be applied in near-future CMOS-technology, if doped with the proper nitrogen content, or implemented as silicides.

iv

### Kurzfassung

Seit beinahe vierzig Jahren treiben technologischer Fortschritt und wirtschaftlicher Nutzen die Skalierung der CMOS-Technologie voran. Die Verwendung von Siliziumdioxid als Gate-Dielektrikum einerseits, und von hochdotiertem Polysilizium als Gate-Elektrode andererseits, spielt hierbei eine zentrale Rolle, und ermöglichte prozesstechnische Vereinfachungen unter Beibehaltung hervorragender Bauelementeigenschaften. Allerdings führt die fortschreitende Skalierung unter Verwendung dieser Materialkombination zu quantenmechanischen Effekten, die sich in einem dramatischen Anstieg der Gateleckströme bemerkbar machen. Durch die Einführung neuer Materialien mit hoher Dielektrizitätskonstante – gegebenenfalls in Kombination mit metallischen Elektroden anstelle von Polysilizium Elektroden – kann dieses Problem vorerst behoben, und so eine weitere Skalierung der CMOS-Bauelemente ermöglicht werden.

Die vorliegende Arbeit beschäftigt sich mit der Herstellung und Charakterisierung hochpermittiver Dielektrika, und deren Einsetzbarkeit in CMOS-Bauelementen unter Verwendung metallischer Elektroden. Der Inhalt umfasst zunächst die Abscheidung von Zirkonium-, und Hafniumdioxid aus der Gasphase. unter Verwendung metallorganischen von Vorläufersubstanzen, und deren physikalisch-chemischer Charakterisierung. Des Weiteren werden, durch das gezielte Aufbringen von Gate-Elektroden aus Aluminium, Molybdän, Nickel oder Titan-Nitrid, MOS-Kondensatoren erzeugt und bezüglich ihrer elektrischen Eigenschaften charakterisiert. Darüber hinaus werden diese Materialsysteme bezüglich ihrer thermodynamischen Stabilität untersucht.

Die erbrachten Ergebnisse zeigen, dass gut abgestimmte, und richtig angewandte thermische Nachbehandlung der Bauelemente, zu eindeutig verbesserten elektrischen Eigenschaften führt. Dennoch zeigen die prozessierten Oxide keine ausreichende Stabilität in Kontakt mit Silizium, was

die erreichbare 'elektrische Dicke' limitiert. Nickel, Molybdän und Titan-Nitrid zeigen "Mid-gap"-Verhalten in Bezug auf Silizium. Diesen Materialien – wenn entsprechen mit Stickstoff dotiert, oder als Silizid ausgeführt – schreiben wir gute Aussichten zu, in der nahen Zukunft in der CMOS-Technologie Anwendung zu finden.

# "High-κ/metal-gate devices for future CMOS technology"

### PART I: INTRODUCTION

| I.1 From Micro- to Nanotechnology | 2 |

|-----------------------------------|---|

| I.2 Motivation of this work       | 4 |

| I.3 Objectives of this work       | 5 |

### PART II: FUNDAMENTALS

| II.1 Current CMOS (Complementary MOSFET)<br>technology   | 7  |

|----------------------------------------------------------|----|

| II.1.1 Basic MOS semiconductor fabrication processes     | 7  |

| II.1.2 MOSFET and MOSCAP device physics                  | 14 |

| II.1.2.1 MOSFET device physics                           | 15 |

| II.1.2.2 MOSCAP device physics                           | 19 |

| II.1.3 Device scaling                                    | 28 |

| II.1.4 Parasitic effects and future trends               | 31 |

| II.2 High-κ/metal-gate devices                           | 40 |

| II.2.1 High-κ gate isolator                              | 40 |

| II.2.2 Metal gate electrode                              | 52 |

| II.2.3 Thin film technology                              | 57 |

| II.2.3.1 Overview and comparison                         | 57 |

| II.2.3.2 MOCVD and ALD                                   | 58 |

| II.2.3.3 Metal gate electrode: Deposition and patterning | 64 |

| II.3 Characterization methodology               |    |

|-------------------------------------------------|----|

| II.3.1 Physico-chemical methodology             | 66 |

| II.3.1.1 Spectroscopic ellipsometry (SE)        | 66 |

| II.3.1.2 Auger-electron spectroscopy (AES)      | 68 |

| II.3.1.3 Atomic force microscopy (AFM)          | 69 |

| II.3.1.4 Transmission electron microscopy (TEM) | 71 |

| II.3.2 Electrical methodology                   | 72 |

| II.3.2.1 Oxide- and interface trapped charge    | 73 |

| II.3.2.2 Capacitance-Voltage (C-V) measurements | 75 |

| II.3.2.3 Current-Voltage (I-V) measurements     | 81 |

| II.3.2.4 Electrical work function extraction    | 83 |

## PART III: EXPERIMENTAL WORK

| III.1 Substrate pre-treatment                                          | 86  |

|------------------------------------------------------------------------|-----|

| III.2 Gate oxide deposition by MOCVD                                   | 89  |

| III.2.1 Experimental setup of the MOCVD process                        | 89  |

| III.2.2 Numerical simulation and modelling of the MOCVD process        | 95  |

| III.3 Fabrication and electrical characterization of<br>MOS-capacitors | 99  |

| III.3.1 Gate electrode deposition and patterning                       | 99  |

| III.3.2 Electrical characterization                                    | 102 |

| III.4 Thermal treatment (Annealing)                                    | 103 |

### PART IV: RESULTS AND DISCUSSION

| IV.1 Physico-chemical properties of the gate oxides | 107 |

|-----------------------------------------------------|-----|

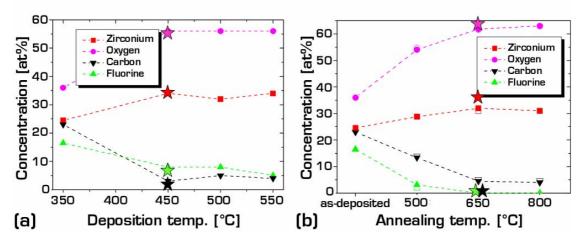

| IV.1.1 Chemical composition                         | 107 |

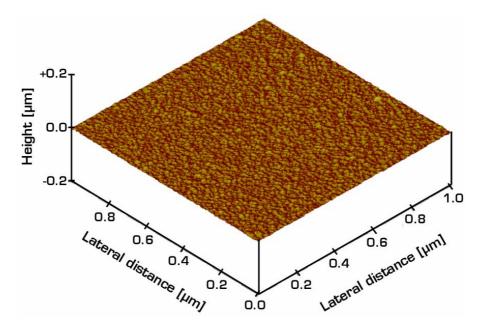

| IV.1.2 Topography                                   | 109 |

| IV.1.3 Morphology                                   | 112 |

| IV.2 Evaluation of the MOS-capacitors               | 114 |

| IV.2.1 Gate Material: Aluminium (Al)                | 114 |

| IV.2.2 Gate Material: Nickel (Ni)                   | 121 |

| IV.2.3 Gate Material: Titanium-Nitride (TiN)        | 128 |

| IV.2.4 Gate Material: Molybdenum (Mo)               | 131 |

| IV.2.5 Comparison of the different gate stacks      | 136 |

| IV.3 Conclusions and Outlook                        | 140 |

# PART V: REFERENCES AND APPENDIX

| V.1 References             | 144 |

|----------------------------|-----|

| V.2 Appendix               | 151 |

| V.2.1 List of symbols      | 151 |

| V.2.2 Index of equations   | 153 |

| V.2.3 Index of figures     | 156 |

| V.2.4 Index of tables      | 161 |

| V.2.5 List of publications | 162 |

| V.2.6 Curriculum Vitae     | 164 |

# PART I: INTRODUCTION

| I.1 From Micro- to Nanotechnology | 2 |

|-----------------------------------|---|

| I.2 Motivation of this work       | 4 |

| I.3 Objectives of this work       | 5 |

According to the Semiconductor Industry Association (SIA), worldwide sales of semiconductors set a new record at \$227.5 billion in 2005. From 1960 to 2003 the world market for semiconductors grew about 14 percent per year. This enormous increase is mainly due to the technological advance of microtechnology, a successful progress that is based on the systematically investigation of the material-, physical-, and chemical properties of silicon - the most important and universal semiconductor - and its processing abilities.

### I.1 From Micro- to Nanotechnology

It is no great surprise that government-financed Research & Development (R&D) institutions, as well as market-oriented companies change their prefix from "micro" to "nano". Now that the semiconductor industry scales the key dimensions of its functional components into regions where they are already partially quantum-mechanical controlled, the era of *microelectronics* passes into an era of *nanoelectronics*.

The remarkable success of the worldwide semiconductor industry principally results from its ability to exponentially decrease the minimum feature sizes used to fabricate integrated circuits. This lead to principal categories of improvement trends that are shown in table 1.A, with examples of each [1]. Of course, the most famous trend listed below is "integration level", which is usually cited as *Moore's Law* formulated by Intel co-founder Gordon Moore in 1965. It predicts the number of components per chip to be doubled every 24 months. An important step for carrying this issue into the 21<sup>st</sup> century was the implementation of Complementary Metal-Oxide-Semiconductor (CMOS) technology.

However, we have reached a point where planar bulk CMOS faces grand challenges, and to overcome these, invention of new processes, materials, or even completely new device concepts are indispensable.

| Trend             | Example                           |

|-------------------|-----------------------------------|

| Integration level | Components/chip, Moore's Law      |

| Speed             | Microprocessor clock rate, GHz    |

| Power             | Laptop or cell phone battery life |

| Compactness       | Small and light-weight products   |

| Functionality     | Non-volatile memory, imager       |

| Cost              | Cost per function                 |

**Table I.A**: Improvement trends for ICs enabled by minimal feature scaling.

### I.2 Motivation of this work

The International Roadmap for Semiconductors (ITRS) in its 2005 Edition classifies the reduction of Equivalent Oxide Thickness (EOT) as the most difficult challenge associated with future device scaling [1]. The gate stack system silicon (Si)/ silicon dioxide (SiO<sub>2</sub>)/polysilicon (poly-Si) has for a long time successfully played the key role in Metal Oxide Semiconductor Field Effect Transistor (MOSFET) technology, and its era has continued with silicon oxynitride (SION) as the gate dielectric. Nevertheless, the strong leakage restrictions in low-power applications will make the introduction of a higher dielectric constant (high- $\kappa$ ) material, in which the tunneling current can be suppressed while maintaining the drain current, necessary.

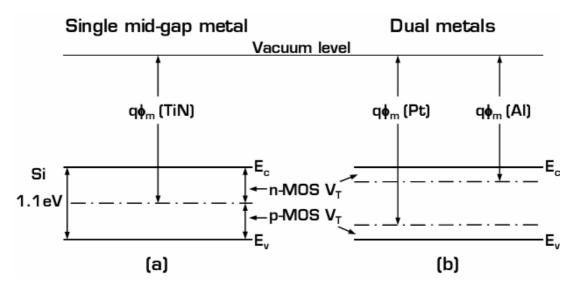

The implementation of such a new class of gate oxides additionally necessitates the introduction of metal gate electrodes. On one hand, this will avoid polysilicon depletion which becomes significant in the use of polysilicon gate electrodes and ads to the equivalent oxide thickness, while on the other hand it prevents boron in-diffusion and lowers the gate resistance. Therefore, metal gate materials that offer an appropriate work function - either as mid-gap metal for both, p-, and n-bulk MOSFETs, or in dual-work-function-gate technology - have to be found.

These material changes address key steps to be taken in future MOSFET-technology, and such new high- $\kappa$  and metal gate stacks are expected to be fundamental structures used within future CMOS devices, such as fully-depleted Silicon On Insulator (SOI) devices, or multi-gate MOSFETs. These issues attracted immense interest within the worldwide semiconductor-R&D-community during the last years and also bear the motivation of this work.

### I.3 Objectives of this work

This work is partially supported by the *Network of Excellence SINANO* (Silicon-based Nanodevices), which is funded by the *European Commission* under the *6th Framework Programme*, and topically embedded within workpackage 2: *Non-classical nano-MOSFET architectures*'. The main objective of this workpackage is to study the scientific challenges related to the fabrication and characterisation of experimental SOI, SON and double-gate (e.g.: FinFET, GAA) ultimate MOS devices that show performances and technological achievements as required by the ITRS roadmap beyond the 45 nm node, i.e. the end of this decade [2].

This work addresses the investigation of new metal gate/high- $\kappa$  dielectric/silicon stacks that fulfil the requirements for future devicetechnology. The contents herein include the complete area of interest, from the fabrication of various MOS-capacitors, via their physical-chemical and electrical characterization, to the investigation of their thermodynamical behaviour.

This thesis is structured into 5 parts: Part I very generally introduces the topic, by giving information about background and motivation. Part II contains all fundamentals that to the author appear necessary to seriously discuss the given topic. The content of this part is based on established and actual literature. In part III, the experimental work performed within the duration of this thesis is described successively. All obtained results and their scientific discussion is presented in part IV. Finally, part V closes with references and appendix.

# PART II: FUNDAMENTALS

| II.1 Current CMOS (Complementary MOSFET)<br>technology   |    |

|----------------------------------------------------------|----|

| II.1.1 Basic MOS semiconductor fabrication processes     | 7  |

| II.1.2 MOSFET and MOSCAP device physics                  | 14 |

| II.1.2.1 MOSFET device physics                           | 15 |

| II.1.2.2 MOSCAP device physics                           | 19 |

| II.1.3 Device scaling                                    | 28 |

| II.1.4 Parasitic effects and future trends               | 31 |

| II.2 High-κ/metal-gate devices                           | 40 |

| II.2.1 High-κ gate isolator                              | 40 |

| II.2.2 Metal gate electrode                              | 52 |

| II.2.3 Thin film technology                              | 57 |

| II.2.3.1 Overview and comparison                         | 57 |

| II.2.3.2 MOCVD and ALD                                   | 58 |

| II.2.3.3 Metal gate electrode: Deposition and patterning | 64 |

| II.3 Characterization methodology                        | 66 |

| II.3.1 Physico-chemical methodology                      | 66 |

| II.3.1.1 Spectroscopic ellipsometry (SE)                 | 66 |

| II.3.1.2 Auger-electron spectroscopy (AES)               | 68 |

| II.3.1.3 Atomic force microscopy (AFM)                   | 69 |

| II.3.1.4 Transmission electron microscopy (TEM)          | 71 |

| II.3.2 Electrical methodology                            | 72 |

| II.3.2.1 Oxide- and interface trapped charge             | 73 |

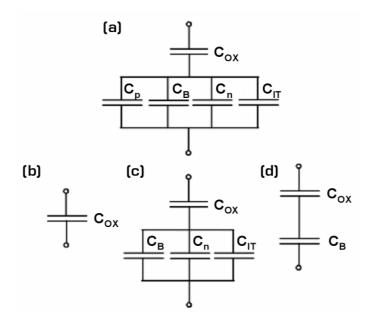

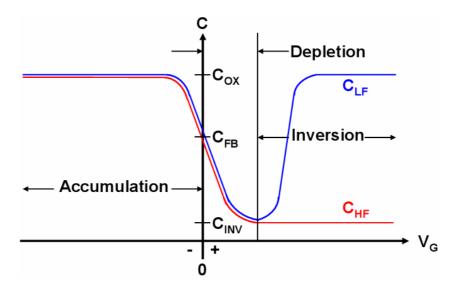

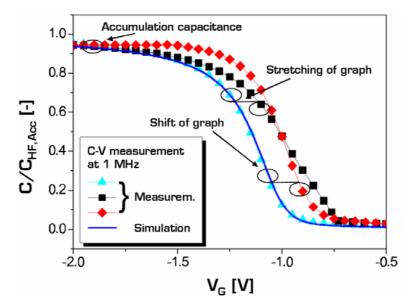

| II.3.2.2 Capacitance-Voltage (C-V) measurements          | 75 |

| II.3.2.3 Current-Voltage (I-V) measurements              | 81 |

| II.3.2.4 Electrical work function extraction             | 83 |

### II.1 Current CMOS (Complementary MOSFET) technology

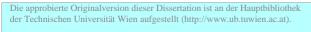

The CMOS (Complementary MOSFET) technology, which employs both n-MOS and p-MOS to form logic elements, was proposed by Wanlass and Saw [3] in 1963. Its advantage is that the logic elements draw significant current only during the transition from one state to another, offering power consumption to be minimized. Since the early 1980s, silicon-gate CMOS is the dominant technology for Very/Ultra Large Scale Integration (VLSI/ULSI) designs [4,5]. Figure II.1 shows a cross-sectional view of a "state-of-the-art" CMOS device. More details on the applied materials are presented in chapters II.2.1 and II.2.2.

**Figure II.1:** Cross-sectional schematic view of a "state-of-the-art" CMOS device, showing n-, and p-MOSFETs, separated by shallow trench isolation. Lightly doped source and drain are indicated (adapted from Wong et al. [18]).

### **II.1.1 Basic MOS semiconductor fabrication processes**

This chapter summarizes the basic processing steps that are widespread in MOS fabrication, whereas it mainly follows the textbook by Allen and Holberg [6]. In a separately discussed paragraph, a common n-well silicon-gate CMOS process will be described in detail.

All CMOS processing starts with single-crystal silicon material, which is mainly grown by the "Czochralski-method", named after its developer Jan Czochralski. A second method, the so-called "float zone technique", produces crystals of high purity, and is often used for power devices. The crystals are usually grown in either a (100)- or a (111) crystal orientation, and are then doped with n-type or p-type impurities to form an n- or a p-substrate, respectively.

The five basic processing steps applied to the doped silicon wafer to fabricate semiconductor components are oxidation, diffusion, ion implantation, deposition, and etching, and will be described in the following paragraphs.

#### A) Oxidation

"Oxidation" is the first basic processing step, during which a layer of  $SiO_2$  is formed on the surface of the silicon wafer. Thereby, the oxide grows into, as well as out of the silicon surface. Typically about 56 % of the oxide thickness are above the original surface, while about 44 % are below. There are two main techniques applied, "dry", or "wet oxidation", which take place at temperatures ranging from 700 °C to 1100 °C, with the resulting oxide thickness proportional to the growth-temperature and the growth-time. The grown oxide thickness  $t_{ox}$  varies from less than 15 nm for gate oxides to more than 1000 nm for field oxides.

#### **B)** Diffusion

"Diffusion" is the movement of impurity atoms from sites of high concentration to sites of low concentration and takes place at temperatures in the range of 800 °C to 1400 °C. The concentration profile of the impurities within the semiconductor is a function of the impurityconcentration at the semiconductor surface and the amount of time for which the semiconductor is placed in a high-temperature environment.

There are two basic types of diffusion, the "infinite-source-" and the "finite-source diffusion", distinguished by the time-dependent concentration of the impurity at the surface. These two types are typically of "pre-deposition"- and "drive-in diffusion"-types, respectively. The object of a pre-deposition diffusion is to place a large concentration of impurities near the surface of the material. The maximum concentration that can be diffused into silicon depends on the type of impurity and is, due to the solid solubility limit, in the range of  $5x10^{20}$  atoms/cm<sup>3</sup> to  $2x10^{21}$  atoms/cm<sup>3</sup>. The drive-in diffusion usually follows a pre-deposition, and is used to drive the impurities deeper into the semiconductor.

### C) Ion implantation

By "lon implantation", ions of a particular dopant (impurity) are accelerated by an electric field to a high velocity, and shot into the semiconductor material. The average depth of penetration, depending on the velocity and angle of the impinging ions, varies typically from 100 nm to 600 nm. The ion implantation process causes damage to the semiconductor crystal lattice, leaving most of the implanted ions electrically inactive. This damage can be repaired by an annealing process, in which the semiconductor temperature is raised to around 800 °C after implantation, allowing the ions to move to electrically active locations. Ion implantation can substitute diffusion, since in both cases the object is to insert impurities into the semiconductor material.

### D) Deposition

This fourth basic process includes the deposition of films of various materials. This may be done by using several techniques, including "Evaporation", "Sputtering" and "Chemical Vapour Deposition (CVD)".

In evaporation deposition, a solid material is placed in a vacuum and heated until it evaporates. The evaporated molecules strike the cooler wafer and condense into a solid film on the wafer surface.

The sputtering technique uses positive ions to bombard the cathode, which is coated with the deposition material, and this dislodged targetmaterial is deposited on the wafers that are placed on the anode.

CVD uses a process, in which a film is deposited by a chemical reaction or pyrolytic decomposition in the gas phase, which occurs at the surface of the silicon wafer.

For further details on thin film deposition techniques, the reader is referred to chapter II.2.3.

#### E) Etching

"Etching" is a process that removes exposed (unprotected) material. The means by which exposed- and unexposed material is structured is usually defined by "Photolithography", and will be discussed in the next paragraph. A protective layer – a so-called "mask" – covers the film, except in the area that is to be etched. The etching process has to satisfy two important properties: *selectivity* and *anisotropy*. "Selectivity" quantifies the ratio of the etch rate of the desired layer to the undesired one; "anisotropy" is the property of the etching process to manifest itself in one direction. In practice, neither perfect selectivity nor perfect anisotropy can be achieved, thus undercutting effects and partial removal of the underlying layer can be significant. There are two basic types of etching techniques, "wet etching", or "plasma etching" that uses ionized gases that are rendered chemically active by generated plasma.

### F) Photolithography

Each of the basic semiconductor fabrication processes discussed above is only applied to selected parts of the semiconductor, with the exception of oxidation and - in most cases - deposition. "Photolithography" refers to the complete process of transferring an image from a photomask or a computer database to a wafer. Its basic components are the "photoresist" material and the "photomask", which is used to expose some areas of the photoresist to UltraViolet (UV) light while shielding the rest. The photoresist is classified into "positive-" and "negative photoresist", whereby a positive photoresist is used to create a pattern where the photomask is opaque to UV light and a negative photoresist creates a pattern where the photomask is transparent to UV light. The resist itself can be removed with organic solvents or plasma ashing.

#### G) CMOS fabrication steps

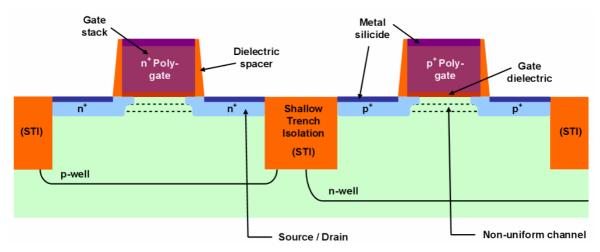

In the following paragraph, the fabrication steps of a common "n-well silicon-gate CMOS process" will be described in detail, whereby the mayor steps are summarized in figure II.2.

The first step of the n-well silicon gate CMOS process is to grow a thin silicon dioxide (SiO<sub>2</sub>) layer on a p-doped silicon wafer. The first lithographic step defines the regions where the n-wells are to exist. The n-type impurities are implanted into the wafer, as illustrated in figure II.2(a). After a high-temperature oxidation/drive-in process, the oxide is removed, and a thin pad oxide layer is grown to protect the substrate from stress due to the difference in the thermal expansion of silicon and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) (figure II.2(b)). Next, a global n-, and p-type field (channel stop) implant is performed, respectively, as illustrated in figure II.2(c). Its purpose is to ensure that parasitic p/n-channel transistors do not turn on under various interconnect lines. To achieve isolation between active regions, a thick SiO<sub>2</sub> layer is grown over the entire wafer, except where

Figure II.2: Mayor CMOS fabrication steps (adapted from [7]).

$Si_3N_4$  exists ( $Si_3N_4$  impedes oxide growth). This process is called "LOCOS isolation", resulting in a thick Field Oxide (FOX). Figure II.2(d) shows the result of this step.

Following, the remaining  $Si_3N_4$  is removed and the very critical growth of the gate oxide, serving as the gate dielectric, is performed by a slow lowpressure CVD process (figure II.2(e)). Its thickness  $t_{ox}$  determines a multitude of parameters of MOSFETs (e.g. drain current, trans-conductance, and reliability). Polysilicon is then deposited, patterned and etched, leaving the required areas to accomplish transistor gates. The result of this process step is illustrated in figure II.2(f).

Now the drain and source areas have to be diffused into the substrate. Ion implantation forms the source/drain regions of n-MOS transistors and n-well contacts (figure II.2(g)). After photolithography has been applied, the areas that consist of source- and drain-junctions of p-MOS transistors and the substrate ties are implanted by p-type ions (figure II.2(h)). These two implantation steps additionally dope the polysilicon layer, reducing its sheet resistance. The following silicidation process begins with creating an oxide spacer at the edges of the polysilicon gate, so that the deposition of the silicide will not short the gate to the source/drain regions. During the silicidation, active areas (source/drain regions, substrate and well ties) are covered with a thin layer of highly conductive material (e.g. titanium-, or tungsten silicide) by a CVD process (figure II.2(i) and figure II.2(j)).

The wafer is now covered with a thick layer of oxide and is again photolithographically patterned. The areas where the contacts are to be made are etched down to the surface of the silicon, whereby for increased reliability, contacts to the polysilicon gate are not placed on top of the gate area (figure II.2(k)). Metal (e.g. aluminium) is deposited over the entire wafer, photolithographically defined and subsequently etched, leading to a cross section shown in figure II.2(I). To prepare for a second metal, another interlayer dielectric is deposited. Intermetal connections (vias) are in principle

defined the same way as metal 1, and the result is illustrated in figure II.2(m). In order to protect the wafer from chemical intrusion or scratching, a passivation layer of  $SiO_2$  or  $Si_3N_4$  is applied over the whole wafer. Pad regions – areas where wires will be bonded between the integrated circuit and the circuit package – are then defined. Figure II.2(n) summarizes a cross section of the final circuit.

It is important to note that there are many other details with CMOS processes that have not been mentioned here, and furthermore there are different variations of the CMOS process just described. There is a wide variety, and the worldwide semiconductor R&D is continuously improving and re-inventing this highly-developed technology.

### II.1.2 MOSFET and MOSCAP device physics

In the previous chapter, we looked at the basic CMOS process steps, and how a MOSFET is typically processed. This chapter will give an overview about the "ideal" MOSFET characteristics. During the progression of this chapter, we will focus on the MOSCAP device as the controlling component of the MOSFET device characteristics. At a first glance, it might look uncommon to start with the more complex topic and progress to the simpler one. But the focus of this work lies on MOSCAP device structures, and therefore the aim of this approach is a stepwise approximation to the relevant fundamentals by "zooming" deeper and deeper into the device, until we get to the "heart" of every MOSFET, the *gate/oxide/semiconductor transition*. All derivations are made at the example of the poly-Si/SiO<sub>2</sub>/Si device, with the contents mainly taken from the excellent textbooks Sze [8], Chang and Sze [9], and Nicollian & Brews [10].

#### II.1.2.1 MOSFET device physics

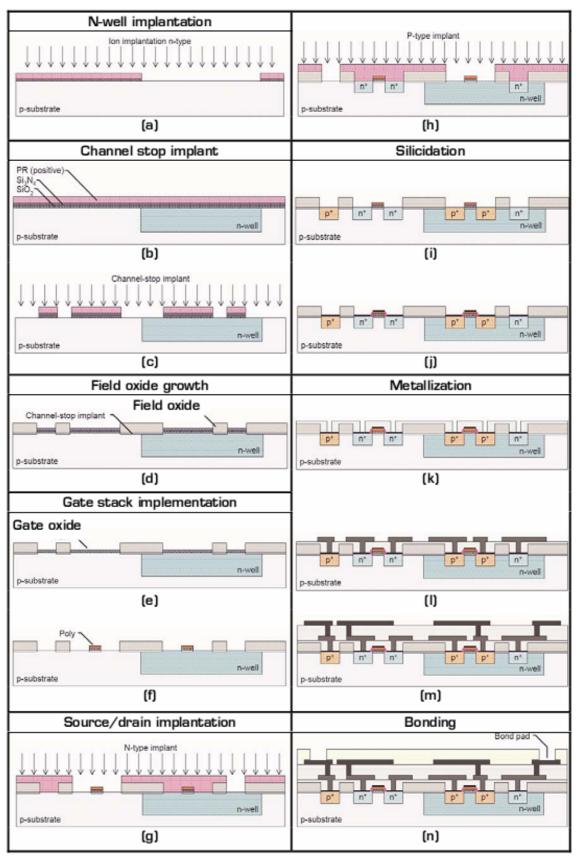

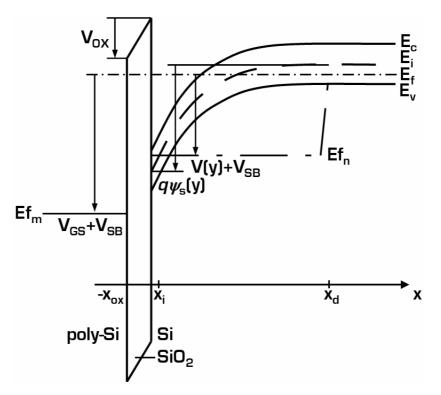

Figure II.3 shows the cross section of an n-channel MOSFET with the voltage terminals and the space coordinates defined. The substrate voltage  $V_B$  is arbitrarily set to be the voltage reference. The one-dimensional energy-band diagram perpendicular to the Si/SiO<sub>2</sub> interface is shown in figure II.4. Assuming that the current flow is essentially one-dimensional from the source to the drain (this assumption will be inadequate for short channel devices), the drain current including both, drift and diffusion, is described by

$$J_n(x, y) = q\mu_n nE + qD_n \frac{dn}{dy}$$

II.1

where  $\mu_n$  is the electron mobility, E is the electric field, and  $D_n$  is the diffusion coefficient. Assuming a Boltzmann-distribution for the minority carriers (electrons for n-channel and holes for p-channel),

$$n = n_{pB} e^{q(\phi - V - V_{SB})/kT}$$

, ||.2

where  $n_{pB}$  is the electron concentration in a p-type semiconductor in the bulk and

$$\frac{dn}{dy} = \frac{q}{kT} n \left( \frac{d\phi}{dy} - \frac{dV}{dy} \right).$$

II.3

Together with the Einstein relation  $(kT/q)\mu_n = D_n$ , equation II.1 reduces to

$$J_n(x, y) = -q\mu_n n \frac{dV}{dy} \,. \tag{I.4}$$

After integrating over the spatial dimensions and with the mobility approximated by a weighted average, the drain current can be written as [11,12]:

Figure II.3: Cross section (schematic) of an n-channel MOSFET with the voltage terminals and the space coordinates defined (adapted from [9]).

**Figure II.4:** Energy-band diagram in the direction perpendicular to the  $Si/SiO_2$  interface corresponding to figure II.3 (adapted from [9]).

with the electron mobility  $\mu_n$ , and the characteristic dimensions channel length *L* and channel width *W*, where

$$Q_n(y) = -q \int_0^{x_w} n(x, y) dx \qquad \qquad \text{II.6}$$

is the two-dimensional (2D) charge density. To obtain the drain current, we need to know  $Q_n$  in equation II.5, which is derived using the solution of the Poisson equation,

$$\nabla^2 \phi(x, y, z) = \frac{-\rho(x, y, z)}{\varepsilon_s}$$

||.7

(electric charge density  $\rho(x, y, z) = q(N_D - N_A + p_p - n_p)$ ), II.8

where  $\varepsilon_s$  is the dielectric permittivity of the semiconductor, the subscript p in the electron density  $(n_p)$  and the hole density  $(p_p)$  refers to the respective quantity in a p-type semiconductor,  $N_A$  is the ionized acceptor-dopant density, and  $N_D$  is the ionized donor-dopant density. Assuming a three-dimensional (3D) density of states and the Maxwell-Boltzmann statistics for the carrier density, and after applying boundary conditions, assuming charge neutrality, and different mathematical transformations (for details, the reader is referred to [8],[9]), we obtain the mobile charge in the inversion layer  $Q_n$ :

$$Q_n = -\frac{1}{2}\lambda C_{ox}\sqrt{\frac{q}{kT}}G(\phi, V, V_{SB}, \phi_F), \qquad \text{II.9}$$

where  $\lambda = \sqrt{2\varepsilon_s q N_A} / C_{ox}$ ,  $C_{ox}$  is the gate oxide capacitance, and the function G is dependent on applied voltage V, and the location-dependent potential  $\phi$ .

The total charge of the semiconductor  $Q_s$  and the mobile charge in the inversion layer  $Q_n$  has to be related to the applied terminal voltages in order to relate the terminal currents to their corresponding voltages. Referring to figures II.3 and II.4 and taking an one-dimensional slice along the *x* direction, the terminal voltages and the potential at the Si/SiO<sub>2</sub> interface  $\psi_s$  can be brought into context as:

$$V_{G} - V_{B} - V_{FB} = V_{OX}(y) + \psi_{S}(y)$$

$$V_{GB} = V_{FB} + V_{OX}(y) + \psi_{S}(y)$$

II.10

and

$$Q_s(y) = Q_n(y) + Q_d(y) = -V_{OX}(y)C_{OX}$$

, ||.11

where  $V_{FB}$  is the flatband voltage,  $V_{OX}$  is the voltage drop across the gate oxide, and  $Q_d$  is the charge per unit area in the depletion region of the semiconductor.

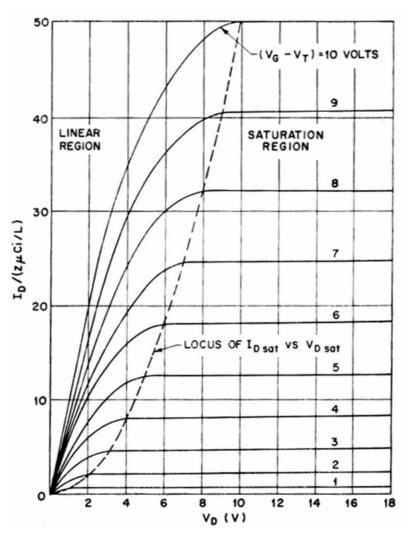

We can now obtain the drain current in strong inversion. Therefore, we have to obtain the depletion charge  $Q_d$  by solving the Poisson equation. The drain current can then be obtained by integrating equation II.5 (for details, the reader is referred to [8],[9]. If we ground the source and substrate terminals ( $V_S = V_B = 0$ ), and with the threshold voltage, we obtain for the linear region ( $V_D \ll V_G - V_T$ ):

$$I_D = \mu_n \left(\frac{W}{L}\right) C_{OX} (V_G - V_T) V_D.$$

II.12

As the drain voltage is increased, the channel will be pinched off. If we set  $Q_n(y = L) = 0$ , when  $V(y = L) = V_{Dsat}$ , we get (by additionally assuming a large  $V_G$  or a small  $N_A$ ):

$$I_{D} = \frac{1}{2} \mu_{n} C_{OX} \left(\frac{W}{L}\right) (V_{G} - V_{T})^{2}.$$

II.13

Summarizing, figure II.5 shows idealized drain characteristics of a MOSFET. In the subthreshold region ( $\phi_F + V + V_{SB} < \psi_S < 2\phi_F + V + V_{SB}$ ), the drain current is mainly a diffusion current, in contrast to a drift current in the strong-inversion region [8].

**Figure II.5:** Idealized drain characteristics ( $I_D$  versus  $V_D$ ) of a MOSFET. The dashed line indicates the locus of the saturation drain voltage ( $V_{Dsat}$ ). For  $V_D > V_{Dsat}$ , the drain current remains practically constant [8].

#### II.1.2.2 MOSCAP device physics

In the previous paragraphs, we showed that the functionality of a MOSFET can be controlled by the central Metal/Insulator/Semiconductor (MIS, or commonly: MOS) structure. Therefore, the MOS is a very useful device to study, and for this reason the fabrication and characterization of such MOS devices builds the core of this work. In this chapter, we will summarize the fundamental device physics, whereas we will follow of the contents the excellent textbook from Nicollian and Brews [10].

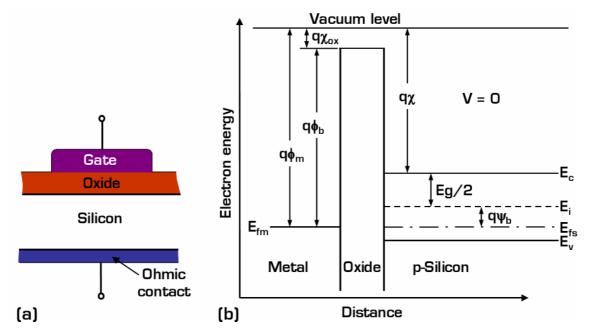

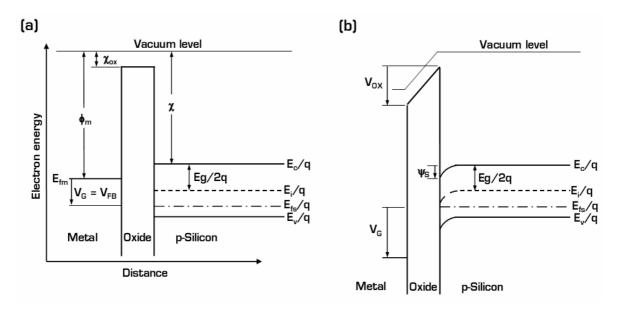

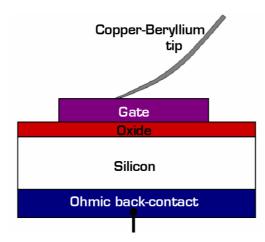

A MOS capacitor (MOSCAP) consists of a parallel plate capacitor with one electrode, the "gate", and the other electrode, the "silicon". The two electrodes are separated by a thin insulating layer ("oxide") of (conventionally) SiO<sub>2</sub>. Such a structure is shown in figure II.6(a). Figure II.6(b) illustrates the corresponding energy band diagram (ideal case) for a p-type semiconductor at zero applied bias (V = O);  $E_{fm}$  is the metal work function,  $\chi$  the semiconductor electron affinity,  $\chi_{ox}$  the oxide electron affinity,  $E_g$  the bandgap,  $\phi_b$  the potential barrier between the metal and the insulator, and  $\psi_b$  the potential difference between the Fermi level  $E_{fs}$  of the semiconductor and its intrinsic Fermi level  $E_{j}$ . In these conditions the energy bands are flat ("flatband condition").

We now discuss the silicon surface charge layer for such a MOSCAP. Applying a negative bias to the gate causes the holes to be attracted to the Si/oxide interface, where they form an accumulation layer. Its thickness is comparable to a "Debye length" (typically 10 nm - 100 nm, depending on bias and doping density). If we increase the gate bias, holes leave the accumulation layer. At the flatband voltage V<sub>FB</sub>, the silicon will be neutral everywhere. As the gate bias is made positive with respect to flat bands, holes are repelled from the silicon surface. The positive gate charge is balanced by negative acceptor ions within the silicon *depletion layer*, so-called because holes have been depleted from the surface region. As the gate bias increases, the depletion layer widens to provide more acceptor ions to balance the gate charge (0.1)μm  $10 \ \mu m$  deep, depending on bias and doping density).

Finally, we increase positive gate bias until electrons appear at the silicon surface in great numbers. These electrons then form a thin *inversion layer*, located at the Si/oxide interface, in a region 3 nm - 30 nm thick. Once inversion occurs, any further increase in positive gate charge is almost entirely balanced by the addition of electrons to the

inversion layer. Consequently, the depletion layer no longer increases much in width.

For a mathematical description of this picture of the silicon surface charge layer and its variation with bias, we need to solve Poisson's equation, whereby we assume the MOSCAP to be in thermal equilibrium under applied bias. The whole system will be in thermal equilibrium only, when the Fermi level  $E_f$  is the same in both parts, because all quantum levels at a given energy must have equal occupation probabilities at thermal equilibrium. If  $E_f$  is not equal before contact, electrons will flow from higher to lower  $E_f$  until equality is achieved. After the initial transient, no current flows through the system, because the current flow is blocked by the large energy barriers between the oxide and each electrode. Only for oxide layers remarkably thinner than 5 nm, thermal equilibrium can be disturbed by tunnelling through the oxide. We solve the Poisson equation with certain simplifying conditions:

**Figure II.6:** (a) Cross section of a p-MOS capacitor. (b) Energy band diagram (ideal case) of an MOS capacitor as shown in figure (a) for a p-type semiconductor at zero applied bias (V = O).

- 1) Poisson equation will be solved in one dimension. (The field under the gate is uniform and perpendicular to the silicon surface)

- Impurity concentration in the silicon is uniform. This assumption does not apply, but is a good introduction.

- 3) The equation is solved for the non-degenerate case.

- 4) The Poisson equation will be solved using an approximate charge density. Each electron or hole is treated as if it moved in an average field. Thus, each electron or hole can be treated as an independent particle.

- 5) Surface quantization (carriers are trapped in a narrow potential well at the Si-surface) is neglected.

The "band bending approximation" assumes that the density of states in the conduction- and the valence band is not changed by the applied electric field. The only effect of an electric field is to shift all energy levels in the conduction- and valence band by a constant amount, determined by the potential at each given point in the silicon. This approximation is valid over temperature- and electric field ranges of interest in many device applications and MOSCAP measurements; but it fails in surface quantization and very heavy doping. We now calculate the hole and electron density distribution at the silicon surface under applied bias. Free carrier concentrations are functions of distance and therefore calculated as a function of x, measured in a direction perpendicular to the interfacial plane into the silicon bulk. For the electron density n(x) in the conduction band, in the presence of an electric field, we obtain

$$n(x) = N_D \exp\left(\frac{q\psi(x)}{kT}\right), \qquad \qquad \text{II.14}$$

and similarly the hole density p(x) in the valence band is

$$p(x) = N_A \exp\left(-\frac{q\psi(x)}{kT}\right), \qquad \qquad \text{II.15}$$

where  $\psi(x)$  is the band bending and  $N_D/N_A$  are the donor/acceptor densities per unit volume, respectively.

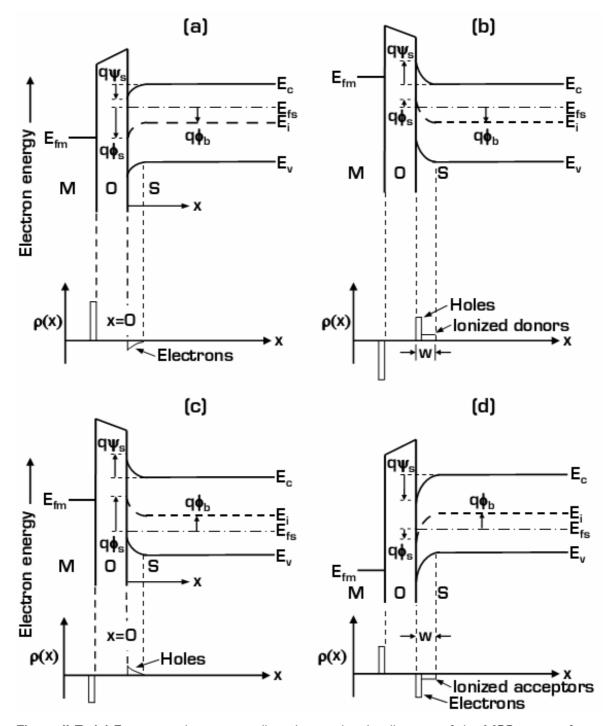

Figure II.7 shows the energy diagram for n/p-type silicon in accumulation and depletion-inversion, respectively. An arrow pointing down denotes a positive potential, an arrow pointing up a negative one. The potential  $\phi(x)$  is defined by the equation

$$q\phi(x) \equiv E_{fs} - E_i(x)$$

, II.16

where  $E_{fs}$  is the extrinsic Fermi level and  $E_i(x)$  is the intrinsic energy level. Deep in the silicon  $(x \to \infty)$ ,  $\phi(x)$  is called the "bulk potential"  $\phi_B(x)$ , and at the silicon surface  $(x \to 0)$ ,  $\phi(x)$  is called the "surface potential"  $\phi_S(x)$ . The band banding  $\psi(x)$  is defined as

where  $\psi(x)$  represents the potential at any point x in the depletion layer with respect to its value in the bulk. In particular, the barrier height  $\psi_s(x) = \phi_s(x) - \phi_B$  is the total potential difference between the silicon surface and the bulk; that is,  $\psi_s(x)$  is the total band bending.

The sign conventions for the potentials for n-type silicon in figure II.7 are:

- accumulation:  $\phi_B > 0, \psi_S > 0, :and \cdot \phi_S > 0$

- flat bands:  $\psi_s = 0 \cdot and \cdot \phi_s = \phi_B$

- intrinsic point ( $n_S = p_S$ ):  $\psi_s = -\phi_B < 0$

- inversion:  $\psi_s \leq -2\phi_B < 0$ .

The sign conventions for the potentials for p-type silicon in figure II.7 are:

- accumulation:  $\phi_B < 0, \psi_S < 0, and \cdot \phi_S < 0$

- flat bands:  $\psi_S = 0 \cdot and \cdot \phi_S = \phi_B$

**Figure II.7:** (a) Energy- and corresponding charge density diagram of the MOS system for n-type silicon in accumulation. An arrow pointing down denotes positive potential. (b) Same as (a), except depletion-inversion is shown. (c) and (d) are same as (a) and (b), but for p-type silicon.

We are now ready to discuss the surface charge region quantitatively. This problem is one dimensional, so that potentials are functions of x only. The Poisson's equation will be solved under the simplifying conditions listed above, and where the band-bending approximation is valid (for a review, see [13]):

where  $\rho(x)$  is the charge density composed of immobile ionized donors, acceptors, mobile holes, and electrons [ $\rho(x) = q(p(x) - n(x) + N_D - N_A)$ ] and  $\varepsilon_s$  is the dielectric permittivity of silicon. The condition of charge neutrality has to exist in the bulk; that is, far from the surface where  $\phi(\infty) = \phi_B \cdot and \cdot \rho(x) = 0$ . Integrating the Poisson equation from the surface to the bulk, we get the field of a semiconductor at the surface, and to get the total charge per unit area, one can use the Gaussian law:

$$Q_{S} = \varepsilon_{S} F_{S} = \operatorname{sgn}(u_{B} - u_{S}) C_{o} \left(\frac{kT}{q}\right) F(u_{S}, u_{B}), \qquad \text{II.19}$$

where  $F_S$  is the field at the semiconductor surface,  $u(x) = q\phi(x)/kT$  is the dimensionless potential in the bulk (index <sub>B</sub>) and at the surface (index <sub>S</sub>),  $C_o = \varepsilon_S / \lambda_i$  is an effective semiconductor capacitance per unit area with the intrinsic Debye length  $\lambda_i$  defined as

$$\lambda_i = \left(\frac{\varepsilon_s kT}{2q^2 n_i}\right)^{1/2} [cm] [14], \qquad \qquad \text{II.20}$$

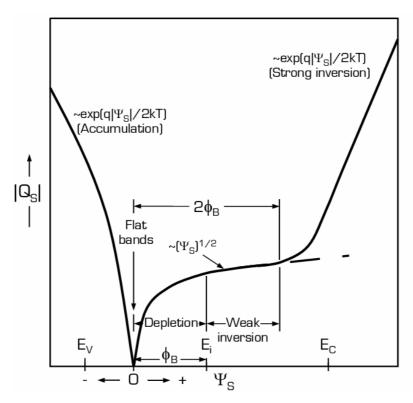

and  $F(u_B, u_S)$  is the dimensionless electric field. Figure II.8 gives a plot of relation II.19.

The "depletion approximation" approximates the free carrier distribution in the transition region between the depletion region and the neutral bulk by a step function. This step function greatly simplifies the

**Figure II.8**: Plot of relation II.19, showing the silicon surface charge density  $|Q_s|$  as a function of barrier height  $\psi_s$  for p-type silicon (adapted from [8]).

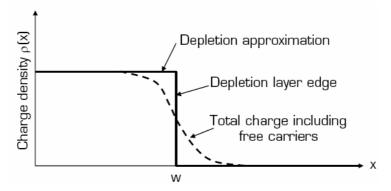

solution of Poisson's equation in depletion and is widely used. Figure II.9 shows total charge density as a function of distance from the silicon surface. That is, if p = n = 0 in the depletion layer and charge neutrality prevails beyond the depletion layer edge. As doping concentration increases, the transition from the depletion region to the neutral bulk region becomes more abrupt.

For the general case of a non-uniform impurity distribution (e.g. diffused or ion implanted surface, or impurity redistribution), the depletion layer charge density in the depletion approximation is

$$\rho(x) = q[N_D(x) - N_A(x)].$$

II.21

After obtaining Poisson's equation and integration, we get:

$$F(x) = \frac{q}{\varepsilon_s} \int_{w}^{x} [N_A(x') - N_D(x')] \cdot dx'. \qquad \text{II.22}$$

**Figure II.9**: Silicon surface charge density in the depletion layer (width is w) approximation. Total charge density including free carriers is shown as dotted curve. The sign of majority carriers is always opposite the sign of ionized impurities, so that the total charge is the difference between the two (adapted from [10]).

The potential in the depletion layer is obtained by integrating again:

$$\psi(x) = \frac{q}{\varepsilon_{s}} \int_{w}^{x} dx' (x - x') [N_{A}(x') - N_{D}(x')].$$

II.23

Assuming the specific case of a uniform impurity distribution (  $q(N_{\rm A}$  -  $N_{\rm D})$  = constant ), equation II.22 can be written

$$F(x) = \frac{q}{\varepsilon_s} (N_A - N_D)(x - w).$$

II.24

Integrating equation II.24, substituting the obtained relation into equation II.23 and integrating once more from the bulk to the surface, yields

$$\psi(x) = \frac{1}{2} \frac{q}{\varepsilon_s} (N_A - N_D) (x - w)^2.$$

II.25

For n-type  $N_D > N_A$ , so that  $\psi_S < 0$ , whereas for p-type  $N_A > N_D$ , so that  $\psi_S > 0$ . Finally, we can write:

$$\psi(x) = \psi_s \left(1 - \frac{x}{w}\right)^2, \qquad \qquad \text{II.26}$$

where we can see from equation II.26 that the band bending in the depletion layer has a parabolic shape as it varies from  $\psi_s$  at the surface to zero in the bulk.

The depletion layer width increases with applied bias until the silicon surface becomes strongly inverted. With further increases in bias, the depletion layer width then increases only slowly, because the inversion layer shields the silicon from further penetration of the applied field. We have to keep in mind, that equations II.22 and II.23 are not exact, since the depletion approximation ignores some important facts that will not be mentioned here (please see [10] for further information). But for gradual profile variations, such as thermal redistribution effects, the errors are small, and the depletion approximation can be used with confidence.

In the previous three chapters, we worked out the basic processing steps in CMOS technology, as well as the fundamental device physics of its dominant component, the MOSFET. We have shown that the central MOSCAP structure - with its most critical part, the gate dielectric - of a MOSFET determines and controls the functionality of the device. In the following part, we will once more dare the balancing act between semiconductor physics and technology by discussing the basic concepts of device scaling.

## II.1.3 Device scaling

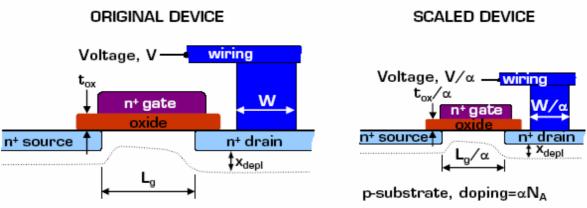

The first concise concept of device scaling was introduced by Dennard et al. [15] and further developed in the 1980s [16]. Figure II.10 illustrates the concept of device scaling, whereby the larger device is scaled down by a factor  $\alpha$  to yield the smaller device. The theoretical basis of scaling is formulated by considering the Poisson- and the current continuity equations, which will not be shown here in detail (for further information, the reader is referred to [16]). Table II.A summarizes the scaling relations for various scaling scenarios.

p-substrate, doping=N<sub>A</sub>

The first case in table II.A summarizes scaling relations for constant electric field scaling ( $\varepsilon = 1$ ). In practice, because of the difficulties with standard voltage supplies, the voltage is seldom scaled as rapidly as the linear dimensions. Thus, an additional scaling factor  $\varepsilon$  ( $\varepsilon > 1$ ) for the electric field is introduced, as summarized under "generalized scaling" in table II.A. Increasing the electric field requires increasing the amount of doping, and also increases the power dissipation. The disadvantage of this scaling is that the increasing electric field increases the energy of the carriers, resulting in such undesirable effects as "hot-carrier injection" into the gate oxide, or "impact ionization", which affects device reliability. Indeed, this reliability concern forces the use of lower supply voltages for smaller devices, even if power dissipation is not an issue [17]. In recent technology generations (Gate length  $L_a < 0.5 \mu m$ ), the wiring is not scaled to the same extend as the gate length, since this improves the wiring yield without degrading the gate delay. This "selective scaling" approach is shown in the third column of table II.A, and has two spatial dimension scaling parameters,  $\alpha_d$  for scaling the gate length and device vertical dimensions, and  $\alpha_w$  for scaling the device width and wiring.

Figure II.10: Schematic illustration of CMOS scaling technology by a factor  $\alpha$  (adapted from [9]).

| Physical parameter                     | Constant<br>electric field<br>scaling factor | Generalized<br>scaling factor | Generalized<br>selective<br>scaling factor |

|----------------------------------------|----------------------------------------------|-------------------------------|--------------------------------------------|

| Channel length,<br>insulator thickness | 1/α                                          | 1/α                           | $1/\alpha_d$                               |

| Wiring width, channel<br>width         | 1/α                                          | 1/α                           | $1/\alpha_w$                               |

| Electric field in device               | 1                                            | 3                             | 3                                          |

| Voltage                                | 1/α                                          | ε/α                           | $\epsilon/\alpha_d$                        |

| Doping                                 | α                                            | ωз                            | $\epsilon  lpha_{d}$                       |

| Area                                   | 1/α²                                         | 1/α²                          | 1/a <sub>w</sub> ²                         |

| Capacitance                            | 1/α                                          | 1/α                           | $1/\alpha_{w}$                             |

| Gate delay                             | 1/α                                          | 1/α                           | $1/\alpha_{d}$                             |

| Power dissipation                      | 1/α²                                         | ε²/α²                         | $\epsilon^2 / \alpha_w \alpha_d$           |

| Power density                          | 1                                            | 2 <sup>2</sup>                | $\epsilon^2 \alpha_w / \alpha_d$           |

Table II.A: Technology scaling rules for three cases.

$\alpha$  is the dimensional scaling parameter,  $\epsilon$  is the electric field scaling parameter, and  $\alpha_d$  and  $\alpha_w$  are separate dimensional scaling parameters for the selective scaling case.  $\alpha_d$  is applied to the device vertical dimensions and gate length, while  $\alpha_w$  applies to the device width and the wiring. After Wong et al. [18].

Despite the aim of increasing the number of components/chip, an improvement in performance by reducing the average switching time drives ongoing device scaling. The switching time  $\tau$  of a MOSFET results from the charging and discharging of a capacitive load, where

with the load capacitance  $C_{Load}$ , the drain voltage  $V_D$ , and the drive current  $I_D$ . The load capacitance reduces to the gate capacitance  $C_G$ , if we ignore parasitic contributions, such as junction and interconnect capacitance. For a device scaled by a factor  $\alpha$  the switching time (in the case of constant field scaling; see table II.A) is given by

$$\tau_{scaled} = \frac{C_G V_D}{I_D} \cdot \frac{1}{\alpha} \,. \tag{II.28}$$

Scaling therefore leads to higher clock speeds and faster devices. To achieve this improved clock speed, also the gate capacitance has to be scaled by the factor  $\alpha$ . If we keep in mind that the area of the gate is scaled in both lateral dimensions by the factor  $\alpha$ , the capacitance per area *C*/*A* has to rise by the amount of the scaling factor. In this case we consider a parallel plate capacitor:

where  $\kappa$  is the relative dielectric constant of the material,  $\varepsilon_0$  is the permittivity of free space, and *t* is the thickness of the gate dielectric. To maintain the relation in equation II.29 constant, we have to reduce the thickness *t* of the gate dielectric by the factor  $\alpha$ .

However, a reduction of the oxide thickness is not endlessly possible, as will be shown in the following chapter, and therefore the only alternative to solve this problem is a raise of the relative dielectric constant of the insulating material.

# II.1.4 Parasitic effects and future trends

This chapter focuses on several parasitic effects that are crucial for MOSFETs in the ULSI era. These non-ideal effects were ignored in the firstorder models in chapters II.1.1 and II.1.2, but are of utmost importance for device design. Hereby, we intentionally don't treat important issues, such as short-channel effects or transport properties coming along within the ULSI era, since this would go beyond the scope of this work. The reader therefore is once more referred to the previously mentioned references, which provide an excellent insight.

In the progress of this section, we will then figure out some future trends in MOSFET device technology to overcome these difficulties. Therefore, this final section of chapter II.1 bridges the gap to chapter II.2, where we will introduce high- $\kappa$ /metal-gate devices.

## A) Hot carriers:

Because of the desire to keep the power supply voltage high compared to the threshold voltage to improve performance, the electric fields typically rise as devices are scaled. Carriers in the channel gain energy as they travel from the source to the drain, and this energy is increased by an increasing electric field. These high-energy carriers are called "hot carriers" [19,20]. Due to a redirection scattering some carriers gain enough energy and momentum, so that they may surmount the interfacial Si/SiO<sub>2</sub> energy barrier and be injected into the gate oxide as gate current [21]. Currents through the gate insulator create interface traps, which in turn cause degradation of the device performance [22].

The most effective way to reduce hot-carrier degradation effects, apart from reducing the power supply voltage, is to use lightly doped drain (LDD) structures [23]. The basic concept behind the LDD is to drop the drain voltage in a lightly doped drain region between the channel and the heavily doped drain, and thereby reducing the maximum lateral electric field experienced by channel carriers.

#### B) Gate-Induced Drain Leakage (GIDL):

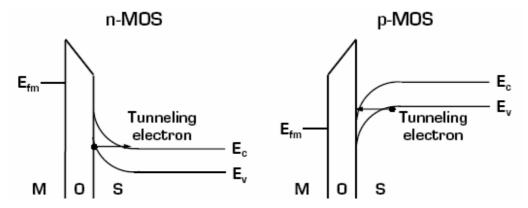

The "gate-induced drain leakage (GIDL) current" is attributed to bandto-band tunneling in the high-field regions in the silicon [24]. This effect is to be avoided in MOSFET design, to limit the transistor OFF-current. Band-toband tunneling occurs in the high-field depletion region under the gate-drain overlap region. Figure II.11 illustrates the process for n- and p-channel devices. For n-channel devices, electrons tunnel from the valence band to the conduction band when the applied gate-to-drain bias results in band bending beyond the silicon band gap (similarly for holes in p-channel devices). The generated electrons travel laterally in the depleted drain and these carriers may be amplified by impact ionization if the carriers attain enough energy in the high-field region (as in a large drain bias).

Band-to-band tunneling can be used to generate hot carriers for injection into the gate insulator, for programming of nonvolatile memory devices [25]. Reference [25] introduces a band-to-band tunneling model.

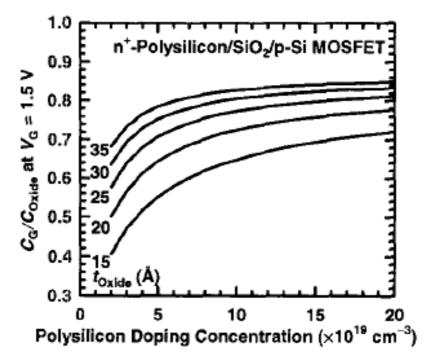

#### C) Gate capacitance degradation

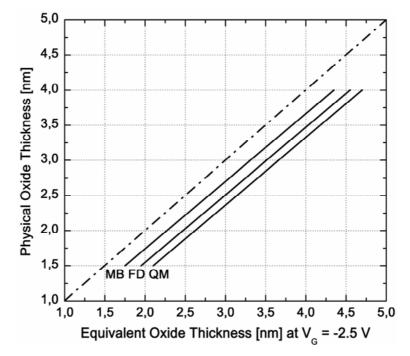

The gate capacitance is an important determinant for the transconductance and the current drive, attainable by a MOSFET. For MOSFETs scaled to small dimensions, the gate capacitance is no longer simply the specific gate oxide capacitance  $C'_{ox} = \varepsilon_0 \kappa / t_{ox}$  based on the oxide thickness  $t_{ox}$ , but can best be described by an equivalent electrical thickness  $t_{eq} = \varepsilon_0 \kappa / C_{inv}$ , where  $C_{inv}$  is the gate capacitance at inversion. Figure II.12 shows the calculated electrical equivalent oxide thickness  $t_{eq}$  versus the physical oxide thickness  $t_{ox}$  [26]. The calculation compares the classic (Maxwell-Boltzmann (MB)- and Fermi-Dirac (FD)-distribution) assumptions and the more accurate quantum-mechanical (QM) description.

**Figure II.11**: Energy-band diagram illustrating the band-to-band tunnelling process in silicon in the gate-drain overlap region. Electron-hole pairs are generated by the tunnelling of valence-band electrons into the conduction band and collected by the drain and the substrate separately (adapted after [27]).

For thin physical oxide thickness, the discrepancy between physical oxide thickness and the electrical thickness is significant. The gate capacitance is degraded by two effects:

- 1. Inversion-layer broadening due to quantum confinement of the 2D electron gas [28,29].

- 2. Depletion of the polysilicon gate [30].

The inversion-layer capacitance  $C_{inv}$  becomes non-negligible compared to the gate oxide capacitance, as gate oxides are scaled below 10 nm, or when the temperature is lowered. The channel charge is reduced by quantum-mechanical broadening of the inversion layer [29].

For MOSFETs with a heavily doped poly-silicon gate, the polysilicon is either depleted or accumulated, depending on the gate bias. In either case, the finite thickness of the depletion-accumulation region contributes to a reduction of the gate capacitance, because the depletion-

**Figure II.12**: Calculated (QM)  $t_{ox} - t_{eq}$  curves for n<sup>+</sup>-poly-Si/p-Si MOS devices. Two other groups are based on the classical model with Fermi-Dirac (FD) and Maxwell-Boltzmann (MB) statistics, respectively, for comparison. Each group summarizes four curves (adapted from [26]). The dash-dotted line represents the unaffected reference for SiO<sub>2</sub>.

accumulation capacitance of the poly-silicon gate is in series with the gate oxide capacitance [31]. This effect becomes significant as the gate oxide becomes thinner in the ULSI regime. As it is common to employ an n<sup>+</sup>-gate polysilicon doping for n-channel MOSFETs and a p<sup>+</sup>-gate polysilicon doping for p-channel MOSFETs, the polysilicon gate is inverted when the MOSFET channel is in inversion.

Figure II.13 shows the ratio of gate capacitance to gate oxide capacitance as a function of the doping of the polysilicon gate. It highlights that the total gate capacitance is degraded for thin gate oxides due to polysilicon depletion effects, and that it is extremely important to control the doping of the polysilicon gate, to provide uniformity of the electrical gate oxide thickness. It is particularly difficult to achieve high doping for  $p^+$ -polysilicon gates, because of the segregation of boron into the gate oxide and the possible penetration of the boron into the channel during high-temperature activation anneals.

**Figure II.13**: Calculated gate capacitance to oxide capacitance ratio versus polysilicon doping concentration with oxide thickness as a parameter [26].

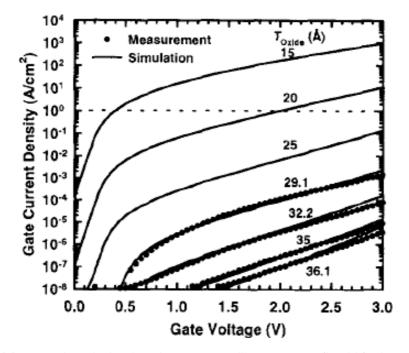

#### D) Gate tunneling current

As the physical thickness is scaled below ~ 3 nm in ULSI devices, significant direct tunneling occurs under high gate biases between the MOSFET channel and the gate. Figure II.14 shows the experimental and calculated gate tunneling current for various gate oxide thicknesses used in ULSI MOSFETs. The direct-tunneling current increases exponentially with decreasing gate oxide thickness and will impose a lower limit of standby-power dissipation and an upper limit of the number of active FETs on a chip for a given standby-power specification. For ULSI systems, a gate tunneling current of about 1 A/cm<sup>2</sup> is usually considered acceptable for high-performance microprocessor applications [31].

#### E) Output resistance

The drain current saturates (output resistance tends to infinity) when the drain voltage is larger than the drain saturation voltage. In practice, *Channel Length Modulation (CLM)* will limit the output resistance

**Figure II.14**: Measured and simulated gate tunnelling current ( $I_G - V_G$ ) characteristics of a MOSFET under inversion conditions. The dotted line indicates the 1 A/cm<sup>2</sup> limit for leakage current [26].

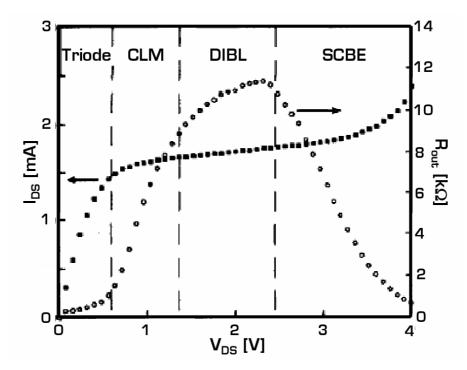

$[r_0 = (\partial I_D / \partial V_D)^{-1}]$  to a finite value at the low-drain-voltage region, while *drain-induced barrier lowering (DIBL)* and *substrate-current-induced body effect (SCBE)* limit the output resistance at moderate and high-drain-voltage regions [32]. A typical drain current and output resistance characteristic is illustrated in figure II.15, in which the regions where these effects dominate are marked. The finite output resistance has important consequences for analog signal processing applications, where the small-signal voltage gain is determined to a great extend by the output resistance [33]. Huang et al. [32] derived the output resistance in the presence of drain-induced barrier lowering and substrate-current-induced body effect and compared these results with experimental data.

#### F) Future trends:

Ever since the concept of MOSFET device scaling has been introduced, and especially in the late 1990s, there have been predictions and speculations of when MOSFET scaling will reach a limit. After

Figure II.15: Typical drain current and output resistance of a MOSFET. W/L = 10/0.43,  $t_{ox}$  = 7.5 nm (adapted from [32]).

the publication of the widely referenced *SIA National Roadmap for Semiconductors* [1], there has been much discussion about being near the limit of CMOS device scaling due to fundamental physics (Meindl [34] summarized the limits of CMOS scaling into a hierarchy of limits due to (1) physics, (2) materials, (3) devices, (4) circuit, and (5) system).

The critical dimensions that need to be engineered are the gate length  $L_g$ , the gate oxide thickness  $t_{ox}$ , the depletion depths under the gate  $x_{depl}$ , the source-drain junction depth  $x_j$ , and the steepness of the source-drain junction. All these parameters have to be scaled together. The gate length is the smallest feature of the MOSFET, patterned by lithography and etching. Employing light with a wavelength shorter than 193 nm presents many difficulties. Currently, there is much debate about how the lithographic requirements will be met; with X-ray, extreme UV, and electron beam, all being considered. Sublithographic feature size may be obtained by etching techniques or sidewall image-transfer techniques. The development of a reliable, manufacturable cost-effective lithographic technique is absolutely essential for the progress in CMOS technology.

As previously mentioned, the electrical thickness of the gate insulator has to decrease with the channel length. Studies of tunneling through thin oxides have shown that silicon oxy-nitride (SiON), which is the current standard gate dielectric, can potentially be thinned down to around 1 nm equivalence oxide thickness (EOT) before the leakage current and the associated dissipation becomes to large to be acceptable [1]. For equivalent thicknesses below this value, thicker gate insulators with a higher dielectric constant than  $SiO_2$  and accordingly SiON, are being considered, to reduce the tunneling current through the gate insulator. However, reliability, thermodynamical stability, and insulator-semiconductor interface properties remain the most important concerns for such new materials.

Depletion depths and junction depths, as well as random fluctuations of device properties, are additional difficulties that have to be faced with

ongoing device scaling. Nevertheless, we will not discuss these topics in detail, for the scope of this works lies on the challenge of integrating new materials with a higher dielectric constant than  $SiO_2$  and accordingly SiON. This opens the door to the next topic of fundamentals within this thesis, where the reader will be introduced into "high- $\kappa$ /metal-gate devices".

# II.2 High-κ/metal gate devices

One key element that made the scaling of Si-based MOSFET-technology for decades possible is SiO<sub>2</sub>. The use of amorphous, thermally grown SiO<sub>2</sub> as the gate dielectric offers several advantages in processing, including a stable (thermal, chemical and electrical), high-quality Si/SiO<sub>2</sub> interface, as well as superior electrical isolation properties. In modern CMOS processing, defect charge densities are in the order of  $10^{10}/\text{cm}^2$ , and midgap interface state densities are around  $10^{10}/\text{cm}^2 \cdot \text{eV}$ . Hard breakdown fields of 15 MV/cm are routinely obtained, and are therefore expected regardless of the device dimensions. These outstanding electrical properties pose a significant challenge for any alternative gate dielectric candidate [35].

Regarding content, chapter II.2 and chapter II.3 follow the excellent textbook *"High Dielectric Constant Materials"* [36], edited by H. R. Huff and D. C. Gilmer. In chapter II.2.3 the author will address "Thin film technology", since this is one of the key processes that will have to be controlled to successfully introduce metal-gate/high- $\kappa$ /silicon capacitors, as well as the experimental basis of this work.

## II.2.1 High- $\kappa$ gate isolator

To overcome the problems summarized in chapters II.1.3 and II.1.4, much work has been done on so-called "high- $\kappa$  dielectrics" that are hoped to feature a reliable alternative to the SiO<sub>2</sub>/SiON systems. Their fundamental advantage is that they provide a physically thicker dielectric for reduced leakage and improved gate capacitance (Review equation II.29: A higher relative dielectric constant  $\kappa$  allows a higher physical thickness *t*, by keeping

the capacitance per area *C/A*, constant). The commonly used variable in this case is the "Equivalent Oxide Thickness (EOT)", which is defined as

$$EOT = t_{eq} = \frac{\kappa_{SiO_2}}{\kappa_{high-\kappa}} \cdot t_{high-\kappa} , \qquad \qquad \text{II.30}$$

and sets the high- $\kappa$  material and SiO<sub>2</sub> in context. Here,  $t_{high-\kappa}$  is the physical thickness of the high- $\kappa$  material, and  $\kappa_{SiO2}$  and  $\kappa_{high-\kappa}$  are the relative dielectric constants of SiO<sub>2</sub> (= 3.9) and the high- $\kappa$  material, respectively.

In the following paragraphs, we will discuss in detail the most important requirements that have to be met to successfully substitute  $SiO_{P}/SiON$  systems. The requirements can be summarized as follows:

#### A) Permittivity, band gap and barrier height

Of course, the dielectric constant  $\kappa$  of the considered dielectric should be noticeably higher than that of SiO<sub>2</sub>. Table II.B lists relative dielectric constants of most commonly investigated oxides and compares them to SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>. In most cases the values of the permittivity cover a range, because the measurements or calculations can be influenced by many factors, such as film thickness, method of film deposition, and local electronic, or chemical structure within the dielectric. It can be seen that in general, atoms with a high atomic number exhibit more electron dipole response to an external electric field, because there are more electrons to respond. Electronic and ionic dipoles, which give rise to the polarizability, are the two main contributions to the dielectric permittivity, and due to this fact the permittivity for oxides with higher atomic number tends to increase with increasing electronic contribution.

Addressing the tunneling process, the permittivity additionally has to be balanced against the barrier height. This is, because the leakage current increases exponentially with decreasing barrier height (and thickness) for electron "direct tunneling transport" [8,35]:

$$I_{DT} = \frac{A}{t_{OX}^2} \exp\left[-2t_{OX} \sqrt{\frac{2m^* q}{\hbar^2} \left(\phi_B - \frac{V_{OX}}{2}\right)}\right], \qquad \text{II.31}$$

where A is a constant,  $t_{OX}$  is the physical thickness of the dielectric (oxide),  $V_{OX}$  is the voltage drop across the dielectric, and  $m^*$  is the electron effective mass in the dielectric. For electrons tunneling from the Si substrate to the gate, the barrier height is the conduction band offset  $\Delta E_C \cong q[\chi - (\phi_m - \phi_b)]$ , and for electrons tunneling the opposite direction, this is  $\phi_b$  (see figure II.6).

Concerning materials with a low barrier height, at applied voltages near the working-voltage, the tunneling current might be dominated by "Fowler-Nordheim tunneling", where a triangular shape of the barrier is assumed [8,9,10].

For highly defective films with electron trap energy levels in the insulator band gap, the current will instead be governed by trap-assisted mechanisms, such as "Frenkel-Poole emission" [8,9]:

$$I_{FP} \cong E \exp\left[-\frac{q}{kT}\left(\phi_B - \sqrt{\frac{qE}{\pi\varepsilon_i}}\right)\right].$$

II.32

Here, E is the electric field and  $\varepsilon_i$  is the insulator permittivity.

In order to obtain low leakage currents, it is evident to find a gate dielectric that has a large conduction band offset value to Si and ideally to other gate materials that might be used. Table II.B summarizes energy band gap  $E_G$ -values, conduction band offset  $\Delta E_C$ -values, and valence band offset  $\Delta E_V$ -values for potential high- $\kappa$  gate dielectric materials. If we compare the values for  $\kappa$  and  $E_G$ , one can observe a trade-off (although there are departures from this trend). In contrast to the general trend of increasing permittivity with increasing atomic number, the band gap of the metal oxides tends to decrease. An intuitive explanation for this phenomenon is that the band gaps of the transition metal oxides, which all

| Material                                                                                                                                                                                                                                                                                   | Dielectric constant: $\kappa$ [–] | Energy<br>band gap:<br><i>E<sub>G</sub></i> [eV] | Conduction<br>band offset to<br>Si: ⊿E <sub>c</sub> [eV]                                                                                                                                                                                 | Valence band<br>offset to Siª:<br>⊿E <sub>v</sub> [eV] |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| SiO <sub>2</sub>                                                                                                                                                                                                                                                                           | 3.9                               | 8.9                                              | 3.1                                                                                                                                                                                                                                      | 4.7                                                    |

| Si <sub>3</sub> N <sub>4</sub>                                                                                                                                                                                                                                                             | 7.4                               | 5.1                                              | 2.2                                                                                                                                                                                                                                      | 1.8                                                    |

|                                                                                                                                                                                                                                                                                            | 9 - 11                            | 6.2⁵, 8.8°                                       | 2.2⁵, 2.8°                                                                                                                                                                                                                               | 2.9, 4.9                                               |

| $Gd_2O_3$                                                                                                                                                                                                                                                                                  | 9 - 14                            | 5.2                                              | -                                                                                                                                                                                                                                        | -                                                      |

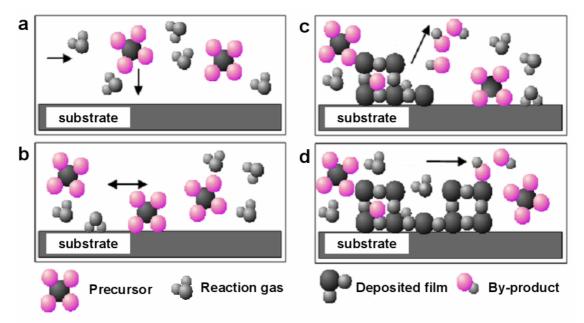

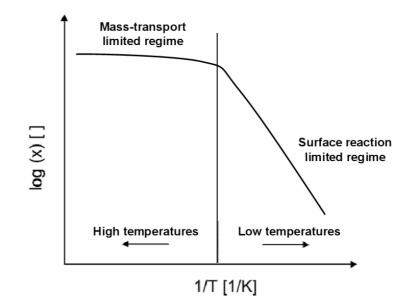

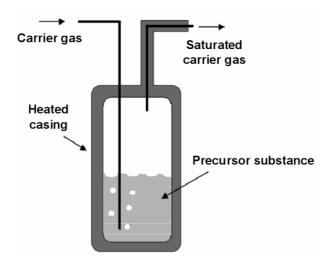

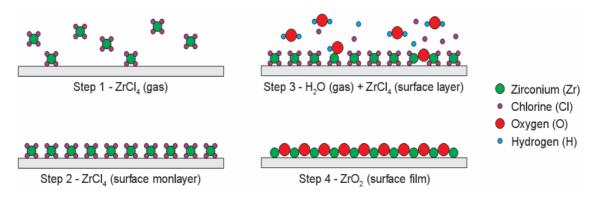

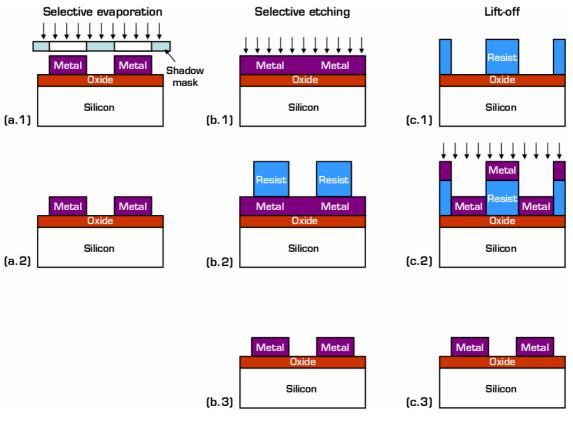

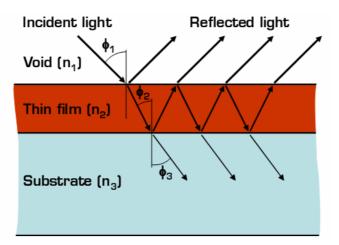

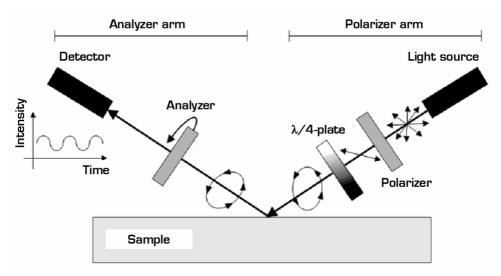

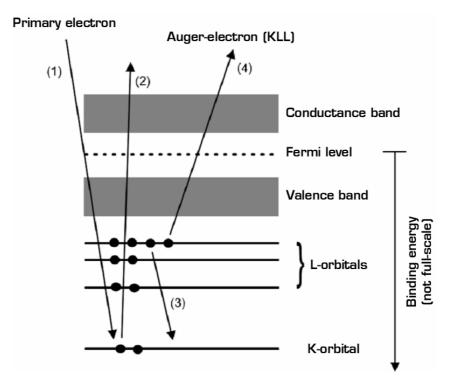

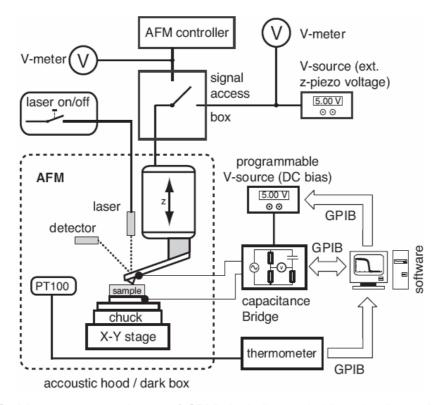

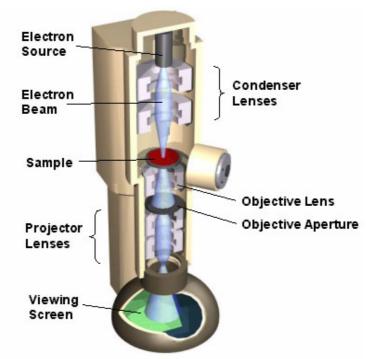

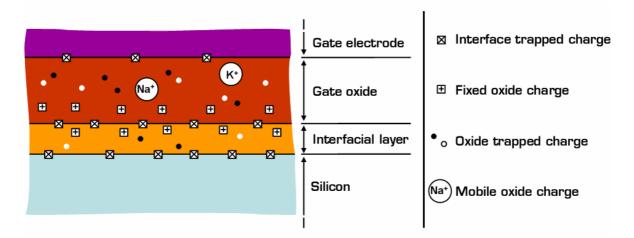

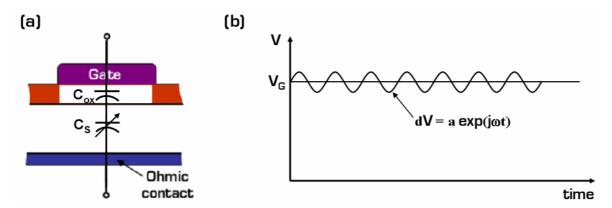

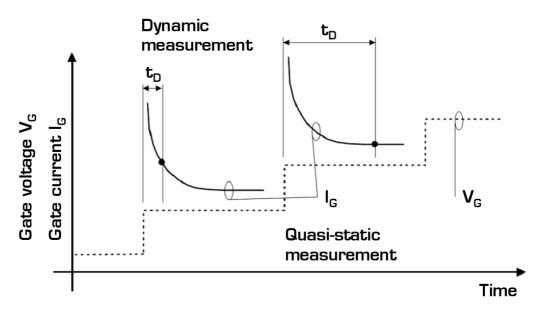

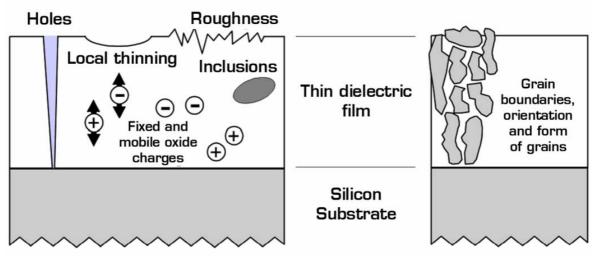

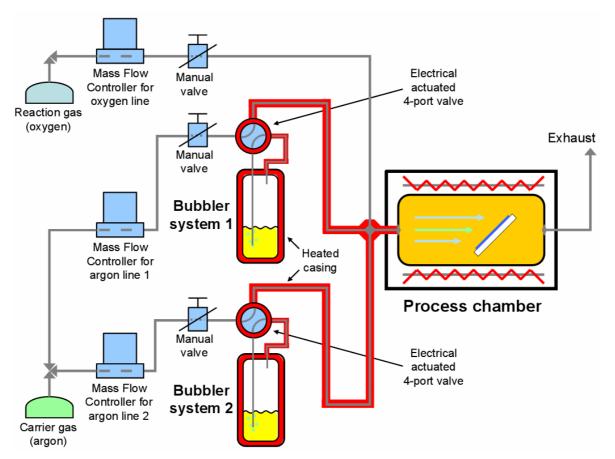

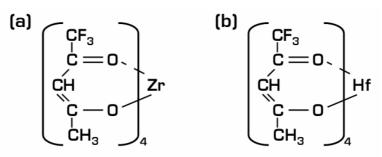

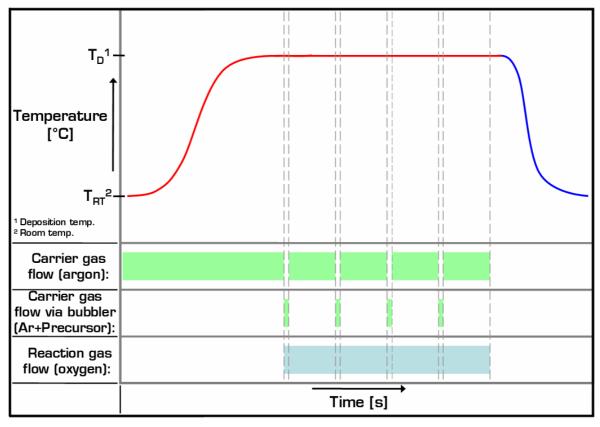

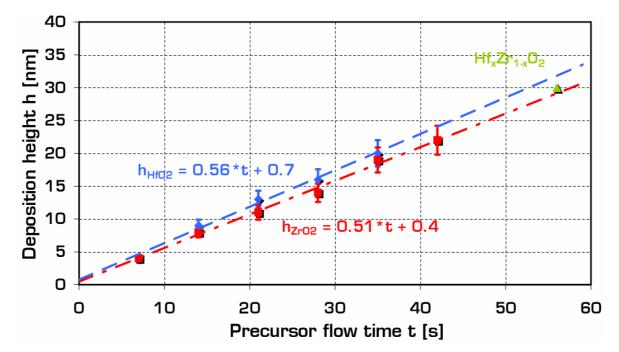

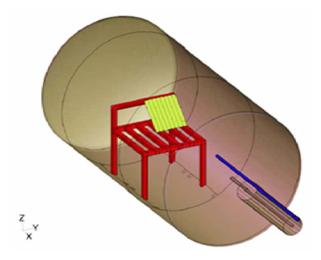

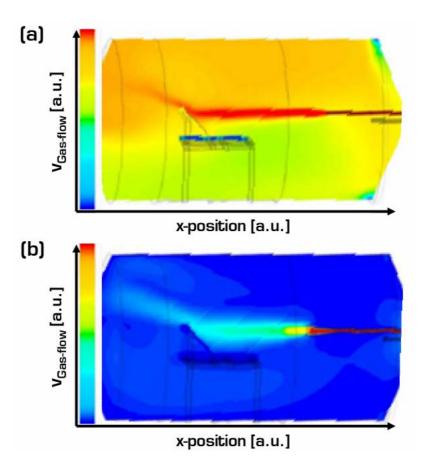

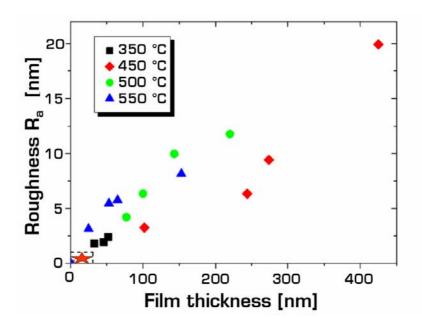

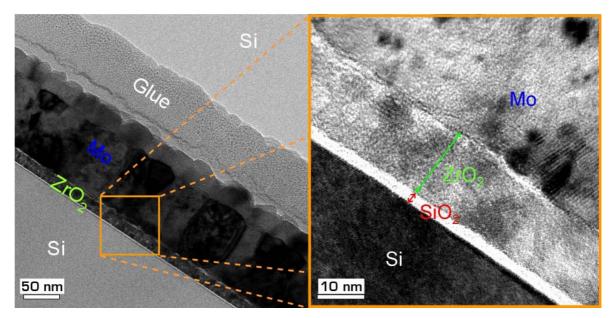

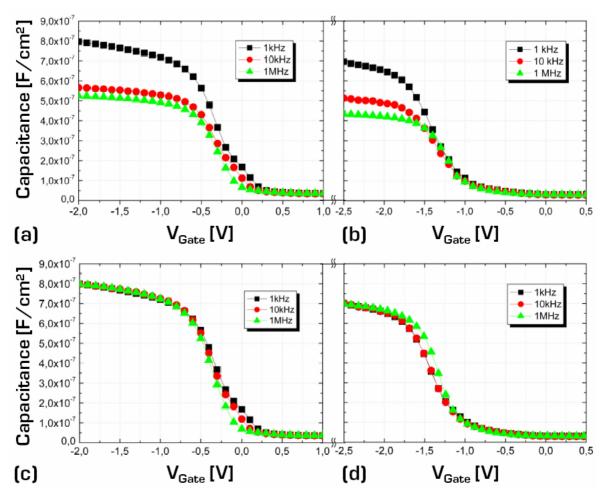

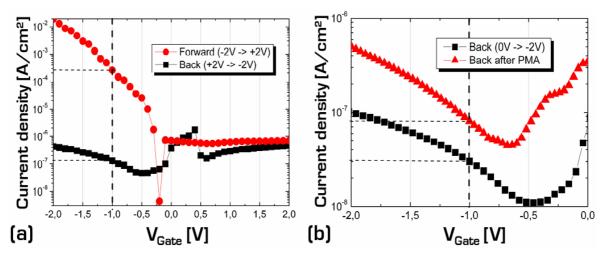

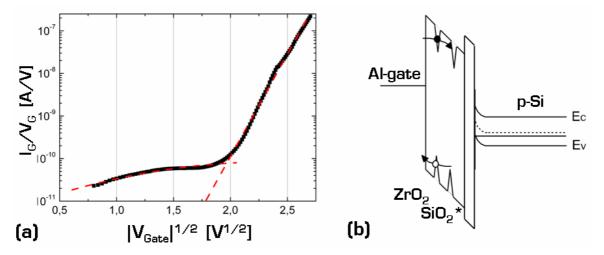

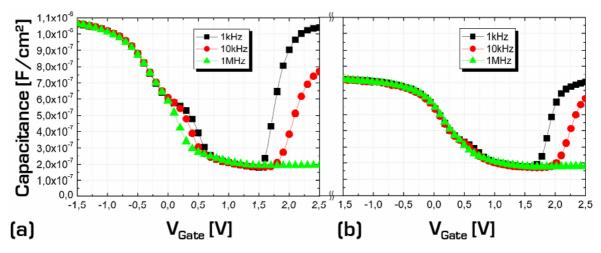

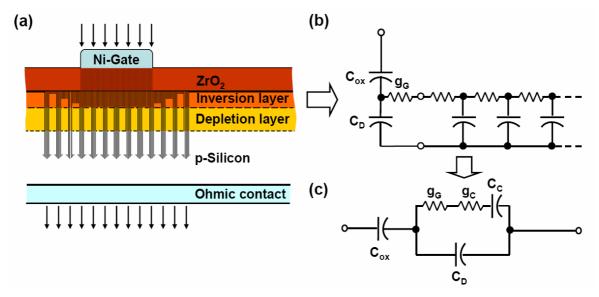

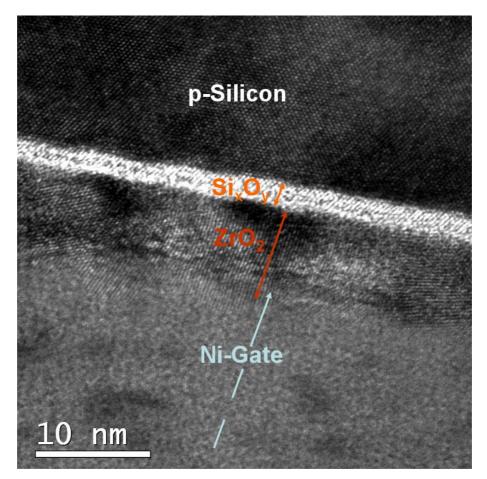

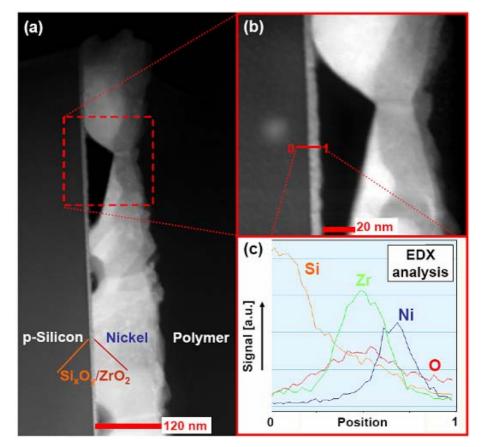

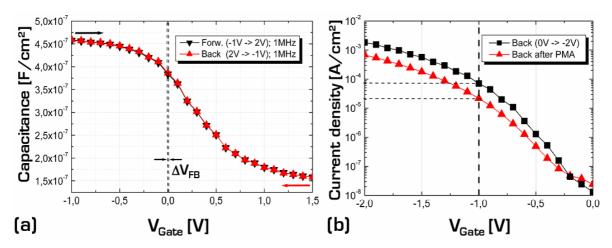

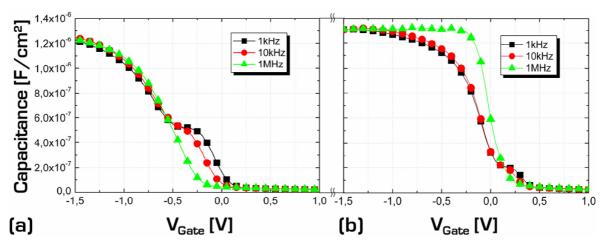

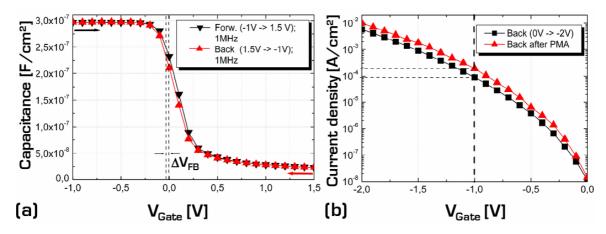

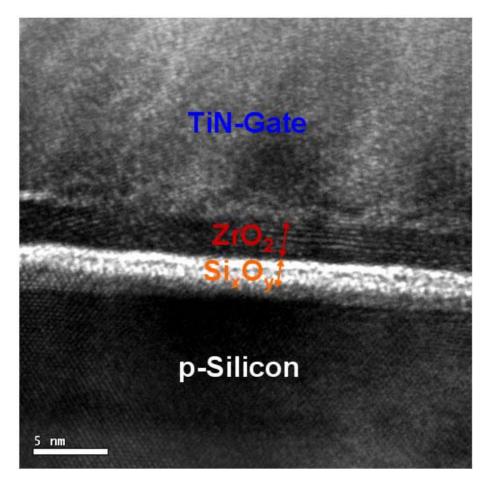

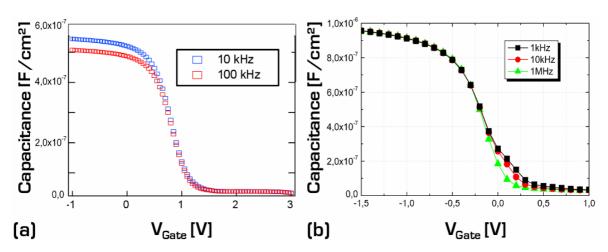

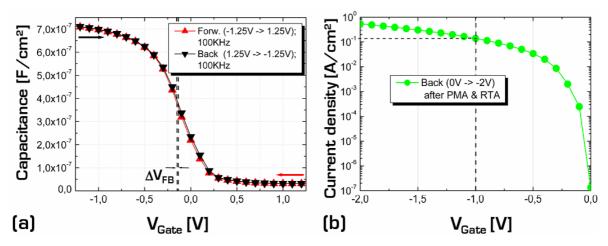

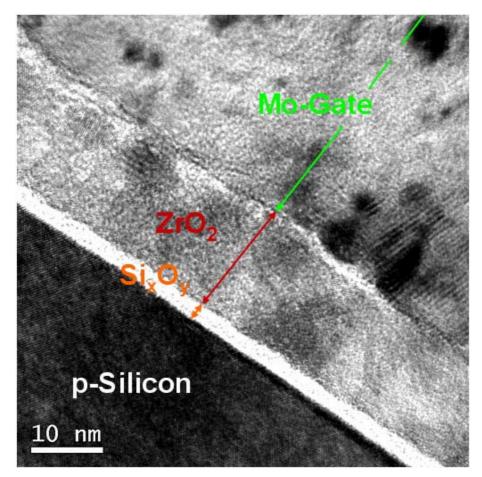

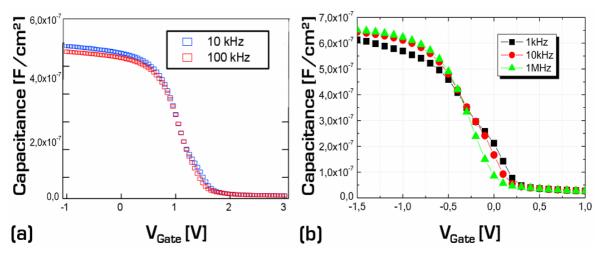

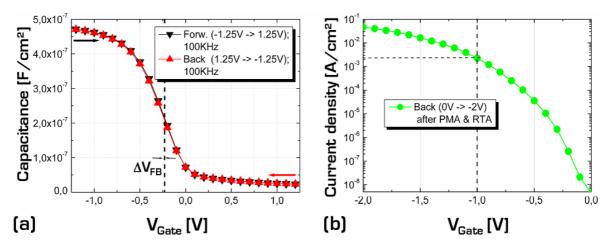

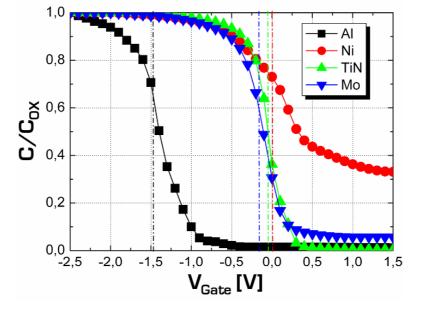

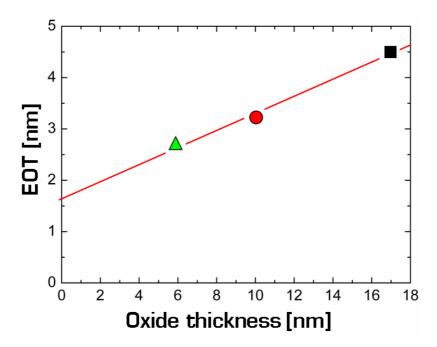

| $Dy_2 O_3$                                                                                                                                                                                                                                                                                 | 11 - 13                           | -                                                | -                                                                                                                                                                                                                                        | -                                                      |