Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

1

# Compilation Techniques for Reducing Energy Consumption of Embedded Digital Signal Processors

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Leitung von

ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall Institut für Computersprachen

Arbeitsbereich für Programmiersprachen und Übersetzerbau

eingereicht an der

Technischen Universität Wien Fakultät für Informatik

von

Dipl.-Ing. Ulrich Hirnschrott 9240416 Halbgasse 26/11 1070 Wien

Wien, im Mai 2005

### Kurzfassung

Die Bedeutung von System-on-Chip und System-in-Package Lösungen im Bereich eingebetteter Systeme hat während der letzten Jahren stetig zugenommen. Aufgrund der steigenden Komplexität eingebetteter Anwendungen und der irregulären Prozessorarchitekturen werden hoch optimierende Übersetzer benötigt, um die hohen Anforderungen an Chipgröße und Leistungsaufnahme zu erfüllen.

Der Energieverbrauch aktueller Prozessoren ist hauptsächlich durch die dynamische Leistungsaufnahme bestimmt. Diese kann durch Minimierung von Speicherzugriffen, Minimierung der Ausführungszyklen und Minimierung der Schaltvorgänge an Bussen reduziert werden. In dieser Dissertation werden Erweiterungen der Registerzuweisung für irreguläre Architekturen vorgestellt, welche die Auslagerungsbefehle reduzieren. Weiters wird eine Programmoptimierung präsentiert, welche die dynamischen Schaltvorgänge am Programmspeicherbus minimiert. Die vorgestellten Techniken wurden für die Architektur des digitalen Signalprozessors xDSPcore implementiert.

Registerzuweisung bildet die Variablen eines Programms auf die Register eines Prozessors ab oder lagert diese in den Speicher aus. Die gebräuchlichste Methode ist das Färben eines Konfliktgraphens, welcher durch Analyse der statischen Lebensdauer von Variablen konstruiert werden kann. Diese Analyse muss die Besonderheiten einer Architektur berücksichtigen. Für die xDSPcore Architektur sind das ein in Bänke geteilter Registersatz, teilbare Register und bedingte Ausführung von Befehlen. Die Beiträge dieser Arbeit sind eine Lebensdaueranalyse unter Berücksichtung bedingter Ausführung und geteilter Register, sowie ein erweitertes Modell des Konfliktgraphens. Beide Techniken sind nötig, um einerseits teilweise Uberschneidungen von Variablen, welche durch nicht orthogonale Befehle entstehen können, zu erfassen und um andererseits präzise Lebensdauerinformation für bedingte Befehle zu erhalten. Zusätzlich wurde eine auf partitionierter Boolscher quadratischen Programmierung (PBQP) beruhende Registerzuweisung implementiert. Dieser Ansatz modelliert Einschränkungen auf Programmvariablen und Auslagerungsentscheidungen durch Kostenfunktionen und Matrizen. Ein PBQP Problemlöser liefert optimale Registerzuweisungen und Auslagerungsentscheidungen. Diese Dissertation trägt die nötigen Kostenfunktionen und Matrizen für xDSPcore bei, welche wiederum geteilte Register und teilweise Überschneidungen modellieren. Die beiden Lösungsansätze werden empirisch verglichen.

Zugriffe auf den Programmspeicher tragen wesentlich zum Energieverbrauch eines Prozessors bei. Dieser kann durch Minimierung der Schaltvorgänge zwischen aufeinander folgenden Speicherzugriffen reduziert werden. Die Schaltvorgänge können durch die Hamming Distanz der binär kodierten Befehlsworte modelliert werden. Der Beitrag dieser Dissertation ist eine Programmoptimierung, welche die Befehlsworte von Funktionen so anordnet, dass eine globale Hamming Distanz der Befehlsworte minimal ist. Dies wird durch Permutation der Befehle innerhalb einzelner Ausführungseinheiten und durch Vertauschen der Operanden bei kommutativen Operationen erreicht. Ein präzises Optimierungsmodell für xDSPcore und die damit verbundenen Algorithmen werden vorgestellt. Im Unterschied zu bekannten Methoden behandeln diese Algorithmen Kanten im Kontollflussgraphen ohne Heuristiken und können auch mit nicht ausgerichteten Ausführungseinheiten umgehen.

If-Umwandlung ist eine bekannte Technik, um Sprunganweisungen aus dem Programm zu eliminieren. Eine Analyse typischer Programme zeigt die Notwendigkeit und Wichtigkeit dieser Transformation. In dieser Dissertation wird eine Implementierung vorgestellt, welche auf eine kleine Teilmenge von Kontrollflussmustern limitiert ist. Weiters werden Abschätzungsfunktionen für maximale Ausführungszeit und Programmgröße vorgestellt, welche während der Transformation verwendet werden, um potenzielle negative Auswirkungen zu vermeiden.

Befehlsanordnung ist eine Technik, um Parallelität auf Befehlsebene auszunützen. Gebräuchliche vorwärts planende Algorithmen leiden an der oftmals zu frühen Einordnung von Befehlen und erzeugen dadurch künstlich Registerdruck. Diese Arbeit analysiert das der Anordnung zugrunde liegende Modell des Datenabhängigkeitsgraphens. Dadurch zeigt sich, dass die Algorithmen adaptiv gestaltet werden müssen, um mit den verschiedenartigen Strukturen der Graphen besser umgehen zu können. Detailverbesserungen an den Anordnungsentscheidungen für Auslagerungsbefehle werden präsentiert.

Ein wichtiger Aspekt auf Ebene des Systementwurfs ist das Untersuchen des architekturellen Gestaltungsraumes. Dadurch wird versucht, den Unterschied in der Effizienz von fest verdrahteten Hardware-Lösungen und programmierbaren Komponenten auszugleichen. In dieser Dissertation wird ein auf Hochsprachen basierender Ansatz namens *DSPxPlore* präsentiert. Dieser erlaubt es die Mikroarchitektur in manchen Parametern so zu skalieren, dass sie den Anforderungen der eingebetteten Anwendung exakt entspricht. Zentraler Punkt von DSPxPlore ist eine Konfigurationsdatei, welche die gesamte Beschreibung der Architektur enthält.

### Abstract

The importance of *System-on-Chip* and *System-in-Package* solutions in the domain of *embedded systems* was steadily increasing during the last years. Due to the rising complexity of embedded applications and irregular processor architectures, highly optimizing compilers are needed to meet the stringent chip area and power dissipation requirements of such platforms.

The energy consumption of current processors is dominated by the dynamic power dissipation, which can be reduced largely by minimizing the number of memory accesses, minimizing execution cycles, and minimizing switching activities on buses. This thesis contributes improvements on register allocation for an irregular architecture which reduce memory accesses and execution cycles, and a post-pass code optimization for minimizing the dynamic switching on the instruction memory bus. The techniques presented in this thesis are implemented in the context of the xDSPcore architecture which will be introduced shortly.

Register allocation maps the program variables to the registers of a processor or spills them to a memory location. The most common technique is coloring an interference graph which is constructed through liveness analysis. Liveness analysis on code for the xDSPcore has to deal with an irregular and banked register file, and with predicated execution. The contributions of this thesis are a predicated liveness analysis on shared registers and an augmented interference graph. Both methods are necessary for modeling partial interferences which arise from non-orthogonal instructions, and for precise liveness information of predicated code. Additionally, a register allocation approach based on partitioned boolean quadratic programming (PBQP) is implemented. This approach models architectural constraints and the problem of spilling decisions by cost functions and matrices. Register assignments and spilling decisions are calculated by a solver that delivers optimal results. This thesis contributes the necessary cost functions for xDSPcore that model shared registers and partial interferences. An empirical comparison of the graph-coloring and the PBQP-based approach is given.

Code memory accesses during *instruction fetch* of the processor make a substantial contribution to power dissipation which can be minimized by reducing the switching activities between successive fetches. Switching activities are modeled by the Hamming distance of the binary encoded instruction words. This thesis contributes a post-pass optimization that finds the code arrangement for a function which yields a globally minimized Hamming distance of all instruction words. This is done through *permuting* instructions of the *execution bundles* and through *swapping* the operands of commutative operations. A precise optimization model for xDSPcore and the associated optimization algorithms are introduced. In contrast to existing work, the algorithms consider control flow edges without using heuristics and can operate on non-aligned execution bundles which can even cross fetch word boundaries. If-conversion is a known technique for reducing the amount of branching instructions in assembly code. The necessity and importance of this transformation is pointed out by analysis of typical algorithms. This thesis presents an implementation which is limited to a small subset of control flow graph patterns and contributes estimation functions for *worst-case execution time* and *code size*. These functions are applied for guiding the transformation in order to avoid negative impacts and interferences with other dependent optimizations.

Instruction scheduling is a technique for exploiting instruction level parallelism in code sequences. Top-down list scheduling algorithms suffer from overscheduling instructions and thus create artificial register pressure. In this thesis, an extensive analysis of the underlying problem model, the *data dependence graph*, is presented. This analysis shows that scheduling heuristics have to be adapted to the particular graph-structures. Refinements on root node selection and on handling spilling instructions are presented.

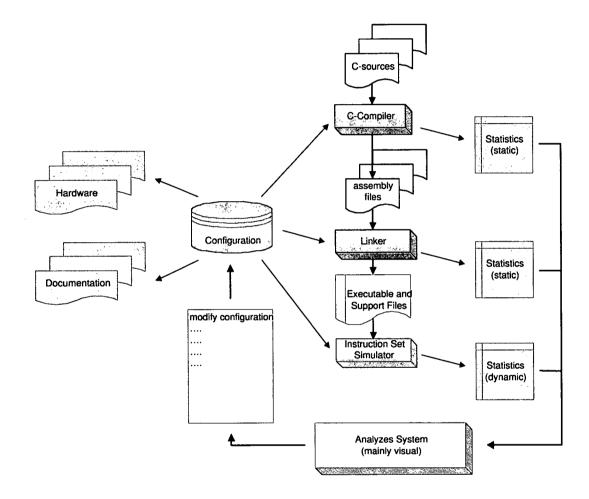

Design space exploration based on a high-level language is an approach of embedded systems design that attempts to close the efficiency gap between dedicated hardware circuits and software programmable components. This thesis contributes a methodology named *DSPxPlore* which allows to scale important micro-architectural features of xDSPcore in order to adapt the processor to the requirements of the embedded application. A unique configuration file contains the entire architectural description and constitutes the central part of this methodology. It is used for setting up the *toolchain* at run time in order to generate and simulate machine code for the currently specified architecture.

# Contents

| 1 | Intr                      | oduction                                                     | 6  |

|---|---------------------------|--------------------------------------------------------------|----|

|   | 1.1                       | Embedded DSPs                                                | 6  |

|   | 1.2                       | Compilers                                                    | 7  |

|   | 1.3                       | Power & Energy                                               | 8  |

| 2 | Tow                       | vards energy reduction                                       | 10 |

|   | 2.1                       | Definitions                                                  | 10 |

|   | 2.2                       | Optimization targets                                         | 11 |

|   |                           | 2.2.1 Physical Capacitance                                   | 11 |

|   |                           | 2.2.2 Supply voltage and clock frequency                     | 12 |

|   |                           | 2.2.3 Switching activity                                     | 12 |

|   |                           | 2.2.4 Time                                                   | 13 |

| 3 | Rel                       | ated Work                                                    | 16 |

|   | 3.1                       | Traditional compiler optimizations                           | 16 |

|   |                           | 3.1.1 Register allocation                                    | 16 |

|   |                           | 3.1.2 If-Conversion & Predicated Execution                   | 18 |

|   |                           | 3.1.3 Instruction scheduling                                 | 19 |

|   | 3.2                       | Power- and Energy-Related Aspects                            | 20 |

|   |                           | 3.2.1 Compiler techniques                                    | 21 |

|   |                           | 3.2.2 Techniques on Operating System and System Design Level | 23 |

|   |                           | 3.2.3 Profiling and Simulation                               | 24 |

| 4 | Tar                       | get architecture                                             | 25 |

|   | 4.1                       | Design objectives and philosophy                             | 25 |

|   | 4.2                       | Example architecture                                         | 26 |

| 5 | 5 Investigated techniques |                                                              | 30 |

|   | 5.1                       | Major contributions                                          | 32 |

|   |                           | 5.1.1 Register allocation                                    | 32 |

|   |                           | 5.1.2 VLIW optimization                                      | 57 |

|   | 5.2                       | Minor contributions                                          | 68 |

|   | -                         | 5.2.1 If conversion                                          | 68 |

| Conclusions |       |                          |    |

|-------------|-------|--------------------------|----|

| 5.3         | Summ  | nary                     | 93 |

|             | 5.2.3 | Design Space Exploration | 88 |

|             | 5.2.2 | Instruction scheduling   | 76 |

### 6 Conclusions

# List of Figures

| 1.1          | General structure of a compiler                               | 8        |

|--------------|---------------------------------------------------------------|----------|

| 1.2          | Trend of power dissipation                                    | 9        |

| 2.1          | Architectural switching on a 16 bit register                  | 13       |

| 4.1          | Design philosophy of xDSPcore                                 | 26       |

| 4.2          | Architecture Overview                                         | 27       |

| 4.3          | Examples for register file accesses                           | 29       |

| 5.1          | Backend tasks and ordering                                    | 31       |

| $5.1 \\ 5.2$ | Sub-tasks of graph-coloring                                   | 33       |

| 5.2          | Sub-tasks of PBQP register allocation                         | 34       |

| 5.3          | Interference graph construction                               | 36       |

| 5.4<br>5.5   | Example assembly code                                         | 37       |

| 5.6          |                                                               | 37       |

| 5.0<br>5.7   | Resulting WIG                                                 | 39       |

|              | Example assembly code with refined liveness sets              | 39<br>39 |

| 5.8          | Augmented WIG                                                 |          |

| 5.9          | Selecting colors from gaps                                    | 40<br>42 |

| 5.10         | 1 0 1                                                         |          |

|              | The PBQP problem formulation                                  | 44       |

|              | Control flow and interference graph                           | 46       |

|              | Example of Reduction                                          | 46       |

|              | RN Reduction                                                  | 47       |

|              | Details of coalescing                                         | 49       |

|              | Illustration of calling conventions                           | 52       |

|              | Maximum reads on data register file                           | 53       |

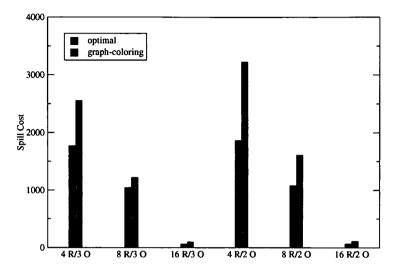

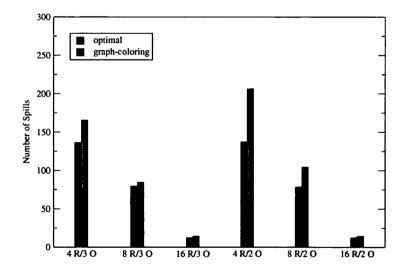

|              | Spill cost comparison                                         | 55       |

|              | Number of spills comparison                                   | 55       |

|              | Instruction sequence and possible xLIW mapping to code memory | 58       |

|              | Illustration of switching heuristic during compilation        | 58       |

|              | Illustration of block alignment                               | 60       |

|              | DP algorithm for local VLIW optimization                      | 62       |

|              | Calculation of the global Hamming distance                    | 63       |

| 5.25         | Total recursive enumeration                                   | 64       |

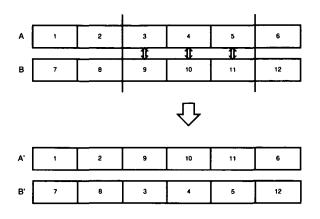

| 5.26 | Illustration of two-point crossover                                                                              | 65 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 5.27 | Genetic Evolution                                                                                                | 66 |

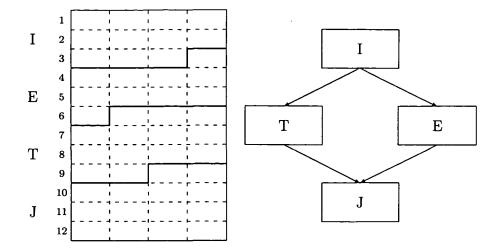

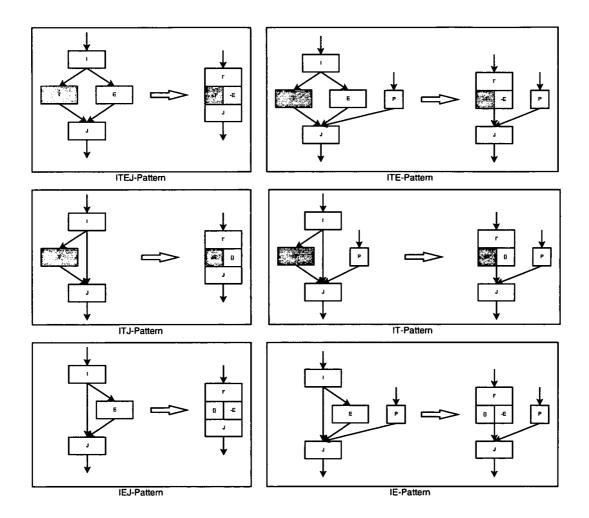

| 5.28 | CFG patterns and transformed hyperblocks                                                                         | 69 |

| 5.29 | An ITEJ pattern using branches or predicated execution                                                           | 70 |

| 5.30 | If conversion algorithm                                                                                          | 72 |

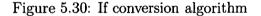

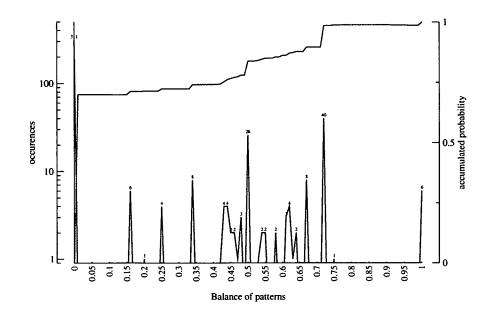

| 5.31 | Occurrence of patterns                                                                                           | 74 |

|      | Balance of patterns                                                                                              | 75 |

| 5.33 | Available resources and sample resource vectors                                                                  | 77 |

| 5.34 | Original scheduling algorithm                                                                                    | 79 |

|      | Original scheduling algorithm                                                                                    | 80 |

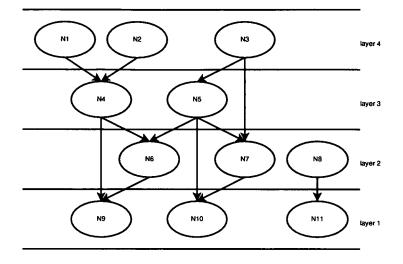

| 5.36 | Layering of a data dependence graph                                                                              | 81 |

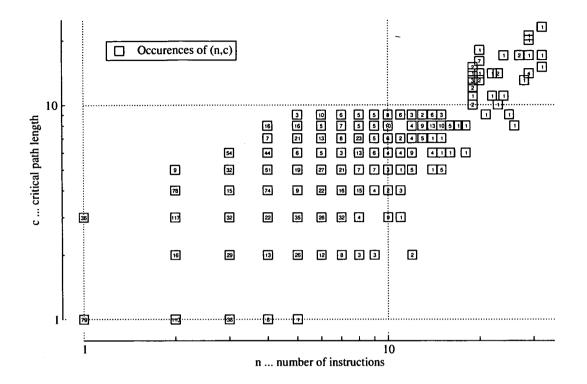

| 5.37 | Histogram of $(n,c)$ pairs $\ldots \ldots \ldots$ | 82 |

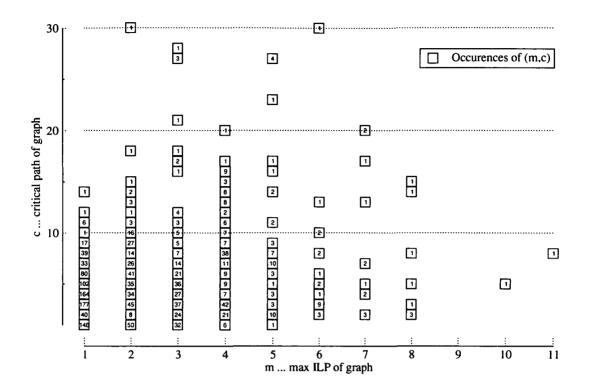

| 5.38 | Histogram of (m,c) pairs                                                                                         | 83 |

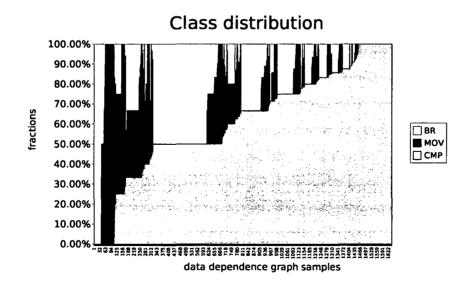

| 5.39 | Distribution of class fractions                                                                                  | 83 |

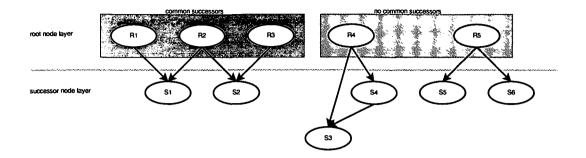

| 5.40 | Common successor root nodes                                                                                      | 85 |

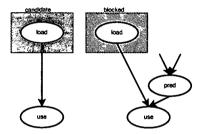

| 5.41 | Spilling loads selection                                                                                         | 85 |

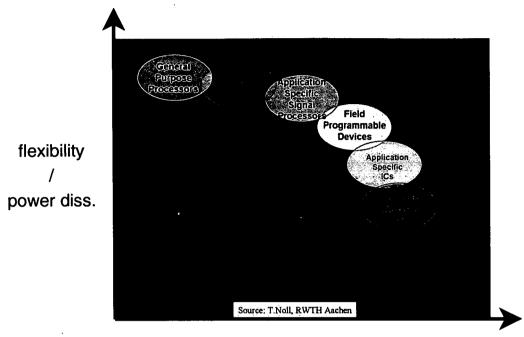

| 5.42 | HW/SW tradeoff                                                                                                   | 88 |

| 5.43 | Overview of DSPxPlore                                                                                            | 90 |

# List of Tables

| 5.1  | Colorability test for example graph 37                                                                              |

|------|---------------------------------------------------------------------------------------------------------------------|

| 5.2  | Register assignment                                                                                                 |

| 5.3  | Register assignment for augmented WIG                                                                               |

| 5.4  | Cost functions for the xDSPcore                                                                                     |

| 5.5  | Cost functions for example 5.7                                                                                      |

| 5.6  | Code transformation for (n-1)-operand instructions                                                                  |

| 5.7  | Number of parallel execution units                                                                                  |

| 5.8  | Averages of Hamming distance reduction                                                                              |

| 5.9  | Optimality of genetic evolution                                                                                     |

| 5.10 | ITEJ Evaluation                                                                                                     |

| 5.11 | Quantitative results of if-conversion                                                                               |

| 5.12 | Basic data dependence graph statistics                                                                              |

| 5.13 | Statistics for MOV, CMP, BR 82                                                                                      |

| 5.14 | Regression analysis for $n \ldots $ 84 |

| 5.15 | Evaluation of scheduling modification                                                                               |

.

# Chapter 1

# Introduction

### **1.1 Embedded Digital Signal Processors**

The continuous growth of the embedded systems market in recent years and the increasing complexity of embedded software are a big challenge: Heterogeneous hardware and software platforms have to be handled by the system designers, emerging topics like *Ubiquitous Computing* demand for new solutions. In parallel, the energy budget for mobile devices is not growing, whereas upcoming audio, imaging, and video techniques require highest computing power. In contrast to this evolution, the product development cycles are getting shorter and shorter.

Decreasing feature size and rising cost pressure lead to highly integrated solutions where a complete system is realized on one die (System-on-Chip, SoC) or in one package (System-in-Package, SiP). Computing intensive algorithms are partly mapped to hardware accelerators to meet the power dissipation and chip area requirements. *Embedded Digital Signal Processors (DSP)* are used for parts of the application with lower data rates which have to be kept flexible due to runtime adaption requirements and changing standards, whereas micro-controllers and protocol processors are used for control and protocol parts of the application.

The digital signal processors of the application are facing specific requirements and can therefore be considered as *application specific processors* with the following distinctive properties:

- fixed-point arithmetic

- accumulator registers supporting higher precision for internal calculation

- multiply-accumulate instructions for filter structures

- zero-overhead hardware loop instructions

- dual (multi) banked data memory

- complex addressing modes like auto-increment and -decrement, moduloaddressing, bit-reversed addressing, etc.

- explicit instruction level parallelism (VLIW)

- single instruction, multiple data parallelism (SIMD)

- predicated execution

Due to these architectural features, DSPs are considered as compiler-unfriendly, and therefore existing compilers for DSPs do not attain the necessary code quality in terms of performance and especially code size. Therefore most of today's application code for DSPs is still written in assembly code in order to meet the stringent chip area and performance requirements.

With increasing system complexity and the upcoming of more powerful and complex DSP core architectures, writing assembly code manually is not longer feasible. Additionally, assembly code suffers from its lack in portability to other architectures. Therefore the necessity for having highly optimizing compilers is given. Further on, the compilation, linking, and simulation tools (the *toolchain*), have to integrate smoothly into existing system design flows.

### **1.2** Compilers

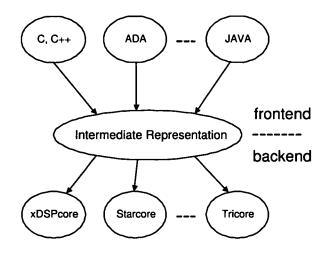

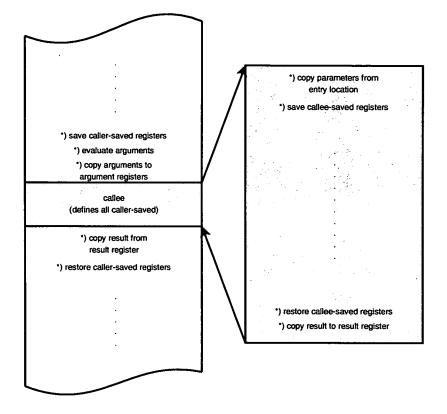

Compilers belong to the fundamentals of computing science. They translate high-level language programs into executable machine code. Usually a compiler is divided into two parts: The *frontend* is responsible for reading a program, transforming it to an intermediate representation, and performing hardware independent optimizations. The *backend* transforms the intermediate representation to machine code, doing machine specific optimizations. Figure 1.1 shows a general structure of a compiler for different input languages and different target machines.

Traditional optimizations done in the frontend of the compiler include dead code elimination, constant propagation, function inlining, common sub-expression elimination, strength reduction, induction variable elimination, etc. The major optimizations in the backend part are instruction selection, instruction scheduling and register allocation. This thesis discusses design and implementation of backend optimizations for a digital signal processor architecture named xDSPcore. These optimizations are built upon the frontend of the *Open Compiler Environment (OCE)*. The OCE was developed by Atair Software GmbH, Vienna, Austria.

Figure 1.1: General structure of a compiler

### 1.3 Power & Energy

The traditional focus of compiler optimizations was improving the execution time of programs. For todays' embedded processors, *code size* is of significant importance as well, because it highly impacts silicon area and therefore production costs. Prior research has found many approaches and solutions so that these criteria can be solved to a satisfying extent.

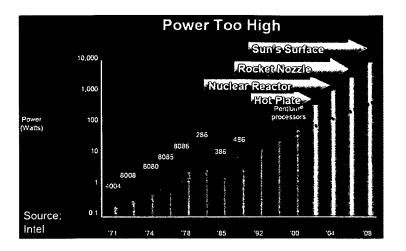

In recent years, power dissipation raised as another dimension in the optimization space. The increased power dissipation causes heavy thermal problems. Special packaging and cooling techniques had to be developed in order to overcome those problems and to keep systems reliable. Current desktop processors seem to have reached the critical point in thermal density. Without cooling measures, they would not even be operable any more. Only very careful system design, mainly seen at laptops and notebooks, allows un-cooled operation. Figure 1.2, originally published by Intel around 2000, shows the trend of power dissipation in recent years and further emphasizes the related problems.

This picture illustrates that new ideas are required to overcome the increased power dissipation of new generation processors. Applications based on embedded systems do not draw such a drastic picture like the standalone processors of the desktop world. Nevertheless, it is reasonable to look at such a picture, as it gives a good indication for the problem.

### Organization of this thesis

Chapter 2 introduces the reader to the field of energy consumption of CMOS technology driven computing, and figures out the optimization opportunities. Chapter 3 provides an overview of related work. Chapter 4 describes the target

Figure 1.2: Trend of power dissipation

architecture which has been considered within this thesis. The main body of this thesis is covered in Chapter 5, which is divided into two parts: The first part presents extensions to register allocation for irregular architectures and an optimization to reduce switching activities on the instruction memory bus. The second part describes some minor improvements of if conversion and instruction scheduling, and also introduces a design space exploration methodology. Chapter 6 concludes this thesis and gives an outlook on further work to be conducted in the future.

# Chapter 2

# Towards energy reduction

The rising computational requirements of current embedded software and signal processing algorithms result in raised energy demands. Factors like packaging costs, chip area, voltage and clock supply are also tightly connected to the terms *power dissipation* and *energy consumption*. This asks for new power and energy optimizations to be investigated.

Before developing such optimizations, it is necessary to identify the main contributing factors and to clarify the technical terms. What else has to be stated here is, that only the contribution of the digital signal processor and its attached memories is considered within this thesis.

### 2.1 Definitions

The terms *power dissipation* and *energy consumption* have already been stated several times. The following paragraphs give definitions for both of them, mostly taken from [7]. However, hardware experts may find some slight inaccuracies, but the definitions are sufficiently accurate for software optimization models.

Equation (2.1) shows the main three sources of power dissipation in current CMOS technology.

$$P_{total} = P_{leakage} + P_{short} + P_{dynamic} \tag{2.1}$$

$P_{leakage}$  is the power which is dissipated through leakage current that arises from substrate injection and sub-threshold effects. It is primarily determined by fabrication technology considerations.  $P_{short}$  comes from the direct-path short circuit current, which arises when both NMOS and PMOS transistors are simultaneously active.  $P_{dynamic}$  comes from charging and discharging of capacitive loads due to logical changes. From these facts and as stated more precisely in [7], it becomes apparent that leakage and short circuit current can be handled only during hardware design and implementation, whereas dynamic switching power widely depends on the software running on the system. Therefore, the dynamic power has to be considered in more depth.

$$P_{dynamic}(t) = \frac{1}{2} C V_{dd}^2 f_{cl} D(t)$$

(2.2)

Equation (2.2) shows the factors which contribute to the dynamic power dissipation. C is the switched capacitance,  $V_{dd}$  the supply voltage,  $f_{cl}$  the clock frequency and D(t) the density of bit transitions (i.e. switching activity in the current hardware state).

$$E_{dynamic} = \int P_{dynamic}(t) \ dt \tag{2.3}$$

In general, energy is the product of power and time (E = Pt) as can be read in physics textbooks. As indicated in Equation (2.2), power dissipation is a function in time. Therefore, energy consumption has to be calculated through integration as stated in Equation (2.3).

At first sight, the optimization objectives can be easily deduced from these equations. Any reduction of either of the factors results in a reduction of power dissipation and thus reduces the amount of consumed energy. However, the factors are not completely independent and only careful analysis and integral optimization techniques will lead to an energy consumption optimized embedded system.

### 2.2 Optimization targets

The following sub-sections will discuss how each of the contributing factors can be tackled and how those are particularly related to each other.

#### 2.2.1 Physical Capacitance

The switched capacitance is mostly determined through the low-level circuit design and therefore seems to be out of scope for software optimization. Nevertheless, the capacitances of the different hardware building blocks range through a wide spectrum. As an example, external buses connecting memories and ALU generally have considerably higher capacitances than ALU internal blocks. This makes memory accesses costly in terms of energy.

From the statements above, it becomes apparent that reducing memory accesses also leads to a reduction of energy consumption. Traditional compiler optimizations already focus on optimizing *data* memory accesses, but mainly motivated from the perspective of locality in memory hierarchies. Apart from that, *program* memory accesses occur more often than data memory accesses and therefore have to be optimized as well.

Additionally, memory accesses can even be optimized on application level through carefully choosing suitable algorithms (and implementations) amongst the available alternatives. System engineers are expected to tend towards low memory throughput and footprint algorithms, which maybe have higher computational costs, but are "cheaper" in terms of energy overall. Only careful system analysis and profiling can deliver the right answers in those matters.

#### 2.2.2 Supply voltage and clock frequency

The quadratic contribution of supply voltage promises large energy savings by voltage reduction. However, voltage and clock frequency cannot be considered isolated from each other, because reducing one induces a reduction of the other.

On the hardware level, each of the required voltage levels and clock frequencies have to be implemented and supported. This can eventually lead to some overhead which has to be payed. If a multi-voltage supply is already implemented on the embedded system, then running the core with different voltage levels is possible with only little hardware overhead. Otherwise, additional hardware blocks like on-chip DC-to-DC converters or Low Dropout Regulators (LDO) which deliver the required voltage levels have to be provided. These additional blocks itself cause additional power dissipation and especially on-chip LDOs may lead to thermal problems as well. The energy savings on the core through reducing its supply voltage may thus be nullified. Therefore this efficient method can only be applied successfully under careful application and system analysis.

Another problem is the transition between different voltage and frequency settings. This takes a considerable amount of time, during which the core does not contribute to the system performance. Additionally, voltage and frequency can not be reduced arbitrarily. Hard real-time requirements demand task completion within a strict deadline. Overly aggressive voltage and frequency reduction can lead to a potential violation of such a deadline.

In spite of those drawbacks, voltage reduction/scaling is an important optimization opportunity for low-power systems. It is most promising, when implemented in a real-time operating system on task level, but can also be taken to a finer granularity.

#### 2.2.3 Switching activity

Switching activity is caused by charge and discharge of capacitors during changes between the logical states 1 and 0. In contrast to technology related power saving modes, switching activity is an issue which can be directly influenced by software development.

Switching activity is caused by charging and discharging of capacitors due to changes in logical state  $(0 \rightarrow 1, 1 \rightarrow 0)$ . Therefore it is directly influenced by the executed code and thus is a major optimization target. Optimizations have to

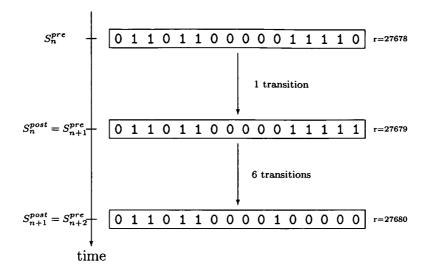

Figure 2.1: Architectural switching on a 16 bit register

focus on architectural features which are visible to the software layer, for example registers and memory buses.

Modeling the architectural switching activities is straight-forward. Each execution cycle n is divided into two states  $S_n^{pre}$  and  $S_n^{post}$ . For each of the architectural features, internal values in  $S_n^{pre}$  and  $S_n^{post}$  are represented through bit vectors  $\vec{B_{pre}}$  and  $\vec{B_{post}}$  ( $\vec{B} = b_0 b_1 \dots b_n | b_i \in \{0, 1\}$ ). Calculating the Hamming distance  $D(\vec{a}, \vec{b}) = \#\{i | a_i \neq b_i\}$  (that means the number of differing bits in  $\vec{a}$  and  $\vec{b}$ ) of  $B_n^{pre}$  and  $B_n^{post}$  gives the number of bit transitions within this cycle.  $S_{n+1}^{pre}$ of the next cycle is then assigned to  $S_n^{post}$  of the current one. Figure 2.1 depicts a 16 bit register to illustrate architectural switching activity.

The Hamming distance is no exact metric for the *absolute* amount of energy that is consumed in an execution cycle. But it delivers an adequate and consistent model for creating objective functions of energy optimizations. Whenever the Hamming distance of two consecutive states is reduced, less energy will be consumed.

#### 2.2.4 Time

Reducing *task completion time* leads to a reduction of energy consumption. The task completion time depends mostly on the number of execution cycles (computations) a task needs for completion and on the clock frequency of the system. Thus, a smaller cycle count and a higher clock frequency leads to a shorter task completion time. Admittedly, this is a rather simple but indeed practical model.

As can be seen from Equation (2.2) and Section 2.2.2, increasing clock frequency is counterproductive in terms of power and therefore compensates the savings from reduced task completion time. Nevertheless, in certain circumstances, where a processor has several predefined power states, it may be beneficial to run a task at maximum performance and then switch the processor to a low-power profile (or turn it off completely). Such techniques are similar to those mentioned in Section 2.2.2 and will be discussed in Section 3.2.2.

As a rule of thumb, it can be claimed that a run time optimized program is also energy optimized (with few exceptions [8]). Minimizing the run time of a task is a traditional domain of compiler optimizations. Lots of source code analysis and target code synthesis techniques have been explored and are still under investigation. Most of these techniques focus on minimizing the average case execution time (ACET). While ACET of DSP algorithms is still an important quality criterion on code optimizations, worst-case execution time (WCET) and its analysis becomes an additional and crucial factor in hard real time systems. Therefore compiler optimizations in the real time domain have to obey additional objectives:

- WCET minimization

- code predictability

The first one directly affects real-time task scheduling. A reduced WCET results in larger schedule slacks and thus gives more freedom in voltage scaling. The second objective mainly targets at the quality of WCET analysis results. If the execution behavior of machine code is predictable, then the estimates of WCET have closer confidence margins. Section 5.2.1 and [9] cover these aspects in more detail. The previous pages have given a short survey on the different topics related to energy consumption. The most important optimization targets have been identified and shortly classified regarding at which level the optimizations have to take place: *Physical capacitance* is mostly determined through hardware design, but can be regarded from the software layer in certain aspects. Building blocks with high capacitances (buses, memory) have a larger potential for energy reduction than those with lower capacitance (datapath). *Supply voltage* and *clock frequency* are overall system related topics and can be optimized on operating system level through *voltage scaling*. *Switching activity* depends mostly on the instructions and instruction sequences that are executed on the processor. It can be minimized by reordering of instructions and a careful choice of registers and addresses at compile-time. *Execution time* depends on clock frequency and the number of execution cycles and thus has to be considered from both real-time and code optimization aspects.

This diversity of topics gives the opportunity to deal with power and energy aspects on different software layers. Depending on system domain and context, appropriate models for optimization guidance have to be deduced. As the title of this thesis indicates, the main techniques which have been investigated in this thesis are in the context of an embedded DSP core, the architecture of which will be briefly summarized in Chapter 4. Section 5.1 focuses on compilation techniques that reduce execution time, data memory accesses, and switching activities on the instruction memory bus. A considerable amount of work on compiler supported application analysis and design space exploration has been carried out and is described in Section 5.2.3.

Due to this narrow domain, optimization models can be kept relatively simple. Missing details from system and implementation level make it unnecessary to include detailed power and energy estimates into the compilation toolchain. Key figures like *code size*, *execution cycles*, *bit transitions on memory buses*, number of *memory accesses* (both data and code) are sufficient and serve as main optimization objectives. Nevertheless, this does not relieve the tools from 'knowing' how each of these factors impact energy consumption.

# Chapter 3

# **Related Work**

This chapter is divided into two parts. The first part covers traditional compiler optimizations which served as starting points for this thesis' contributions. The second part discusses work which has been carried out in the closer context of power and energy topics.

### **3.1** Traditional compiler optimizations

Compiler research focused largely on techniques for optimizing the execution time of programs. The next sub-sections will introduce some existing techniques which are relevant for this thesis.

#### 3.1.1 Register allocation

Register allocation is of vital importance in optimizing compilers. In general, compilers use an internal program representation which assumes an unlimited number of available registers. Register allocation maps these so-called *symbolic registers* (or live-ranges) to physically available hardware-registers of the target architecture. Depending on its scope, a classification into local, global, and inter-procedural register allocation is done. This work focuses on global register allocation. Details on local and inter-procedural register allocation can be found in [10] and [11, 12, 13], respectively.

The most common technique for solving register allocation is based on graph-coloring and was first introduced by Chaitin [14]. Based on global liveness analysis, an *interference graph* is built. For each symbolic register, a node is inserted in the interference graph. Whenever two symbolic registers are live at the same time, an edge between their representing nodes is inserted. If this graph can be colored with k colors (k is the number of architectural registers), this coloring model is a valid register assignment for the symbolic registers. If no such coloring can be found, some of the symbolic registers have to be spilled to data memory.

Spilling means, that after each definition point of the symbolic register, its value has to be stored to memory, and before every use of the symbolic register, the value has to be re-loaded from the spill location again.

Coloring the graph can be done through graph simplification. Nodes with a degree less than k (these are trivial to color) are removed from the graph and put onto a stack repeatedly. When the empty graph remains, the nodes are reinserted into the graph in stack order and assigned an available color. When the simplification leaves a non-empty graph, spilling candidates have to be chosen heuristically and the corresponding spill code has to be inserted. Then the whole process starts again with building the interference graph, which now is less constrained and therefore more likely to be colorable.

Briggs [15] improves this coloring scheme by delaying the spill decision to the reinsert phase. This benefits from the fact, that nodes of significant degree can be colored when two adjacent nodes have been assigned the same color. This technique is called *optimistic coloring*. Further refinements of Briggs are presented in [16, 17]. A technique called *rematerialization* is introduced. Briggs points out that for certain symbolic registers, the value often can be easily recomputed. Therefore it is beneficial not to spill those values, but rather insert appropriate instructions for re-computation if necessary. Other improvements introduced consider closeness of use-points when inserting spill code. Whenever two use-points of a live-range are close, this live-range is kept in register instead of being spilled and re-loaded.

A sub-problem of register allocation is *coalescing* of copy-related symbolic registers (source and destination operands of copy instructions). Whenever these registers are assigned the same color, the copy instruction is redundant and can be eliminated. Chaitin's allocator performs aggressive coalescing, where every non-interfering pair of copy-related symbolic registers is coalesced to a single live-range. This may impair colorability. Therefore Briggs suggested conservative coalescing, where two registers only are coalesced, if it is guaranteed that the new live-range is not spilled. George [18] suggests a method called *iterated coalescing*, where coalescing and graph simplification is done iteratively. A superior approach called *optimistic coalescing* is presented by Park in [19]. Positive and negative impact of coalescing are elaborated in detail by showing examples for improvement or degradation of colorability. It is shown that the conservative approaches of Briggs and George do not benefit from the positive impact. The optimistic approach therefore performs aggressive coalescing on an optimistic register allocator. When a live range xy becomes an actual spill, it is split into two live ranges x and y again, recovering the original edges of the interference graph. It might now be possible to color x or y or both, because the degree of the nodes in the graph is likely to be reduced.

A considerably different approach to register allocation is presented by Chow [20] and is *called priority-based coloring*. Different to a Chaitin-style allocator, this approach assumes live-ranges to reside in memory at first. The register

allocator calculates which live-ranges are most profitable when kept in a register. The order in which live-ranges are assigned registers is determined by a priority function that is based on the control flow graph and a cost model for memory loads and stores. This approach does not need an iterative step and therefore is faster for heavily constrained interference graphs. Several internal assumption of this approach (like reserving registers for temporal values introduced by the code generator) make this approach problematic for embedded processors, where register resources are scarce. The remainder of this work will focus on graph-coloring techniques, which are superior in this sense.

The graph-coloring approach is best-fitted for RISC machines with a regular general-purpose register file. For irregular architectures as often seen for embedded processors, some modification are necessary for making graph-coloring work. Briggs [21] and Smith [22] introduce similar techniques for coloring register pairs. Register pairs allow to combine two single precision registers two one of double precision. These two registers must be adjacent and aligned. Briggs solves this by introducing multi-edges in the interference graph. Smith puts weights on the nodes. Both approaches model the additional constraints through the colorability property of the nodes in the graph. Smith recently published some more extensions to his work in [23].

Other work which focuses on irregular architectures is done by Runeson [24]. A more complex colorability test, called  $\langle p, q \rangle$ -test is introduced. This approach is superior to those of Briggs and Smith as it models a larger range of irregularities.

All these approaches for handling irregularities suffer from the fact that it is necessary to change the fundamental model of the interference graph and its colorability test.

An approach for *optimal* register allocation is proposed by Goodwin in [25] and is based on 0-1 integer programming. An analysis module analyzes the control flow graph of a function, where register allocation decisions have to be made. These points are assigned a *register allocation action* and decision variable. Actions can be such like *define register assignment, keep register assignment, load from memory, store to memory.* A '1' in the decision variable indicates that this action is taken, '0' means not taken. The decision variables and associated spill-code overhead for each of them are used to formulate a 0-1 integer program, which is then solved using a standard solver. Kong [26] presents an extension to this approach which focuses on irregular architectures. Several classes of irregularities are identified and proper cost models for handling them are introduced.

#### 3.1.2 If-Conversion & Predicated Execution

*Predicated execution* is a technique that helps on transforming control dependencies into data dependencies through *if conversion*. In predicated execution, the execution of instructions depends on a logical expression called *guard*. The in-

struction is only executed if the run time value of the guard is *true*. The original motivation for this transformation is handling (conditional) branches in loop vectorization. Branches in general make the execution of instructions d at the branch target dependent on the execution of the branch b itself. Therefore, instruction d are called *control dependent* on b. These control dependencies impose limitations on loop vectorization and scheduling. For each of those control dependencies, a logical expression (from branch conditions) is derived and assigned as a guard to the dependent instruction. Therefore, the control dependence is transformed to a data dependence and can be handled more easily during loop vectorization and instruction scheduling.

The fundamentals of predicated code and if-conversion were introduced by Allen [27]. Park [28] presented a refined transformation with optimal predicate calculation and assignment. Mahlke [29] points out several short-comings of unconstrained if-conversion on unbalanced control flow regions and with speculative execution. A structure called *hyperblock*, which consists of a set of predicated blocks and has a single entry but multiple exits, is introduced to overcome these problems. August [30] points out further inherent problems of if-conversion and presents a refined version of hyperblock selection. It is based on *partial reverse if-conversion* which is used to keep the balance between control-flow and predication.

Work presented in [31, 32, 33] focus on the impact of predicated code onto other code analysis techniques like register allocation. Several modifications and enhancements of existing algorithms are shown.

#### 3.1.3 Instruction scheduling

Scheduling is a technique that reorders instructions so that maximum instruction level parallelism is exploited and thus execution time is minimized. It is a crucial optimization for pipelined architectures, where data dependencies or resource constraints between instructions can cause hazards which would lead to pipeline stalls and performance degradation. For super-scalar architectures, an order of instructions has to be determined which reduces such stalls. Parallelization of the instructions will be done implicitly by the hardware. Scheduling for VLIW architectures needs a more complex approach because it has to be specified explicitly which instructions are executed in parallel. Nevertheless, both strategies have to model architectural resources which may cause hardware contention. This is mostly done by *reservation tables* or *resource vectors*.

Scheduling can be done on local scope (basic blocks) or global scope (whole function). Global techniques offer a better exploitation of instruction level parallelism but often suffer from the drawback of enlarged code size due to code duplication or compensation code. This is barely acceptable for embedded systems, where code size of the program significantly influences chip area. The remainder of this work will focus on local scheduling, more details on global scheduling can be found in [34, 35, 36, 37, 38].

In *list scheduling* as presented in [39], a directed acyclic graph for the instructions of a basic block is constructed. This graph expresses the scheduling constraints between the instructions. A topological sort of this graph then yields the schedule. This sort is determined through several heuristics, for example root nodes with the longest path to the leaves have to be scheduled first. Warren [40] presents refinements on selecting the next root node to be issued and on minimizing liveness.

A considerably different approach is *software pipelining*. In software pipelined loops, the execution of the next loop iteration is started before the prior one has completed. This yields a better utilization of functional units during execution of loops and thus improves performance. Lam [41] showed a basic approach how to implement software pipelining in compiler optimization by making use of an iterative approach for scheduling cyclic graphs. A technique called *hierarchical reduction* is introduced, which allows software pipelining in presence of conditional statements.

Rau [42] presented another algorithm for software pipelining which is called *iterative modulo scheduling (IMS)*. This algorithm searches for a schedule where a new loop iteration is initiated after a pre-defined number of cycles, called initiation interval. IMS begins with a *minimum initiation interval*, which is determined by resource- or recurrence-constraints and tries to build a schedule. If no solution can be found, the initiation interval is increased and the scheduling process is started again.

Bala [43] presents an efficient method to perform complex resource contention checks during scheduling, based on finite state automatons. It is more time- and space efficient than prior techniques which are based on reservation tables.

Liu [44] presents a near-optimal approach to instruction scheduling. The method is based on totally enumerating possible schedules with pruning the search space if it can be proved, that no feasible schedule can be found in the current enumeration candidate.

### **3.2** Power- and Energy-Related Aspects

In recent years, more and more scientific work has been carried out in the field of low-power and power-aware software techniques. While there have been some interesting and fundamental insights, the field is still rather young and sometimes controversial. A profound knowledge of the underlying hardware technology and a precise context of the presented techniques is necessary to fully understand and evaluate the consequences of the presented work. This section only presents a selection of some of the relevant topics in order to show the diversity and complexity of matters. It does not cover the particular work in whole depth.

#### 3.2.1 Compiler techniques

This sub-section gives an overview of work which is conducted in the closer context of compiler techniques.

#### General

Lorenz [45] presents a phase-coupled code generation technique for DSP processors. The inherent interdependencies of code selection, instruction scheduling and register allocation are pointed out and a genetic algorithm for solving these problems concurrently is presented. The fitness function of the genetic algorithm includes both execution time and energy estimations from a sufficiently accurate model. Evaluation justifies the claim of reducing energy consumption. In [46], Lorenz refines his work by including loop vectorization and exploiting zerooverhead hardware loops. A more extensive experimental evaluation is given.

Marwedel [47] provides a general overview and motivation on embedded systems compilation techniques. Some low-power optimizations are pointed out and verified through measurements on an ATMEL evaluation board. Some compilation techniques for exploiting DSP characteristics are presented and key metrics for code quality identified.

Wehmeyer [48] presents an energy-aware compilation framework for an ARM processor which uses power-models gained from empirical measurements on an evaluation board. The size of the register file is then considered as a parameter for compilation and the effects of spilling and register usage are evaluated regarding performance and energy consumption. The work shows that a good trade-off between register file size and spilling has to be taken early at design time.

#### **Register allocation**

Chang [49] describes a technique for calculating the switching activity of set of registers shared by different data values. Given a probability density function of the input values, register assignment is done by minimum cost clique covering of an compatibility graph. The evaluation proved this algorithm to effectively reduce switching activity on the register file.

Gebotys [50] focuses on simultaneous memory and register allocation. The objective is minimization of energy dissipation in onchip and offchip storage components. Modeling as network flow and solving the minimum cost problem, an (energy–)optimal assignment of data variables to registers or memory per basic block is found.

Work from Zhang [51, 52] targets on the same problem as [49, 50], but extends it to global scope. The basic blocks of the control flow graph of a function are topologically ordered with a special handling of branch, merge and loop structures within the network flow problem. The experimental evaluation, based on static and activity-based energy models, showed that energy consumption can be reduced compared to a traditional style graph-coloring register allocator.

#### Scheduling

In [53], Lee exploits special features of a Fujitsu DSP processor in order to reduce energy consumption. A minimal VLIW scheduling called instruction packing and operand swapping of a Booth multiplier are implemented and evaluated by physical measurements. Introducing these optimizations, an energy reduction of up to 56% was achieved (dependent on the chosen multiplier structure and the input data).

Tiwari [54] provides an extensive overview on instruction level power modeling and points out possible software energy optimization techniques. An experimental evaluation based on physical measurement for three different processors is given.

Toburen [55] presents a modified list-scheduling algorithm which uses a machine description model for power estimation. The list scheduler fills cycles with instructions up to a certain energy threshold. When the threshold is reached, scheduling proceeds with the next cycle. This technique reduces current spikes during program execution and virtually has no overhead due to schedule slacks in the code.

Lee [56] investigates techniques to reduce the power consumption on the instruction bus of VLIW architectures. A horizontal scheduling pass reorders the instructions within one VLIW. A vertical pass moves instructions throughout different cycles. The overall goal is minimization of the bit transitions on the instruction bus. Experiments with 4-way and 8-way VLIW architectures showed reduction of switching activity by 13.3% and 20.15% on average for horizontal scheduling, and an extra improvement by 7-10% when also vertical scheduling is applied.

In [57], Parikh presents several list scheduling algorithms with different node selection strategies. While the classic approach is purely performance oriented, an energy oriented top-down, an energy oriented bottom-up, and an energy oriented with look-ahead strategies are introduced for reducing energy consumption. Further several unified strategies are investigated. The experimental evaluation only uses a very simple architecture and a modest energy-cost model, applied on randomly generated DAGs.

Shin [58, 59] presents an optimization for reducing power consumption in VLIW instruction fetch. The problem is divided into a local (per basic block) and global (per function) step. Both are modeled as shortest-path problem in a graph. For solving the global step, some transformations and heuristics are necessary in order to use the same algorithm. Experiments with a TMS320C6201 from Texas Instruments show a reduction of the switching activity during instruction fetch by 34% through local optimization only. Global optimization gave additional

2.9% reduction.

Choi [60] introduces an enhanced scheduling algorithm which is based on a modified control flow and data dependence graph. Energy-costs from interinstruction effects are modeled by additionally inserting edges between independent nodes. This yields the so-called weighted strongly connected graph, for which a precedence constrained Hamiltonian path has to be found. Minimum spanning tree and simulated annealing techniques are applied for solving this problem. Evaluation is done using the SimpleScalar toolset. Power savings between 3 and 30% have been observed.

Yun [61] shows a modified iterative modulo scheduling approach, which both optimizes step-power and peak-power of VLIW architectures. This is reached by generating a balanced parallel schedule without sacrificing the performance. Experiments on a SPARC-based VLIW testbed showed, that the balancing reduces the number of cycles which dissipate more than 70% of the maximum power of an 8-way machine from 58% to 8%. The standard deviation of power distribution is reduced from 0.31 to 0.08.

### 3.2.2 Techniques on Operating System and System Design Level

The following paragraphs emphasize the importance of system considerations in the low-power domain and present topics on various distinct levels.

In [62], Benini provides a brief overview on system techniques to be applied for power optimization. Each technique is accompanied by a concise explanation and an extensive list of pointers.

In [63, 64], the authors present a technique to optimize switching activity on a multiplexed DRAM address bus, called Pyramid code. An extensive overview on several bus coding techniques and on DRAM technology is given. The switching problem is formulated as finding a Eulerian path in a so called RC–graph. The implementation shows a reduction of the switching activity by 50% in case of sequential accesses.

Peymandoust [65] presents a low-power technique that works on specification level by using algebraic transformations. Algorithmic parts with high computational costs, for example calculating a cosine, are replaced by simpler and sufficiently accurate calculations. The presented tool *SymSoft* was used to optimize an MP3 decoder. Besides an increased performance it was possible to decrease energy consumption.

As already stated in Chapter 2, the quadratic contribution of supply voltage to power dissipation offers a great potential for reducing energy consumption by *voltage scaling*. This term subsumes optimization techniques which focus on assigning different supply voltage levels to tasks and sub-tasks in order to minimize energy consumption. Voltage assignments have to be carried out in such a way, that real-time constraints of the tasks are still fulfilled when running at reduced voltage levels (and thus at a lower clock frequency).

Ishihara [66] and Okuma [67] present static voltage scaling techniques for dynamically variable voltage processors. Given a set of real-time parameters of a task and the available clock and voltage specifications, an *integer linear pro*gramming (*ILP*) formulation of the scheduling problem gives ideal static voltage assignments in order to minimize energy consumption.

Hsu [68] presents a compiler-directed voltage scaling technique which takes into account the speed gap between processor and memory. Regions with potential energy savings are identified and the appropriate slow-down instructions inserted. Experiments with SimpleScalar and the SPECfp95 showed energy savings of 4-23% at a performance penalty of 1-2%.

Shin [69] points put some weaknesses in inter-task voltage scaling techniques and present an intra-task based solution. Based on worst-case execution time analysis, the variations in task execution time due to different control paths are gathered. Each basic block of the task is then assigned a proper speed so that timing constraints are fulfilled and energy consumption is minimized. Remaining task slack time is also exploited and used for further voltage reduction.

Saputra [70] shows how to apply compiler loop optimizations to static voltage scaling. Whenever the number of cycles needed for execution of a program is reduced, the required frequency can be reduced and therefore also the supply voltage (with quadratic relation to power dissipation). The absolute execution time keeps the same. Additionally, an approach of dynamic voltage scaling within the execution of one task is presented. It makes use of integer linear programming and assigns voltage levels to the loop nests encountered in the code.

#### **3.2.3** Profiling and Simulation

Low-power design also needs substantial support on simulation level. Different approaches have already been presented, where the range of accuracy spans from architectural level to finer granularity.

Brooks [71] presents a tool for power analysis on the architectural level. It allows sufficiently fast power estimation early in the design process with an accuracy nearly similar to lower-level tools.

Ye [72] introduces an add-on to the SimpleScalar framework for doing cycleaccurate energy estimation and bases on transitive-sensitive energy models. Energy estimates for the processor datapath, memory, and on-chip buses are delivered.

Some other work in [73, 74, 75] also focus on energy estimation and profiling but will not be further discussed.

# Chapter 4

# Target architecture xDSPcore

This thesis has been carried out in the domain of programmable embedded digital signal processors. Generally, the presented techniques can be applied to virtually any of current DSP architectures. In order to approach the topics on a conceptual level, a prototype being currently developed at Infineon Technologies Austria has been chosen as target architecture. This chapter will briefly introduce the xDSPcore architecture, a more elaborate presentation can be found in [76].

## 4.1 Design objectives and philosophy

Designing an architecture from scratch is of course a longsome, complicated but indeed interesting matter. It was mainly motivated by the deficiencies of currently available solutions and often driven by the enthusiasm and curiosity of the team members only.

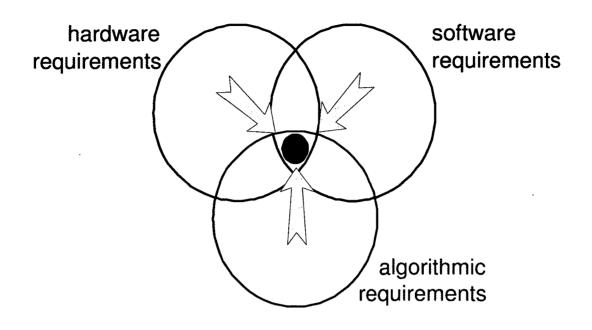

One of the key ideas in xDSPcore is *scalability*. The demands on an embedded digital signal processor come from different directions. As already pointed out, there are stringent requirements from the perspective of hardware, which demand a great flexibility in implementation. From the perspective of programmers, the processor has to be programmable in high-level languages, which means that its architecture should be compiler-friendly. And last but not least, algorithms may demand special functionality to be implemented efficiently. All these factors have to be considered already during the design phase of an architecture. This philosophy is briefly depicted by Figure 4.1, a broader discussion can again be found in [76]. xDSPcore is therefore not *one* architecture. It is a *family* of architectures with a similar top-level design, but different in certain scalability factors. These factors will be discussed later in Section 5.2.3. The next section introduces the top-level design of xDSPcore based on one architectural instance which served as a reference during carrying out this thesis.

Figure 4.1: Design philosophy of xDSPcore

### 4.2 Example architecture

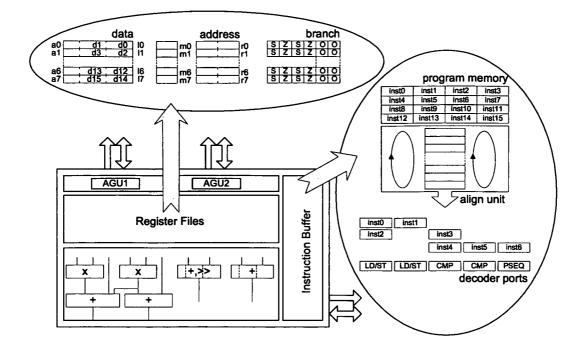

The xDSPcore is based on a modified, dual Harvard load-store architecture [77, 78]. Figure 4.2 shows a top-level overview of the architecture.

xDSPcore uses a variable-length VLIW programming model. In general, VLIW suffers from poor code density. This problem is solved by introducing a code compression technique called xLIW [79]. xLIW is based on a *variable length execution set (VLES)*, which enables a decoupling of fetch and execution bundles. Compared to VLES, xLIW permits a reduction of the size of the program memory port (and therefore reduces the wiring effort) without limiting the architecture's peak performance. The program memory port size is 4 instruction words whereas an xLIW instruction can use up to 10 instruction words. An instruction buffer overcomes the possible bandwidth mismatch resulting from the reduced size of the program memory port [80]. The align unit, closely related to the instruction buffer, is responsible for re-building the execution sets from the fetch bundles.

Two independent data buses connect the xDSPcore data path to the data memory. The data memory is split into two banks, x- and y-memory. Two concurrent memory accesses in one execution cycle can be performed only if these do not refer to the same bank. Otherwise, a memory stalling occurs and the accesses are serialized by the hardware. This happens transparently to the software.

For load-store architectures, the register file is a central part of the data path.

Figure 4.2: Architecture Overview

Separate instructions are used for moving data between a register file and data memory (MOV instruction class); all arithmetic and control-flow instructions (CMP and BR instruction classes respectively) only use register operands from the register file.

The register file of xDSPcore is split into three parts: data register file, address register file including modifier registers and a separate branch file (which is not fully visible to the instruction set). The structure of the register file is orthogonal. There are no restrictions on the usage of registers for special instructions.

The data register file supports three types of register sizes. 40 bit accumulator registers (Ax) constitute the base registers. The 32 least significant bit of an accumulator can be accessed as a long register (Lx). A long register can be split and accessed as two 16 bit short registers (Dx).

Address registers (Rx) are 20 bit wide. Each one has a 12 bit modifier register (Mx) attached, which is used for modulo- and bit-reversed addressing modes.

The branch file contains status information of the core architecture. It holds static information about the register content (e.g. sign and zero flag for each register of the data register file) and dynamic information updated by the data flow (e.g. overflow flags or flags indicating loop status). The separate branch file is implemented in order to relax the number of read/write ports associated with the register files, which are already stressed by the orthogonality requirements [81]. xDSPcore offers a fully predicated instruction set [82]. Predication is register based (not on special flags) and offers much flexibility in building complex conditional expressions. ('true', 'false', and 'dont care'; conjunction, disjunction, loop status, etc ...). More details on predicates will be given in Section 5.2.1.

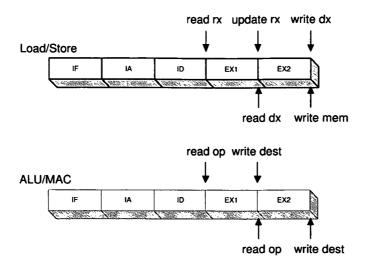

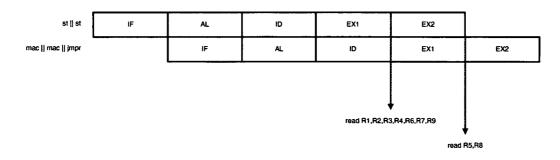

The RISC-like pipeline of xDSPcore is split into three phases: *fetch*, *decode* and *execute*. Each of the phases can be split into several clock cycles, which results in higher clock frequencies. The reference architecture has a five stage pipeline:

- 1. IF ... instruction fetch

- 2. IA ... instruction align

- 3. ID ... instruction decode

- 4. EX1 ... execute stage 1 (for simple ALU instructions)

- 5. EX2 ... execute stage 2 (for memory accesses and multiplications instructions)

However, splitting the instruction fetch into several clock cycles increases the number of branch delays. Spending several clock cycles on the execution phase increases load-use and define-use dependencies. Compensation methods for the arising drawbacks (bypasses, branch prediction) are available [83, 84, 85, 86, 87] but increase core complexity and silicon area.

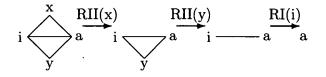

Accesses to the register file occur in the pipeline stages where values are actually used or computed. In this way, register pressure is reduced and software pipelining can be implemented without the need for rotating register files and modulo variable renaming. Figure 4.3 shows examples for the timings of register file accesses of MOV and CMP instructions. read rx denotes the pipeline edge where *MOV* instruction read the memory address from the address register file. update rx denotes when the updated address (in case of auto-modifying MOVinstructions) is written back to the address register. read dx shows the pipeline edge, where the data to be stored by a MOV instruction is read from the register file, whereas write dx shows the edge where a loaded value is written to the register file. Finally, write mem is the edge where a stored value is written into the memory. The upper read op of CMP instruction denotes the pipeline edge where simple ALU operations and multiplications read the source operands. Its corresponding *write dest* is the edge where the result of simple ALU operations is written to the register file. The lower read op denotes the edge where a multiplyaccumulate instruction reads the accumulator. Finally, the lower write dest is the edge where all multiplication instructions write the result to the register file.

The size of the native instruction word of the reference implementation is 20 bit. An instruction word contains three bits used to indicate operation class and containing alignment information. The remaining bits are used for instruction

Figure 4.3: Examples for register file accesses

coding. An additional parallel word is available for coding long immediate values or offsets, thus resulting in a 40 bit instruction word (in short this coding is called 20/40-bit coding). Other codings might be 16/32, or 12/24/36.

# Chapter 5

# **Investigated techniques**

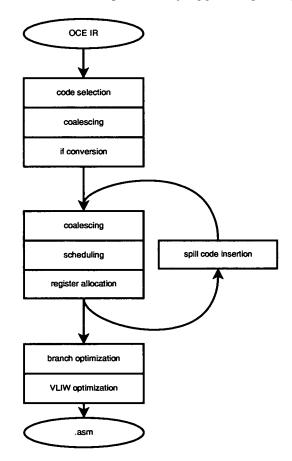

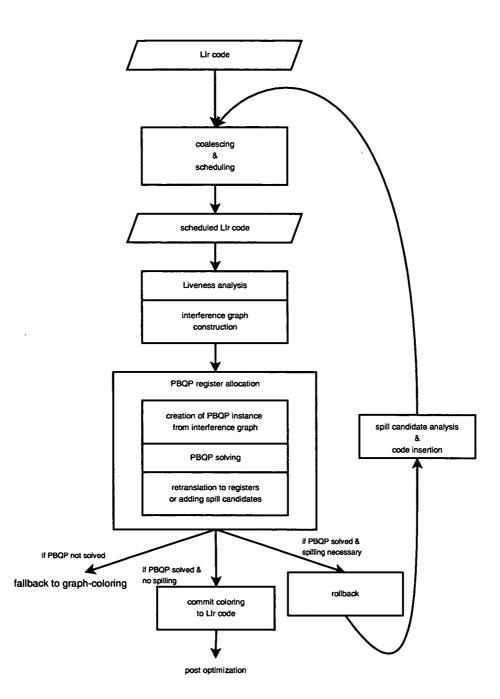

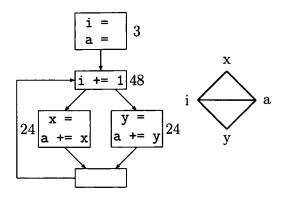

This chapter presents the contributions of this thesis. The presented techniques have been implemented in an optimizing compiler backend for the xDSPcore architecture. Figure 5.1 gives a brief overview of the backend tasks and the chosen order of optimization. The individual passes and the motivation for this particular phase-ordering are explained in further detail in the rest of this chapter.

### Assembly code notation

The assembly code examples in the next sections will follow the rules given subsequently:

An instruction is built from a *mnemonic* and a list of operands. Source operands appear first, the destination operand is at the last position. For example add D0,D1,D2 adds the registers D0 and D1 and writes the result to register D2.

Each instruction can be assigned a predicate, which is placed before the mnemonic and surrounded by parentheses. The instruction is then executed conditionally, depending on the run time value of the predicate (for example (DO>O) add D1,D2,D3 executes an addition of D1 and D2 to D3 only if the value of D0 is greater than 0).

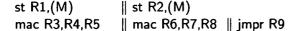

An execution bundle is made up from multiple instructions written on one line and separated by a double-pipe ( $\parallel$ ) symbol. All these instructions are executed in the same execution cycle. The bundle

add D0,D1,D2 || sub D0,D1,D3

performs an addition and a subtraction of D0 and D1. The results are written to D2 and D3 respectively.

Bundles which contain predicated instructions have to be flagged by a corresponding  $pe^{*1}$  instruction, depending on the set of predicates. The bundle

(DO>O) add D1,D2,D3 || (DO<=O) sub D1,D2,D3 || pe

is an example for a simple predicated bundle, where either an addition or a subtraction of D1 and D2 is performed (depending on the value of D0).

Branch instructions in the examples will have two delay slots. These delay slots have to be made explicit by either inserting instructions which can be executed before the branch takes place or by appending no-ops.

Figure 5.1: Backend tasks and ordering

<sup>&</sup>lt;sup>1</sup>pe,pel,peal,pexl: these offer different possibilities for predication, including conjunction and disjunction of up to three simple predicates

# 5.1 Major contributions

This section presents two optimizations: (1) register allocation techniques for irregular architectures, which are necessary to reduce the data memory accesses due to spilling, and (2) a post-pass code optimization method which reduces the switching activities on the instruction memory bus.

# 5.1.1 Register allocation

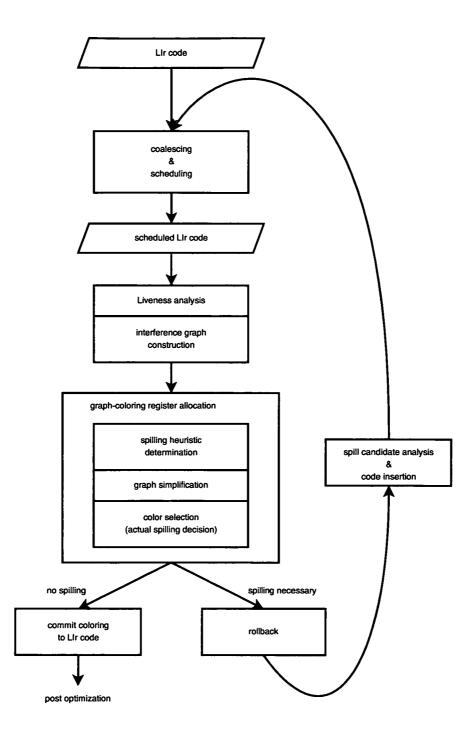

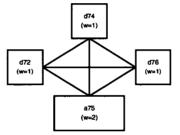

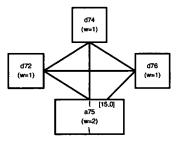

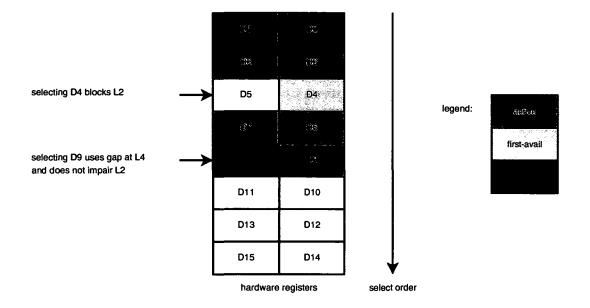

Section 3.1.1 already gave a short introduction to the field of global register allocation, covering the graph-coloring approach and its descendants. In this section, the topics relevant to xDSPcore will be presented in more detail. This includes basics like liveness analysis for predicated code or modeling architectural constraints like shared registers. Additionally, an optimal register allocator based on a PBQP approach is implemented. Figure 5.2 gives a detailed overview of the sub-tasks for a graph-coloring register allocator. The PBQP-based register allocator looks quite similar and is depicted in Figure 5.3.

#### Peculiarities

A register allocator for the xDSPcore architecture has to consider some architectural peculiarities which are only partly covered in related work. Disregarding these peculiarities leads to an overly constrained interference graph. This yields conservative colorings and thus results in inefficient spilling code. Both an overhead in code size through the additional spilling instructions (static overhead) and an increase in data memory accesses (dynamic overhead) will occur.

**Predicated liveness and interference** The most fundamental difference to traditional register allocation techniques arises from predicated code. Liveness analysis as commonly formulated does not deliver correct results, and construction of the interference graph may lead to overly constrained nodes. An extended formulation of these algorithms is needed in order to achieve a proper modeling of the constraints on symbolic registers.

Liveness analysis is a backward data-flow problem. It is solved by iteratively applying data flow equations (5.1) for all instructions i until reaching a fixed-point in the liveness sets (see [88]).

$$IN_{i} = USE_{i} \cup (OUT_{i} \setminus DEF_{i})$$

$$OUT_{i} = \bigcup_{s \in Succ_{i}} IN_{i}$$

(5.1)