The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# Reverse Compilation Techniques for VLIW Architectures

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

## ao.Univ.Prof. Dipl.-Ing. Dr. Andreas Krall

E185 Institut für Computersprachen Technische Universität Wien

eingereicht an der Technischen Universität Wien

Fakultät für Informatik

von

## Mag. Nerina Bermudo Pla

$\begin{array}{c} 0427348\\ \text{Bräuhausgasse } 48/37\\ 1050 \text{ Wien} \end{array}$

Wien, am 25. Oktober 2005

# Abstract

Reverse compilation (or decompilation) is the translation of machine or assembly language into a high-level machine independent language. Decompilation can be used to recover lost or inaccessible source code, to translate code originally written in an obsolete language into a new language or to migrate applications to a new hardware platform.

A digital signal processor (DSP) is a microprocessor designed specifically for the efficient implementation of digital signal processing algorithms. Aiming for high-performance newer DSP processors use design approaches typical of super computer architectures. Very long instruction word (VLIW) architectures consist of multiple execution units, allowing the parallel execution of instructions. Pipelines divide the execution process in several steps in such a way that an instruction can be dispatched before the previous one has finished execution.

Optimizing compilers for modern DSP architectures allow the efficient execution of applications written in high-level languages. Since most available software for older architectures is coded in assembly language, a reverse compiler that translates assembly language code into a high-level language is exceptionally useful.

For both understanding the software and for reverse compiling it to a highlevel language, a control flow graph (CFG) is required. However, CFG construction is complicated by architectural features of pipelined VLIW architectures, which include predicated instructions, VLIW parallelism, instructions (in particular branches) with delay slots. This work introduces a new approach for the construction of a CFG, where the parallelism has been eliminated, instruction reordering has been reversed and delay slots have been removed.

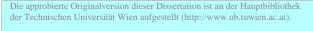

Software pipelining is a widely implemented optimization technique used to speed up loop execution in processors that support instruction level parallelism. Software pipelining basically overlaps several loop iterations so that they can be executed concurrently. This causes an increase in the CFG size. Understanding the code becomes very difficult. Software de-pipelining is the reverse of software pipelining. It restores the assembly code of a softwares pipelined loop back to its semantically equivalent sequential form. This thesis presents a de-pipelining algorithm for single loops.

In the course of this thesis a retargetable decompiler framework has been developed which includes entirely new techniques for CFG construction and software de-pipelining. They have been tested on several digital signal processing applications for the TIC62x DSP.

Abstract

# Kurzfassung

*Reverse compilation* (Rückübersetzung) ist die Übersetzung von Programmen in Maschinen- oder Assemblerspache in eine architekturunabhängige höhere Programmiersprache. Rückübersetzung wird verwendet, um verlorenen oder unzugänglichen Quelltext, der ursprünglich in einer technisch überholten Sprache geschrieben wurde, in eine neue Sprache zu übersetzen oder um Anwendungen zu einer neuen Architektur zu migrieren.

Ein digitaler Signalprozessor (DSP) ist ein Mikroprozessor, der speziell für die effiziente Ausführung von Signalverarbeitungsalgorithmen entwickelt wurde. Neuere DSP verwenden Designlösungen, die typisch für Hochleistungrechner sind: VLIW (very long instruction word) Architekturen enthalten mehrere unabhängige Funktionseinheiten und ermöglichen so die parallele Ausführung mehrere Befehle. Pipelines zerlegen die Ausführung von Befehlen in mehrere Teile, so dass der nachfolgende Befehl geladen werden kann, bevor die Abarbeitung des vorherigen Befehls abgeschlossen ist.

Optimierende Übersetzer für moderne DSP Architekturen ermöglichen die effiziente Ausführung von Anwendungen, die in einer höheren Programmiersprache entwickelt wurden. Da ein Großteil der Software für ältere Architekturen in Assemblersprache entwickelt wurde, ist ein Rückübersetzer, der Assemblersprache in eine höhere Programmiersprache übersetzt, sehr wertvoll.

Ein Kontrollflussgraph (CFG) ist notwendig, sowohl um das Programm zu verstehen, als auch für die Rückübersetzung in eine höhere Programmiersprache. Die Konstruktion des CFG wird komplizierter durch Architektureigenschaften, wie bedingt ausgeführte Befehle, VLIW Parallelismus und verzögert ausgeführte Befehle (insbesonders Sprünge). Diese Arbeit stellt eine neue Methode vor, um einen Kontrollflussgraphen zu erstellen, in dem sowohl Parallelismus, als auch die Auswirkungen von verzögert ausgeführten Befehlen entfernt worden sind.

Software pipelining ist eine weit verbreitete Optimierung, um die Abarbeitung von Schleifen bei Prozessoren, die Parallelismus unterstützen, zu beschleunigen. Beim software pipelining werden mehrere Iterationen einer Schleife überlappend ausgeführt. Der Kontrolflussgraph ist dann grösser und unübersichtlicher, wobei der generierte Programmcode schwieriger zu verstehen wird. Software de-pipelining ist die Umgekehrung der Optimierung, dessen Ziel die Wiederherstellung der sequenziellen Form der Schleife ist, ohne die Sematik des Programmes zu verändern. Diese Arbeit stellt ein Algorithmus für software de-pipelining von Schleifen vor.

Im Verlauf dieser Doktorarbeit wurde ein Rückübersetzer entwickelt, der diese neuen Techniken enthält. Mehrere Signalverarbeitungsanwendungen für den TIC62x DSP wurden mit diesem Rückübersetzer evaluiert.

Kurzfassung

Als meus pares, per tot. Für dich und die Tiere.

# Acknowledgements

I would like to thank several people that have directly or indirectly contributed to this work. Andreas Krall, my supervisor, for his support and dedication. Bogong Su, for the long discussions and his help with software de-pipelining. Everybody at the computer languages department and, in particular, to my colleagues at the CD lab, Gerhart Kobinger, Ivan Prianichnikov, Viera Sipkova, Ulrich Hirnschrott and Christian Thalinger.

I also would like to thank the Kristen family and Harald for helping me in a million ways and making me feel part of their family. Thanks to the Bermudo family for their calls and support and to Piero, for remembering me every time I went to Barcelona. I want to thank my friends that were far away, in particular Jaume for having read this thesis.

Finally, very special thanks to Oliver, Barkley Kingwood, We de Boer, Enju Mabura and Minerva Fernández. Thank you all.

A cknowledgements

# Contents

| 1        | Dec | ompila | ation Techniques                         | 1         |

|----------|-----|--------|------------------------------------------|-----------|

|          | 1.1 | Decon  | npilers                                  | 1         |

|          |     | 1.1.1  | Decompilation Problems                   | 2         |

|          |     | 1.1.2  | Motivation                               | 2         |

|          | 1.2 | Histor | ry of Decompilation                      | 3         |

| <b>2</b> | Har | dware  | and Software Considerations              | 9         |

|          | 2.1 | Hardv  | vare Issues                              | 9         |

|          |     | 2.1.1  | Parallelism                              | 9         |

|          |     | 2.1.2  | ILP-Architectures                        | 11        |

|          | 2.2 | DSP I  | processors                               | 12        |

|          | 2.3 | Softwa | are Issues                               | 14        |

|          |     | 2.3.1  | Instruction Scheduling                   | 14        |

|          |     | 2.3.2  | Software pipelining                      | 15        |

|          | 2.4 | TMS3   | 20C62x DSP                               | 16        |

|          |     | 2.4.1  | Assembler language                       | 17        |

|          |     | 2.4.2  | Parallel Operations                      | 17        |

|          |     | 2.4.3  | Conditional Operations                   | 18        |

|          |     | 2.4.4  | Pipeline and Delay Slots                 | 18        |

|          |     | 2.4.5  | Resource Constraints                     | 19        |

| 3        | Dec | ompila | ation Framework                          | <b>21</b> |

|          | 3.1 | The D  | Decompiler                               | 21        |

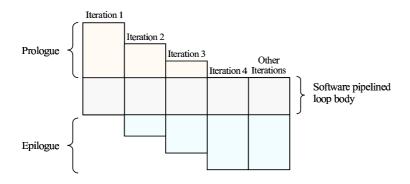

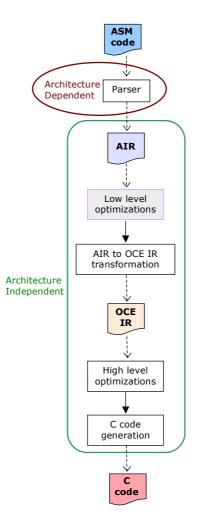

|          |     | 3.1.1  | Parser and Internal Representation       | 23        |

|          |     | 3.1.2  | Low Level Optimizations                  | 24        |

|          |     | 3.1.3  | Transformation to the OCE Representation | 25        |

|          |     | 3.1.4  | High Level Optimizations                 | 27        |

|          |     | 3.1.5  | C Code Generation                        | 31        |

|          | 3.2 | Relate | ed Work                                  | 32        |

| 4        | CFO | G Reco | onstruction and Sequentialization        | 37        |

|          | 4.1 | Introd | luction to the Problem                   | 37        |

|          |     | 4.1.1  | Delayed Instructions                     | 38        |

|          |     | 4.1.2  | Choices for Removing Delay Slots         | 39        |

|          |     | 4.1.3  | Delay Slots Resolution                   | 41        |

## CONTENTS

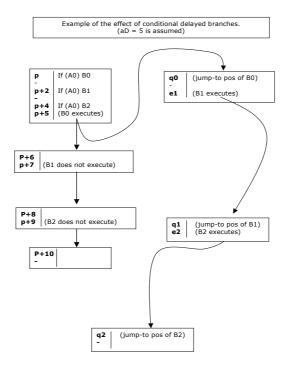

|   |      | 4.1.4                                                                                                                                      | Delayed Branches and the Control Flow                                                                                                                                                                                                                                                                                                                     |                           |                                                                      |                                                | •                   | 41                                                                                             |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------|------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------|

|   |      | 4.1.5                                                                                                                                      | Parallel Instructions                                                                                                                                                                                                                                                                                                                                     |                           |                                                                      |                                                |                     | 46                                                                                             |

|   | 4.2  | CFG I                                                                                                                                      | Reconstruction                                                                                                                                                                                                                                                                                                                                            |                           |                                                                      |                                                |                     | 47                                                                                             |

|   |      | 4.2.1                                                                                                                                      | Solution Approach                                                                                                                                                                                                                                                                                                                                         |                           |                                                                      |                                                |                     | 47                                                                                             |

|   | 4.3  | Edge I                                                                                                                                     | Recognition                                                                                                                                                                                                                                                                                                                                               |                           |                                                                      |                                                | •                   | 48                                                                                             |

|   |      | 4.3.1                                                                                                                                      | Selecting new delayed branches                                                                                                                                                                                                                                                                                                                            |                           |                                                                      |                                                |                     | 48                                                                                             |

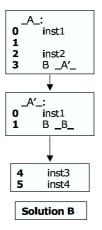

|   |      | 4.3.2                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   |                           |                                                                      |                                                |                     | 51                                                                                             |

|   | 4.4  | Minim                                                                                                                                      | al Number of Edges                                                                                                                                                                                                                                                                                                                                        |                           |                                                                      |                                                |                     | 52                                                                                             |

|   |      | 4.4.1                                                                                                                                      | Algorithm                                                                                                                                                                                                                                                                                                                                                 |                           |                                                                      |                                                |                     | 53                                                                                             |

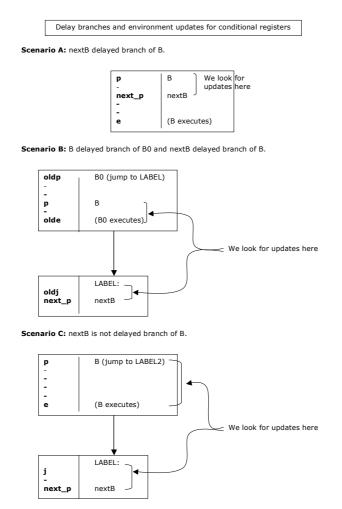

|   |      | 4.4.2                                                                                                                                      | How to Update the Environment                                                                                                                                                                                                                                                                                                                             |                           |                                                                      |                                                |                     | 56                                                                                             |

|   |      | 4.4.3                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   |                           |                                                                      |                                                |                     | 57                                                                                             |

|   | 4.5  | Basic I                                                                                                                                    | Blocks Construction                                                                                                                                                                                                                                                                                                                                       |                           |                                                                      |                                                |                     | 59                                                                                             |

|   |      | 4.5.1                                                                                                                                      | Definitions                                                                                                                                                                                                                                                                                                                                               |                           |                                                                      |                                                |                     | 60                                                                                             |

|   |      | 4.5.2                                                                                                                                      | Algorithm                                                                                                                                                                                                                                                                                                                                                 |                           |                                                                      |                                                |                     | 60                                                                                             |

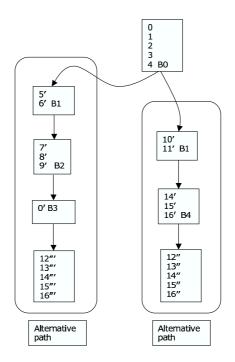

|   |      | 4.5.3                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   |                           |                                                                      |                                                |                     | 62                                                                                             |

|   | 4.6  | Delay                                                                                                                                      | Resolution                                                                                                                                                                                                                                                                                                                                                |                           |                                                                      |                                                |                     | 64                                                                                             |

|   |      | 4.6.1                                                                                                                                      | Data Conflict Resolution                                                                                                                                                                                                                                                                                                                                  |                           |                                                                      |                                                |                     | 66                                                                                             |

|   | 4.7  | Sequer                                                                                                                                     | ntialization                                                                                                                                                                                                                                                                                                                                              |                           |                                                                      |                                                |                     | 68                                                                                             |

|   | 4.8  | -                                                                                                                                          | mental Results                                                                                                                                                                                                                                                                                                                                            |                           |                                                                      |                                                |                     | 68                                                                                             |

|   |      | 4.8.1                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   |                           |                                                                      |                                                |                     | 70                                                                                             |

|   | 4.9  | Relate                                                                                                                                     | d Work                                                                                                                                                                                                                                                                                                                                                    |                           |                                                                      |                                                |                     | 70                                                                                             |

|   |      | 4.9.1                                                                                                                                      | CFG Construction                                                                                                                                                                                                                                                                                                                                          |                           |                                                                      |                                                |                     | 70                                                                                             |

|   |      | 4.9.2                                                                                                                                      | Basic Block Construction                                                                                                                                                                                                                                                                                                                                  |                           |                                                                      |                                                |                     | 75                                                                                             |

|   |      | 4.9.3                                                                                                                                      | Delay Resolution Problems                                                                                                                                                                                                                                                                                                                                 |                           |                                                                      |                                                |                     | 76                                                                                             |

| 5 | Soft | waro I                                                                                                                                     | De-pipelining                                                                                                                                                                                                                                                                                                                                             |                           |                                                                      |                                                |                     | 79                                                                                             |

| 0 | 5.1  |                                                                                                                                            | uction                                                                                                                                                                                                                                                                                                                                                    |                           |                                                                      |                                                |                     | <b>7</b> 9                                                                                     |

|   | 0.1  | minou                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                           |                           | • •                                                                  | •                                              |                     | 79                                                                                             |

|   |      | 5.1.1                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                           |                           |                                                                      |                                                |                     |                                                                                                |

|   |      | 5.1.1<br>5 1 2                                                                                                                             | Example                                                                                                                                                                                                                                                                                                                                                   |                           |                                                                      |                                                |                     |                                                                                                |

|   |      | 5.1.2                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   | •                         |                                                                      |                                                |                     | 81                                                                                             |

|   | 5.2  | $5.1.2 \\ 5.1.3$                                                                                                                           | Example                                                                                                                                                                                                                                                                                                                                                   |                           | <br>                                                                 | •                                              |                     | 81<br>83                                                                                       |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa                                                                                                                   | Example                                                                                                                                                                                                                                                                                                                                                   |                           | <br><br>                                                             |                                                |                     | 81<br>83<br>83                                                                                 |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1                                                                                                          | Example                                                                                                                                                                                                                                                                                                                                                   |                           | · ·                                                                  |                                                | •                   | 81<br>83<br>83<br>84                                                                           |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2                                                                                                 | Example                                                                                                                                                                                                                                                                                                                                                   |                           | <br><br>                                                             |                                                | •                   | 81<br>83<br>83<br>84<br>87                                                                     |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3                                                                                        | Example.Limitations.Reversing Software Pipelining: Problems.re De-pipelining Approach.Notation and Concepts.Locate Prephase, Prelude and Postlude Blocks.Schedule Loop Instructions.                                                                                                                                                                      |                           | <br><br><br>                                                         |                                                | •<br>•<br>•         | 81<br>83<br>83<br>84<br>87<br>89                                                               |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                                               | Example                                                                                                                                                                                                                                                                                                                                                   |                           | · · ·<br>· · ·<br>· · ·                                              |                                                |                     | 81<br>83<br>83<br>84<br>87<br>89<br>91                                                         |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                      | Example                                                                                                                                                                                                                                                                                                                                                   | • • • • •                 | · · ·<br>· · ·<br>· · ·                                              |                                                |                     | 81<br>83<br>83<br>84<br>87<br>89<br>91<br>94                                                   |

|   |      | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                             | Example                                                                                                                                                                                                                                                                                                                                                   | • • • • • • •             | · · ·<br>· · ·<br>· · ·                                              |                                                | • • • • • •         | 81<br>83<br>84<br>87<br>89<br>91<br>94<br>94                                                   |

|   | 5.2  | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog                                                   | ExampleLimitationsReversing Software Pipelining: Problemsre De-pipelining ApproachNotation and ConceptsLocate Prephase, Prelude and Postlude BlocksSchedule Loop InstructionsCompute the New Initial Value of the Loop CounterRewrite LoopDot Product ExampleZ/ Epilog Collapsing                                                                         | • • • • • •               | · · ·<br>· · ·<br>· · ·<br>· · ·                                     | ·<br>·<br>·<br>·<br>·                          | • • • • • •         | 81<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>96                                             |

|   |      | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1                                          | ExampleLimitationsReversing Software Pipelining: Problemsre De-pipelining ApproachNotation and ConceptsLocate Prephase, Prelude and Postlude BlocksSchedule Loop InstructionsCompute the New Initial Value of the Loop CounterRewrite LoopDot Product Example*Epilog Collapsing                                                                           | · · · · · · · · · ·       | · · ·<br>· · ·<br>· · ·<br>· · ·                                     | ·<br>·<br>·<br>·<br>·                          | • • • • • • •       | 81<br>83<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>94<br>96<br>97                           |

|   |      | 5.1.2<br>5.1.3<br>Softwa<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1<br>5.3.2                                 | Example                                                                                                                                                                                                                                                                                                                                                   | • • • • • • • • •         | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                            | ·<br>·<br>·<br>·<br>·<br>·                     | • • • • • • • • •   | 81<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>96<br>97<br>98                                 |

|   | 5.3  | 5.1.2<br>5.1.3<br>Softwar<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1<br>5.3.2<br>5.3.3                       | Example                                                                                                                                                                                                                                                                                                                                                   | • • • • • • • • • •       | · · · · · · · · · · · · · · · · · · ·                                | ·<br>·<br>·<br>·<br>·<br>·                     | • • • • • • • • • • | 81<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>96<br>97<br>98<br>98                           |

|   | 5.3  | 5.1.2<br>5.1.3<br>Softwar<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1<br>5.3.2<br>5.3.3<br>Softwar            | Example                                                                                                                                                                                                                                                                                                                                                   | • • • • • • • • • • •     | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                   | ·<br>·<br>·<br>·<br>·<br>·<br>·                | • • • • • • • • • • | 81<br>83<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>94<br>94<br>96<br>97<br>98<br>98<br>98   |

|   | 5.3  | 5.1.2<br>5.1.3<br>Softwar<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1<br>5.3.2<br>5.3.3<br>Softwar<br>General | ExampleLimitationsReversing Software Pipelining: Problemsre De-pipelining ApproachNotation and ConceptsLocate Prephase, Prelude and Postlude BlocksSchedule Loop InstructionsCompute the New Initial Value of the Loop CounterRewrite LoopDot Product ExampleEpilog CollapsingProlog CollapsingDot Product ExampleLocate De-pipelining Formal Description | · · · · · · · · · · · · · | · · ·<br>· · · | · · · · · · · · · · · · · · · · · · ·          |                     | 81<br>83<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>94<br>96<br>97<br>98<br>98<br>101<br>104 |

|   | 5.3  | 5.1.2<br>5.1.3<br>Softwar<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>Prolog<br>5.3.1<br>5.3.2<br>5.3.3<br>Softwar            | Example                                                                                                                                                                                                                                                                                                                                                   |                           | · · ·<br>· · · | ·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>· |                     | 81<br>83<br>83<br>84<br>87<br>89<br>91<br>94<br>94<br>94<br>94<br>96<br>97<br>98<br>98<br>98   |

|   |     | 5.5.3  | Criterion for Prolog / Epilog Collapsing                | 110 |

|---|-----|--------|---------------------------------------------------------|-----|

|   |     | 5.5.4  | General Algorithm to Compute the New Loop Counter Value | 113 |

|   | 5.6 | Other  | Loop Optimizations                                      | 114 |

|   |     | 5.6.1  | Loop Unrolling                                          | 114 |

|   |     | 5.6.2  | Modulo Variable Renaming                                | 114 |

|   |     | 5.6.3  | Loop Peeling                                            | 114 |

|   |     | 5.6.4  | Loop Optimizations and De-pipelining                    |     |

|   | 5.7 | Other  | Types Of Loops                                          | 116 |

|   |     | 5.7.1  | Variable Counter                                        |     |

|   |     | 5.7.2  | Not Counted Loops                                       | 116 |

|   | 5.8 | Exper  | imental Results                                         | 118 |

|   | 5.9 | Relate | ed Work                                                 | 118 |

|   |     | 5.9.1  | Software Pipelining                                     | 118 |

|   |     | 5.9.2  | Software De-ipelining                                   |     |

| 6 | Con | clusio | ns and Further Work                                     | 121 |

## CONTENTS

# List of Figures

| 2.1  | Software Pipelining                                        | 6 |

|------|------------------------------------------------------------|---|

| 3.1  | The decompiler                                             | 2 |

| 3.2  | Class Diagram of the IR                                    | 3 |

| 3.3  | Iterative Computation of Liveness 28                       | 8 |

| 3.4  | Removing Dead Computations 29                              | 9 |

| 3.5  | C Code Generation Algorithm                                | 2 |

| 4.1  | One delayed branch                                         | 3 |

| 4.2  | Two delayed branches                                       | 4 |

| 4.3  | Program with one branch 44                                 | 5 |

| 4.4  | CFG Edge Construction Algorithm                            | 9 |

| 4.5  | B independent and D empty                                  | 0 |

| 4.6  | B is a delayed branch                                      | 0 |

| 4.7  | Explosion of branches                                      | 3 |

| 4.8  | Effect of Conditional Register Analysis                    | 4 |

| 4.9  | CFG Edge Construction Algorithm With Register Analysis 55  | 5 |

| 4.10 | Redefinition Intervals                                     | 6 |

| 4.11 | CFG with conditions analysis                               | 7 |

| 4.12 | BB Construction: example code                              | 8 |

| 4.13 | BB Construction: direct solution                           | 9 |

| 4.14 | BB Construction: correct solution                          | 9 |

| 4.15 | Result of the edges construction algorithm                 | 1 |

| 4.16 | CFG                                                        | 2 |

| 4.17 | Handling Of Data Conflicts                                 | 6 |

| 4.18 | Delay resolution algorithm                                 | 7 |

| 4.19 | Sequentialization Algorithm                                | 9 |

| 4.20 | Example Assembler Code                                     | 1 |

| 4.21 | CFG for Figure 4.20 after Delay Resolution                 | 2 |

| 4.22 | C Code for Figure 4.20                                     | 3 |

| 5.1  | Non-Parallel Assembler Code for Fixed-Point Dot Product 80 | 0 |

| 5.2  | Parallel Assembler Code for Fixed-Point Dot Product        | 1 |

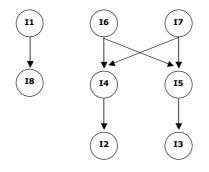

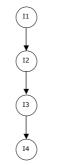

| 5.3  | Control Flow Graph of Dot Product Sequential Version 82    | 1 |

| 5.4  | Dot Product Assembler                                      | 2 |

| 5.5  | Control Flow Graph of Dot Product Software Pipelined Version  | 82  |

|------|---------------------------------------------------------------|-----|

| 5.6  | Control Flow Graph of Dot Product Sequential Version          | 85  |

| 5.7  | Control Flow Graph of Dot Product Sequential Version (cont.)  | 86  |

| 5.8  | Prephase, Prelude and Postlude Location                       | 90  |

| 5.9  | Loop scheduling algorithm                                     | 91  |

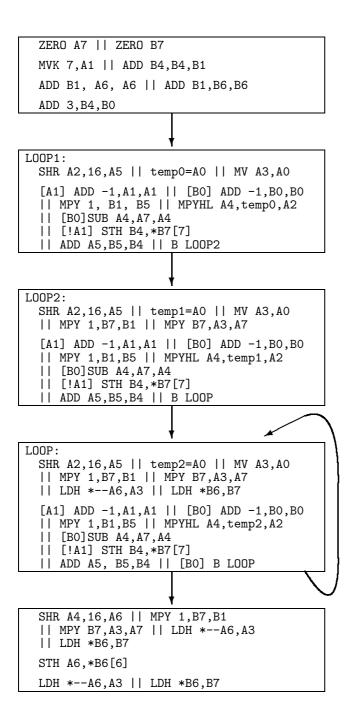

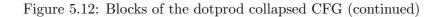

| 5.10 | Dot Product with prolog and epilog collapsed                  | 98  |

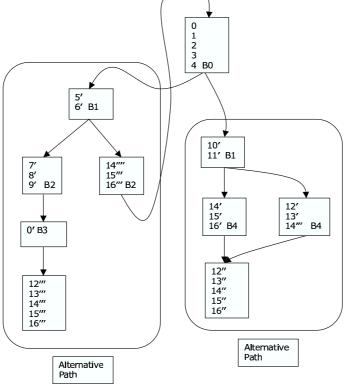

| 5.11 | Blocks of the dotprod collapsed CFG                           | 100 |

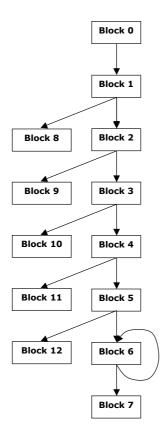

| 5.12 | Blocks of the dotprod collapsed CFG (continued)               | 101 |

| 5.13 | Data dependence graph of dotprod's Loop Body                  | 106 |

| 5.14 | Loop Scheduling with Prelude Collapsing                       | 106 |

| 5.15 | Prolog and Epilog not collapsed                               | 107 |

| 5.16 | Prolog not collapsed, Epilog collapsed                        | 108 |

| 5.17 | Prolog and Epilog collapsed                                   | 109 |

| 5.18 | Another example of Prolog collapsing                          | 110 |

| 5.19 | DDG example                                                   | 111 |

| 5.20 | Algorithm for Computing the Initial Value of the Loop Counter | 113 |

| 5.21 | Assembler Code for Max Function                               | 115 |

| 5.22 | Strlen Software Pipelined                                     | 117 |

| 5.23 | Strlen Sequentialized                                         | 117 |

# List of Tables

| 3.1 | AIR to OCE Transformation Table               | 25  |

|-----|-----------------------------------------------|-----|

| 3.2 | AIR to OCE Transformation Table (Operations)  | 26  |

| 3.3 | AIR to OCE Transformation Table (Expressions) | 26  |

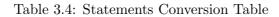

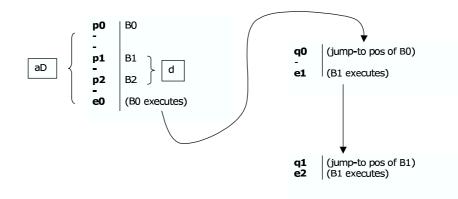

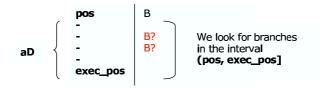

| 3.4 | Statements Conversion Table                   | 32  |

| 3.5 | Operations Conversion Table                   | 33  |

| 4.1 | Experimental Results CFG Construction         | 69  |

| 5.1 | Experimental Results Software De-Pipelining   | 118 |

LIST OF TABLES

## Chapter 1

# **Decompilation Techniques**

Decompilation is a program transformation which takes machine or assembly language code as input and generates a semantically equivalent high-level language code.

Program compilation translates a high-level program into machine code for a chosen architecture. Due to the major differences between the original and the target language, and considering other restrictions such as performance and code size, several analyses and optimizations must take place to allow a correct and efficient translation. Compiler techniques have been studied by the computer science community for many years and still represent an important research field.

Decompilation is not so different from compilation as it performs the translation of a program from one language to another. Thus, the main structure of a decompiler does not differ significantly from a compiler and many analyses and optimizations are common to both processes. However, the translation from assembly language language into a high-level language opens new issues to take care of.

This chapter introduces the subject of decompilation describing its goals and problems. Section 1.2 presents the main research results in the history of decompilation

#### 1.1 Decompilers

A decompiler is a program that takes machine code as input and translates it into semantically equivalent high-level code. In this sense, a decompiler reverses the compilation process. However, in the compilation process information about the program is lost, such as data structures and function boundaries. Therefore, the answer to the question whether it is possible to decompile a program is not obvious.

Unfortunately, the decompilation problem is theoretically equivalent to the Halting Problem [Dav58]. In practice this means that fully automated decompilation of arbitrary machine-code programs is not possible. Thus, automatic decompilation without user intervention cannot be achieved for all programs.

The question about what proportion of real-world programs can be decompiled to useful source code is still open at this point. This section introduces the main difficulties of decompilation and describes some possible usages of such a tool.

#### 1.1.1 Decompilation Problems

The following issues represent important complications for decompilers.

Separation of data and code

In machine code, data and program instructions are represented in the same way. This makes it very difficult to distinguish between them. Some decompilers do not take machine code as input, but code written in assembly language, where this problem does not occur. In this work, assembly language language is considered.

Self modifying code

Self modifying code refers to instructions that are modified during the execution of the program. This technique has been used mainly for reducing the code size. Nowadays, since memory is no longer a major limitation, self modifying code is not often used. However, it is used in just-in-time compilers, security applications and virus code.

Types and data structures

In machine or assembly language code types of variables are not specified. Data structures are not explicitly defined. For decompilation it is necessary to recover the type information and to be able to identify variables.

#### Indirect Jumps

Indirect jumps represent an important obstacle for decompilation. A branch that jumps to an address contained in a register has no explicit target. Complex memory analyses are needed that determine the possible jump-to addresses.

Complex architectures

The evolution in the computer architecture has led to more complex features like parallelism and pipelining. Decompilers need to face the new problems emerging from these new architectures.

#### 1.1.2 Motivation

Decompilers have been written for different purposes since the development of the first compilers. Throughout the last decades, different uses have been given to decompilers. In the 1960s, decompilers were used to aid in the program conversion process from second to third generation computers. In this way, manpower would not be spent in the time consuming task of rewriting programs for the third generation machines. During the 70s and 80s, decompilers were used for translating

#### 1.2. HISTORY OF DECOMPILATION

code originally written in an obsolete language into a new language, migrating applications to new hardware platforms, documentation, debugging, recovery of lost or inaccessible code, and software maintenance.

In the last years, decompilers have become a reverse engineering tool capable of helping the user with such tasks as

- recovery of lost source code,

- migration of assembly language applications to a new hardware platform,

- translation of code written in obsolete languages no longer supported by compiler tools,

- checking that a compiler generates the right code,

- detection of the existence of viruses or malicious code in the program, and

- understanding of the implementation of a particular library function.

Not all uses of decompilers are legal uses, since computer programs are protected by copyright law. Different countries have different exceptions to the copyright owner's rights so that different uses are allowed by law. However, it is not in the scope of this thesis to discuss the legal and ethical aspects of decompilation.

### **1.2** History of Decompilation

The first decompilers were developed in the 1960s as a help to programmers in the conversion process of programs from second to third generation computers. Porting these programs automatically to third generation computers would reduce the cost of doing so. Porting programs, together with recovery of lost codes, maintainance and modification of existing binaries and debugging were the main applications of decompilation until the 1990s. Then, decompilers became an interesting reverse engineering tool to help the user check whether the compiler generates the correct code, whether the program contains illegal code such as virus and trojan horses and to translate binary programs from one architecture to another.

The use of decompilers for software piracy is, at least at the moment, not really practicable, since the decompilation problem is not solvable in general. Anyway, we are not going to discuss the legal aspects of decompilation in this work.

Next, the most relevant results in the field of the decompilation since its origin will be presented. A complete history of decompilation up to these days can be found at [Tho].

• 1960 - D-Neliac decompiler The Donnelly-Neliac Decompiler [Hal62] was developed at the Navy Electronics Laboratory (NEL) in 1960. Neliac is an Algol-type language developed at the NEL in 1955. The D-Neliac decompiler produced Neliac code from machine code programs. This decompiler proved that decompilation is possible. It was also useful for detecting logic errors in the original high-level programs.

• **1966** - **W.Sassaman** Sassaman developed a decompiler to aid the conversion of programs from second to third generation computers [Sas66]. This decompiler translated assembler programs for the IBM 7000 series into Fortran. It was the first decompiler to use symbolic assembler instead of binary code.

With help from the user who, for example, was required to define rules for function recognition, this decompiler was 90% accurate. This work was developed at TRW Inc.

• **1967** - **Halstead** An enhanced version of the Neliac decompiler was realized at the Lockheed Missiles and Space Company (LMSC) [Hal67]. The input of this decompiler was source code for the IBM 7094, which was then translated into Neliac code for the Univac1108.

This decompiler successfully decompiled 90% of the instructions [Hal70]. The other 10% was left for the user to handle. At this time, decompilers focused on straightforward cases. The more complex ones were always left for the programmer to solve, since it had been shown that the time needed to solve this remaining 10% of the instructions was approximately equal to the effort already spent.

- 1967 IBM Autocoder to Cobol Conversion Housel at IBM developed a set of decompilers to translate Autocoder programs to Cobol [HH73]. A direct one-to-one mapping was performed and manual optimization was required. There was no type of automatic analysis and optimization, which lead to a rather large and inefficient code.

- 1973 Hollander syntax-oriented decompiler Hollander introduced in his PhD dissertation a new approach to decompilation, by means of a formal syntax-oriented metalanguage [Hol73]. The decompiler consisted of 5 processes: initializer, scanner, parser, constructor and generator, each of which were implemented as an interpreter of sets of metarules.

An experimental version of this decompiler was implemented to translate a subset of IBM's 360 assembler into an Algol-like target language, which worked correctly on the 10 programs it was tested against.

Basically, this technique can be seen as a kind of pattern-matching of assembler instructions into high-level instructions. This involves a strong limitation on the programs that can be decompiled, since instructions are forced to be in a certain order for patterns to be recognized. Different control flow patterns or optimized code are not allowed.

• 1973 - Housel PhD Thesis Housel describes in his PhD dissertation [Hou73] an approach for decompilation that uses techniques from the compiler, graph and optimization th theories. A decompiler is divided in three main parts: partial assembly (separates data from instructions, builds the control flow graph generating an intermediate representation of the program), analyzer (analyzes the program in order to detect loops and remove useless instructions)

#### 1.2. HISTORY OF DECOMPILATION

and code generator (optimizes the translation of arithmetic expressions and generates code for the target language).

Such a decompiler was implemented for translating Knuth's MIX assembler into PL/1 code for the IBM370 machines. In the 6 programs that were tested 88% of the instructions were correctly translated whereas the rest needed manual intervention.

The introduction of an intermediate representation made the decompiler machine independent. However, the chosen architecture provided an assembler that was not general enough.

- 1974 The Piler System The Piler System [Bar74] was a first attempt at a general decompiler, able to read machine code of several different machines and able to generate code for different high level languages. It was implemented only for one source architecture (GE/Honeywell 600) and for two target languages (Fortran and Cobol). It used a microform representation for the programs to be decompiled, which was lower-level than an assembler-type representation and made it difficult to be general enough.

- 1974 Friedman's PhD Thesis Friedman describes in his PhD thesis a decompiler used for the translation of minicomputer operating systems within machines of the same architectural class [Fri74]. This system consisted of four main phases: pre-processor, decompiler, code generator and compiler. The decompiler used was an adaption of Housel's decompiler [Hou73].

This is the first attempt to decompile operating systems. However, the preprocessor phase of this decompiler took a too large effort and the final results turned out to be inefficient due to a larger size of the code and longer execution times.

• 1974 - Schneider and Winiger Schneider and Winiger presented a notation for specifying the compilation and decompilation of high-level languages. A context-free grammar is defined for the compilation process and then, it is shown how this grammar can be inverted to decompile the object code into the original source program [SW74].

This is another approach of syntax-oriented decompilation [Hol73]. Unfortunately, this only works for a particular compiler and only under certain circumstances, failing in the presence of optimizations, which makes it useless in practice.

• 1978 - Hopwood PhD Thesis Hopwood describes a 7-step decompiler designed to aid porting and documentation [Hop78]. An experimental decompiler was implemented which translated assembly language into an artificial language called MOL620, featuring machine registers. This choice made the decompiler easy to implement, but the result was not high-level code. Besides, the control flow graph used had one node for each instruction (instead of a node for each basic block), which led to a huge control flow graph in case of large programs.

This decompiler was able to translate one large program successfully.

• 1978 - Workman Workman introduced a new use of decompilation. The goal of his work was to define a high-level language suitable for real time training device systems using decompilation [Wor78]. In particular, it was implemented for the F4 trainer aircraft. Since the operating system of the F4 was in assembler, this was the input language, rather than machine code. The output language was not determined, as it was the goal of this project to define one.

However, no code was generated. Only the first parts of the decompiler were implemented. The conclusions of this work were that the high-level language should have the following properties: handle bit strings, support loops and conditional control structures and not require dynamic data structures or recursion.

• **1981 - Zebra** The Zebra decompiler was developed at the Naval Underwater Systems Centre [Bri81]. It should port assembler programs from one platform to another. Thus, the output language was assembler as well.

This project used available results to develop a decompiler of assembler programs. Although it did not introduce new concepts, it showed that it was hard to capture the semantics of the program to decompile, and that complete decompilation was not economically practical, but could be used as an aid for porting assembler programs.

- 1988 Decomp Decomp is a decompiler written by J. Reuter, which took object files of the VAX BSD 4.2 with additional symbolic information and generated C-like programs [Reu88]. This decompiler was exclusively intended to port the Empire game to the VMS environment, as the source code was not available. No data flow analysis was performed and the output still needed significant manual work before it could be recompiled.

- 1990 exe2C The exe2c decompiler intended to translate Intel80286/DOS executables into C code [War89]. Basically, the programs were disassembled, then converted into an internal format and finally converted to C. Several machine features such as registers were visible in the output. High level control flow structures such as loops and conditional constructs were recovered up to a certain point.

However, this project was never completed. The results showed that data flow analysis and heuristics are necessary to produce better C code. It also remarked the importance of detecting library subroutines.

• **1991 - PLM-80 Decompiler** The Information Technology Division of the Australian Department of Defence tried to use decompilation for defence applications, such as maintenance of obsolete code and assessment of systems for hazards to safety and security. This work was described in [Hoo91].

#### 1.2. HISTORY OF DECOMPILATION

A decompiler for Intel 8085 assembler programs that had been compiled by the PLM-80 compiler was developed, which produced programs in a subset of the C language. It inverted a grammar of the input assembly language. As in the previous attempts to use this kind of approach, optimized code is not supported.

However, this was the first decompiler to include a graphical interface to help the user document the program.

• **1991-1994 - Decompiler compiler** A decompiler compiler is a program that generates a decompiler from a formal specification of the relationship between source code and compiled object code [BBL93a, BB91, BB93, BBL93b, BB92, BB94b, Bow91, Bow93].

In general, these compiler specifications are not available. Only customized compilers and decompilers can be build using this approach. Since this is a similar idea to inverting the grammar of the input language, optimized code is not supported. Actually, real executable programs cannot be handled. However, this sort of decompiler is useful in the verification of code in safety-critical applications.

- 1991-1993 C Decompiling System This work describes an Intel8086/DOS to C decompiler [FZL93, FZ91, HZY91]. It includes a hand-crafted and compiler specific function recognition, which allows the generation of more readable C code, but is rather inefficient in a general case. It contains a more sofisticated data types analysis than all decompilers until this point, since it tries to recognize types of arrays, pointers and structures. However, little detail is given on how this is done.

- 1993 Source /PROM Comparator At the Nuclear Electric plc, a tool was developed to demonstrate the correctness of the compilation of source code into Programmable Read-Only Memories (PROMs) in safety-critical systems [PW93].

This project describes a use of decompilation techniques to help demonstrate the equivalence of high-level and low-level code in a safety-critical system. The output of the decompiler is a special intermediate language that facilitates comparison of the source and decompiled codes. The symbol table from the compiler, as well as specific knowledge of the compiler facilitate the work.

• 1994 - Cifuente's PhD Thesis Cristina Cifuente's thesis "Reverse Compilation Techniques" [Cif94] sets the standards for the future decompilation research. In her work she showed the usefulness of data flow and control flow analyses in a decompiler. Both are common compiler analyses deeply studied in the computer science community. These techniques were implemented in the research decompiler dcc [Cif], which reads small Intel 80286/DOS programs and generates readable C code. • 1997-2000 - REC The Reverse Engineering Compiler is a retargetable decompiler which extends Cifuente's work in several ways. It handles several processors (Intel 386, Motorola 68K...) and multiple input formats (WLF, Windows PE...). It can use debugging information in the input file to name variables and functions. Variable arguments to library functions are handled well. Complex types such as arrays are translated into expressions. Registers and individual instructions semantics are visible in the decompiled output. However, the output is less readable.

Binary distributions of REC are available from [Cap03].

• 1999 - Mycroft's Type Based Decompilation In [Myc99] Mycroft describes a system for decompiling Register Transfer Language (RTL) to C. RTL is a common compiler intermediate representation. He uses type inferencing to find types from semantics of machine instructions and is able to generate code with pointers, structures and arrays.

The solution is not always unique, which requires the user intervention. Since no experimental results are given, the generality and feasibleness of this approach is uncertain.

• 1999 - Ward's FermaT transformation system Ward's FermaT system is based on formal transformations and is capable of transforming from assembly language to specifications [War99a, War00]. Even though the output is somewhat difficult to read, the system is validated by almost 2000 assembly language files which were translated to C and recompiled without error or warning.

FermaT is property of Software Migrations Ltd [Ltd01] and is now released under GPL license [War01a].

• **2002-2003** - **Boomerang** Boomerang [boo02, Tho] is a general decompiler which, for now can only decompile very small files.

## Chapter 2

# Hardware and Software Considerations

This work has been developed in the context of a retargetable decompiler for assembler languages with focus on digital signal processors (DSP). Even though the techniques presented here are architecture independent, they have been tested on the TIC62x DSP, which is a core with advanced architecture features. In order to motivate and understand the algorithms that will be explained later several hardware and software issues are discussed in the following sections.

Section 2.1 introduces the concept of parallelism and the hardware approaches to extract as much parallelism as possible from the programs. Digital Signal Processors and their technical evolution are presented in section 2.2. The software approaches to exploit parallelism are described in section 2.3. A description of the TIC62x DSP architecture concludes this chapter.

### 2.1 Hardware Issues

Parallel computing is the simultaneous execution of several tasks (which may, but do not need to be identical) [Mor98, HP90]. From the performance point of view, the advantages of executing several instructions in parallel is evident.

Thus, parallelism is one of the most interesting ideas in computing. Architectures and compilers have been striving for more than two decades to extract and utilize as much parallelism from the programs as possible in order to speed up computation.

#### 2.1.1 Parallelism

The notion of parallelism is used in two different contexts: the **available** and the **utilized** parallelism. The available parallelism in programs refers to the possibility to perform several operations in parallel. The utilized parallelism is the parallelism occurring during execution, that is, the tasks that the processor does actually execute at the same time.

#### Types and levels of available parallelism

We can distinguish between two types of parallelism: *functional* and *data parallelism*, where the first one is the parallelism available in a program and data parallelism refers to the data structures (perform a similar computation on many data objects simultaneously). Here we will refer only to the functional parallelism. More information about data parallelism can be found at [Mor98].

Parallelism in a program can be available at different levels

#### Instruction level

Particular instructions of a program may be executed in parallel.

#### Loop level

Consecutive loop iterations are candidates for parallel execution.

#### **Procedure level**

Parallel executable procedures.

The fact that parallelism is available does not necessarily mean that the processor takes advantage of it when executing the program. Consider the C statements

These two statements are completely independent from each other. Whatever program they belong to, it would certainly not affect to the final result if the second statement were executed in the first place. Since the execution order makes no difference, both statements could be executed in parallel. In such a case, instruction level parallelism is *available*.

However, if the architecture where they should be executed has only one execution unit, so that it can only carry out one instruction at a time, these two statements will certainly not be executed in parallel. Thus, the available parallelism cannot be utilized.

Furthermore, even if the architecture were able to execute these operations in parallel, if the compiler cannot detect that these statements can be executed in parallel, the available parallelism will not be utilized either.

#### Utilization of parallelism

Available parallelism can be utilized by architectures and compilers for speeding up computation. It is quite natural to utilize available parallelism, which is inherent in a conventional sequential program, at the instruction level by executing instructions in parallel, as seen in the example above. For this purpose, architectures are needed, which are capable of executing several instructions at the same time. Such architectures are referred to as instruction-level parallel architectures (ILP-architectures). Since available instruction-level parallelism is typically implicit in traditional sequential programs, it must be detected before execution. This is done, either by the compiler or by the ILP-architecture itself.

#### 2.1.2 ILP-Architectures

There are two basic ways of exploiting parallelism in ILP-architectures:

#### • Pipelining

In pipelining a number of functional units are employed in sequence to perform a single computation. These functional units form an assembly line called a *pipeline*. Each functional unit represents a certain stage of the computation and each computation goes through all stages of the pipeline.

#### • Replication

A natural way of introducing parallelism to a computer is the replication of functional units (for example, processors). Replicated functional units can execute the same operation simultaneously on as many data elements as there are replicated computational resources available.

These two approaches are orthogonal, meaning that they can both be used at the same time in an architecture design.

#### **Pipelined Architectures**

The term *pipelining* refers to the temporal overlapping of processing. To achieve this, the job of executing an instruction is divided into several steps or pipeline stages. A basic division would be

1. Fetch

Take the instruction that will be executed.

2. Decode

Extract the instruction in order to know which operation needs to be executed.

3. Execute

Compute the operation.

4. Write

Write the results of the operation.

Since not all instructions need the same number of stages, there are instructions that need longer to execute than others.

Unfortunately, the pipelining of a functional unit does not ensure that the execution of the program will be ideal. There are several situations, called hazards, that prevent the next instruction in the instruction stream from executing during its designated clock cycle and reduces the performance of the pipeline. Hazards in pipelines can make it necessary to stall the pipeline, that means that some instructions in the pipeline are delayed. The rest is allowed to proceed. As long as the pipeline is stalled, no other instructions can start execution, which obviously slows down the execution of the program. We will not extend the possible causes of the hazards and how to deal with them, since it is out of the scope of this thesis. More information about this topic can be found at [Mor98].

#### Superscalar and VLIW Architectures

Another way to exploit the instruction level parallelism is using replication. Superscalar and VLIW architectures consist of multiple execution units operating in parallel which are intended to exploit as much as possible the instruction level parallelism of the programs.

Superscalar architectures are able to dispatch a few independent instructions per clock cycle. Instructions are scheduled dynamically, being the processor who is responsible for the order in which they are executed and on which functional unit.

VLIW architectures get their name, Very Long Instruction Word from the way instructions are formulated. The length of the instructions depends on the number of execution units available and the code length required to control each of the units.