Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## MASTER THESIS

## An Extensible Interface Subsystem For A Novel Time-Triggered System-on-a-Chip Architecture

fulfilled at the institute of

COMPUTER ENGINEERING, REAL-TIME SYSTEMS GROUP of the

VIENNA UNIVERSITY OF TECHNOLOGY

under the guidiance of O. UNIV.-PROF. DR. PHIL HERMANN KOPETZ and

UNIV.ASS. DIPL.-ING. CHRISTIAN EL SALLOUM

by Вакк. тесни. Roman Seiger Overbeckgasse 37 A-1130 Wien

Vienna, August 2007

## An Extensible Interface Subsystem For A Novel Time-Triggered System-on-a-Chip Architecture

The Time-Triggered System-on-a-Chip (TTSoC) architecture provides a predictable integrated execution environment for the component-based design of many types of embedded applications. It was inspired by the experience gained in previous related research efforts, like the DECOS project, which focused on the integration of mixed-criticality application subsystems. The TTSoC architecture provides a predictable time-triggered Network-on-a-Chip (NoC) to maintain strict encapsulation of the different cores and to support safety-critical real-time applications. The encapsulation mechanisms facilitate to manage the rising complexity of today's and future embedded systems by allowing a larger system to be broken down into smaller subsystems that can be designed independently. The NoC establishes a message-based, a priori scheduled communication between different cores. This thesis focuses on the design and implementation of the NoC interface. In addition, possible extensions used to improve the functional range of the TTSoC, Middleware Plug-Ins, are introduced. To show the advantages of this concept, a Direct Memory Access (DMA) Plug-In and, to support application systems requiring Triple Modular Redundancy, a Voter Plug-In are described.

# Contents

| 1 | Intro | oductio | n                               | 1  |

|---|-------|---------|---------------------------------|----|

| 2 |       | kground |                                 | 5  |

|   | 2.1   |         | Triggered Communication         | 5  |

|   | 2.2   | 0       | ated vs. Federated Architecture |    |

|   | 2.3   | DECO    | S                               | 13 |

| 3 |       |         | ered System-on-a-Chip           | 15 |

|   | 3.1   |         | rements                         | 15 |

|   | 3.2   | Overvi  | ew                              | 17 |

|   | 3.3   | -       | pts                             | 19 |

|   |       | 3.3.1   | Time                            | 19 |

|   |       | 3.3.2   | Messages                        | 20 |

|   |       | 3.3.3   | Pulsed Data Streams             | 22 |

|   |       | 3.3.4   | Ports                           | 24 |

|   | 3.4   | Operat  | tion                            | 25 |

|   |       | 3.4.1   | Configuration                   | 26 |

|   | 3.5   | Compo   | onents                          | 28 |

|   |       | 3.5.1   | Trusted Interface Subsystem     | 28 |

|   |       |         | 3.5.1.1 MAC Layer               | 29 |

|   |       |         | 3.5.1.2 LLC Layer               | 29 |

|   |       | 3.5.2   | CNI Layer                       | 30 |

|   |       |         | 3.5.2.1 CNI Layer Extensions    | 30 |

|   |       | 3.5.3   | Interconnect                    | 31 |

|   |       | 3.5.4   | Resource Management Authority   | 31 |

|   |       | 3.5.5   | Trusted Network Authority       |    |

|   |       |         |                                 |    |

| 4 |       |         | NI Layer                        | 35 |

|   | 4.1   | Overvi  | ew                              | 35 |

|   | 4.2   | Interfa | ces                             | 36 |

|   |       | 4.2.1   | MAC Interface                   | 37 |

|   |       | 4.2.2   | Host Interface                  | 39 |

|   |       |         | 4.2.2.1 Physical Host Interface | 39 |

|   |       |         | 4.2.2.2 Logical Host Interface  | 41 |

|   | 4.3   | Implen  | nentation                       | 53 |

|   |       | 4.3.1   | LLC Layer                       | 53 |

|     |        |          | 4.3.1.1    | Address Logic                                           | 54  |

|-----|--------|----------|------------|---------------------------------------------------------|-----|

|     |        |          | 4.3.1.2    | Configuration Memory                                    | 60  |

|     |        |          | 4.3.1.3    | Watchdog Service                                        | 62  |

|     |        |          | 4.3.1.4    | Error Status Register                                   | 63  |

|     |        | 4.3.2    | CNI Lay    | er                                                      | 64  |

|     |        |          | 4.3.2.1    | Communication Network Interface                         | 65  |

|     |        |          | 4.3.2.2    | Host Address Decoder                                    | 67  |

|     |        |          | 4.3.2.3    | Interrupt Service                                       | 67  |

| 5   | CNI    | Layer    | Extensio   | 15                                                      | 69  |

|     | 5.1    | Hardw    | are Midd   | leware Bricks                                           | 69  |

|     | 5.2    | Middle   | eware Plu  | g-Ins                                                   | 73  |

|     |        | 5.2.1    | Direct M   | Iemory Access Plug-In                                   | 76  |

|     |        |          | 5.2.1.1    | $Implementation \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 76  |

|     |        |          | 5.2.1.2    | Direct Memory Access Plug-In Register File              | 81  |

|     |        | 5.2.2    | Voter Pl   | ug-In                                                   | 83  |

|     |        |          | 5.2.2.1    | 1                                                       | 87  |

|     |        |          | 5.2.2.2    | Voter Plug-In Register File                             | 93  |

|     |        | 5.2.3    | Other Pl   | lug-Ins                                                 | 95  |

| 6   | Con    | clusion  |            |                                                         | 97  |

| Α   | Оре    | n Core   | Protoco    | I                                                       | 99  |

|     | A.1    | OCP S    | Signals    |                                                         | 99  |

|     | A.2    | OCP (    | Operation  |                                                         | 101 |

| В   | Ava    | on Ada   | apter      |                                                         | 103 |

|     | B.1    | Avalor   | n Memory   | -Mapped Interface                                       | 103 |

|     | B.2    | Avalor   | n Slave Ac | lapter                                                  | 103 |

|     | B.3    | Avalor   | n Master A | Adapter                                                 | 105 |

| С   | Pow    | erlink E | Bus Adap   | oter                                                    | 107 |

|     | C.1    | Powerl   | Link Coni  | nection Bus                                             | 107 |

|     | C.2    | Implen   | nentation  |                                                         | 107 |

| Bil | bliogi | raphy    |            |                                                         | 111 |

# **List of Figures**

| 2.1  | TTP/C Cluster with TTP/A Transducer Cluster          |   |   |   |   | 6               |

|------|------------------------------------------------------|---|---|---|---|-----------------|

| 2.2  | Sparse Time Base                                     |   |   |   |   | 7               |

| 2.3  | State Information vs. Event Information              |   |   |   |   | 8               |

| 2.4  | The DECOS Integrated System Architecture             | • |   |   | • | 14              |

| 3.1  | Overview of the TTSoC architecture                   |   |   |   |   | 18              |

| 3.2  | TTSoC Architecture Time Format                       |   |   |   |   | 19              |

| 3.3  | NoC Message                                          |   |   |   |   | $\frac{10}{21}$ |

| 3.4  | NoC Pulsed Data Streams                              |   |   |   |   | 23              |

| 3.5  | TTSoC Operation                                      |   |   |   |   | $\frac{20}{26}$ |

| 3.6  | TTSoC Message Configuration Procedure                |   |   |   |   | $\frac{20}{27}$ |

| 3.7  | Trusted Interface Subsystem (TISS) Overview          |   |   |   |   | $\frac{21}{28}$ |

| 3.8  | Different Interconnect Topologies                    |   |   |   |   | $\frac{20}{32}$ |

| 0.0  | Different interconnect topologies                    | • | • | · | • | 52              |

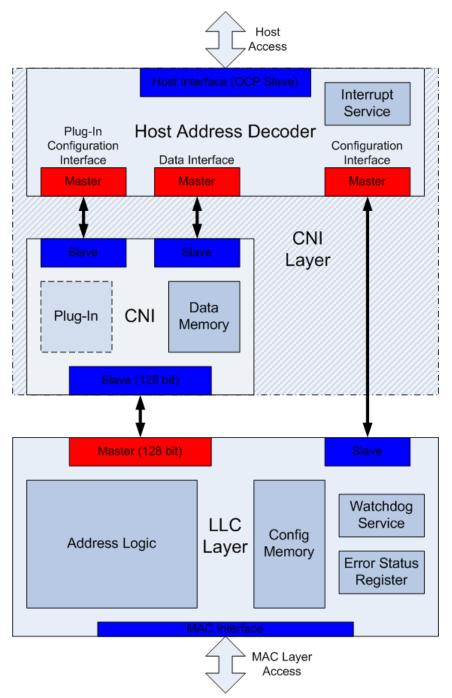

| 4.1  | Overview of the LLC and CNI Layers                   |   |   |   |   | 36              |

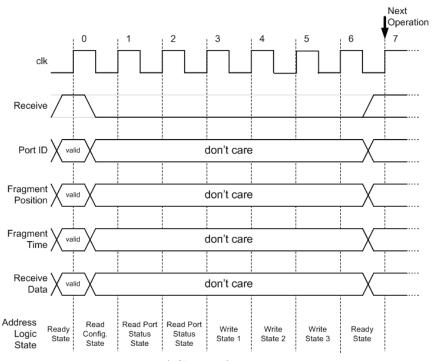

| 4.2  | Medium Access Control (MAC) Interface Receive Timing |   |   |   |   | 38              |

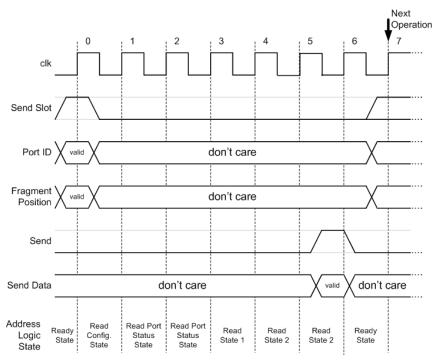

| 4.3  | MAC Interface Send Timing                            |   |   |   |   | 39              |

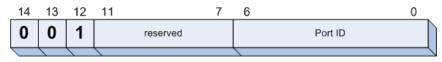

| 4.4  | Port Address                                         |   |   |   |   | 42              |

| 4.5  | State Port                                           |   |   |   |   | 43              |

| 4.6  | Input State Port Port Flags                          |   |   |   |   | 44              |

| 4.7  | Output State Port Port Flags                         |   |   |   |   | 44              |

| 4.8  | Input Streaming Port Port Flags                      |   |   |   |   | 45              |

| 4.9  | Output Streaming Port Port Flags                     |   |   |   |   | 45              |

| 4.10 | Event Port Flags                                     |   |   |   |   | 46              |

|      | Event Port                                           |   |   |   |   | 47              |

|      | Register Addressing                                  |   |   |   |   | 48              |

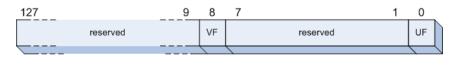

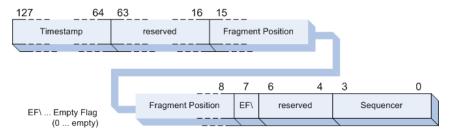

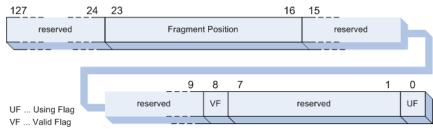

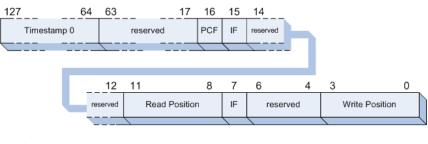

|      | LLC Layer and CNI Layer Register File                |   |   |   |   | 49              |

|      | Interrupt Status Register                            |   |   |   |   | 50              |

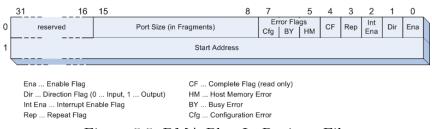

|      | Port Configuration Data                              |   |   |   |   | 52              |

|      | Port Configuration Addressing                        |   |   |   |   | 53              |

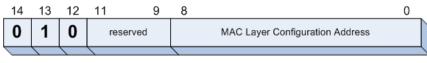

|      | MAC Layer Configuration Address Space                |   |   |   |   | 53              |

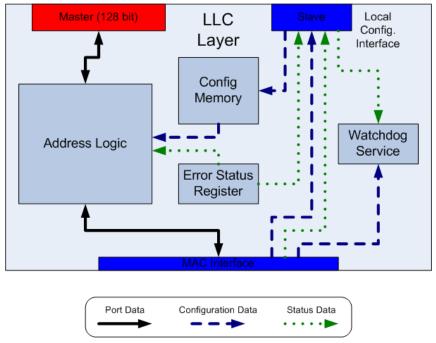

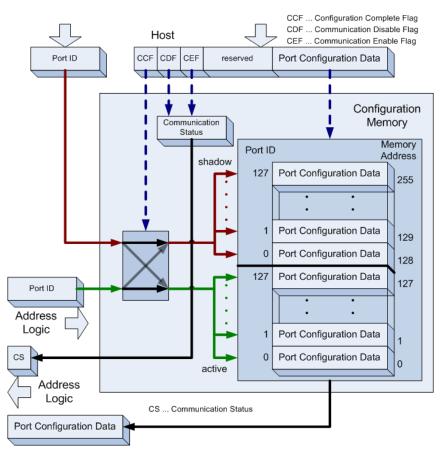

|      | Control and Data Flow inside of the LLC Layer        |   |   |   |   | 54              |

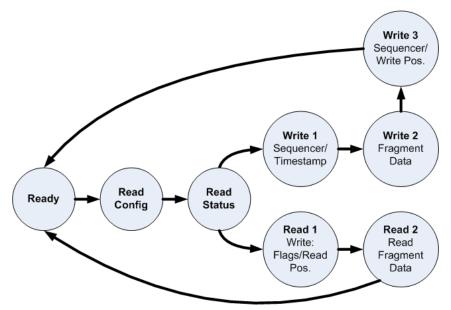

|      | Address Logic Finite State Machine                   |   |   |   |   | 55              |

|      | Operation of the Configuration Memory                |   |   |   |   | 62              |

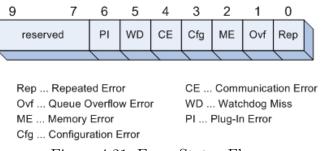

|      | Error Status Flags                                   |   |   |   |   | 63              |

| 11   |                                                      | • | · | • | • | 00              |

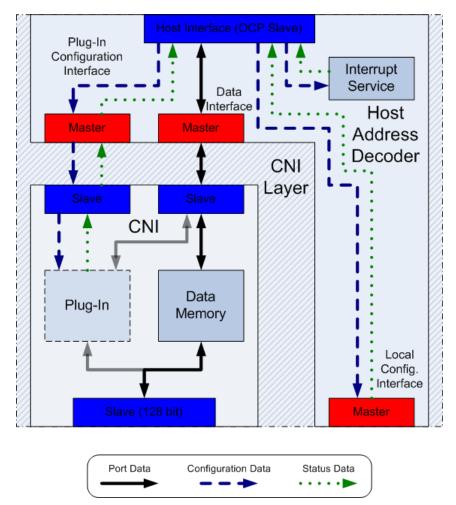

| 4.22 | Control and Data Flow inside the CNI Layer                  | 64 |

|------|-------------------------------------------------------------|----|

| 4.23 | Data Word Width Reduction in the Communication Network      |    |

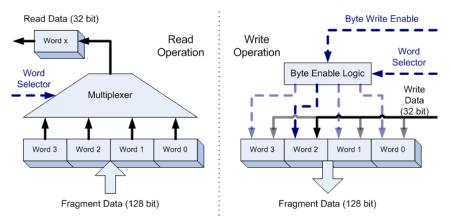

|      | Interface (CNI)                                             | 65 |

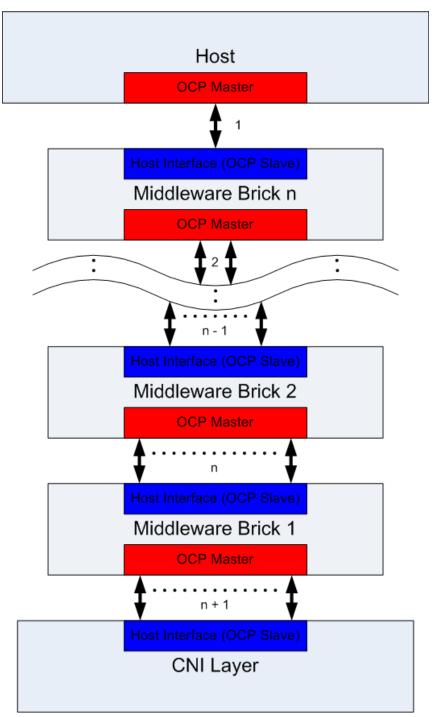

| 5.1  | Stacking of Hardware Middleware Bricks                      | 71 |

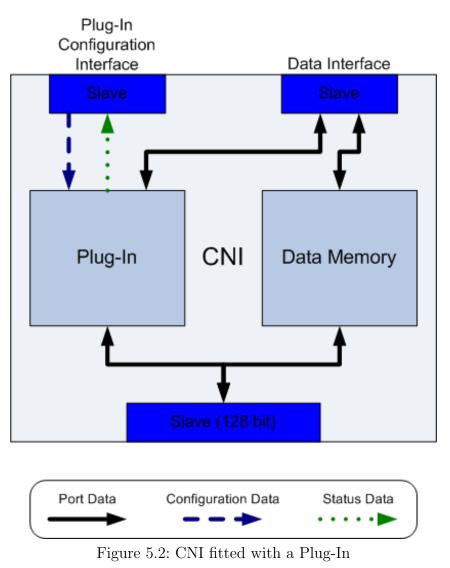

| 5.2  | CNI fitted with a Plug-In                                   | 74 |

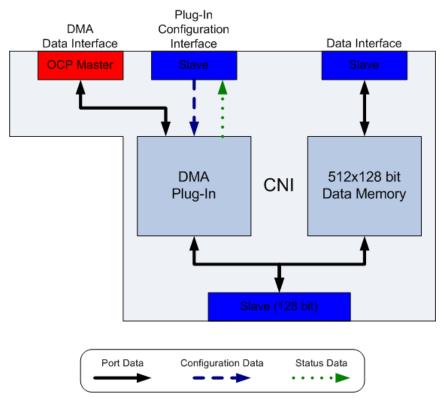

| 5.3  | CNI fitted with a Direct Memory Access (DMA) Plug-In        | 77 |

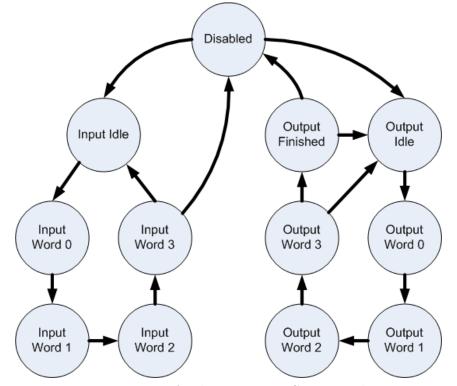

| 5.4  | DMA Plug-In Finite State Machine                            | 79 |

| 5.5  | DMA Plug-In Register File                                   | 81 |

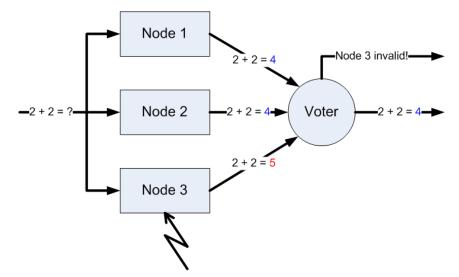

| 5.6  | Triple Modular Redundancy (TMR) System with Voter           | 84 |

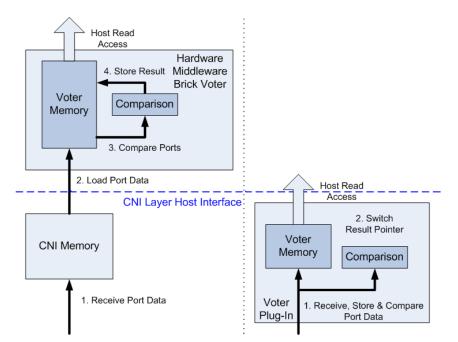

| 5.7  | Comparison: Hardware Middleware Brick Voter / Voter Plug-In | 85 |

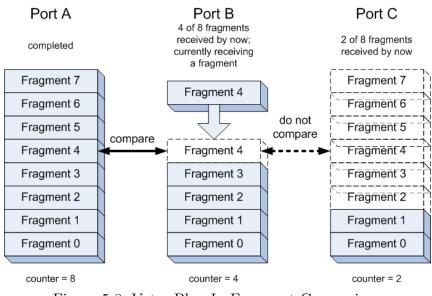

| 5.8  | Voter Plug-In Fragment Comparison                           | 87 |

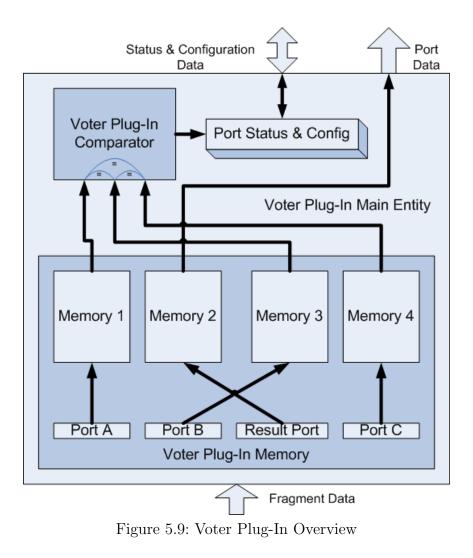

| 5.9  | Voter Plug-In Overview                                      | 89 |

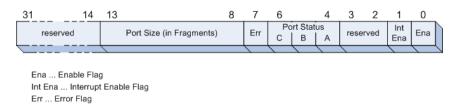

| 5.10 | Voter Plug-In Register                                      | 93 |

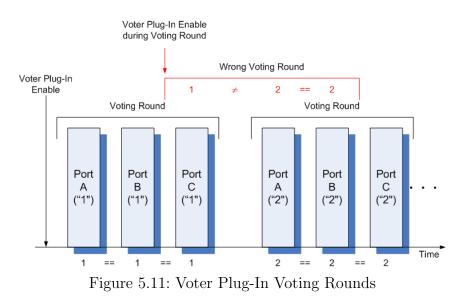

| 5.11 | Voter Plug-In Voting Rounds                                 | 94 |

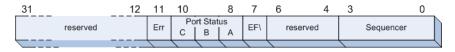

|      | Voter Plug-In Result Port Port Flags                        | 95 |

# List of Tables

| 3.1 | Time Format Comparison: TT Ethernet vs. TTSoC          | 20  |

|-----|--------------------------------------------------------|-----|

| 4.1 | Open Core Protocol (OCP) Signals used by the CNI Layer | 40  |

| 4.2 | Port Memory Usage                                      | 48  |

| 4.3 | Fragment Address Calculation                           | 57  |

| 4.4 | Output Event Port Behavior                             | 58  |

| 4.5 | Input Event Port Behavior                              | 59  |

| 5.1 | DMA Plug-In Memory Usage                               | 78  |

| 5.2 | Voter Plug-In Memory Usage                             | 88  |

| 5.3 | Pointer Exchange due to Voting Results                 | 90  |

| 5.4 | Voting Results                                         | 94  |

| A.1 | OCP Master Commands                                    | 00  |

| A.2 | OCP Slave Response Encoding                            | .01 |

| B.1 | Avalon Slave Adapter Signals                           | .04 |

| B.2 | Avalon Master Adapter Signals                          | 05  |

## **1** Introduction

Over the last years, an increasing amount of embedded computer systems were designed and integrated into consumer products, especially in the automotive industry. In a competitive economic environment where time-to-market issues and product originality are the driving factors for development, embedded computer systems, which, among other advantages, offer the possibility to improve a car's performance envelope while optimizing its fuel efficiency and to introduce additional comfort functions, could achieve a sustained, extraordinary success. This trend, supported by the semiconductor industry which made a vast progress in developing smaller, more powerful, and more energy efficient systems, is continuing or even increasing, although not all of its effects are beneficial. Among the problems attached to the inflationary replacement of mechanical or hydraulic systems by embedded computer systems are rising development and electronic hardware costs, dependability requirements, and Intellectual Property (IP) protection [OPHS06, p. 84], to point out only some of them.

With these challenges in mind, the Dependable Embedded Components and Systems (DECOS) project [Dep] focuses on the development of an integrated, distributed architecture capable of managing arising complexity issues as well as economical difficulties. One aspect of the DECOS architecture is to brake down the whole application system into so called Distributed Application Subsystems (DASs). Each DAS consists of a number of jobs and is responsible for providing a meaningful part of the overall service of the application system. This and other concepts behind the DECOS architecture and a number of experiences gained during the DECOS design process were reviewed carefully, leading to the decision to further improve the DECOS architecture. The intended goal was to develop a System-on-a-Chip (SoC) capable of housing jobs of different Distributed Application Subsystems with different criticality levels on the same microchip while preserving strong encapsulation of the single DASs.

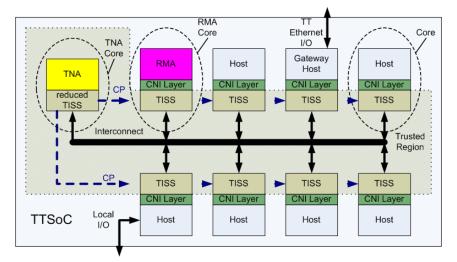

By adapting the well established Time-Triggered Architecture (TTA) [KB03] the design led to the Time-Triggered System-on-a-Chip (TTSoC) architecture, an SoC housing multiple potentially heterogenous cores. Predictable communication among the single cores of the TTSoC is provided by a deterministic time-triggered Network-on-a-Chip (NoC). A chip-wide global time service which can be synchronized to external time references (e.g., the Global Posi-

tioning System (GPS) time) allows to temporally coordinate the action of multiple cores. Among other additional services, strict encapsulation of the cores to prevent any unintended interference is one of the major goals of the Time-Triggered System-on-a-Chip architecture. As a guard for the time-triggered NoC, the Trusted Interface Subsystem (TISS) is introduced. The TISSs protect the NoC from cores violating their temporal specification and furthermore provide a small and stable set of generic services which are required by the different cores. These generic services can be customized by adding Middleware Plug-Ins taylored to the required application domain (e. g., fault tolerance, security, etc.).

Dynamic resource management (i.e., allocation of computational and communication resources at runtime) in the TTSoC architecture is carried out by a Resource Management Authority (RMA) and a Trusted Network Authority (TNA) as a two-stage process. While the RMA dynamically builds and adapts the resource allocation, the certified TNA checks this allocation for conflicts and ensures that safety-critical functions are always provided with sufficient resources.

Since every core in the TTSoC architecture hosts only a single job of a DAS and unintended interference between DASs is prevented by the TTSoC architecture, each DAS can be designed independently from the other DASs, limiting the cognitive complexity of the design process and simplifying the final integration of the Distributed Application Subsystems.

By introducing gateways, multiple TTSoCs can be combined to form a cluster in a higher-level communication system (e.g., Time-Triggered Ethernet [Ste06]), therefore a Distributed Application Subsystem can be spread among different (physically separated) TTSoCs.

To make use of the communication service of the Network-on-a-Chip and the various other services the TTSoC architecture provides, a standardized host processor interface is required. To adapt to the changing demands of different applications, the interface subsystem of the TTSoC architecture has to provide possibilities to extend it with additional, customized hardware components providing domain specific higher-level services. This thesis describes the concept and the implementation of such an extendible interface subsystem for the Time-Triggered System-on-a-Chip architecture.

The thesis is structured as follows: Chapter 2 points out some of the background issues that led to and/or influenced the development of the Time-Triggered System-on-a-Chip architecture, which is described in chapter 3. Being the main subject of this thesis, the interfaces (sections 4.2 and 4.2.2.2) as well as the implementation (section 4.3) of the LLC and CNI Layers are discussed in chapter 4. To enlarge the functional range of the TTSoC architecture, the CNI Layer was designed to be extendable. Chapter 5 deals with the different kinds of CNI Layer extensions. Chapter 6 offers a conclusion of the thesis, and gives some suggestions for future developments concerning the Time-Triggered System-on-a-Chip architecture. Appendices A, B, and C conclude this thesis with detailed information on the Open Core Protocol (OCP), an Avalon Adapter, and a Powerlink Bus Adapter, respectively.

1 Introduction

## 2 Background

## 2.1 Time-Triggered Communication

An embedded system has to be aware of the progression of time if its services should be of any use in the real world. Any results presented by an embedded system have to be valid not only in the value domain, but also have to be "on time". Otherwise, no use can be made of the results, even if correct, since the time in the real world advanced and the achieved results became irrelevant.

To avoid such situations, embedded systems can be designed with sufficient processing power to guarantee completion of their tasks before reaching the deadline at which the produced results would become outdated. Very detailed analysis of the system's timely behavior (reaction time, worst case execution time (WCET), etc.) and the time constraints arising from the application environment (i.e., the deadlines that have to be met) become necessary to ensure dependable real-time behavior.

The efforts to guarantee timeliness rise significantly when dealing with larger distributed embedded systems. Communications between components of a distributed system and the possibility of unpredictable behavior due to indeterministic arbitration or scheduling algorithms, along with possible inherent indeterminism of the application itself make matters worse.

A more promising approach to cope with the increasing effort in designing and evaluating real-time application systems is not only to design embedded systems that are aware of real-time, but to make the notion of time an integral part of a dependable distributed embedded system architecture.

The Time-Triggered Architecture (TTA) [KB03] provides a solution to the increasing complexity of large real-time embedded systems by decomposing such a system into nearly autonomous nodes and clusters and introducing a fault-tolerant global time base used for interface specification, error detection, communication protocols, and to guarantee the timeliness of real-time applications. Research on the TTA started at the Technical University of Berlin in 1979 and continued at the Vienna University of Technology since 1982. The TTA has been further developed ever since, including implementation of several

prototype and even commercially used systems. To ensure further development and marketing of the time-triggered technology, a spinoff company of the Vienna University of Technology, the TTTech Computertechnik AG [TTTb] was founded in 1998.

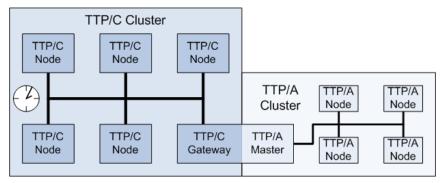

Two time-triggered communication services are described by the TTA, the TTP/C [TTTa] and the TTP/A [EEE+01] protocol. The TTP/C protocol is a fault-tolerant time-triggered communication protocol connecting several distributed nodes of a system to form a cluster and providing fault-tolerant clock synchronization between the nodes, a membership service to monitor the systems "health-state", and message transport with known delay and bounded jitter. The TTP/A protocol is a time-triggered fieldbus protocol which is used to connect low-cost smart transducers forming a transducer cluster to a so called master node. This master node can act as a gateway to a communication system on a higher level, like a TTP/C cluster (figure 2.1).

Figure 2.1: TTP/C Cluster with TTP/A Transducer Cluster

Some concepts of the Time-Triggered Architecture model which largely influenced the development of the Time-Triggered System-on-a-Chip architecture are described in more detail in the following paragraphs.

#### Time

The key concept of the TTA is the use of (physical) real-time as an integral part of the system.

Any happening occurring at a specific time instant, either in the real world (e.g., turning on a switch) or inside the system (e.g., reception of a message), is called an event. A distributed real-time system has to be capable of temporally ordering these events, even if they happen at different nodes which can be distributed over multiple SoCs. To accomplish this task, a system-wide (global) time base, synchronized among all nodes, is needed. By using the same global time in each node, every event can be timestamped and a temporal order of events can be maintained throughout the system.

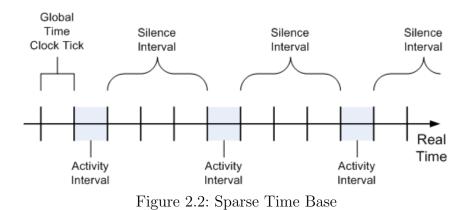

The difficulties in using a global time base in distributed nodes are the impossibility to perfectly synchronize distributed clocks and the denseness of realtime, i. e., no matter how small the clock granularity is, an event can still occur in between two clock ticks and, as a consequence, can be timestamped differently by two different nodes. Since clocks with an infinetely small granularity are physically impossible, the TTA introduces a sparse time base [Kop04b, p. 55].

Time is divided into an infinite sequence of activity and silence intervals in the sparse-time model, in which the duration of the activity interval has to be larger than the precision of the clock synchronization. Figure 2.2 depicts the concept of a sparse time base.

Any events that happen in the same activity interval (at different nodes) are considered simultaneous by the system, events occurring in different activity intervals can definitely be temporally ordered. All events triggered by the system itself (e.g., sending of a message) are restricted to the activity intervals, while events happening during a silence interval outside of the sphere of control of the nodes have to be aligned to the sparse time base by using an agreement protocol.

#### State Information vs. Event Information

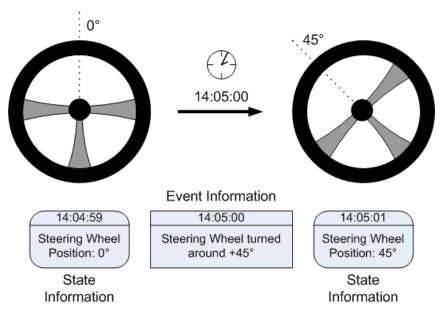

Embedded systems interact with their environment by observing its properties and reacting to them. These observations are done by a variety of different kinds of sensors (e.g., switches, temperature sensors, etc.) which examine the current state of the environment. The examination results can be stored or transmitted inside the system by means of event or state information, enclosed in state or event messages, respectively.

An event is a change of the state of an entity at a specific time instant, therefore event information consists of the name of the observed entity, the time of the event, and the difference between the state before and after the event.

Since the current state of an entity is determined by the initial state and all state changes that occurred since then, all events have to be recorded by an application to ensure a consistent view of its environment. This implies the need for messages containing event information to be sent and received exactly once. Any lost or repeated event message leads to a wrong internal image of the actual state of the observed entity, hence a communication protocol supporting and ensuring exactly-once semantics is required.

Figure 2.3: State Information vs. Event Information

State information consists of the name of the observed entity, the time of the observation, and the state of the entity at observation time. The initial state of the observed entity and/or previous state changes leading to the current state are inherently enclosed in this information. As a consequence, state messages are idempotent and require at-least-once semantics. Repeated state messages do not corrupt the internal image of the observed entity, but lost state messages may lead to an internal image which is not up-to-date due to missed state

changes. The difficulty arising with state messages is to determine the optimal update interval of the state information. An update interval which is too long may lead to missed state changes of the observed entity (e.g., a temperature spike at a sensor in between two state messages may not be recognized by a controlling component), whereas a too short update interval may produce unnecessary traffic on the communication system.

#### Time-Triggered vs. Event-Triggered Communication

Regardless of the type of information contained in a message, the transmission of the message can be triggered by either reaching a specific time instant or by the occurrence of an (external) event.

**Time-triggered communication** is characterized by a schedule which determines the transmission times of certain messages, usually organized in time periods and phase offsets. These periods and phases can be calculated a priori and remain constant during the whole system operation time, or the schedule can be changed regularly to adapt to different communication requirements throughout the system operation time. By nature, a time-triggered communication system transports state messages in regular intervals, no matter if a state change at the observed entity has occurred.

The advantage of the time-triggered approach is that any message sent over the communication system can be identified solely by its send time instant. Neither a sender nor a receiver identification is required to be enclosed in the message since the time of the send instant inherently identifies the message. The active schedule, which is common knowledge at the sending and the designated receiving core(s), is examined with respect to the current time and subsequently triggers a send or receiving operation. Furthermore, a missing message due to an erroneous core which missed a scheduled send slot can easily be detected by a diagnostic entity or by the other cores, simply by not receiving any message. Corrective actions can be commenced immediately to protect the whole system from failing (e.g., restart or disabling of the erroneous core, activation of backup cores, entering a system-wide fail-safe state, etc.).

The difficulty of a time-triggered communication system is to establish a synchronized distributed global time base among all cores with sufficient precission. With respect to dependable distributed embedded systems, the required clock synchronization has to be fault-tolerant to ensure communication, and thus (possibly reduced) system operation, despite the presence of arbitrary (i. e., Byzantine) faults. Another necessity for dependable operation is to restrict core accesses to the communication medium to their designated sending intervals. A core trying to send a message outside of its sending interval will most likely corrupt the data sent by another core, or even mask out core failures by preventing detection of a missing message. The TTA introduces guardians (bus guardians attached to each core in case of a bus topology or guardians located in the center of a star topology network) to protect the system from arbitrary core failures (e.g., "babbling idiot" failures). These guardians ensure fail-silent behavior of all cores by restricting the communication medium access to the respective sending intervals and blocking any other sending attempt.

**Event-triggered communication** does not follow a designated schedule. The sending of an event message is triggered by the occurrence of the associated event. Such events can have an external source (e. g., a user pressing a button, a temperature value exceeding a threshold) or can be triggered by the embedded system itself (e. g., completion of a calculation).

Since an event-triggered communication system only starts the transmission of a message if an event (a state change) occurred, traffic on the network can be significantly reduced as long as the frequency of occurring events is sufficiently low, in contrast to a time-triggered communication system, which transmits messages regardless of any state change. This allows not only for a more efficient use of the available network bandwidth, but also helps to save power, which is a crucial requirement of embedded systems.

On the downside of event-triggered communication systems is the need to enclose sender and/or receiver identification information in every message, increasing the bandwidth usage. In addition, the gain in available bandwidth can be limited by the peak-load of the network (worst-case scenario, usually reached if all cores try to send simultaneously). If the communication system is designed with enough spare bandwidth to handle the rare-event peak-load scenario without violating any system deadlines, the spare bandwidth is useless and wasted most of the operational time of the system (assuming the peak-load scenario is rare under normal operating conditions). By designing the communication system to make a more efficient use of the available bandwidth under normal conditions while abandoning the ability to fulfill all deadlines under higher load, communication integrity can not be guaranteed under peak-load scenarios. This is a design decision which has to be taken according to the intended use of the embedded system (e.g., safety-critical, i.e., (partially) operational under all circumstances, or accepting possible system breakdowns due to high load).

The lack of a priori knowledge of send instants prevents the communication system from detecting a failed core by monitoring missing messages. A fail-silent core shows the same behavior when failed as a working core when no events occur at its observed entity. Even worse, cores with an arbitrary failure mode may block the communication system by uninterrupted sending of messages ("babbling idiot" behavior). As a consequence, the application has to perform failure detection inside the cores by means of restricting network access and/or some kind of fail-silent failure detection (e.g., regular lifesign ("heartbeat") messages), if dependability is to be achieved.

### 2.2 Integrated vs. Federated Architecture

A distributed application can be classified with respect to the overall system architecture. Although most real systems are hybrid systems, the two extremes, integrated and federated architectures, are briefly discussed in this section.

A federated architecture is characterized in that every major function of an embedded system is allocated to a dedicated hardware unit. [Kop04a, p. 160] This results in a vast number of independent hardware subsystems, each performing a certain, specialised function, with minimal or even no interaction between the different subsystems. Every single subsystem is treated as a "stand-alone" system, therefore any maintenance or upgrade actions, although less complex, have to be performed separately for every system. In spite of these and other deficiencies, several advantages of federated architecures can be identified, the major ones are described in [OPHS06, p. 84-85] and briefly listed below.

- **Fault containment** A hardware fault in a core or a disturbance of the communication medium of a federated architecture only affects a single application subsystem, the other application subsystems are not concerned, whereas a hardware fault occurring in a core or communication medium of an integrated architecture may influence multiple different application subsystems.

- **Error containment** Error distribution among different subsystems is prevented (or at least reduced) by the nature of federated architectures, since interaction between different subsystems is limited.

- **Independent development** The independence of the different subsystems allows for their independent development, therefore the subsystems can be manufactured by different vendors or design teams and easily combined to form the whole application system.

- **Complexity control** With no need to adapt a subsystem to operate using the same resources as another subsystem, as inevitable in an integrated architecture, a federated architecture helps to keep the overall system complexity low. Any side effects or dependencies between the different sub-

systems, which significantly increase the cognitive complexity of a system, are prevented.

We call an architecture integrated if a single core can support a number of partitions that can host different functions and a physical wire can host many different virtual encapsulated communication channels of known temporal characteristics. [Kop04a, p. 160] In an integrated architecture, different functions, located in their own, separated subsystems in a federated architecture, are merged into a single system, sharing common resources. Some advantages of integrated architectures are concisely listed below, taken from [OPHS06, p. 85].

- Hardware cost reduction Sharing resources between different application subsystem can significantly reduce the number of required hardware units (e.g., processors, sensors, communication media, etc.), resulting in reduced overall system hardware cost.

- **Dependability improvements due to reductions of wiring and connectors** Since a large amount of electrical failures in embedded systems is due to connector or wiring problems, dependability can be improved by an integrated system, which shares communication media and therefore uses less physical wires in contrast to a federated system.

- **Fault-tolerance** In integrated as well as in federated architectures, fault tolerance is achieved by using replicated hardware. The benefit of an integrated architecture is that these replicated resources are available among the different subsystems, while every subsystem in a federated architecture has to provide its own replicated hardware. Failure of a subsystem in a federated architecture may occur in spite of the presence of a sufficient number of free overall system resources able to tolerate the occurred fault, since a subsystem cannot access the spare resources of other subsystems.

- **Improved coordination of application subsystems** Tight coupling of different subsystems, which is needed by a growing number of complex embedded application systems, is supported by integrated architectures, the coordination of inter-subsystem communication is simplified in contrast to federated architectures.

Both, integrated and federated architectures, offer advantages for future embedded application systems. The ideal future embedded application system would combine the complexity management advantages of the federated approach, but would also realize the functional integration and hardware efficiency benefits of an integrated system. [Ham03, p. 32] To achieve this goal, logical separation and strong encapsulation of different Distributed Application Subsystems (DASs) in an integrated system has to be provided by the underlying system architecture. Although parts of different Distributed Application Subsystems may share the same resources, e.g., the same microchip, the same physical communication medium, etc., the system architecture has to prevent any side effects or unwanted dependencies between the different DASs and has to support the possibility of an independent development of the different Distributed Application Subsystems.

## 2.3 DECOS

The Dependable Embedded Components and Systems (DECOS) project [Dep] is part of the Sixth Framework Programme (FP6) for Research, Technological Development and Demonstration (RTD) of the European Community, which started in 2002. *DECOS methodically targets, investigates, and develops approaches to significantly alleviate* ... the identified five key obstacles ... to the deployment of advanced electronic functions in embedded systems. [CS04, p. 1] Those key obstacles are (taken from [CS04, p. 1]):

- Electronic Hardware Cost

- Diagnosis and Maintenance

- Dependability

- Development Cost

- Intellectual Property (IP) Protection

The DECOS project intends to provide an integrated distributed architecture, consisting of pre-validated hardware components, which allows to execute certified or custom software modules while providing strict encapsulation of different subsystems to ensure their independent development, seamless integration, and operation without any unwanted side effects.

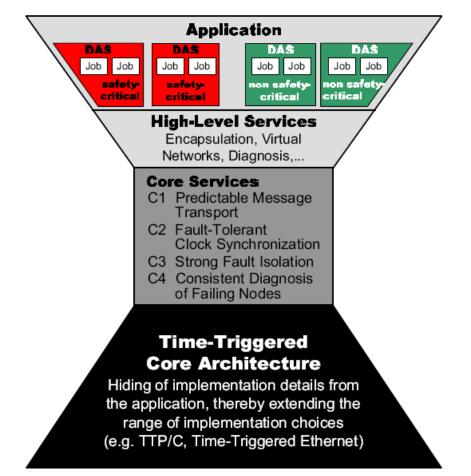

The DECOS architecture offers a framework for the development of distributed embedded real-time systems integrating multiple Distributed Application Subsystems (DASs) with different levels of criticality and different requirements concerning the underlying platform. It is based on a time-triggered core architecture and a set of high-level services that support the execution of newly developed and legacy applications across standardized technology-invariant interfaces. [POT+05, p. 3]

In an ebedded system using the DECOS architecture, the overall application system functionality is divided into Distributed Application Subsystems (DASs), each of which should provide a meaningful part of the service of the overall system (e.g., a brake-by-wire DAS could be responsible for all matters concerning the brake service of a car). Each DAS can be further devided into jobs. A job is the basic unit of work that employs the communication system for exchanging information with other jobs, thus working towards a collective goal. [POT<sup>+</sup>05, p. 4] Figure 2.4 displays a schematic of the DECOS architecture.

Figure 2.4: The DECOS Integrated System Architecture [POT<sup>+</sup>05, p. 4]

A prototype implementation of a DECOS cluster was built at the Technische Universität Wien, Institut für Technische Informatik, and described in [OPHS06, sect. 5].

During the course of the DECOS project, the demand for a System-on-a-Chip (SoC) fulfilling the requirements of the DECOS architecture, namely strict encapsulation of DASs and a dependable, deterministic communication system, arose. As a consequence, the development of the Time-Triggered System-on-a-Chip (TTSoC) architecture (chapter 3) was initiated.

# 3 Time-Triggered System-on-a-Chip

## 3.1 Requirements

In contrast to other System-on-a-Chip (SoC) development efforts aiming at improvement of overall system performance by designing more sophisticated, close-coupled processor cores with strong mutual dependencies, like the Cell Processor [PAB<sup>+</sup>06], the development of the TTSoC architecture described herein was focused on the overall architecture of the SoC and the used onchip communication system, namely the Network-on-a-Chip (NoC). The overall goal of the TTSoC project was to design an SoC architecture which provides strict encapsulation of all host processors and dependable and predictable communication among them to support safety-critical Distributed Application Subsystems (DASs).

As a result, the TTSoC architecture allows the use of arbitrary application specific host processors, as long as a proper interface to the NoC can be established.

The main requirements of the Network-on-a-Chip, identified during the development of the Time-Triggered System-on-a-Chip architecture, are briefly described in the following list.

- **Dependability** In order for a safety-critical DAS to function within the given parameters, the underlying communication network has to fulfill the same or even higher dependability demands. The core components of the TTSoC architecture are designed to be certified to the highest criticality level required by a given application.

- **Encapsulation** A single TTSoC may not run safety-critical applications on all of its cores, but a mixture of safety-critical and standard applications, e.g., parts of a brake-by-wire DAS and a multimedia DAS. To prevent disturbance of the critical DASs caused by faulty or mischievous cores, the NoC has to ensure strict encapsulation of all DASs. Any communication between different DASs has to be regulated, blocking of the communication medium, corruption of communication data, message spoofing,

or similar illegitimate actions by any core have to be suppressed. Even an arbitrary (i.e., Byzantine) failure of a non safety-critical host is not allowed to hamper the service of the other cores of the TTSoC.

**Controlled Complexity** Large distributed embedded systems can become fairly complex, which makes them hard to design and maintain. By encapsulating the application subsystems, the TTSoC architecture allows a system designer to focus on a specific subsystem without the need to know all aspects of the overall system architecture. Every host processor connects to the communication system through a standardized interface, the exact location inside the network (i. e., on which core the software is running) is of no concern during the design process of the host software. Even a migration to another core after finishing the application design or during the system's operational life due to maintenance issues is possible in a well designed application system.

This location-independent behavior is not restricted to a single TTSoC, a cluster of multiple TTSoCs, connected through gateways, can be built to allow a physical separation of different jobs in a DAS. Being able to migrate a job to another core without the need to adapt the host software allows for every DAS to be designed for its own, knowledge of other DASs sharing the same TTSoC or TTSoC cluster is not necessary at design time.

- **Real-Time** Many distributed embedded systems require real-time behavior. To support such systems, the TTSoC architecture has to provide a distributed global real-time service.

- **Replica Determinism** In highly dependable systems, such as drive-by-wire systems, the use of Triple Modular Redundancy (TMR) is very common. For an efficient use of TMR, an application has to show replica deterministic behavior [Pol94]. As a consequence, all components of the implemented NoC have to be replica deterministic too.

- **Resource Efficiency** The use of on-chip resources has to be limited for an embedded system to be competitive on the market. The two crucial resources of an embedded SoC are **chip area** and **power**. While the chip area used by the SoC is determined by the design of all of the implemented SoC components and remains constant during the system's life cycle, power consumption can be regulated "on-line" during operation.

The TTSoC architecture design aims at reducing the used chip area by building all components as compact as possible. Power is considered a dynamic resource, the TTSoC architecture is intended to manage the available on-chip power by disabling the power supply of cores not needed at the moment, reducing a host processor's internal clock frequency, and/or setting low power consumption host modes in low-duty situations. Besides saving power on mobile, battery supplied embedded systems (e.g., in a car), the intention is to secure an uninterrupted power supply for cores running safety-critical applications.

- **Reusability** Any distributed communication system should provide a uniform interface to the attached host processors to simplify access to all communication functions. The NoC fulfills these requirement by introducing a standardized Host Interface providing independence of application software from the communication network. Additional supporting functions (e.g., interrupt, global real-time, and watchdog services) are provided to enhance the functional range of the NoC.

- **Extendability** To bridge the gap between resource efficiency and usability, the TTSoC architecture is designed to be extended by adding additional, special purpose functions. Such functions widen the functional range of specific cores according to application demands, with the disadvantage of increased resource usage.

- **Diagnosis & Maintainability** Embedded systems are, by nature, built into larger technical systems (e.g., cars), which impose various difficulties concerning maintenance. Hence, the possibility to easily diagnose failures and to "repair" a system by simply exchanging a failed component like a whole TTSoC with a new one, is a crucial requirement.

- **Bandwidth** The NoC has to provide enough communication bandwidth to allow unhindered operation of all attached cores. Since the required bandwidth is highly application dependent, no minimum bandwidth is specified. Although intentions are to maximize the available bandwidth, the speed of the NoC (e.g., on-chip clock frequency) is not a driving design factor, the other design requirements are prioritized.

### 3.2 Overview

The Time-Triggered System-on-a-Chip (TTSoC) architecture is developed to house multiple different cores, each consisting of a host processors with peripheral devices (i. e., local I/O controllers like Controller Area Network (CAN) controllers), a Communication Network Interface (CNI) Layer, and a Trusted Interface Subsystem (TISS) on the same microchip and to connect them through a dependable, time-triggered communication system, the Network-on-a-Chip (NoC). The hosts have no other possibility to influence one another but the NoC, guaranteeing encapsulation of different DASs. The TTSoC architecture is designed for safety critical applications, thus some components of the NoC are part of a "trusted region" within the TTSoC architecture. These components have to be certified to the highest criticality level required by any core of a TTSoC, because failures of those core components would cause failures of the entire TTSoC.

The design of the TTSoC architecture and of its components was motivated by [OPHS06] and some early specifications and concepts were introduced in [Obe06] and [KHO<sup>+</sup>06], some of which are used in the implementation described in this thesis.

Figure 3.1 shows an overview of the Time-Triggered System-on-a-Chip architecture.

Figure 3.1: Overview of the TTSoC architecture

A host processor reads and writes all communication data as well as additional status and configuration data, by means of a memory mapped interface provided by the attached Communication Network Interface (CNI) Layer. Since the NoC is a shared resource, a Trusted Interface Subsystem (TISS) is used to connect the CNI Layer to the underlying NoC Interconnect to protect the communication medium from a host violating its temporal specification. A single TISS consists of the Medium Access Control (MAC) Layer, responsible for protecting the communication medium and initiating data transfers according to the communication schedule, and the Logical Link Control (LLC) Layer, which handles all host related communication issues (e.g., presenting the communication data in a convenient way, synchronization, etc.). A host and its attached CNI Layer and TISS is called a core of the TTSoC.

Two special cores which are part of the NoC can be identified: The Trusted Network Authority (TNA) and the Resource Management Authority (RMA).

The RMA, a standard core, manages the available resources of the TTSoC, especially by building a conflict-free communication schedule, while the TNA, as part of the trusted region of the TTSoC, acts as kind of a guard for the NoC. The TNA core uses a special host processor to verify the communication schedule and the resource allocation plan submitted by the RMA and implements an additional configuration planning (CP) interface to forward the valid configuration to all other TISSs.

The host processors can be standard commercial microprocessors, dedicated Intellectual Property (IP) modules, gateways to other communication networks like Time-Triggered Ethernet [SK06] or TTP/C [TTTa], or any custom built hardware module.

The following sections describe some of the crucial concepts associated with the TTSoC architecture development (section 3.3), the general operation of the TTSoC (section 3.4), and the components that form the NoC (section 3.5).

### 3.3 Concepts

#### 3.3.1 Time

The TTSoC architecture provides a synchronized global real-time service for all cores connected to the NoC. The global real-time is not only used to establish the time-triggered communication but can also be accessed by the cores to support real-time operation of installed application software (e.g., job scheduling, etc.).

The time format used by the TTSoC architecture is derived from the Time-Triggered Ethernet time format [Ste06, p. 50] and closely related to the Global Positioning System (GPS) time format. The binary TTSoC architecture time format is 8 bytes (64 bit) wide and is based on the physical second. It inherits the epoch of the GPS (January 6, 1980 at 00:00), unless no external synchronization is possible. In that case, the epoch starts with the system startup instant.

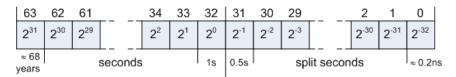

Figure 3.2: TTSoC Architecture Time Format

The 8 bytes of the TTSoC architecture time format (figure 3.2) can be splitted into two four byte segments: the higher 32 bit represent the elapsed number of seconds since the start of the epoch while the lower 32 bit denote the fractions of a second in negative powers of two (i. e., 0.5s, 0.25s, 0.125s, etc.). Thus a time horizon of  $2^{32}$  seconds (i. e., approximately 136 years) and a granularity of  $2^{-32}$  seconds (i. e., approximately 0.2 ns) is established, providing the possibility to uniquely represent every time instant since January 6, 1980 with a precision of under a nanosecond. The small granularity became necessary because a granularity of  $2^{-24}$  seconds (i. e., approximately 60 ns), as introduced by the Time-Triggered Ethernet time format, would restrict the time-triggered Network-on-a-Chip to an on-chip clock frequency of about 16 MHz. Instead of widening the time format to more than 8 bytes, it was decided to reduce the time horizon to support the needed granularity. Table 3.1 compares the Time-Triggered Ethernet and the TTSoC architecture time format with respect to their main characteristics.

|                   | TT Ethernet           | TTSoC              |  |

|-------------------|-----------------------|--------------------|--|

| Overall Size      | 8 bytes               |                    |  |

| $\geq < 1$ second | 5/3 bytes             | 4/4 bytes          |  |

| Epoch             | January 6, 1980, 00:0 | 0 / system startup |  |

| Horizon           | approx. 30 000 years  | approx. 136 years  |  |

| Granularity       | approx. 60 ns         | approx. 0.2 ns     |  |

Table 3.1: Time Format Comparison: TT Ethernet vs. TTSoC

Due to implementation hardware restrictions<sup>1</sup>, the lowest six bits of the TTSoC architecture time format are set to zero throughout the TTSoC implementation described in this thesis, reducing the resource effort for the internal time representation from 64 to 58 bits. External time representation (i. e., the global real-time accessible by the hosts) is not affected. A detailed description of the implemented time format can be found in [Eng07].

#### 3.3.2 Messages

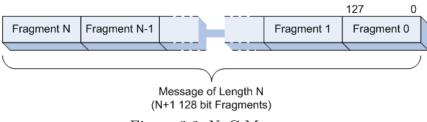

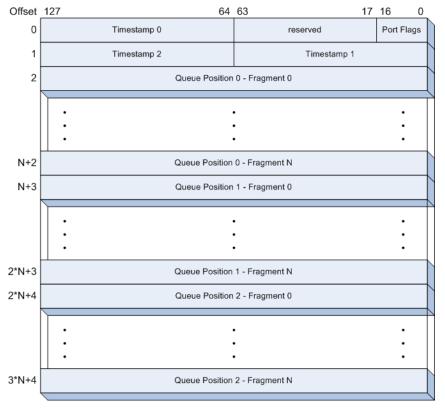

Communication among the cores in the time-triggered NoC is organized in periodic messages. The messages consist of a constant number of fragments which transport 128 bit data each (figure 3.3).<sup>2</sup> The message size ranges from

$<sup>^1{\</sup>rm The}$  granularity of the TTSoC architecture time form at of 0.2 ns would require an on-chip clock frequency of at least 5 GHz to be accurate.

$<sup>^{2}</sup>$ Unless mentioned otherwise, a "fragment", as used in this document, refers to a 128 bit wide part of a message.

0 (1 fragment) to 255 (256 fragments) and is set by the TNA taking the host requests (see section 3.5.5) into account. Message transport is performed by means of periodic Pulsed Data Streams (3.3.3) scheduled by the TNA. Sources and sinks of messages are represented by ports (section 3.3.4) at the sending core and the receiving core(s), the transmission is initiated by the MAC Layer according to the schedule.

Figure 3.3: NoC Message

Three types of messages are supported by the NoC:

- **State Messages** are the intended main communication form of the TTSoC architecture. State Messages contain state information, therefore they are suited best for transportation over a time-triggered network. Because of the at-least-once semantics required by state information, the state information at the receiving core can be updated in place without forcing the receiving core to consume the previous message in advance. A state message is transmitted periodically regardless of any change of the contained state information. An update of this information by the sending core's host is automatically transmitted to the receiving core's host with a maximum (worst-case) delay of one message period duration<sup>3</sup>.

- **Event Messages** are sent after the occurrence of an event. Since the NoC incorporates a time-triggered communication service, these messages have to be scheduled like any other message to reserve the needed amount of bandwidth. Actual sending of event messages can be suppressed until an event occurred, but queues are needed at the sending and receiving event message ports to ensure the required exactly-once sematics. This mechanism helps to save power since no sending and receiving operations have to be performed until there is actual data to be transmitted, and guarantees delivery of event information even under peak-load scenarios, as long as the periods of the event messages in the predefined message

$<sup>^{3}</sup>$ Disregarding the constant sending and receiving operation latencies for every fragment.

schedule are shorter than the minimum time interval between the associated events. A higher event occurrence frequency can be tolerated for a short amount of time, as long as the sender and receiver queues are large enough to store all generated event messages until they can be transmitted over the NoC or consumed by the receiving host. In addition, a longer event occurrence pause is required from time to time to allow the NoC to empty the send queue again.

Streaming Messages are used to transport streaming data (e.g., an audio stream). In contrast to state or event messages, streaming messages are not used to describe the state or the change of state of an entity, but to transport big amounts of information (i. e., a serialized data stream) in a convenient way. Because of the nature of streaming data which requires a constant feed of input by the sender and immediate processing at the receiver, the communicating hosts are forced to update (sender) or read (receiver) the associated Streaming Port before / after the transmission of every single fragment, respectively.

Due to the bus topology of the core interconnection used by the TTSoC implementation described in this document, all messages are broadcasted to all cores. Point-to-point or multicast communication is incorporated transparently by the different medium access schedules of the cores, which allow only the designated receiving cores to read data from the bus while a certain message is presented by a sending core. Future implementations may support true point-to-point communication by using a switched network or other forms of core interconnection. See sections 3.5.3 and 6 for details on the current TTSoC interconnection and possible future improvements.

#### 3.3.3 Pulsed Data Streams

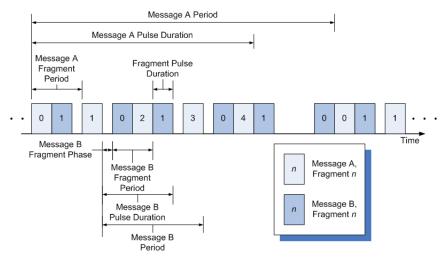

The concept of pulsed data streams was proposed in [Kop06]. The basic requirements for pulsed data streams are an a priori known set of communication participants, a synchronized global notion of time, and a cyclic communication schedule. A pulsed data stream is a cyclic data stream that transports data uni-directionally in pulses from one sender to n a priori identified receivers at a specified phase of the cycle for a specified duration. [Kop06, p. 4].

In the TTSoC architecture, the cyclic communication schedule is established by the TNA among the cores of the NoC. All messages distributed over the NoC are periodic and the cores are aware of a common global real-time, hence the pulsed data stream concept can easily be applied.

Furthermore, since all TTSoC architecture messages consist of fragments, the NoC implements a special pulsed data stream version. In addition to its sender

and receiver identification, each message can be described by its period (i. e., the cycle duration), the message pulse start instant (i. e., the phase offset), and the message pulse duration. To prevent blocking of the communication medium caused by long messages, each message pulse is subdivided into single fragment pulses. The fragment pulses are characterized by the fragment period and the fragment pulse start instant inside a message pulse, the fragment pulse duration is constant due to the constant transmission delay of the fixed length fragments. Figure 3.4 shows the pulsed data streams used for message transmission in the NoC.

Figure 3.4: NoC Pulsed Data Streams

The advantage of this implementation is that the fragments of different messages (with possibly different periods) can be interleaved on the communication medium. Otherwise two messages, one message with a long pulse duration and another message with a message period shorter than the first message's pulse duration could not be scheduled, either the long message would never gain possession of the communication medium or the short-period message would miss its reception deadlines.

The message schedule provided by the TNA aims to fulfill all message requests without violating any message periods or deadlines. If no valid schedule can be found, non safety-critical messages are declined to ensure proper transmission of the safety-critical data among a priori specified high-reliability DASs.

#### 3.3.4 Ports

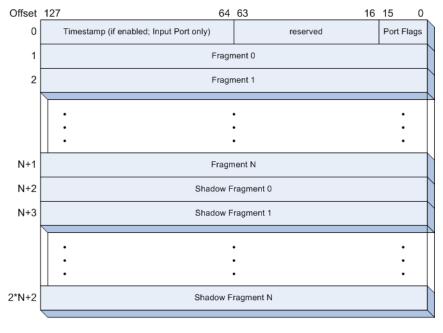

The NoC ports form the end points (one source and one or more sinks) of the communication line between different cores. They were designed to store variable size messages (fragment granularity) ready to be sent at the next message period (output ports), or previously received messages waiting to be processed by a host processor (input ports).

Every port can be identified locally (inside a core) by its unique PortID which is set and associated with a specific message by the TNA. Every message needs a single output port in its sending core (the source of the message) and one input port at every receiving core (the sink(s)).

Three input and output port types matching the three message types described in section 3.3.2 are featured by the TTSoC architecture.<sup>4</sup> All port types provide a different kind of synchronization mechanism to prevent data corruption due to simultaneous read and/or write accesses. Further details of the implemented port types can be found in section 4.2.2.2.1.

- **State Ports** store a whole state message. While input State Ports use an adapted form of the non-blocking write (NBW) protocol [KR93] to ensure proper reception of all state messages, output State Ports are designed to store a second instance of the state message to be sent in a so called "shadow register". Using this mechanism, the host software is allowed to write the next state message to the "shadow register" while transmission of the current state message, stored in the "standard register", is still in progress, or vice versa.<sup>5</sup>

- **Event Ports** provide variable length queues to store a sequence of complete event messages. Input and output Event Ports use the same synchronization mechanism, namely two counters which hold the current read and write positions in the event message queue. The host acts as the *writer* (output) or the *reader* (input) of a certain Event Port, the TISS performs the respective other role. Receiving or sending an event message and simultaneously writing or reading another one to or from the same Event Port is possible at all times, on condition that the queue is not full or empty, respectively.

<sup>&</sup>lt;sup>4</sup>The NoC has no possibility to determine if the message type matches the configured port types of the associated input and output ports. Unless an application is intentionally designed to handle a certain type of messages by using a port of a different type (e.g., a diagnostic entity logging all kinds of message transfers by means of input Streaming Ports), it is strongly recommended to align the port types in the port configuration with the message schedule to prevent system errors due to misinterpreted data.

<sup>&</sup>lt;sup>5</sup>The "standard" and "shadow registers" are no actual registers but consecutive memory areas in the CNI memory.

**Streaming Ports** do not store whole messages but only a single fragment of a streaming message. To maintain a continuous data stream between two cores, the sending host has to update the fragment data before every fragment send instant and the receiving host has to fetch this data before the next fragment arrives over the NoC, otherwise a fragment is sent more frequently than once (sender) or a fragment is overwritten by the following one (receiver). Streaming Port access synchronization is performed with the same mechanisms that State Ports use, synchronization of the data stream (e.g., start, stop, pause, etc.) has to be maintained by the application itself (e.g., by using additional event messages).

### 3.4 Operation

Sending and receiving of messages in the TTSoC architecture is triggered by the progression of time. Every message is associated with a time period and a phase offset at which transmission of this message has to start. Since a message consists of fragments, every message is additionally characterized by a fragment period and a fragment phase offset. These periods and phase offsets are stored in the message schedule of every TISS, allowing the MAC Layer to determine the exact send or receive instant for every fragment.

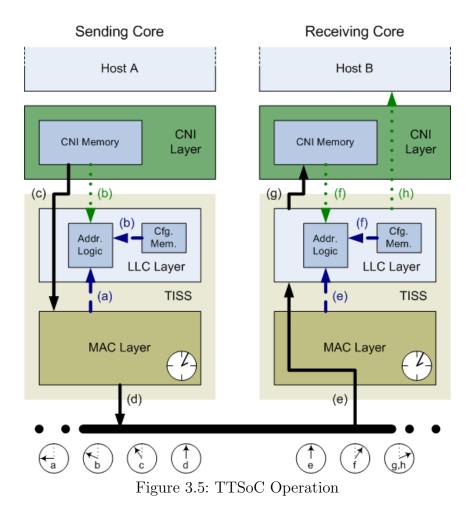

Figure 3.5 shows the transmission of a message from one core to another, the following paragraphs describe this operation in detail.

The MAC Layer requests the data to be sent from the LLC Layer prior to the calculated send instant by driving the PortID and the fragment number of the fragment to be sent on the appropriate lines (a).

The LLC Layer calculates the address of the requested fragment in the CNI memory using the port configuration data written by the host and the current state of the port synchronization information (b). After that, it fetches the fragment from the port stored in the CNI Layer and forwards the data to the MAC Layer (c).

The MAC Layer sends the fragment over the network precisely at the send instant determined by the message schedule (d).

At the receiving core, the message schedule noted the same time instant as receive instant, so the receiving core's MAC Layer stores the fragment data presented on the network and forwards it to the local LLC Layer together with the local PortID and the fragment number (e).

The LLC Layer calculates the local CNI memory address based on the information obtained from the port configuration memory and the synchronization

flags (f) and finally stores the fragment in the port in the CNI Layer (g).

After completing the reception or sending of a whole message, a "New Message" or "Ready" interrupt can be generated to inform the host that the receiving port contains valid data or the sending port is ready for the next message to be written by the host, respectively (h).

#### 3.4.1 Configuration

The message schedule is generated by the RMA according to message requests sent by the hosts, and verified and distributed to the TISSs by the TNA. A reduced message set can be scheduled due to short resources, a failure, or after system startup.

The layout of the message request mechanism is application specific, but the

intended standard configuration operation between the RMA, TNA, and the TISSs is shown in figure 3.6 and described below.

Figure 3.6: TTSoC Message Configuration Procedure

After system startup, an a priori defined, fixed message schedule is active, allowing the cores to request their needed messages by sending message request messages to the RMA (a). Depending on the application requirements, additional diagnostic messages and/or messages used by services that have to start operation immediately after startup can be scheduled too.

The RMA tries to build a feasible message schedule including all requested messages (b) and transfers its solutions to the TNA (c).

The TNA verifies the validity of the received message schedule (d) and, if it is confirmed, sends the according core-local message schedules in combination with a common reconfiguration time period and phase offset to the TISSs (e). When the next reconfiguration time instant is reached, all cores switch to the new configuration simultaneously and normal network operation commences.

Reconfiguration of the TTSoC is a periodic process. If no new messages (and no termination of active messages) are requested by the cores, the previous configuration is kept. A change of the current message schedule can become necessary due to changed application service requirements (e.g., a user requested an additional service by turning a switch) or a core failure that has to be compensated. A change of the message schedule is possible at every periodic reconfiguration instant.

For safety-critical applications, it can be useful to define a fixed backup message schedule during the system design process and store it in the TNA to

be activated in case of a possible RMA failure. Although all flexibility gained by the dynamic resource allocation process is lost in such a case, essential safety critical services can be kept active until a fail-safe state is reached or the occurred failure can be corrected by maintenance, by starting a backup system, or by other means.

The described configuration mechanism can be used to allocate system resources other than communication medium access in future TTSoC implementations, the current TNA implementation supports only message scheduling.

# 3.5 Components

# 3.5.1 Trusted Interface Subsystem

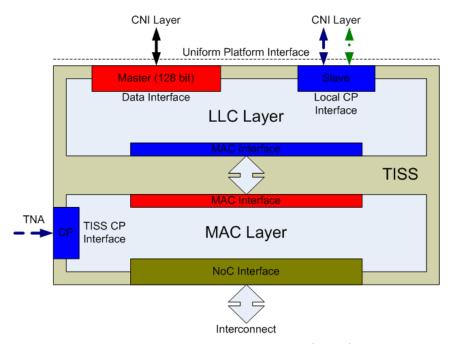

The Trusted Interface Subsystem (TISS) (figure 3.7) consists of two parts: the Medium Access Control (MAC) Layer (section 3.5.1.1) and the Logical Link Control (LLC) Layer (section 3.5.1.2).

Figure 3.7: Trusted Interface Subsystem (TISS) Overview

The purpose of the TISS is to send and receive messages to or from other cores according to the schedule determined by the TNA and fetch or store these messages from/to the CNI Layer. Since the TISS is responsible for communication medium access and provides the different types of ports and their synchronization mechanisms, the TISS is part of the trusted region of the TTSoC architecture. Therefore it is intended to be certified to the highest criticality level of any host within the TTSoC.

#### 3.5.1.1 MAC Layer

The MAC Layer, described in [Eng07], is responsible to protect the communication medium from undesired disturbance. It stores the message schedule determined by the TNA and uses it not only to restrict medium access, but to initiate sending and receiving operations performed by the LLC Layer.

The communication schedule is transferred directly from the TNA to the MAC Layer through the TISS configuration planning (CP) interface, the configuration data needed by the LLC Layer is forwarded upon reconfiguration. In addition, the MAC Layer keeps the global real-time accurate, which is continuously transferred to the LLC Layer through the MAC interface.

Although the host is able to read the MAC Layer configuration, there is no possibility of a host write access to the MAC Layer, hence any disturbance of the time-triggered communication by an erroneous host is avoided. Even the LLC Layer cannot influence the operation of the MAC Layer, thus the whole core is in the sphere of control of the MAC Layer, concerning communication medium access.

#### 3.5.1.2 LLC Layer

The LLC Layer allows a host processor to access the communication service presented by the NoC in a convenient way. While the MAC Layer regulates reception of single fragments at specific time instants and signals these events to the LLC Layer, the LLC Layer is responsible to assemble these fragments to form messages of configurable length, to store these messages in the designated ports of certain types, and to provide the necessary synchronization mechanisms to allow a consistent data transfer to the host. Transmission of fragments is handled similar: Before the occurrence of a send time instant, the MAC Layer requests the fragment to be sent from the LLC Layer which fetches it from the memory location determined by the port identification, fragment position, port configuration (base address, type), and current port synchronization status (e.g., queue positions).

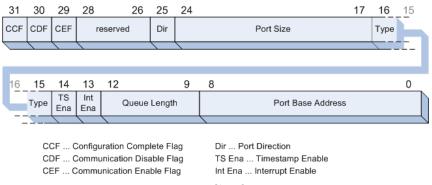

To maintain this highly flexible (concerning port size, port type, queue length, etc.) behavior, the provided ports can be configured by the host according to the application requirements. Apart from the communication service, the LLC Layer houses two additional trusted services: a watchdog service and an error status register to detect and monitor possible core failures.

The LLC Layer and the CNI Layer (section 3.5.2) were both implemented in the course of this thesis, chapter 4 offers a closer view on their operation and implementation.

# 3.5.2 CNI Layer

Memory space to store all port data and the related synchronization data is provided by the Communication Network Interface (CNI) Layer. It therefore acts as a temporal firewall [KO02] for the NoC. The CNI Layer works closely with the LLC Layer, concerning especially the timeliness of read and write accesses to the CNI memory.

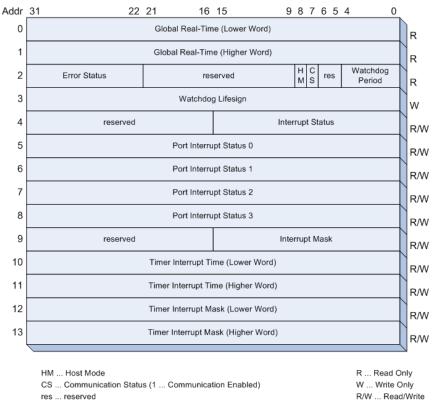

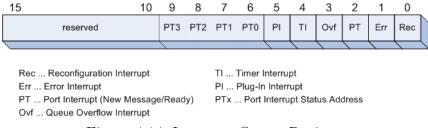

The standard CNI Layer implements a memory-mapped host interface to allow the host software to access the port data memory, the port configuration memory, the MAC Layer configuration memory, possible CNI Layer extensions, and the LLC Layer and CNI Layer register files. Furthermore, an interrupt service is located in the CNI Layer, keeping track of any interrupt triggered by the TISS, the CNI Layer, or any Middleware Plug-In.

The CNI Layer was designed to allow easy modification to suit application needs, either by adding CNI Layer extensions (described in the following paragraph) or by replacing the whole standard CNI Layer with a host-specific implementation, therefore the CNI Layer is located outside of the trusted region of the TTSoC architecture. Certification of the CNI Layer is though possible, if required by the application due to a host or a CNI Layer extension of high criticality.

The CNI Layer is the subject of chapter 4, together with the LLC Layer.

#### 3.5.2.1 CNI Layer Extensions

During the development of the TTSoC architecture, possibilities to further improve the functional range of the NoC were evaluated. To keep possible certification procedures simple and to support the independent development of additional functions, it was decided to enhance the CNI Layer using optional CNI Layer extensions. Different kinds of CNI Layer extensions were discussed, some of which were implemented later.

Chapter 5 deals with the possible forms of CNI Layer extensions.

# 3.5.3 Interconnect

The Network-on-a-Chip Interconnect has to perform three main tasks, all of which are critical for TTSoC operation:

- Distribution of periodic and sporadic messages between the cores of the NoC

- Maintaining a consistent time base among the NoC cores

- Transporting the message schedule and additional configuration parameters from the TNA to the TISS configuration planning interfaces

To guarantee operation in a safety-critical environment, the NoC Interconnect has to be certified to the highest criticality level demanded by the respective application.

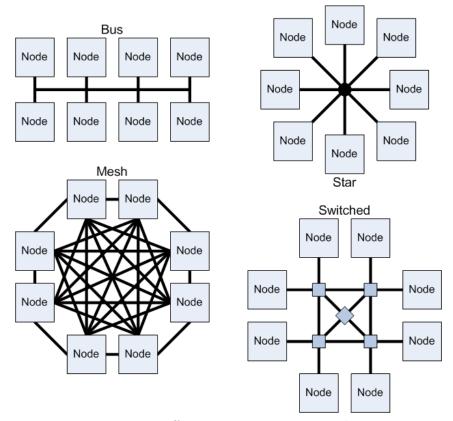

The message distribution service can be implemented using different network architecures, e.g., bus, star, mesh, or switched topology (figure 3.8). In addition, the Interconnect can be replicated to increase transmission bandwidth or network safety by using a second communication channel.

The chip-wide global real-time is accessible by all the TISSs in the NoC and has to be kept consistent among all cores without jitter and with minimal clock skew.

The configuration planning Interconnect can be slow, compared to the message distribution service, since configuration intervals are relatively large, compared to fragment sending periods. The need for the additional configuration planning Interconnect arises due to the requirement to guarantee that only the TNA can write the TISS message schedule and low-level configuration information (i. e., host mode, watchdog period).

The current TTSoC implementation uses a 128 bit wide bus network for message transportation, a simple memory interface for configuration planning purposes and a centralized time distribution system. Details can be found in [Eng07].

# 3.5.4 Resource Management Authority

The Resource Management Authority (RMA), although part of the TTSoC architecture, is implemented as a dedicated standard core. Since performing dynamic management of all available TTSoC resources (e.g., communication, computational, power resources) is a fairly complex task and can be highly application specific, the RMA is not assumed to be free of design faults and therefore is not certified.

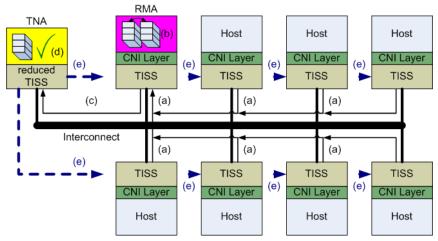

Figure 3.8: Different Interconnect Topologies

The RMA receives message (and/or resource) requests from the cores of the NoC, containing, among other things, the requested message length and message period. It tries to fulfill all message requests by composing a conflict-free schedule for fragment sending and receiving time slots across the NoC. In addition, host mode configurations for all cores have to be evaluated according to the current needs of the application and the available computational resources. The RMA tries to prepare a feasible message schedule and resource allocation plan in a predefined amount of time and transfers these plans to the TNA by means of the standard communication service. In the TNA the message schedule and the resource allocation plan are verified and, if necessary, altered to guarantee unhampered safety-critical operation.

By introducing this two-stage configuration mechanism (the RMA builds a provisional NoC configuration, the TNA verifies this configuration according to safety-critical requirements), the application system designers gain the freedom to implement arbitrary scheduling algorithms best suited for a specific application while the TTSoC architecture ensures validity and dependability of the determined configuration under all circumstances.

### 3.5.5 Trusted Network Authority

The Trusted Network Authority (TNA) is responsible for verifying and distributing a valid message schedule and resource allocation plan for the whole TTSoC. Therefore, the TNA protects all safety-critical resources of the TTSoC. The complexity of the TNA is kept as low as possible to avoid design and operational faults and to ease certification, the TNA is considered to be part of the trusted region of the TTSoC architecture.

After receiving the proposed message schedule and resource allocation plan from the RMA, the TNA verifies them. Should the message schedule or the resource allocation plan be invalid, for instance due to an erroneous RMA or a change in the availability of certain resources, the TNA alters the plan to ensure that certain application specific safety-critical DASs are able to maintain their operation while non-critical application services can be deteriorated. During the application system design process, designers should ensure that this situation is a rare event, only caused by core failures or due to rare peak-load scenarios.