Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# MASTERARBEIT

# picoJava-II in an FPGA

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Diplom - Ingenieurs

am

Institut für Technische Informatik 182/1

$\operatorname{der}$

Technischen Universität Wien

unter der Leitung von

o. Univ. - Prof. Dipl. - Ing. Dr. Herbert Grünbacher

und

Univ. Ass. Dipl. - Ing. Dr. Martin Schöberl

als verantwortlich mitwirkendem Assistenten

durch

Wolfgang Puffitsch Matr. - Nr. 0125944 Aspanger Straße 17, A–2822 Bad Erlach

Wien, im 23. November 2007

.....

# picoJava-II in an FPGA

The picoJava-II processor is Sun MicroSystems' Java processor and thus a popular reference design for other Java processors. While a number of new designs are targeted at FPGAs, the picoJava-II processor was designed for ASICs – as there is no implementation in an FPGA known, the validity of direct comparisons is limited. Moreover, no performance figures are known from ASIC implementations, which means that comparisons in this area could rely on estimations only. The goal of this diploma thesis is the implementation of the picoJava-II processor in an FPGA and the creation of the necessary environment for conducting benchmarks.

In this thesis, an overview about various Java processors is presented; picoJava-II's architecture is covered in detail. The design of the hardware modules that need to be implemented is described as well as the diverse software components. picoJava-II is compared to other Java processors with respect to resource usage and clock frequency. Furthermore the results of the benchmarks are used to evaluate the processor's performance.

# picoJava-II in einem FPGA

Der picoJava-II Prozessor ist ein von Sun Microsystems entwickelter Java-Prozessor und daher ein beliebtes Referenzdesign für andere Java-Prozessoren. Während viele neue Designs jedoch in FPGAs laufen, wurde der picoJava-II Prozessor für ASICs entwickelt - da keine Realisierung in einem FPGA bekannt ist, ist die Aussagekraft von direkten Vergleichen begrenzt. Da darüberhinaus auch keine Ergebnisse bezüglich der Performance von ASIC-Implementierungen bekannt sind, konnten sich Vergleiche auf diesem Gebiet nur auf Abschätzungen stützen. Das Ziel dieser Diplomarbeit ist die Implementierung des picoJava-II Prozessors in einem FPGA und die Schaffung der notwendigen Umgebung für die Durchführung von Benchmarks.

In dieser Arbeit werden überblicksmäßig verschiedene Java-Prozessoren präsentiert; die Architektur von picoJava-II wird detailliert dargestellt. Das Design der für die Realisierung notwendigen Hardware-Module wird beschrieben, wie auch die verschiedenen Software-Komponenten. picoJava-II wird mit anderen Java Prozessoren bezüglich Resourcenverbrauch und Taktfrequenz verglichen. Weiters werden die Ergebnisse dieser Benchmarks dafür verwendet, die Performance des Prozessors zu bewerten.

# Danksagung

Besonderer Dank geht an meine Familie, die mich in allen Belangen bei meinem Studium unterstützt hat.

Ich möchte auch meinem Betreuer, Dipl. - Ing. Dr. techn. Martin Schöberl, für seine hilfreichen Ratschläge danken, die wesentlich zum Gelingen dieser Arbeit beigetragen haben.

# Contents

| 1 | $\mathbf{Intr}$ | oduction                 | 1 |

|---|-----------------|--------------------------|---|

|   | 1.1             | Structure of This Work   | 1 |

|   | 1.2             | Motivation               | 2 |

|   | 1.3             | The Java Virtual Machine | 2 |

|   | 1.4             | FPGAs                    | 3 |

| 2 | Rela            | ated work                | 5 |

| _ | 2.1             |                          | 6 |

|   |                 |                          | 6 |

|   |                 | 1                        | 6 |

|   |                 |                          | 7 |

|   |                 | 5 1                      | 7 |

|   | 2.2             |                          | 8 |

|   |                 | 0                        | 8 |

|   |                 | 0                        | 8 |

|   |                 |                          | 8 |

|   |                 |                          | 9 |

|   |                 |                          | 9 |

|   |                 |                          | 9 |

|   |                 |                          | 0 |

|   |                 |                          | 0 |

|   |                 | •                        | 1 |

|   |                 |                          |   |

| 3 |                 | 1                        | 3 |

|   | 3.1             | 1                        | 3 |

|   | 3.2             | 1                        | 5 |

|   | 3.3             |                          | 5 |

|   | 3.4             |                          | 7 |

|   | 3.5             |                          | 7 |

|   | 3.6             |                          | 9 |

|   | 3.7             | 1                        | 0 |

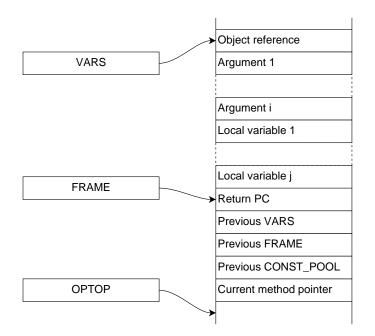

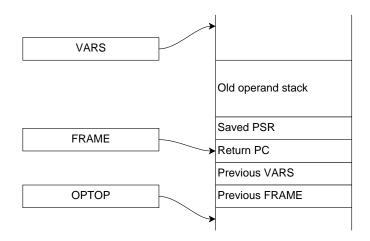

|   | 3.8             | Method and Trap Frames 2 | 1 |

|                           | 3.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Quick Bytecodes                                                                                  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

|                           | 3.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Memory Layout                                                                                    |  |

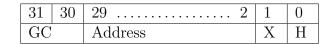

|                           | 3.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Garbage Collection                                                                               |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                  |  |

| 4                         | The diverse the promotion of the second seco |                                                                                                  |  |

|                           | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Design Environment                                                                               |  |

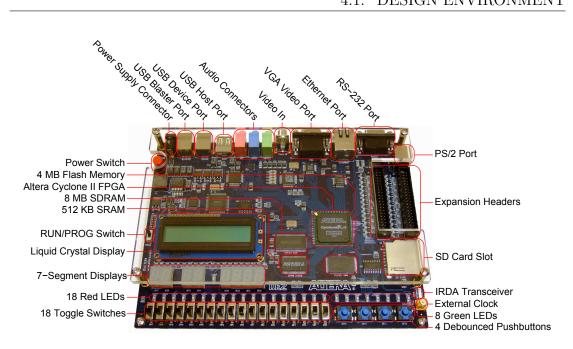

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1.1 The DE2 Board                                                                              |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1.2 Quartus-II                                                                                 |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1.3 ModelSim $\ldots \ldots 32$ |  |

|                           | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Megacells                                                                                        |  |

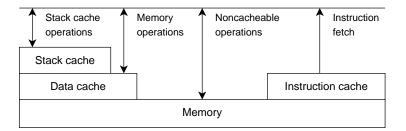

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.1 Stack Cache                                                                                |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.2 Cache Memories                                                                             |  |

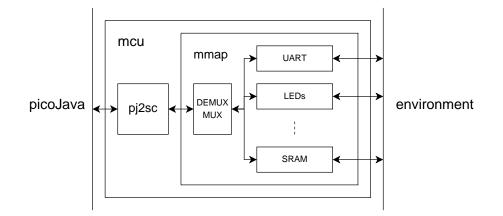

|                           | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Memory and I/O                                                                                   |  |

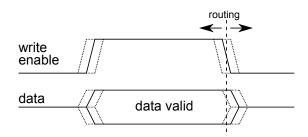

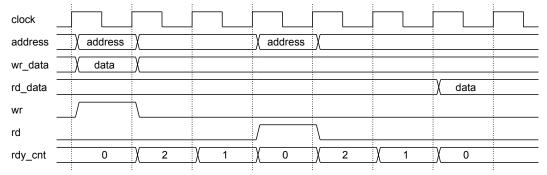

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.1 SimpCon                                                                                    |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.2 picoJava-II's Memory Interface                                                             |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.3 Translating Transactions                                                                   |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.4 XML Schema                                                                                 |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.5 Modules                                                                                    |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                  |  |

| 5 Software Implementation |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                  |  |

|                           | 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Provided Software                                                                                |  |

|                           | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Loader                                                                                           |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.1 Bytecode Engineering Library                                                               |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.2 Passes                                                                                     |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.3 Layout of the Memory Image                                                                 |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.4 Code Transformations                                                                       |  |

|                           | 5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Traps                                                                                            |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3.1 Memory Allocation                                                                          |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3.2 Description of Individual Traps                                                            |  |

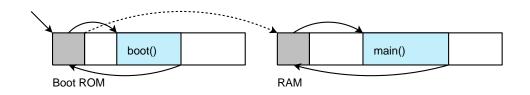

|                           | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Boot Process                                                                                     |  |

|                           | 0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.4.1 Boot Slot/Trampoline                                                                       |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4.2 Boot Loader                                                                                |  |

|                           | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Class Library                                                                                    |  |

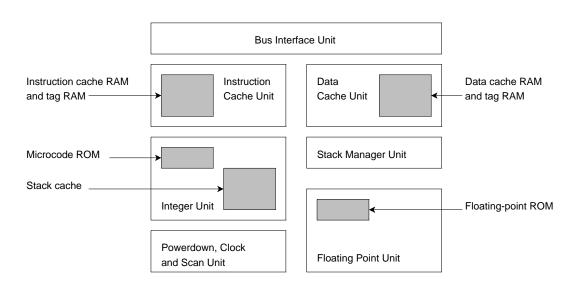

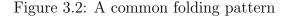

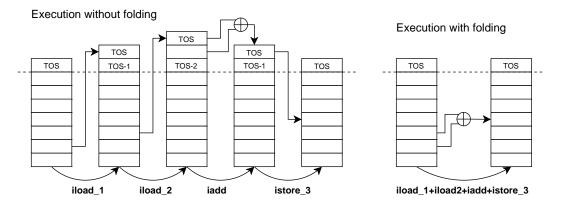

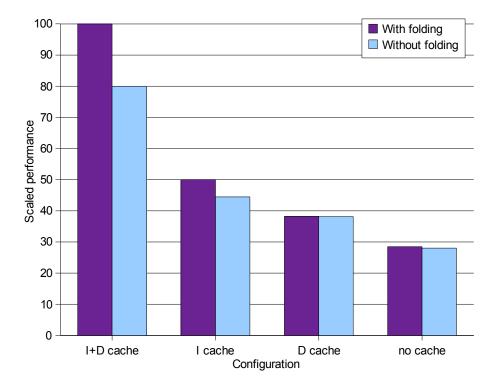

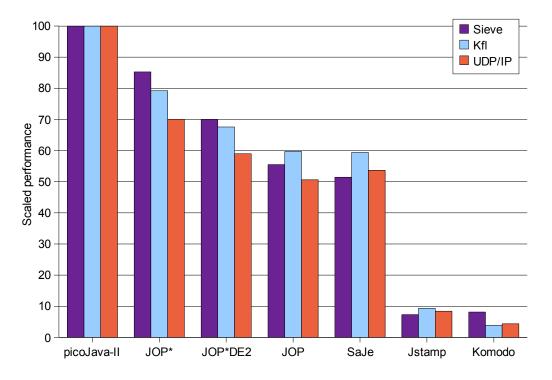

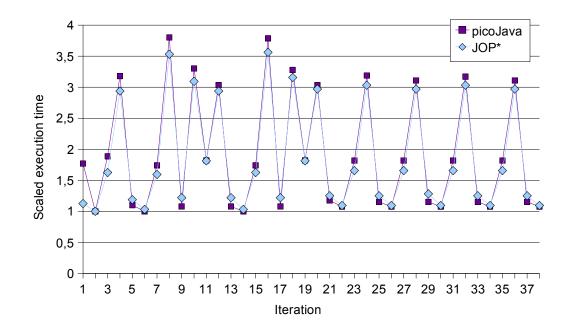

|                           | 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.5.1 Custom Classes                                                                             |  |