Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

Masterarbeit

# Porting the CACAO Virtual Machine to POWERPC64 and Coldfire

ausgeführt am

Institut für Computersprachen Arbeitsbereich für Programmiersprachen und Übersetzerbau der Technischen Universität Wien

unter der Anleitung von Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

durch Bakk. techn. Roland Richard Lezuo Burggasse 35/1 1070 Wien

Oktober 2007

#### Abstract

CACAO is a freely available just in time compiler for the Java language. In the course of this master thesis code generators for the POWERPC64 and Coldfire architectures were developed.

This work describes is the generic structure of a CACAO code generators and elaborates implementation details. Benchmarking results of POW-ERPC64 compared with CACAO on x86\_64 as well as SUN and IBM Java implementations will be presented.

Finally code simplification and future performance optimizations will be proposed by lessons learnt from this master thesis.

#### Kurzfassung

CACAO ist eine frei verfügbare virtuelle Maschine für Java welche auf einer just-in-time Compiler Architektur basiert. Im Zuge dieser Arbeit wurden Code Generatoren entwickelt die die Ausführung von Java Programmen auf POWERPC64 und Coldfire Prozessoren ermöglicht.

Es wird sowohl die generische Struktur eines CACAO Codegenerators beschrieben, als auch Details der Implementierungen die erstellt worden ist. Die Qualität der Arbeit wir aufgrund von Benchmarkergebnissen, in denen die POWERPC64 Architektur gegen IBM Java und CACAO auf x86\_64, sowie SUN Java verglichen wird überprüft.

Schliesslich werden die aus der Arbeit erkannten Vereinfachungen der Codebasis sowie künftige Schritte zur Optimierung der Effizienz zusammengefasst.

# Contents

| 1        | $\operatorname{Intr}$ | oduction 7                                                                                                                |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

|          | 1.1                   | The Java language                                                                                                         |

|          |                       | 1.1.1 The big picture $\ldots \ldots 7$             |

|          |                       | 1.1.2 Design goals $\ldots \ldots $ 8               |

|          | 1.2                   | Language features                                                                                                         |

|          | 1.3                   | Executing Java programs                                                                                                   |

|          | 1.4                   | CACAO architecture $\ldots \ldots 11$ |

|          |                       | 1.4.1 Overview                                                                                                            |

|          |                       | 1.4.2 Startup and shutdown $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 12$                                   |

|          |                       | 1.4.3 Linker $\ldots$ 13                                                                                                  |

|          |                       | 1.4.4 Method compilation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 15$                       |

|          | 1.5                   | Java byte code                                                                                                            |

| <b>2</b> | Rela                  | ated work 25                                                                                                              |

|          | 2.1                   | SUN HotSpot                                                                                                               |

|          | 2.2                   | IBM J9                                                                                                                    |

|          | 2.3                   | Jikes RVM                                                                                                                 |

|          | 2.4                   | Kaffe                                                                                                                     |

|          | 2.5                   | Parrot                                                                                                                    |

|          | 2.6                   | Mono                                                                                                                      |

|          | 2.7                   | Summary                                                                                                                   |

| 3        | Cod                   | e generators for CACAO 35                                                                                                 |

|          | 3.1                   | Symbols needed by CACAO                                                                                                   |

|          | 3.2                   | Register allocation                                                                                                       |

|          | 3.3                   | Code generation macros                                                                                                    |

|          | 3.4                   | Post compile time code patching                                                                                           |

|          | 3.5                   | Data segment                                                                                                              |

|          | 3.6                   | Runtime code patching - Patchers                                                                                          |

|          | 3.7                   | Exceptions $\ldots \ldots 43$                |

|          |                       |                                                                                                                           |

| 4        | PO           | WERPC64 code generator                          | 47       |

|----------|--------------|-------------------------------------------------|----------|

|          | 4.1          | The POWERPC64 architecture                      | 47       |

|          | 4.2          | Design decisions                                | 47       |

|          |              | 4.2.1 PPC64 ELF ABI                             | 47       |

|          |              | 4.2.2 PPC64 CACAO ABI                           | 48       |

|          |              | 4.2.3 Loading addresses                         | 48       |

|          |              | 4.2.4 Integer and long arithmetic               | 50       |

|          |              | 4.2.5 Float and double arithmetic               | 50       |

|          |              | 4.2.6 Exception handling                        | 50       |

|          | 4.3          | Porting PPC to PPC64                            | 51       |

|          | 4.4          | Implementation details                          | 52       |

|          | 4.5          | Current state and benchmark results             | 54       |

| <b>5</b> | Col          | dfire code generator                            | 63       |

| 0        | 5.1          | The Coldfire architecture                       | 63       |

|          | $5.1 \\ 5.2$ | The development environment                     | 63       |

|          | $5.2 \\ 5.3$ | Design decisions                                | 65       |

|          | 0.0          | 5.3.1 CACAO register usage                      | 65       |

|          |              | 5.3.2 M68K ABI                                  | 67       |

|          |              | 5.3.3 CACAO ABI                                 | 67       |

|          |              | 5.3.4 Dedicated pv register                     | 68       |

|          |              |                                                 | 69       |

|          |              | 0                                               | 69       |

|          |              | 5.3.6Exceptions5.3.7Native double return values | 09<br>70 |

|          | F 4          |                                                 | 70<br>70 |

|          | 5.4          | Implementation details                          | 70<br>72 |

|          | 5.5          | Current state and benchmark results             | (2       |

| 6        | Sun          | nmary                                           | 75       |

|          | 6.1          | Conclusion                                      | 75       |

|          | 6.2          | Future                                          | 75       |

|          | 6.3          | Source code                                     | 76       |

# List of Figures

| 1.1  | CACAO architecture overview                                                                                                                                | 11 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Method signature specifiers                                                                                                                                | 12 |

| 1.3  | A CACAO vtable                                                                                                                                             | 12 |

| 1.4  | Method compilation                                                                                                                                         | 16 |

| 1.5  | Stack changes                                                                                                                                              | 19 |

| 1.6  | Instruction type prefixes                                                                                                                                  | 19 |

| 2.1  | SUN HotSpot code generation                                                                                                                                | 25 |

| 2.2  | IBM J9 code generation                                                                                                                                     | 26 |

| 2.3  | Jikes RVM code generation                                                                                                                                  | 28 |

| 2.4  | Kaffe code generation                                                                                                                                      | 29 |

| 2.5  | Parrot code generation                                                                                                                                     | 31 |

| 2.6  | Mono code generation                                                                                                                                       | 33 |

| 3.1  | Data segment layout                                                                                                                                        | 41 |

| 3.2  | Patcher assembler output (old)                                                                                                                             | 42 |

| 3.3  | Patcher assembler output (new)                                                                                                                             | 43 |

| 3.4  | Number of exceptions in DaCapo                                                                                                                             | 45 |

| 3.5  | Stackframeinfo chaining with native invocation                                                                                                             | 45 |

| 4.1  | PPC64 function descriptor                                                                                                                                  | 48 |

| 4.2  | PPC64 CACAO ABI                                                                                                                                            | 49 |

| 4.3  | PPC64 patcher argument stack                                                                                                                               | 53 |

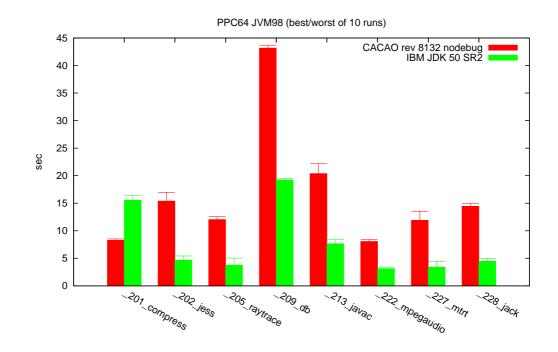

| 4.4  | JVM98 benchmark (lower is better)                                                                                                                          | 55 |

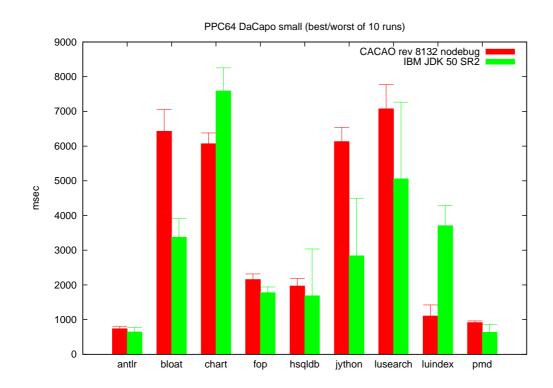

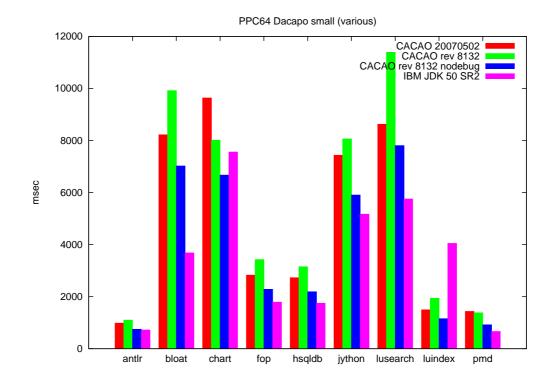

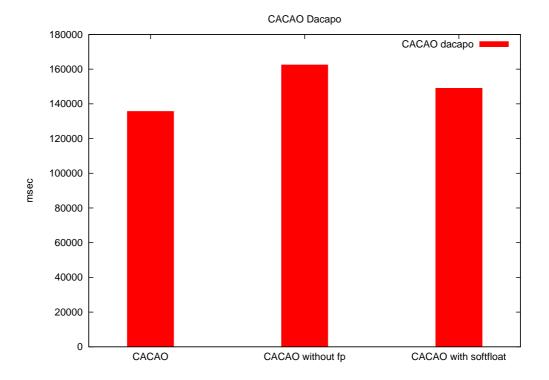

| 4.5  | DaCapo 2006-10-MR2 benchmark (small, lower is better)                                                                                                      | 56 |

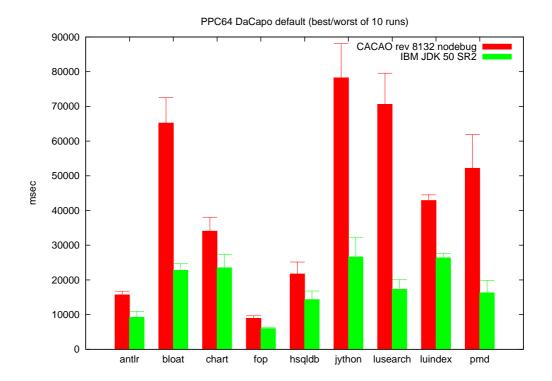

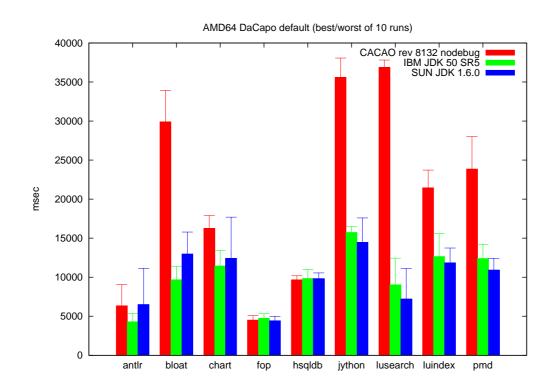

| 4.6  | DaCapo 2006-10-MR2 benchmark (default, lower is better)                                                                                                    | 57 |

| 4.7  | DaCapo 2006-10-MR2 benchmark (default, lower is better)                                                                                                    | 58 |

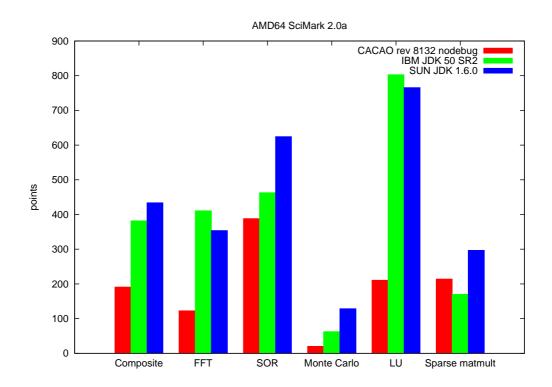

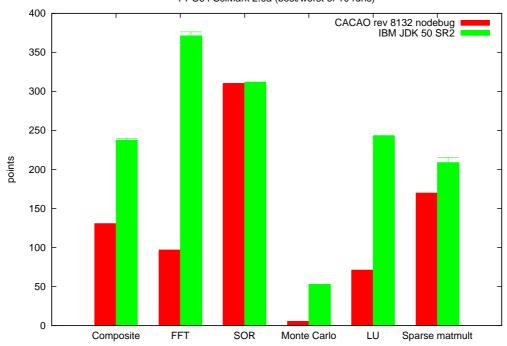

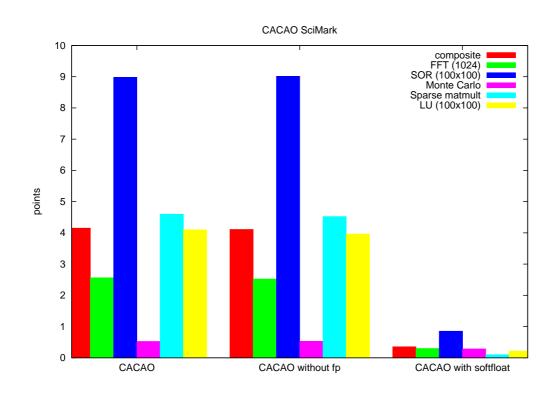

| 4.8  | SciMark 2.0a benchmark (higher is better)                                                                                                                  | 59 |

| 4.9  | SciMark 2.0a benchmark (higher is better)                                                                                                                  | 60 |

| 4.10 | DaCapo 2006-10-MR2 benchmark (small, various, lower is bet-                                                                                                |    |

|      | $\operatorname{ter}) \ldots \ldots$ | 61 |

| 5.1 | M68K stack layout                  | 67 |

|-----|------------------------------------|----|

| 5.2 | M68K CACAO ABI                     | 68 |

| 5.3 | M68K patcher argument stack        | 71 |

| 5.4 | DaCapo 2006-10-MR2 antlr benchmark | 73 |

| 5.5 | SciMark 2.0a benchmark             | 74 |

|     |                                    |    |

# Listings

| 1.1 | Java hello world                             | 8 |

|-----|----------------------------------------------|---|

| 1.2 | Java memory leak                             | 8 |

| 1.3 | Stack operations                             | 9 |

| 2.1 | Jikes RVM baseline add instruction           | 7 |

| 2.2 | Jikes RVM baseline assembler add instruction | 7 |

| 2.3 | Jikes RVM optimzing add instruction          | 7 |

| 2.4 | Kaffe intermediate example                   | 9 |

| 2.5 | Kaffe intermediate transformation            | 9 |

| 2.6 | Kaffe codegenerator definition example       | 0 |

| 2.7 | Parrot codegeneration example                | 1 |

| 2.8 | Parrot JIT definition                        | 1 |

| 2.9 | Mini generic instruction selection           | 2 |

| 3.1 | Codegeneration for iadd 3                    | 9 |

| 3.2 | Codegeneration macros                        | 0 |

| 4.1 | PowerPC64 load a 64bit address               | 9 |

| 4.2 | PPC64 exception triggering                   | 1 |

| 5.1 | Coldfire compiler bug testcase               | 4 |

| 5.2 | Coldfire compiler bug testrun                | 5 |

| 5.3 | Linux 2.6.10 sys_cacheflush patch 6          | 6 |

| 5.4 | M68K exception using trap 6                  | 9 |

| 5.5 | M68K exception by illegal memory access      | 0 |

LISTINGS

# Chapter 1

# Introduction

# 1.1 The Java language

#### 1.1.1 The big picture

The Java programming language was designed as a language for micro controllers around 1990[12]. One design goal was easy portability to new micro controllers which lead to a virtual machine (VM) based implementation of the language. The Java language has a syntax very similar to C++ but its design is more influenced by smalltalk. In Java every object is derived from java.lang.Object so there is exactly one class hierarchy. Additionally so called primitive types are used which are not part of the class hierarchy and therefore disturb the orthogonally of the language. The rationale for primitive types is performance as no runtime type checks are needed when operating with them.

Today the Java language is widely used, primary for server side applications but also for cross platform solutions and web applets. It is also used for teaching computer science students, for example at Vienna University of Technology although doing so is not uncritizised [8]. On http: //freshmeat.net 5267 out of 41.916 projects (as on 3.1.2007) are tagged as being implemented in the Java language. It has to be stated that these numbers are not representative as freshmeat.net mainly hosts UNIX software nonetheless it shows that Java has practical relevance.

The world famous "Hello world!" program in Java may look like listing 1.1. Although hello world programs tend to have little expressiveness describing features of a language they at least show the wordiness and Java is a very wordy language. This is not a bad thing as reading code tends to be easier when the language is more verbose, which is important for large scale projects with more than a handful of developers.

```

public class HelloWorld {

public static void main(String[] args) {

System.out.println("Hellouworld!");

}

}

```

Listing 1.1: Java hello world

Listing 1.2: Java memory leak

#### 1.1.2 Design goals

Java is a rather modern language and although compiled it has dynamic features as well. Java provides automatic garbage collection and does not provide pointer types. The rational behind this decisions was the believe that pointers are the main source of programming errors in C/C++. It is a common misbelief that Java eliminates memory leaks as a whole, it just eliminates some error classes where memory can leak. As counterexample for a Java program leaking memory see listing 1.2, which will be aborted by a java.lang.OutOfMemoryError exception. The problem with this program is the static Vector buffer which will always hold a valid reference to the Integer objects allocated in the loop. Therefore the garbage collector can not remove the objects and eventually all available memory will be used. In cases where static members are involved or objects with a very long lifespan the programmer has to take care that no resources are leaked.

A very interesting feature of the Java language is the security manager. The Java class library has hooks weaved in calling back java.lang.Security Manager before executing code which may harm the system. The security manager of a program can be provided by the user so he has fine grained controls even for untrusted programs. That this sandbox can not be left easily

8

is due to the virtual machine based implementation of the Java language which defines an interface to the host running the Java program. As any operations affecting the underlying system have to be passed through that interface it is possible to prevent possible harmful actions by blocking them at this defined border.

The Java platform is designed to be architecture neutral and portable. It therefore makes no assumption about host specific properties like machine word size or endianess. Instead a virtual machine interface is defined expected to be provided by the host. It is the responsibility of the virtual machine vendor to encapsulate hardware details in a way compatible with the expectations of a Java program executed. This includes word sizes, memory model and the semantics of built in functions or native interfaces. All programs written in the Java language can then be executed in a Java virtual machine (JVM) without any modification and are expected to behave identically.

It is stated that Java is high performance. This statement won't hold when comparing interpreted Java programs against native compiled binaries - an interpreter will always have some overhead [17, 11]. Nonetheless good performance of Java programs can be achieved by using just-in-time (JIT) compiler techniques, which may actually out perform native compiled code [23]. The majority of this paper will cover this topic. As a possibility to boost performance it is suggested to use the Java native interface (JNI)<sup>1</sup>. The JNI defines an interface to invoke native compiled code which may perform better than an implementation using Java. The main drawback of doing so is to loose the portability of the program.

Further the Java language supports threading at language level. This also lead to the class library being thread safe which eliminates a source of bugs with which for example C++ programmers are confronted when using standard template library (STL) containers in multi threaded applications.

Linking in Java happens dynamically. Classes are loaded and linked into the program when first accessed, not when the program is loaded. This is convenient when loading application via network as the initial start-up time is reduced.

# **1.2** Language features

Java offers so called primitive data types, types which are no objects. The integer types offered by the language are all signed, there is no unsigned data type available. The following integer types are offered:

<sup>&</sup>lt;sup>1</sup>http://java.sun.com/docs/books/jni/html/intro.html

- byte (8 bit)

- short (16 bit)

- int (32 bit)

- long (64 bit)

The character type char is a 16 bit unsigned integer type as Java uses  $Unicode^2$  as character encoding. Java also offers two floating point types, float (32 bit) and double (64 bit). Additionally a boolean type is offered which can be assigned the symbolic values true and false solely.

Objects are the main abstraction in Java programs. Objects can have members (primitive data types, other objects) and methods. Methods consist of statements and can operate on the members of an object. Java supports class inheritance with the limitation that a class can only inherit from one so called superclass. In addition so called interfaces are offered. An interface solely consists of method signatures and constants. A class implementing an interface has to provide an implementation for each interface method.

A more detailed introduction into the Java language is beyond the scope of this paper.

# **1.3** Executing Java programs

Java programs are compiled into so called class files by the Java compiler. The compilation process translates the textual representation of the program into an easier to parse intermediate form, called byte code. The byte code is not machine specific but operates on an abstract machine model. There are around 200 instructions, which a JVM executing the byte code has to implement. There are different approaches to implement a JVM. The earliest JVMs were interpreters, today just-in-time compilers are common. A just in time compiler creates machine code for the methods denoted as byte code and executes them directly on hardware. The name comes from the fact that the code is compiled directly before a method is executed. Most JVM implementations have an interpreter and compile only performance critical parts of the Java program.

<sup>10</sup>

<sup>&</sup>lt;sup>2</sup>http://www.unicode.org

## 1.4 CACAO architecture

#### 1.4.1 Overview

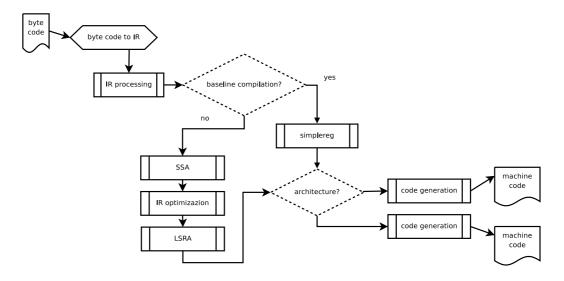

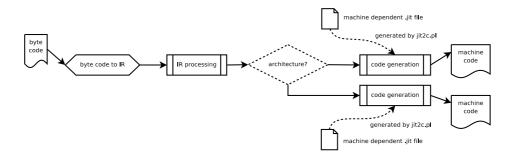

Figure 1.1: CACAO architecture overview

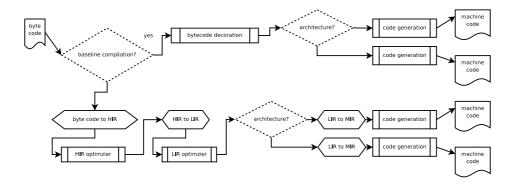

As described in [14], the CACAO system uses a compile only approach to execute bytecode. An interpreter has been added recently but a mixed mode where parts of the code are compiled and other parts are interpreted is not implemented. When initially loading a class no methods are compiled. This is done to save start-up time and due to the fact that many methods are never executed at all (when executing the DaCapo benchmark suite a total number of 86730 methods are loaded from class files but only 28240 are actually compiled. This is approximately 33%).

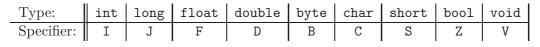

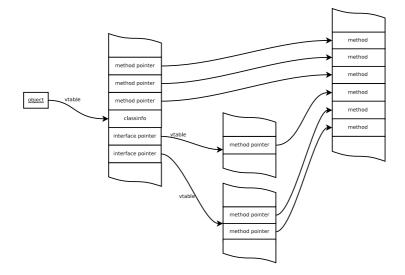

For each class loaded a so called vtable is created. A vtable contains pointers to the methods implemented by a class. Each object knows it's classes vtable and looks up the method entry point there on invocation. Interface methods need a second indirection to be looked up. Figure 1.3 shows the layout of a vtable. Method lookup tries to match the signature of the method to be called with a signature of a method referenced by the vtable. In Java not only the method name but also the types of the arguments define the signature. java.lang.System.exit(I)V is an example for a Java method signature. The letter I means that there is an integer argument V means a return value of type void. Figure 1.2 shows how to construct method signatures. Array types are denoted by prefixing the type with [ (there are not arrays of type void however).

Figure 1.2: Method signature specifiers

Figure 1.3: A CACAO vtable

Figure 1.1 gives an overview of the CACAO architecture. The byte code gets parsed and information is added. This results in an intermediate representation (IR) consisting of ICMD. For each method one of two possible compilers can be used. The baseline compiler is the simpler one and is used to quickly generate code. The optimizing compiler will only be used for performance critical methods. The compile time is increased, but much better code is generated. This pays back when the method is executed frequently[3]. It has to be noted that at the time of the writing only the baseline compiler is working. LSRA[24] and SSA[20] are currently implemented, recompilation framework is in place but still unused, this basically means that the current CACAO does not do any optimizations.

The vtable entries initially point to so called compiler stubs. The compiler stub when invoked determines the call site (from where it has been invoked), triggers compilation of the method which should have been called and updates the vtable accordingly (just-in-time compilation).

#### 1.4.2 Startup and shutdown

The startup happens in **src/vm/vm.c** and initializes all modules needed by the runtime environment. The Java program is started with a single call

to vm\_call\_method, which runs the main method of the given class. This method returns when the Java program main thread has terminated. When there are still active threads vm\_destroy waits for all of them terminating before the whole Java program is terminated. In case of program termination caused by an uncaught exception a global variable called exceptionptr points to this exception. A stacktrace is generated and the VM terminates with an error exit code by calling java.lang.System.exit(I)V. Last mentioned function is called with a success exit code when no exception has occurred.

#### 1.4.3 Linker

The linker is responsible for building the vtable of a class. It therefore has to load and link all interfaces a class implements as well as its superclass (recursively). When initializing the linker important classes are preloaded. The very first class to be loaded is java.lang.Class. Hardcoding classes to be loaded of course binds the VM somewhat to a class library layout and naming conventions. There are essential classes in a Java SE (Standard Edition) not found in a Java ME (Micro Edition). What follows is an incomplete list of classes the VM assumes to exist. They are used hardcoded from within the VM. Cacao supports GNU Classpath<sup>3</sup> (a free implementation of a Java class library), Sun CLDC<sup>4</sup> (a Java Micro Edition profile for mobile handsets), and recently support for Sun OpenJDK<sup>5</sup> class libraries - the open source version of the Java SE - has been added.

Some classes are only needed when using a specific class library implementation. Such classes are marked.

- java.lang.Object

- java.lang.Class

- java.lang.ClassLoader

- java.lang.Cloneable

- java.lang.SecurityManager

- java.lang.String

- java.lang.System

<sup>&</sup>lt;sup>3</sup>http://www.gnu.org/software/classpath/ <sup>4</sup>https://phoneme.dev.java.net/

<sup>&</sup>lt;sup>5</sup>http://openjdk.java.net/

- java.lang.Thread

- java.lang.ThreadGroup

- java.lang.VMSystem

- java.lang.VMThread

- java.io.Serializable

- java.lang.Throwable

- java.lang.Error

- java.lang.LinkageError

- java.lang.NoClassDefFoundError

- java.lang.OutOfMemoryError

- java.lang.VirtualMachineError

- java.lang.AbstractMethodError (Java SE)

- java.lang.NoSuchMethodError (Java SE)

- java.lang.VMThrowable (GNU Classpath)

- java.lang.Exception

- java.lang.ClassCastException

- java.lang.ClassNotFoundException

- java.lang.IllegalArgumentException

- java.lang.IllegalMonitorStateException

- java.lang.Void (Java SE)

- java.lang.Boolean

- java.lang.Byte

- java.lang.Character

- java.lang.Short

- java.lang.Integer

- java.lang.Long

- java.lang.Float

- java.lang.Double

- java.lang.NullPointerException

- java.lang.StackTraceElement (Java SE)

- java.lang.reflect.Constructor (Java SE)

- java.lang.reflect.Field (Java SE)

- java.lang.reflect.Method (Java SE)

- java.security.PrivilegedAction (Java SE)

- java.util.Vector (Java SE)

## 1.4.4 Method compilation

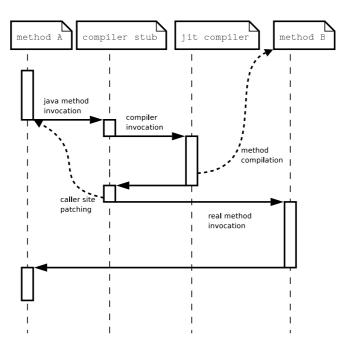

Whenever a not compiled method gets invoked the compiler stub ultimately invokes jit\_compile\_intern which controls the compilation (see figure 1.4). As a first step it is tested whether the method is native, in this case no code needs to be compiled, but a stub invoking the native function needs to be emitted. This stub code translates CACAO internal argument passing conventions to platform C ABI and calls the native function. When bytecode needs to be compiled the following phases are passed consecutively.

#### Parse

The basic blocks are determined. A basic block starts at an instruction which can be jumped to and ends at the first branching instruction or at the next basic block, whatever applies first. The stack usage of the method is simulated, and the Java byte code operands are translated into an internal representation. Complex instructions, like dup\_x2 are converted to a sequence of simpler instructions.

#### Stack analysis

For each basic block a symbolic evaluation of the code is performed, to check whether the stack underflows. At basic block boarders so called interface registers are used to merge control flow [13].

Figure 1.4: Method compilation

#### Control flow graph

Afterwards a control flow graph is built upon the basic blocks. The control flow graph is needed for the verifier. Code verification is mandatory for a Java virtual machine and specified in the JVM specification <sup>6</sup>. The verifier basically assures that all local variables references are valid, that parameters on the stack have correct types and no stack underflows occur.

#### Typecheck

As local variables are just index numbers in bytecode with no type information attached, they can be reused when their live ranges do not overlap. The verifier has to symbolically evaluate the code in more detail than needed for stack analysis.

#### Loop optimization

When enabled the compiler can try to optimize array bound checks in loops. The array bound check can be propagated outside the loop when the optimizer can prove that the index will stay in known borders and will therefore be only checked once [7].

$<sup>^{6}</sup> http://java.sun.com/docs/books/vmspec/2nd-edition/html/VMSpecTOC.doc.html$

#### 1.4. CACAO ARCHITECTURE

#### Static if-conversion

If-conversion is used to reduce the number of mispredicted branches, which lead to cache invalidation and therefore penalizes performance. To benefit from if-conversion a processor must support predicated opcodes. These are opcodes which are only executed when certain conditions (e.g. flags in the status registers) are met. For CACAO ARM and x86\_64 are possible beneficiaries of if-conversion. Performance impact on real hardware is described in [4] for the Intel Itanium processor.

#### Inlining

Method inlining is another way to improve performance. Small methods are embedded in the caller instead of generating a method invocation. For Java this is especially true as a lot of getter methods are used which basically just return a value they read by a **getfield** instruction. Additionally a lot of initializers are called when creating an object. Most of them are empty or trivial. 80% of method invocations can be saved by inlining in some testcases[19].

Static, final and private methods are good candidates for inlining as the compiler knows which code will get called. Overwritten methods can not be inlined as the decision which implementation to call depends on the runtime type of the object. A potentially overwriteable method which is not overloaded on the other hand can be inlined as well. Care has to be taken when new classes get loaded by the program because some class may overload the method in which case the inlining has to be undone - by recompiling the method. All speculative inlinings need to be kept track of to handle this case.

#### **Block reordering**

All basic blocks get reordered with respect to their calling frequency. This is done to increase cache locality and described in [9].

#### **Register allocation**

Every slot from the stack machine model gets assigned a register on the real hardware. As there is only a limited number of registers available and the number of used stack slots may exceed the registers of a processor register allocation is crucial for performance. The register allocator in CACAO is replaceable, but for now only a very simple allocator is implemented. The simple register allocator first allocates interface registers [13] and does register precoloring for argument and return registers. Next so called temporaries and finally local variables are allocated. When there are not enough registers available the stack slot is allocated in memory and has to be swapped in before each usage and stored back afterwards. More sophisticated register allocators may avoid some spilling and copying but take more time and therefore hurt performance more than they benefit as compile time is part of method run time (at least for the first run). [13].

**LSRA** Linear Scan Register Allocation is a fast register allocator suitable for just in time compilation described in [15]. It's results are comparable with more expensive graph coloring based allocators. CACAO will only use LSRA when compiling a method using the optimizing compiler, the baseline compiler uses the simple register allocator described earlier.

#### Code generation

The last step of compilation is the code generation. CACAO supports multiple platforms and all phases so far have been generic. Code generation basically iterates all bytecodes of a method and writes machine code implementing theses bytecodes. Chapter 3 will examine the work of the code generator in more detail.

# 1.5 Java byte code

The Java compiler does not produce machine code which can be executed on the host CPU directly but an intermediate form called byte code. There are around 200 instructions defined which a virtual machine has to execute according to their specification. Instructions are specified as operations on an operand stack. This type of virtual machine is therefore called a stack machine. The program listing 1.3 manipulates the stack as shown in figure 1.5. The opcode iconst\_3 pushes the integer 3 on top of the stack, iconst\_5 pushes 5, iadd takes the two topmost elements of the stack, adds them and pushes the result back. The stack growing from bottom to top and its initial state is unknown but also unimportant.

The JVM internally uses 32 bit for each stack slot. Therefore the primitive types boolean, char, byte, short, int and float take exactly one stack slot, long and double take two. Each instruction consists of at least one byte (the opcode itself) followed by optional arguments. The getfield instruction for example uses two argument bytes indexing the field in the object, while

```

iconst_3

iconst_5

iadd

```

Listing 1.3: Stack operations

Figure 1.5: Stack changes

it's object reference is passed on the stack. The arithmetic instructions are additionally tagged with the type of the arguments (e.g. iadd adds two int whereas ladd adds two long values). Figure 1.6 shows the type prefixes.

The following sections list the most important opcodes defined by the virtual machine definition grouped by usage.

#### Arithmetic opcodes

- iadd, ladd, fadd, dadd addition

- isub, lsub, fsub, dsub subtraction

- imul, lmul, fmul, dmul multiplication

- idiv, ldiv, fdiv, ddiv division

- irem, lrem, frem, drem remainder of division

- ineg, lneg, fneg, dneg negation

#### Bit instructions

• ishl, lshl - shift left

| Prefix: | i   | 1    | f     | d      | b    | С    | S     | a       |

|---------|-----|------|-------|--------|------|------|-------|---------|

| Type:   | int | long | float | double | byte | char | short | address |

Figure 1.6: Instruction type prefixes

- ishr, lshr shift right

- iushr, lushr shift right unsigned (logical shift)

- ior, lor logical or

- iand, land logical and

- ixor, lxor logical exclusive or

#### Comparisons

- dcmpg, dcmpl compare doubles

- fcmpg, fcmpl compare floats

- lcmp compare longs

#### Conversions

- i21, i2f, i2d, l2f, l2d, f2d widening conversions

- i2b, i2c, i2s, l2i, f2i, f2l, d2i, d2l, d2f narrowing conversions

#### Flow control

- ifeq, iflt, ifle, ifne, ifgt, ifge, ifnull, ifnonull takes one int value from stack, compare with 0, and jump at a given offset if true.

- if\_icmpeq, if\_icmpne, if\_icmplt, if\_icmpgt, if\_icmple, if\_icmpge - take two int values from stack, compare and jump at given offset.

- if\_acmpeq, if\_acmpne take two addresses from stack, compare and jump at given offset.

- lookupswitch used to implement the switch/case statement of the Java language.

- tableswitch similar to lookupswitch

- goto, goto\_w jump at given address

- jsr, jsr\_w jump to subroutine, store return address on stack

- ret return from subroutine

## Load and store

The virtual machine additionally knows the concept of local variables. These are numbered memory locations, not located on the stack. Local variables are generated by the compiler for each method and can be thought of as an fixed size array. Local variables are used to pass method arguments and hold temporary variables needed during calculations. The following operations are used to access them.

- iload, lload, fload, dload, aload load value from given variable and stores on stack.

- bipush, sipush push a constant byte/short onto the stack.

- ldc, ldc2\_w push a 32/64 bit value onto the stack.

- istore, lstore, fstore, dstore, astore take value off stack and stores it in local variable.

- wide most opcodes use an 8 bit offset to number local variables. If such an opcode is preceded by wide it uses a 16 bit offset.

Some instructions used for optimization - like the already mentioned iconst\_3, which stores an integer value of 3 onto the stack - have been skipped for clarity.

#### **Stack operations**

- pop, pop2 remove the (two) topmost element(s) from the stack.

- dup, dup2 duplicate the topmost element (twice).

- dup\_x1, dup2\_x1, dup\_x2, dup2\_x2 duplicate one or two words and insert them one or two words below the top of stack.

- swap swap the two topmost elements.

#### **Object** operations

- new create an instance of a class

- instanceof test whether an object is of class type

- checkcast similar to instance of

#### **Field operations**

- getfield, getstatic load on stack content of (static) member

- putfield, putstatic store value in (static) member

## Method invocation

- invokevirtual invoke a method using vtable lookup.

- invokeinterface invoke a method looking up in interface table.

- **invokespecial** used to invoke initialization methods and methods from superclass and private methods.

- invokestatic invoke a static method

- ireturn, lreturn, freturn, dreturn, areturn return value of given type.

- return return void type.

#### Array operations

- newarray, anewarray, mulitnewarray create a new array.

- baload, caload, saload, iaload, laload, faload, daload, aaload load from array.

- bastore, castore, sastore, iastore, lastore, fastore, dastore, aastore store into array.

- arraylength store length of array onto stack.

### Miscellaneous operations

- athrow throw an exception.

- monitorenter, monitorexit each object has a monitor associated with it, when entered it blocks access from concurrent threads until left.

A detailed definition of the Java instruction set has been published by SUN (The Java<sup>TM</sup>Virtual Machine Specification, Second Edition) which is also available online at http://java.sun.com/docs/books/jvms/second\_edition/html/VMSpecTOC.doc.html.

# Chapter 2

# Related work

This chapter will introduce a few important other Java VMs. Sun's HotSpot, IBM's J9 and the open source Jikes RVM. The architecture of their code generator will be compared to CACAO's design. Further interesting VMs will be introduced. Kaffee an open source Java VM, Parrot the Perl 6 implementation and Mono a C# VM.

# 2.1 SUN HotSpot

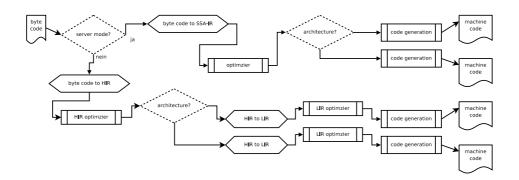

SUN's own Java VM implementation features two different implementations<sup>1</sup>. Client and server mode. Client mode JIT compiler focuses on local optimizations, whereas server mode takes the global situation into account at much higher compile time costs. Code generators are available for SPARC, x86 and AMD64. An rough overview of the architecture is given in figure 2.1.

CACAO does not feature two different operation modes (client, server),

<sup>&</sup>lt;sup>1</sup>http://java.sun.com/products/hotspot/whitepaper.html#client

Figure 2.1: SUN HotSpot code generation

Figure 2.2: IBM J9 code generation

the compiler has only one IR, whereas HotSpot has two IRs (in client mode). In client mode HotSpot differs hardware architecture earlier than CACAO and has a platform specific LIR.

## 2.2 IBM J9

The IBM J9 virtual machine is derived from the Sun Classic VM, but has been further developed[10]. Code generators are available for PPC, x86 and AMD64. The JIT compiler transforms the byte code into extended byte code (EBC) which is still stack based. After optimizing the EBC (e.g. inlining) this form is transformed into a register based quadruple (QUAD) representation. Common subexpression elimination is among other things performed on the finer grained quadruple code which is the transformed into a directed acyclic graph (DAG) which gets scheduled and is then transformed back into quadruple code for code generation. This architecture of the optimizing compiler is shown in figure 2.2.

IBM's J9 even features three IRs for the optimizing compiler. Like in CACAO most stages are generic, only the codegenerator is architecture specific.

# 2.3 Jikes RVM

The Jikes RVM<sup>2</sup> was initially started as project Jalapeño[1] by IBM in 1997. It has been put under an open source license in 2001 and is since then actively maintained. The main focus of the project is to provide a research VM. New ideas shall be quickly implementable on top of Jikes RVM. Nonetheless Jikes RVM is a fast VM too. Most parts of the VM are implemented in the Java language as well, only around 1000 lines of C code are needed for bootstrapping. Jikes RVM features an unoptimizing baseline compiler as well as an highly sophisticated optimizing compiler. Code generators are available for PPC and x86.

<sup>&</sup>lt;sup>2</sup>http://jikesrvm.org

```

protected final void emit_iadd() {

popInt(T0);

popInt(T1);

asm.emitADD(T2, T1, T0);

pushInt(T2);

}

```

Listing 2.1: Jikes RVM baseline add instruction

```

public final void emitADD(int RT, int RA, int RB) {

int mi = ADDtemplate | RT << 21 | RA << 16 | RB << 11;

mIP++;

mc.addInstruction(mi);

}</pre>

```

Listing 2.2: Jikes RVM baseline assembler add instruction

Listing 2.1 shows a baseline compiler code snippet taken from /rvm/src/ org/jikesrvm/compilers/baseline/ppc/VM\_Compiler.java emitting the code to generate a Java iadd instruction. The code snippet generating the assembler code is shown in listing 2.2 and is taken from src/org/jikesrvm/ compilers/common/assembler/ppc/VM\_Assembler.java

The optimizing compiler is using a different assembler, generated by a BURS[16] implementation. Listing ref 2.3 shows the definition of an add instruction take from rvm/src-generated/opt-burs/ppc/PPC\_Alu32.rules

An overview of the code generator is given in figure 2.3. Jikes's baseline compiler is similar to CACAO, its optimizing compiler features three IRs with one being hardware specific.

Figure 2.3: Jikes RVM code generation

# 2.4 Kaffe

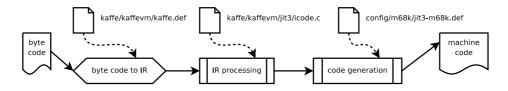

The Kaffe<sup>3</sup> project is one of the oldest free (GPL licensed) Java implementations around. Version 0.6 was released in 1996, version 1.1.7 was released in march 2007. Kaffe features an interpreter and a JIT for some architectures. It also supports different flavour of Unixes including Linux and FreeBSD. Version 1.1.7 includes JIT for ALPHA, ARM, X86, X86\_64, PPC, M68K MIPS, S390 and others. Kaffe has 2 different JIT engines, in this paper only JIT3 (the newer one) is covered. An architectural overview is shown in 2.4.

As a first step of code generation Kaffe translates the Java byte code into an Kaffe specific intermediate format. This transformation is driven by kaffe/kaffevm/kaffe.def. An example of such a transformation rule is given in listing 2.4, which shows the transformation for the Java bytecode operation IADD.

The translation of this sequence of opcodes into machine code is implemented in kaffe/kaffevm/jit3/icode.c. For each opcode processed a callback into an architecture specific code generator is invoked. This translation process knows about machine details and only invokes callbacks implemented by the code generator. This is controlled by a bunch of HAVE\_ macros, e.g. HAVE\_add\_int. An example of such a callback invocation is given in listing 2.5.

The Code generation is driven by a machine definition file in the config sub directory of the Kaffe source. For m68k the file is located at config/m68k/jit3-m68k.def. As example the generation of machine code performing integer addition is given in listing 2.6.

The main difference to the CACAO architecture is the highly configurable but generic code generator which drives machine code output for each

<sup>&</sup>lt;sup>3</sup>http://kaffe.org

```

define_insn(IADD)

{

/*

* ..., val1, val2 -> ..., val1+val2

*/

trace_jcode ("iadd\n");

check_stack_int(0);

check_stack_int(1);

add_int(stack(1), rstack(1), rstack(0));

pop(1);

}

```

Listing 2.4: Kaffe intermediate example

```

void

add_int(SlotInfo* dst, SlotInfo* src, SlotInfo* src2)

{

#if defined(HAVE_add_int_const)

if (slot_type(src) == Tconst) {

add_int_const(dst, src2, slot_value(src)->i);

}

else if (slot_type(src2) == Tconst) {

add_int_const(dst, src, slot_value(src2)->i);

}

else

#endif

_add_int(dst, src, src2);

}

```

Listing 2.5: Kaffe intermediate transformation

Figure 2.4: Kaffe code generation

```

define_insn(add_int, addi_RRR)

{

int r = rreg_int(2);

int w = rwreg_int(0);

assert(rreg_int(1) == w);

op_addl_dd(r, w);

}

static inline void

op_addl_dd(int src, int dst)

{

debug(("addl_%s,_%s\n", regname(src), regname(dst)));

assert_dreg(src);

assert_dreg(dst);

WOUT(0xD080 | (dst << 9) | (MODE_d << 3) | (src & 7));

}</pre>

```

Listing 2.6: Kaffe codegenerator definition example

platform. The code generator provides a bunch of functions emitting the assembler instructions, but contains no loop iterating the byte code.

# 2.5 Parrot

Parrot <sup>4</sup> 0.0.1 was released in September 2001, the last release as of now is 0.4.12 which has been released in May 2007. Parrot was originally started as implementation of Perl 6 but now focuses on providing a virtual machine for many dynamically typed languages as Python and Lua. Parrot is a register based virtual machine featuring a lot of high level instructions, including e.g. an implementation for the coversine function<sup>5</sup> or string concatenation. Parrot also tries to make objects implemented in different languages interoperable. The JIT compiler is ported for alpha, arm, x86, IA64, PC, sun4, MIPS and HPPA.

The Parrot JIT compiler is written in a markup language processed by a Perl script to generate C source code. An example snippet from src/jit/ppc/jit\_emit.h is given in listing 2.7 and shows how an add in-

<sup>&</sup>lt;sup>4</sup>http://www.parrotcode.org

<sup>51 -</sup> sin(x)

Figure 2.5: Parrot code generation

```

#define jit_emit_3reg_x(pc, opcode, D, A, B, type, Rc) \

*(pc++) = opcode << 2 | D >> 3; \

*(pc++) = (char)(D << 5 | A); \

*(pc++) = B << 3 | type >> 7; \

*(pc++) = (char)(type << 1 | Rc);

#define jit_emit_add_rrr(pc, D, A, B) \

jit_emit_3reg(pc, 31, D, A, B, 0, 266, 0);

Listing 2.7: Parrot codegeneration example</pre>

```

struction is emitted. Code generation is driven by src/jit/ppc/core.jit which implements Parrots intermediate instructions, an example is given in listing 2.8 and shows generation of an addition, the binop\_x\_x template expands to jit\_emit\_add\_rrr, this expansion is done by the Perl script tools/build/jit2c.pl. An overview is shown in figure 2.5.

The main difference to CACAO is the introduction of another intermediate language to describe the code generators. In addition Parrot is a register based VM where CACAO is stack based and Parrot is tailored towards dynamically typed languages.

Listing 2.8: Parrot JIT definition

```

lreg: OP_I8CONST {

MONO_EMIT_NEW_ICONST(s,state->reg1,tree->inst_ls_word);

MONO_EMIT_NEW_ICONST(s,state->reg2,tree->inst_ms_word);

}

```

#### Listing 2.9: Mini generic instruction selection

## 2.6 Mono

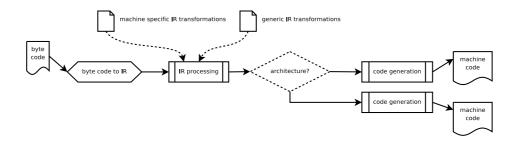

The Mono<sup>6</sup> project was initiated by Miguel de Icaza in 2001. Novell<sup>7</sup> picked up the idea and Mono 1.0 was released in June 2004. The Mono project aims to provide a C# compiler and a .NET runtime under a free software license. The Mono system is available for different operation systems and features a JIT compiler for all supported platforms. As of today s390, SPARC32, PPC, x86, x86\_64, IA64, arm, alpha and MIPS are supported. Mono code generation is driven by the function mini\_method\_compile which first of all reads in the .NET IL (intermediate language) and constructs a mono specific intermediate representation (IR).

This IR is then transformed by mini\_select\_instructions into a machine dependent optimized IR. An iburg like instruction selector[6] called mini has been implemented for this purpose. There are also generic rules, e.g. to map 64 bit operations to 32 bit operations, or to use floating point software emulation when appropriate. Listing 2.9 shows an example rule for loading a 64 bit constant on a 32 bit architecture (mono/mini/inssel-long32.brg).

mono\_codegen finally produces machine instruction from the IR by calling an architecture specific backend (e.g mono/mono/mini/mini-ppc.c). The code generator iterates all IR opcodes of a basic block and selects machine instructions by using a big switch statement. This process is visualized in figure 2.6.

The machine instructions are described in a CPU specific file, and example taken from mono/mono/mini/cpu-g4.md may look like add: dest:i src1:i src2:i len:4, which describes the add instruction and its register usage. This information is used by the Mono registers allocator and instruction scheduler, but is otherwise unrelated to instruction selection.

The biggest difference between CACAO and Mono is the machine dependent transformation on the IR performed by Mono. This reduces the size of each code generator as e.g. 64 bit arithmetic byte code instruction don't need to be implemented by each 32 bit generator. In CACAO each 32 bit

<sup>&</sup>lt;sup>6</sup>http://www.mono-project.com

<sup>&</sup>lt;sup>7</sup>http://www.novell.com

Figure 2.6: Mono code generation

code generator implements 64 bit arithmetic.

# 2.7 Summary

Despite their similar function code generators differ a lot. The number of introduced IRs is related to optimizations implemented. Only the commercial VMs implement the complex optimizations demanding different IRs. Some VM vendors decided to implement an instruction selector, while others iterate the IR and generate machine code by a switch statement. Another design decision is when to consider hardware specific aspects. Most code generators try to stay generic as long as possible. CACAO does not use an instruction selector. Therefore the code generators source size is huge, but mostly trivial. By directly implementing the machine code generating in C no additional language (like Parrot's JIT definition) has to be learned for development.

# Chapter 3

# Code generators for CACAO

CACAO provides code generators for many platforms. Currently code generators for ALPHA (FreeBSD, Linux), ARM (Linux) i386 (Cygwin, Darwin, FreeBSD Linux), MIPS (Irix, Linux), POWERPC (Darwin, Linux, NetBSD), SPARC64 (Linux), x86\_64 (Linux) and s390 (Linux) are available. When building CACAO for a platform the according code generator is linked statically. To be able to easily exchange code generators an internal interface is defined. A code generator has to implement this interface.

# 3.1 Symbols needed by CACAO

The following symbols need to be defined to link a code generator with CA-CAO. As CACAO is under development this list is not stable, probably some symbols have been renamed and/or added, removed. The functions prefixed with md\_ are machine dependent, but also often operating system depended, they have been factored out to make porting from one operating system to another easier. The asm\_ prefixed functions are implemented in assembler language for various reasons. The signatures of the functions do not match reality, none of them is void actually, the notation has been chosen to differ between functions and global variables, the signature is skipped for clarity.

- void codegen(void) {} Main driver function for the code generator.

- void createnativestub(void) {} Generates code which translates CACAO internal argument format to platform C ABI format and calls a native function.

- void createcompilerstub(void) {} Generates code which invokes the compiler when a not compiled method

is invoked.

- void md\_init(void) {} Initializations needed for the machine dependent part.

- void md\_get\_method\_patch\_address(void) {} When a method has been compiled the method entry point has to be patched so that further invocations execute the compiled code directly. This function returns a pointer to the memory location of the method entry point and differs types of method invocations.

- void md\_icacheflush(void) {} Invalidates the processors instruction cache. This is needed when code patching took place as the processor would execute obsolete instructions else.

- void md\_stacktrace\_get\_returnaddress(void) {} Returns the return address of the current stackframe. The caller does not need to know about the details of the platform. This is needed for the stacktrace generating code.

- void md\_codegen\_get\_pv\_from\_pc(void) {} Each CACAO method has a procedure vector, this is its start address (entry point). This function takes a program counter as argument and returns the start address of the method.

- void md\_signal\_handler\_sigsegv(void) {} Cacao uses illegal memory access to implement exceptions. The signal handler gets called by the operating system in such a case and activates exception handling.

- void md\_codegen\_patch\_branch(void) {} This function changes the displacement of a branching instruction. The caller does not need to know details about the platform.

- void md\_cacheflush(void) {} Invalidates the CPU data cache, this is needed when data patching took place otherwise the processor would work with obsolete values.

- void md\_param\_alloc(void) {} This function preallocates stack slots to argument registers for method invocations. This prevents copying values to argument registers by holding the arguments in the correct registers in the first place.

36

#### 3.1. SYMBOLS NEEDED BY CACAO

#### • void md\_return\_alloc(void) {}

Preallocates the register holding the return value of a native function call.

• int nregdescint;

An array containing the usage description for each integer register. A register description is one of: reserved, argument, saved and temporary. The register allocator needs this information. Saved registers are callee saved, whereas the others are caller saved.

#### • int nregdescfloat;

Same as nregdescint for floating point registers.

• void compare\_and\_swap(void) {}

Compare and swap (CAS) is a universal locking primitive [22] and can be used to implement lot of non-blocking algorithm. In CACAO it is used to implement method and object locks. Not all platforms are capable to provide an atomic implementation as it would be needed.

#### • #define STORE\_ORDER\_BARRIER()

Guarantees that store operation preceding the barrier are finished before stores following the barrier.

- #define MEMORY\_BARRIER\_BEFORE\_ATOMIC() Needed to implement the Java memory model as described in chapter 17 of the Java Language Specification <sup>1</sup>.

- #define MEMORY\_BARRIER\_AFTER\_ATOMIC() See MEMORY\_BARRIER\_BEFORE\_ATOMIC().

- #define MEMORY\_BARRIER() See MEMORY\_BARRIER\_BEFORE\_ATOMIC().

- #define PATCHER\_CALL\_SIZE The size of a patcher in bytes. Patcher are described in 3.6.

#### • #define BRANCH\_NOPS

Generates enough **nop** instructions to overwrite it with a branch instruction later.

• void asm\_vm\_call\_method{}

Called when a Java method is invoked by C code. Mainly performs argument adaption, from C ABI to CACAO intern argument handling.

<sup>&</sup>lt;sup>1</sup>http://java.sun.com/docs/books/jls/third\_edition/html/memory.html

- void asm\_vm\_call\_method\_[int|long|float|double] {} These four functions are specialized versions of the above. The type in the name indicates the type of the return value expected.

- void asm\_vm\_call\_method\_exception\_handler {} Needed to propagate exceptions beyond an asm\_vm\_call\_method stackframe. See 3.7 for more details.

- void asm\_call\_jit\_compiler {} Invokes the JIT compiler from within JIT code and takes care of the calling conventions.

- void asm\_criticalsections {} A data structure needed by asm\_getclassvalues\_atomic, contains start and end address of critical sections.

- void asm\_getclassvalues\_atomic {} Subtype testing in CACAO is implemented by relative numbering [18] which uses the post order numbering of an inheritance tree. These values need to be recomputed when new classes get loaded and may not be read while class loading is performed. This function reads a classes values and sets up a critical section around itself.

```

• void asm_abstractmethoderror {}

This stub gets called when an abstract method is executed (which is

prohibited in Java) and throws an AbstractMethodError exception.

```

# 3.2 Register allocation

When the code generator is invoked, all stack slots used by the method have been assigned a register or a memory location. The code generator has to emit code running on register based hardware, so each operand has to be loaded into a register before usage. For that reason three registers (of each type) are reserved for the code generator. Every bytecode instruction can be implemented using a maximum of three registers. The reserved registers are called REG\_ITMP1, REG\_ITMP2 and REG\_ITMP3 for integer operations and REG\_FTMP1, REG\_FTMP2, REG\_FTMP3 for floating point operations. The emit\_load\_s1, emit\_load\_s2 and emit\_load\_s3 functions are used to load operands for the current bytecode operation. These functions take a temporary register as argument and return the register holding the operand. When the operand was in memory it has been loaded into the given temporary registers, otherwise the register assigned for the operand by the register allocator

38

```

case ICMD_IADD:

s1 = emit_load_s1(jd, iptr, REG_ITMP1);

s2 = emit_load_s2(jd, iptr, REG_ITMP2);

d = codegen_reg_of_dst(jd, iptr, REG_ITMP2);

M_IADD(s1, s2, d);

M_EXTSW(d,d);

emit_store_dst(jd, iptr, d);

break;

```

Listing 3.1: Codegeneration for iadd

is returned. An emit\_store function is used to finally store the result in either destination register or memory location. The destination register of an operation is returned by the function codegen\_reg\_of\_dst. See listing 3.1 for an example showing the implementation of the iadd opcode on PPC64.

By using this API the code generator is completely decoupled from register allocation, with the costs of statically assigning three registers dedicated to the code generator.

# 3.3 Code generation macros

The code generator iterates over all bytecode instructions of the method to be compiled selecting machine code by a switch statement. The generated machine code is written to temporary memory and afterwards copied to an executable memory location. The assembler instructions are generated by macros, so care has to be taken with side effects of arguments which could be evaluated twice. To achieve a better conformity of the code generators all platforms try to use similar macro names originally inspired by alpha naming conventions. Listing 3.1 shows the implementation of the iadd operation for POWERPC64. One can see the load of the two operands. The macros M\_IADD emits the machine code for an addition, M\_EXTSW is needed for sign extension and is platform specific. Finally the result is stored in the according register. jd and iptr contain information about the state of the JIT compiler and the current instruction processed. The implementation of the M\_IADD is shown in listing 3.2.

Listing 3.2: Codegeneration macros

# **3.4** Post compile time code patching

One reason the code generated is written into a buffer is due to unresolved jumps. Imagine a forward jump in a method. The target address points into code still not generated and the compiler does not know the exact offset in advance as it depends on the opcodes in between. Additionally the offset also depends on the whereabouts (register, memory) of the operands used by the instructions in between as this may change their size. For that reason a post pass has been added to code generation which patches the code after generation. A function named codegen\_add\_branch\_ref is responsible for collecting branch addresses which may be unresolved at compile time. As an argument it takes the target basic block. When the jump can not be resolved the branch displacement will be patched in the post compilation phase using the function md\_codegen\_patch\_branch. By using the machine dependent patching function the post compilation phase is platform independent.

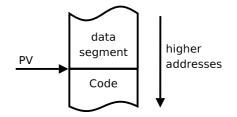

# **3.5** Data segment

The generated code needs lots of constant values, some embedded in the program executed but also function entry addresses. Some architectures can load immediate values large enough to hold all constant values needed, other architectures have immediates not covering the whole range. For that reason a data segment holding constant values is generated for each method. The data segment is built together with code and later both are copied into memory consecutively. The first operation of the method is reference by the procedure vector (pv) in CACAO. Further instructions are at memory locations above the pv the data segment is below the pv (see figure 3.1).

40

Figure 3.1: Data segment layout

When a constant exceeding the size of immediate operands is needed it is loaded from the data segment by using an indirect load operation. In addition a method header is stored in the data segment which points to a C data structure describing the method (e.g. stack size, argument types, signature). The exception table and the line number table are stored in the data segment as well.

# **3.6** Runtime code patching - Patchers

Some references can not be resolved at compile time at all. An example would be a getstatic instruction, which loads a static field from a given class. The class may be unresolved when code for getstatic was generated in which case the runtime system has to load and initialize the class, resolve the address of the member and return that value. For this purpose so called patchers are embedded into the generated code which remove themselves after execution as they are only needed once.

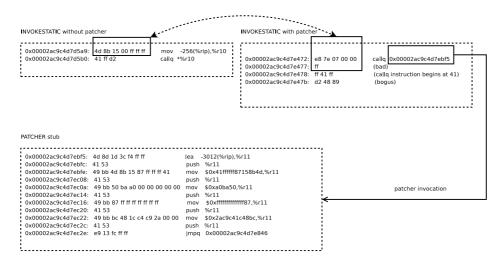

#### The old approach

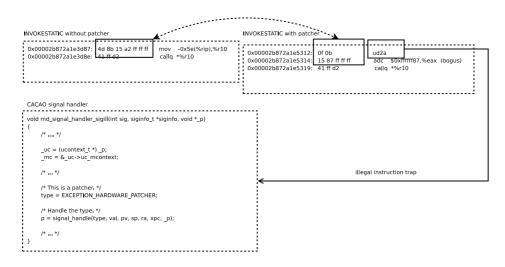

Old versions of CACAO implement patchers as branch instructions and jump to a generated patcher stub setting up a special stack frame and invoke asm\_patcher\_wrapper thereafter. asm\_patcher\_wrapper takes care of register storing and restoring and calls patcher\_wrapper which is written in C. Figure 3.2 shows the assembler code of an embedded patcher. These snippets are from x86\_64 and show an invokestatic with and without patcher. The leftmost snippet shows an invocation with known method entry point. The right snippet shows the code generated when the entry point was unknown at compile time. A branch to a patcher has been emitted. The patcher invocation is one byte shorter than the original invocation, therefore the assembler output is disturbed by the last byte of the original machine code (0xff). One can see the sequence 0x41 0xff 0xd2 which is the callq of the original

Figure 3.2: Patcher assembler output (old)

code. The patcher jumps to the shown patcher stub. This stub sets up the special stack layout used by patchers and invokes the patcher wrapper. This wrapper finally calls the patcher needed. The patcher is implemented in C code and afterwards the patcher invoking instruction is overwritten by the original machine code. This code is an argument for the patcher and can be seen in the patcher stub at line 3. 0x41fffff87158b4d is the endian correct representation of a x86\_64 mov instruction as seen in line 1 of the code snippet without patcher.

On some architectures patcher invocations may be larger than the instruction patched. This may lead to problems at basic block borders. Imagine a short instruction needing patching at the end of a basic block. The patcher invocation exceeds the basic block and overwrites some bytes in the following basic block. For correct operation the patcher would need to be executed before the following basic block is executed, but that is not assured. For that reason when a patcher is inserted into emitted code it is checked if at least PATCHER\_CALL\_SIZE bytes follow. If that is not the case an appropriate number of NOPs is inserted at the end of the basic block.

#### The new approach

Recent versions of CACAO use a different approach to decrease the assembler code and get rid of the patcher stubs at all. Instead of branching to a stub, an illegal instruction is generated covering the original code. The operating system raises a signal caught by a signal handler. The signal handler needs to be able to differ patchers from exceptions, e.g. by using a different trapping

Figure 3.3: Patcher assembler output (new)

instruction. The handler then looks up the proper patcher and invokes it. For that purpose a list of patching positions combined with the patcher to be invoked and the data passed via patcher stack in the old approach is kept in memory. The code generator needs to provide a function called emit\_trap capable to generate a trapping instruction using 32 bits. Assembler code to build the patcher stack can be removed, as well as patcher stub generating code.

Figure 3.3 shows the generated assembler code on the x86\_64 architecture. The illegal instruction (u2da) is generated where a patcher is needed When the trap instruction is executed control flow branches to a signal handler written in C. The disassembler wrongly interpretes the bytes 15 87 ff ff ff as adc instruction. They are part of the offset of the mov instruction covered by the ud2a instruction.

A race condition exists when patching the trapping instruction in case he instruction can not be overwritten atomically on multiprocessor machines. One thread could just patch back the original code, while a different thread executes exactly this code and comes across a half patched instruction. For that reason single word instructions are used for trapping, as they can be written back atomically.

# 3.7 Exceptions

Exceptions are an integral part of the Java language and are used a lot. Nonetheless exceptions are rare events and occur irregularly. Figure 3.4 shows the number of exceptions for a run of the DaCapo benchmark suite using default data size. Although the number of exception for **lusearch** seems to be huge it has to be seen in relation to the approximately 540 million method calls.

Each method has an exception handler table associated. This table describes the start and end instruction of each exception handler directly corresponding to the Java language try clause. When an exception occurs at some point in the program, a lookup is performed in the exception table. The type of the occurring exception is compared to the type of each handler covering the throwing instruction.

If a match can be found the handler is executed, else the exception is propagated outside the method. For the caller this looks like a throwing invoke instruction. As the caller of a method is unknown at compile time, the caller has to be determined at runtime. This is achieved by looking up the return address which is stored on the stack. The offset is known as CACAO knows about the stack usage of each method. Stack space is allocated on method entry and no dynamic allocation is performed.

An operation called "stack unwinding" is performed whenever an exception is propagated to its caller. As control flow continues at the invoking instruction all callee saved registers have to be restored for each stack frame unwound. Callee saved register are stored on the method stack when a method is entered, therefore the restore operation is implemented by loading these registers from known stack locations.

This process either terminates when an appropriate handler has been found or the whole stack is unwound in which case the exception is unhandled and the program will be aborted.

In CACAO no explicit code is generated for calling back the runtime when an exception occurred but an illegal memory operation is performed. POSIX compatible operation systems provide a signal handling mechanism which invokes a function in this case. This signal handler tests if the memory operation was performed intentionally and if so it calls the exception handling code. In case the memory access took place unintentionally an internal exception is thrown and the vm aborts.

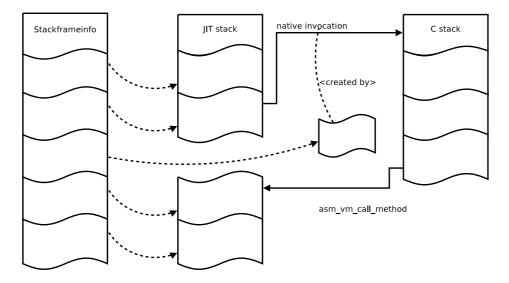

When native functions have been called they could have thrown an exception too. Natives can not throw exceptions directly but have to notify the runtime by setting a flag in the environment. When they return the environment is checked for an exception and exception handling code is executed when needed. Exception handling is complex because natives may call back into Java code. The stack layout is only known in JIT code, native code has a different stack layout and stack unwinding would fail when a native frame is found. Therefore a chained data structure called stackframe info is built up when invoking natives. Figure 3.5 illustrates this chaining. Technically

| $\operatorname{antlr}$ | bloat | chart | fop  | hsqldb | jython | lusearch | luindex | pdm   |

|------------------------|-------|-------|------|--------|--------|----------|---------|-------|

| 318                    | 265   | 1194  | 6233 | 224    | 40040  | 524381   | 5014    | 15420 |

Figure 3.4: Number of exceptions in DaCapo

Figure 3.5: Stackframeinfo chaining with native invocation

there are no **stackframeinfo** structures for JIT frames, as this stack layout is known and contains all needed information already.

When unwinding the stack finds asm\_vm\_call\_method (each native to Java invocation is performed by this function), the exception is caught and builtin\_throw\_exception is invoked which assignds the exception object to the (thread) global exceptionptr. When the asm\_vm\_call\_method was invoked by a native the stackframeinfo structure enables the exception handling code to figure out the call site in JIT code (see stacktrace\_create).

# Chapter 4

# **POWERPC64** code generator

# 4.1 The POWERPC64 architecture

The POWERPC architecture<sup>1</sup> has been created in 1991 by Apple, IBM and Motorola. The specification describes many features, but a processor does not have to implement all of them. There exist specifications for 32 and 64 bit modes, as well as little and big endian modes. CACAO supports 64 bit big endian mode. POWERPC is a reduced instruction set computer (RISC) CPU, with a load-store design. It has 32 general purpose registers and 32 floating point registers. Instructions have a fixed size of 32 bit. The floating point registers are 64 bit wide and can hold IEEE-754<sup>2</sup> single and double precision values.

# 4.2 Design decisions

#### 4.2.1 PPC64 ELF ABI

The Linux Standard Base (LSB) published by The Linux Foundation<sup>3</sup> specifies calling conventions and stack layout to be used for PPC64. CACAO implements LSB  $3.1^4$ .

<sup>&</sup>lt;sup>1</sup>http://www.power.org

<sup>&</sup>lt;sup>2</sup>http://ieee.org

<sup>&</sup>lt;sup>3</sup>http://www.linux-foundation.org

<sup>&</sup>lt;sup>4</sup>http://refspecs.freestandards.org/LSB\_3.1.0/LSB-Core-PPC64/

LSB-Core-PPC64.html

| Figure 4.1:          | n descriptor |                     |

|----------------------|--------------|---------------------|

| function entry point | TOC address  | environment pointer |

#### 4.2.2 PPC64 CACAO ABI

The CACAO register usage is shown in figure 4.2. r0 has a special meaning during address operations on PPC64 and can not be used uniformly therefore. To keep the register allocator simple it is marked as reserved. r1 is used as stack pointer conforming to the ELF ABI. r13 is reserved for system usage. r12 is also reserved and is used by the runtime linker when invoking function descriptors.

#### Function descriptors

r2 is used for linking purpose and contains a linking module specific address pointing to the start of the data segment called TOC (table of contents). The compiler generates code loading constants relative to r2. When invoking functions residing in an external linkage unit (e.g. a shared object) a special calling sequence invoking a so called function descriptor is used. The format of a function descriptor is shown in 4.1. The function descriptor is provided instead of the function entry point when calling an external symbol. This demands different calling conventions when linking CACAO statically.

#### 4.2.3 Loading addresses

To load a 64 bit address into a register the assembler sequence 4.1 is needed. This is due to the 32 bit fixed sized opcodes which restrict immediate values to 16 bit for lis and ori. rldicr shifts the register left 32 bits and then the rest of the 64 bit value is ORed in. As even the "Hello World" program needs about 13000 address constants using the code from listing 4.1 to load addresses would waste a lot of memory. For that reason all address constants are loaded using the data segment on PPC64. For that purpose one register is reserved and holds the start address of the data segment during execution of JIT code. This register is called pv the procedure vector. Loading an address constant is thus reduced to a single 32 bit long ld instruction with a 16 bit signed offset. For offsets beyond this 32 kb boundary the addis instruction is used to realize an effective offset of 32 bit which restricts the maximum size of the data segment to 2 GiB. The memory consumption is 12 byte for small offsets and 16 for larger ones instead of 20 bytes for the sequence shown in listing 4.1.

| Register | Argument | Callee saved | Caller saved | Reserved |

|----------|----------|--------------|--------------|----------|

| r0       |          |              |              | Х        |

| r1       |          |              |              | Х        |

| r2       |          |              |              | Х        |

| r3-r10   | Х        |              |              |          |

| r11      |          |              |              | Х        |

| r12      |          |              |              | Х        |

| r13      |          |              |              | Х        |