The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

**DIPLOMARBEIT**

# Entwicklung eines ,,Hardware Description Language" Testbench-Generators

ausgeführt am Institut für Computertechnik der Technischen Universität Wien

unter der Anleitung von Univ. Prof. Dipl.-Ing. Dr. techn. Richard Eier,

Univ. Ass. Dipl.-Ing. Martin Horauer und

Univ. Ass. Dipl.-Ing. Wolfgang Radinger

als verantwortlich mitwirkendem Universitätsassistenten

durch

Csongor Huba Attila Sass Kornhäuselgasse 5/4/10, 1200 Wien Matr. Nr. 9227693

| Wien, 24.01.2005 |                |

|------------------|----------------|

|                  | (Unterschrift) |

# Kurzfassung

Die computerunterstützte Simulation hat auch in der Digitaltechnik die Spuren hinterlassen. Um eine Simulation durchführen zu können, wird ein Modell des Entwurfsobjekts benötigt. Die Modellierung der digitalen Systeme wurde durch die HDL (Hardware Description Language) Sprachen vereinfacht. Eine sehr verbreitete Variante der HDL Sprachen ist VHDL (Very High Speed Integrated Circuit Hardware Description Language). Mit VHDL werden die Funktionalität und das zeitliche Verhalten des Entwurfsobjekts modelliert. Durch Simulationswerkzeuge können bereits komplexe VHDL-Modelle simuliert werden. Damit kann die Funktionalität des Entwurfsobjekts vor einer Hardware-Realisierung überprüft werden.

Ein nicht zu unterschätzender Teil einer Hardware-Entwicklung ist die Überprüfung des Entwurfsobjekts. Die Fehler rechtzeitig zu Erkennen und zu Beseitigen, reduzieren die Entwicklungszeiten und die Entwicklungskosten. Um die korrekte Funktion des Modells zu überprüfen, wird eine Testbench realisiert. Die Realisierung einer Testbench ist eine mühsame und kostspielige Arbeit. Die Testbench-Strukturen weisen meistens einen ähnlichen Aufbau auf. Diese bestehen aus einem Datengenerator, aus Stimulidaten und weiteren Modulen für die Auswertung der Ergebnisse.

Im Rahmen dieser Diplomarbeit werden zwei Testbench-Strukturen präsentiert. Ausgehend von diesen Strukturen und von weiteren Überlegungen, um die Entwicklung einer Testbench und die Erfassung der Stimulidaten zu erleichtern, wurde ein Testbench-Generator realisiert. Die notwendigen Daten für eine Testbench werden mit dem Testbench-Generator über eine grafische Benutzeroberfläche erfasst. Die Daten sind auf einer sehr hohen Abstraktionsebene dargestellt. Dadurch können jeweils eine Vielzahl von Testbench-Strukturen, Stimulibefehl Modellen und Dateiformaten unterstützt werden. Die Dateien werden mit dem Testbench-Generator erzeugt. Welche Dateien generiert werden, können vor der Generierung ausgewählt werden. Die derzeit unterstützten Testbench-Strukturen und Stimulibefehl Modelle werden in dieser Arbeit auch präsentiert. Die Erweiterung der unterstützten Testbench-Strukturen, Stimulibefehl Modelle oder weiterer Dateiformate kann mit der Entwicklung neuer Programmmodulen realisiert werden, die mit einem Plugin-Mechanismus in den Testbench-Generator eingebunden werden können.

### **Abstract**

Computer aided simulation left its traces also in the realm of digital technology. In order to carry out a simulation a model of the draft-object is needed. Modeling digital systems is simplified by HDL (Hardware Description Language). One widely used variant of HDL languages is VHDL (Very High Speed Integrated Circuit Hardware Description Language). Using VHDL the functionality and the temporal behaviour of draft object is modelled. Simulation tools are already able to simulate complex VHDL models. In such a way the functionality of a draft object can be verified before the realisation of the hardware.

One Step in developing hardware which should not be underestimated is testing the draft object. Identification and elimination of errors in due time reduces development time and development costs. In order to carry out a test as regards the proper functioning of the model a testbench is realised which is a cumbersome and expensive task. Most of the testbenches have similar structures. These consists a data generator, stimulus data and modules for the evaluation of the results.

Within the scope of my thesis some testbench structures are presented. Outgoing from these structures and from further considerations in order to facilitate the development of a testbench and the collection of the stimulus data a testbench generator is realized. Necessary data for the testbench are gathered with the help of the testbench generator. The data are displayed on a very high level of abstraction. Thus many testbench structures, stimulus command models and other file formats can be supported. The files are produced with the testbench generator. What kind of file is necessary can be selected before the generation. In the context of this thesis already existing structures and command models are also presented. An extension of the supported testbench structures, stimulus command models or other file formats can be realized with the development of new program modules, which can be merged with a plug-in mechanism into the testbench generator.

# **Danksagung**

Ich möchte mich bei allen Personen bedanken, die mich während meines Studiums und meiner Aufwendungen für die Diplomarbeit unterstützt haben.

Für die gute Betreuung möchte ich mich im Besonderen bei Herrn Dipl.-Ing. Martin Horauer und bei Herrn Dipl.-Ing. Wolfgang Radinger bedanken.

Meinen Eltern und meiner Familie gilt ein ganz besonderer Dank.

Meine Frau Judit hat immer Verständnis gezeigt, wenn ich meine Freizeit nicht ihr und meinen Kindern gewidmet, sondern für mein Studium aufgebracht habe.

Für die moralische Unterstützung möchte ich Mag. Dieter Maier, Mag. Christian Lintner und allen Kollegen danken.

# Abkürzungen

AMS Analog und Mixed Signal

API Application Programming Interface

ASIC Application Specific Integrated Circuit, Anwendung spezifischen integrierten

Schaltungen

EIS Enterprise Information System

ER Entity Relationship

HDL Hardware Description Language

ISS Instruktion Set Simulator

SQL Structured Query Language

TBG Testbench-Generator

UML Unified Modeling Language

UUT Unit Under Test

VHDL Very high speed integrated circuit Hardware Description Language

VHSIC Very High Speed Integrated Circuit

XML Extended Markup Language

# Inhaltsverzeichnis

| 1 | Entwickl | ung von integrierten Schaltkreisen | 1  |

|---|----------|------------------------------------|----|

|   | 1.1 VHI  | OL Entwicklung                     | 1  |

|   | 1.2 Mod  | lellierung mit VHDL                | 2  |

|   | 1.2.1    | Abstraktion                        | 2  |

|   | 1.2.2    | Modularität                        | 3  |

|   | 1.2.3    | Hierarchie                         | 4  |

|   | 1.3 Desi | ign Flow                           | 4  |

|   | 1.4 Test | bench-Strukturen                   | 6  |

|   | 1.5 Rela | nted Works                         | 8  |

|   | 1.5.1    | Kommerzielle Werkzeuge             | 8  |

|   | 1.5.2    | Freie Werkzeuge                    | 10 |

|   | 1.5.3    | Vergleich der Werkzeuge            | 11 |

|   | 1.6 Auf  | gabenstellung                      | 12 |

| 2 | Testbenc | h-Generator Design                 | 13 |

|   | 2.1 Test | bench-Generator Spezifikation      | 13 |

|   | 2.1.1    | Eingabefunktionalität              |    |

|   | 2.1.2    | Ausgabefunktionalität              |    |

|   | 2.2 Test | bench-Struktur mit Controller      |    |

|   | 2.2.1    | Parser                             | 17 |

|   | 2.2.2    | Controller                         | 19 |

|   | 2.2.3    | Stimuligenerator                   | 22 |

|   | 2.2.4    | Taktgenerator                      | 23 |

|   | 2.2.5    | Comparator                         | 25 |

|   | 2.2.6    | Reportgenerator                    | 26 |

|   | 2.3 Test | bench-Struktur ohne Controller     | 28 |

|   | 2.4 Stim | nulibefehl Modelle                 | 28 |

|   | 2.4.1    | Stimulibefehl Modell 1             | 29 |

|   | 2.4.2    | Stimulibefehl Modell 2             | 30 |

|   | 2.4.3    | Stimulibefehl Modell 3             | 31 |

|   | 2.5 Test | bench-Generator Datenmodell        | 31 |

|   | 2.5.1    | Signaldefinition                   | 33 |

|   | 2.5.2    | Signalwertdefinition               | 35 |

|   | 2.5.3    | Befehlsdefinition                  | 38 |

|   | 2.5.4    | Programmdefinition                 | 42 |

|   | 2.5.5    | Moduldefinition                    | 43 |

|   | 2.5.6    | Taktdefinition                     | 43 |

|   | 2.5.7    | Comparator Definition              | 44 |

|   | 2.5.8    | Reportgenerator Definition         | 45 |

|     | 2.5.9  | )     | Konstantendefinition                       | 45 |

|-----|--------|-------|--------------------------------------------|----|

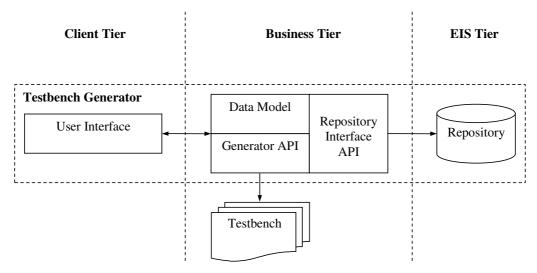

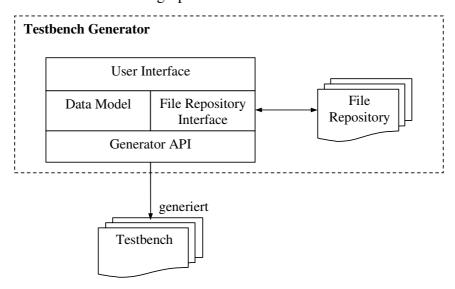

|     | 2.6    | Tes   | tbench-Generator Architektur               | 45 |

|     | 2.6.   | 1     | User Interface                             | 46 |

|     | 2.6.2  | 2     | Data Model                                 | 46 |

|     | 2.6.3  | 3     | Generator API                              | 46 |

|     | 2.6.4  | 4     | Repository                                 | 46 |

| 3   | Test   | benc  | h-Generator Implementierung                | 48 |

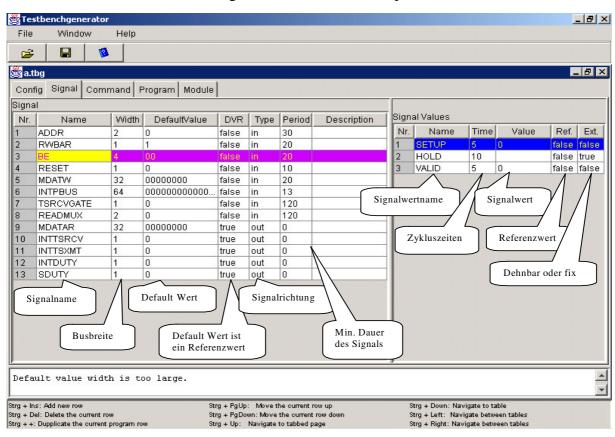

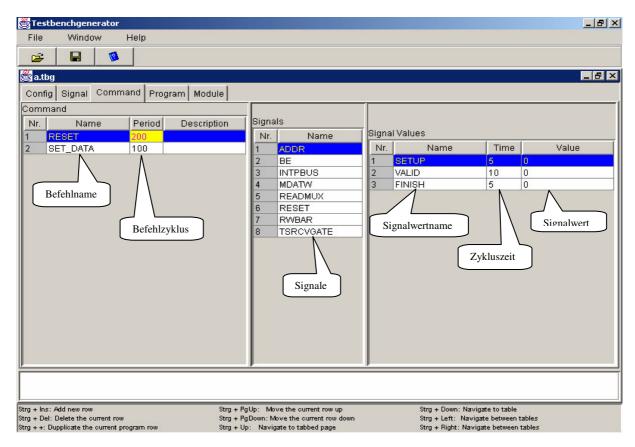

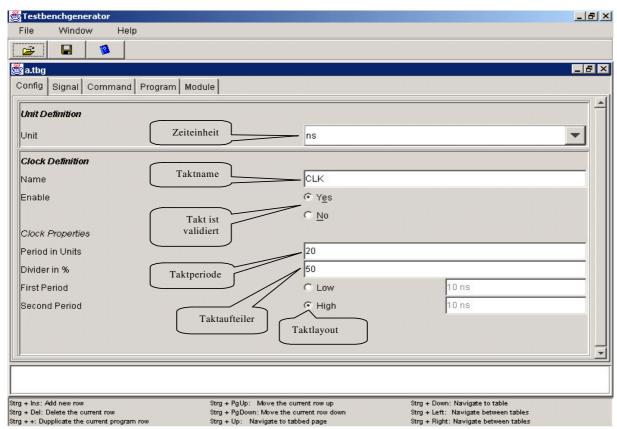

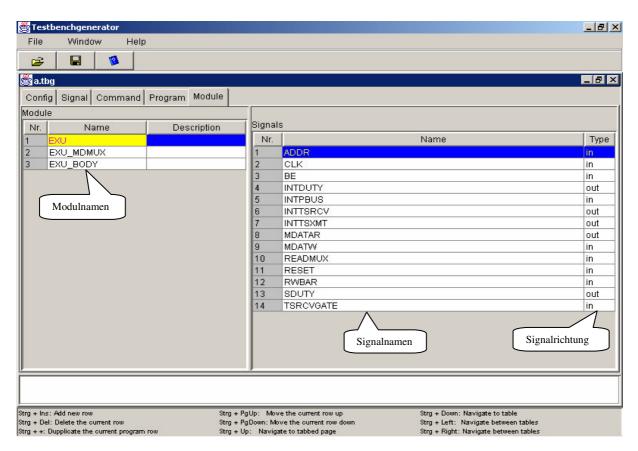

|     | 3.1    | Use   | r Interface                                | 48 |

|     | 3.1.   | 1     | Masken für die Befehlsbibliothekerstellung | 49 |

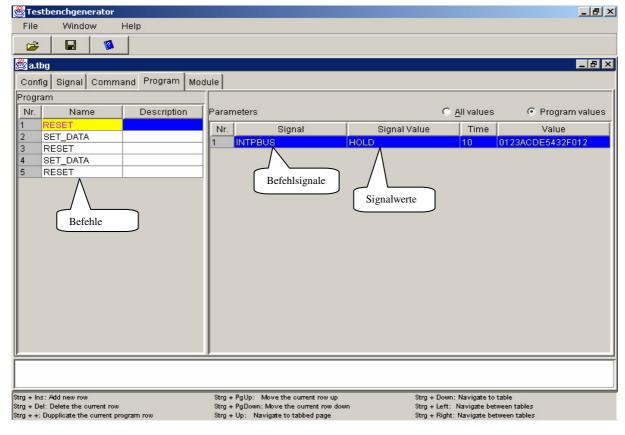

|     | 3.1.2  | 2     | Masken für die Programmerstellung          | 50 |

|     | 3.2    | Gen   | eratoren                                   | 53 |

|     | 3.3    | Rep   | ository                                    | 53 |

| 4   | Anw    | vend  | ungszenario (Case Study)                   | 54 |

|     | 4.1    | Auf   | gabenbereiche                              | 54 |

|     | 4.1.   | 1     | Testfälle identifizieren                   | 54 |

|     | 4.1.2  | 2     | Design der Testbench                       | 54 |

|     | 4.1.3  | 3     | Realisierung der Testbench                 | 54 |

|     | 4.1.4  | 4     | Simulation und Auswertung der Ergebnisse   | 55 |

|     | 4.2    | Bei   | spiel                                      | 55 |

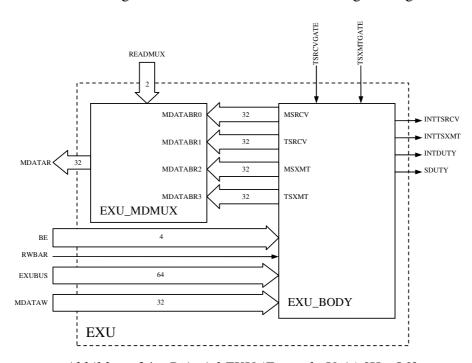

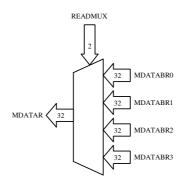

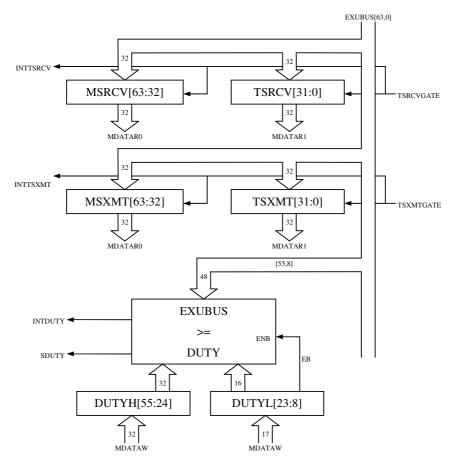

|     | 4.2.   | 1     | Beschreibung des Testobjekts               | 55 |

|     | 4.2.2  | 2     | Testfälle identifizieren.                  | 63 |

|     | 4.2.3  | 3     | Design der Testbench                       | 63 |

|     | 4.2.4  | 4     | Realisierung der Testbench                 | 68 |

|     | 4.2.5  | 5     | Simulation und Auswertung der Ergebnisse   | 73 |

| 5   | Ana    | lyse. |                                            | 74 |

|     | 5.1    | Zus   | ammenfassung                               | 74 |

|     | 5.2    | Aus   | blick                                      | 75 |

| т ; | orotur | 1047  | ichnic                                     | 76 |

# 1 Entwicklung von integrierten Schaltkreisen

Für die heutige Generation ist die Verwendung der mikroelektronischen Anlagen in allen Bereichen eine Selbstverständlichkeit. Fast jeder kennt die Bedienung eines Fernsehers, eines Telefongerätes oder eines Bordcomputers. Die Funktionalität dieser basiert auf bestimmten elektronischen Schaltungen, die grundlegend aus zwei Arten von Schaltkreisen bestehen. Einige Entwicklungen verwenden nur Standardschaltkreise, andere benötigen Spezialbausteine, um die gewünschte Funktionalität zu erreichen. Eine integrierte elektronische Schaltung, die für bestimmte Anwendungen erstellt ist, wird ASIC (Application Specific Integrated Circuit) genannt. Der Entwurf solcher Schaltungen wird durch die Verwendung einer Hardware-Beschreibungssprache und von Software-Werkzeugen stark erleichtert.

VHDL (Very high speed integrated circuits Hardware Description Language) ist eine formale, genormte Hardware-Beschreibungssprache. Sie wird immer mehr bei der Entwicklung von Mikrochips, insbesondere von ASIC, eingesetzt. Durch die Simulation können die Kodierungsfehler und die konzeptionellen Fehler des Modells aufgedeckt werden. Das VHDL-Modell wird mit verschiedenen Eingangswerten stimuliert und die Reaktionen des Modells können beobachtet und überprüft werden. Um ein System letztendlich fertigen zu können, muss die Beschreibung immer genauer werden. Die Umformung einer weniger detaillierten Beschreibung in eine mehr detaillierte Beschreibung wird als Synthese bezeichnet. Es gibt Synthesewerkzeuge, die einzelne Konstrukte von Hardwarebeschreibungssprachen direkt auf Hardwareelemente abbilden können. Die Top-Down-Designmethode mit VHDL in Verbindung mit der Simulation und mit der automatischen Logiksynthese ermöglicht die Bewältigung der Komplexität von integrierten Schaltungen. Auf Grund des selbstdokumentierenden Charakters von VHDL kann ein mit VHDL beschriebenes Modell auch eingeschränkt als Dokumentation dienen.

# 1.1 VHDL Entwicklung

Die Entwicklung von VHDL ging vom amerikanischen Verteidigungsministerium aus. Das Ziel war eine maschinen- und menschenlesbare Sprache zur Beschreibung einer Hardware zu realisieren. VHDL wird ständig erweitert und überarbeitet. Der Standard selbst brauchte 16 Jahre von der ursprünglichen Ideensammlung bis zum offiziellen IEEE Standard. Erstmals wurde VHDL in 1987 standardisiert. Bei der Verabschiedung des Standards einigte man sich, in einem Zeitraum von fünf Jahren, neue überarbeitete Versionen des Standards herauszubringen. Dies führte bisher zu einer Erneuerung des Standards im Jahre 1993, 1998 und 2002. Eine bedeutende Erweiterung ist eine Übermenge von VHDL, nämlich VHDL-AMS (Analog und Mixed Signal). Es handelt sich um eine Erweiterung von analogen Beschreibungskonstrukten. Eine aktuelle Sammlung der Standards der Version 2002 ist in [EDA04] zu finden.

# 1.2 Modellierung mit VHDL

Die Modellierung hat in der Hardware- und Software- Entwicklung immer mehr an Bedeutung gewonnen. Die Modelle machen die Entwicklungen übersichtlicher. In VHDL wurden drei wichtige Modellierungsmethodiken berücksichtigt:

- 1. **Abstraktion:** verschiedene Teile eines Modells unterschiedlich detailliert zu beschreiben.

- 2. **Modularität:** große Funktionsblöcke zu unterteilen und in abgeschlossene Unterblöcke, den so genannten Modulen, zusammenzufassen.

- 3. **Hierarchie:** ein System aus mehreren Modulen, die wiederum aus mehreren Modulen bestehen können, aufzubauen.

#### 1.2.1 Abstraktion

Die Abstraktion erlaubt es, verschiedene Teile eines Modells unterschiedlich detailliert zu beschreiben. Die Module, die nur für die Simulation gebraucht werden, müssen nicht so genau beschrieben werden, wie Module die für die Synthese gedacht sind.

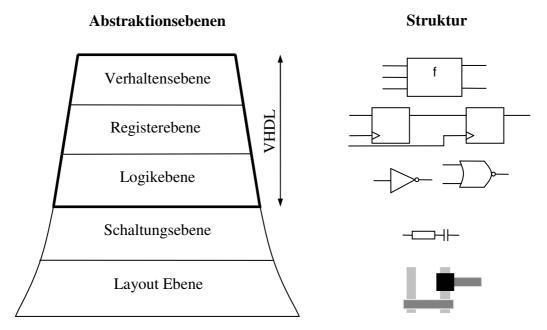

Die Abstraktion wird definiert als das Weglassen von Detailinformationen. Es wird also zwischen aktuell wichtigen und unwichtigen Informationen unterschieden. Eine neue Abstraktionsebene wird definiert, in dem bestimmt wird, welche Informationen auf dieser Ebene wichtig sind und welche unwichtig. Die unwichtigen Informationen werden bei der Modellierung auf dieser Abstraktionsebene nicht berücksichtigt. Soll ein Modell einen bestimmten Abstraktionsgrad besitzen, so muss jedes Modul des Modells den gleichen Abstraktionsgrad besitzen. Ansonsten entsteht ein gemischtes Modell. In der ASIC Modellierung werden fünf Abstraktionsebenen unterschieden, die graphisch in der Abbildung 1 dargestellt sind:

- Verhaltensebene: gibt die funktionale Beschreibung des Systems wieder. Es gibt keinen Systemtakt und die Signalwechsel sind asynchron, mit Schaltzeiten beschrieben. In der Regel sind solche Beschreibungen nur simulierbar, nicht aber synthetisierbar.

- 2. **Registerebene:** wird mittels zusammen geschalteter Funktionsblöcke, wie z.B. Register, ALU, Zähler oder Speicherelemente, aufgebaut. Die Funktionsblöcke können auch parallel arbeiten. Die Register Veränderungen und Zustandsübergänge werden mit Wahrheits-, bzw. Zustandsübergangstabellen beschrieben.

- 3. **Logikebene:** das gesamte Design wird durch Logikgatter und speichernde Elemente beschrieben. Den Schritt von der Registerebene zur Logikebene übernehmen die Synthesewerkzeuge.

- 4. Schaltungsebene: Wenn die topologische Objekte miteinander verknüpft sind,

entsteht eine Schaltung. Die Struktur der Schaltung ist aus passiven und aktiven Bauelementen aufgebaut. Für die Beschreibung des Verhaltens der elektrischen Größen im Zeitbereich werden im allgemeinem Differentialgleichungen verwendet.

5. **Layout Ebene:** Die unterste Ebene bildet das Layout. Hier werden die verschiedenen elektronischen Bauelemente in der entsprechenden Technologie auf den Ebenen des Chips verteilt und verbunden. Nach dem Layout kann anschließend die Schaltung gefertigt werden.

Abbildung 1 – ASIC Modellierung Abstraktionsebenen

In der Literatur gibt es weitere Definitionen der Abstraktionsebenen. In [Arm00] oder in [Hof97] wurden z.B. sechs Ebenen Definiert.

VHDL findet Anwendung in den oberen drei Abstraktionsebenen. Es ist nicht geeignet, ein Layout zu beschreiben. Der Wechsel von einer höheren zu einer tieferen Abstraktionsebene wird unterschiedlich gut von Computerwerkzeugen unterstützt.

#### 1.2.2 Modularität

Die Modularität erlaubt, große Funktionsblöcke zu unterteilen und in abgeschlossene Unterblöcke, so genannte Module, zusammenzufassen. Dadurch kann ein komplexes System in handhabbare Subsysteme unterteilt werden. Die Kriterien, nach denen die Unterteilung vorgenommen wird, können von Entwurf zu Entwurf unterschiedlich sein. Meist erfolgt sie aber nach funktionalen Gesichtspunkten. Dies erlaubt, z.B. die Modellierung des Gesamtsystems auf mehrere Entwickler aufzuteilen. Jeder Entwickler entwirft ein abgeschlossenes Subsystem.

## 1.2.3 Hierarchie

Die Hierarchie erlaubt, ein System aus mehreren Modulen, die wiederum aus mehreren Modulen bestehen können, aufzubauen. Eine Ebene in der Beschreibungshierarchie kann also ein oder mehrere Module mit unterschiedlichem Abstraktionsgrad, beinhalten. Die Untermodule der darin enthaltenen Modulen bilden die nächste darunter liegende Hierarchieebene.

Die Modularität und die Hierarchie dienen also der Vereinfachung und der Ordnung. Es gibt noch weitere Vorteile: Es ist möglich an beliebigen Stellen unterschiedliche Realisierungen eines Moduls zu untersuchen. Es wird jeweils nur die entsprechende Einbindung im Gesamtmodell geändert. Zu einem Simulationsmodell kann z.B. neben dem zu entwerfenden digitalen Modul auch eine analoge Schnittstelle gehören. Auch andere, bereits als echte Hardware vorliegende Bausteine (ASICs, FPGAs), können als Simulationsmodelle eingebunden werden.

# 1.3 Design Flow

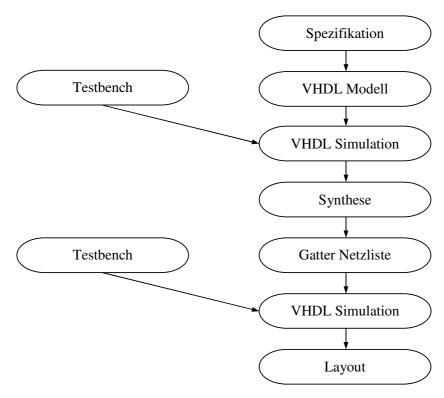

Die Entwicklung wird auf mehreren Phasen aufgeteilt. Ein Zusammenhang der Phasen wird in der Abbildung 2 dargestellt. Nach der Spezifikation (Funktion und Zeitverhalten) wird ein synthesegerechtes VHDL-Modell erstellt (eventuell über ein Modell auf Verhaltensebene). Dieses kann nun simuliert und damit auf Richtigkeit der Funktion geprüft werden. Zeigt das Modell das gewünschte Verhalten, so kann die VHDL Beschreibung synthetisiert werden. Dabei sucht ein Synthese-Werkzeug aus einer anzugebenden ASIC Bibliothek die entsprechenden Gatter und Flip-Flops heraus, um die Beschreibung nachzubilden. Wesentlich bei diesem so genannten Synthesevorgang ist, dass die Summe der Gatterlaufzeiten der gewählten Gatter auf den längsten Pfaden (von jedem Flip-Flop Ausgang bis zum nächsten Flip-Flop Eingang) kleiner als die Taktperiode ist. Sobald das Modell durch bestimmte Elemente einer ASIC Bibliothek dargestellt ist, kann eine Simulation auf Gatterebene durchgeführt werden. Erst jetzt treten Gatter- und Leitungsverzögerungen bei den einzelnen Signalen auf. Die einzelnen Gatter können als Verzögerung behaftete VHDL-Modelle beschrieben werden. Für die Leitungsverzögerungen werden Schätzwerte berechnet (die tatsächlichen Werte stehen erst nach dem Layout zur Verfügung). Jetzt muss nochmals geprüft werden, ob die Schaltung das vorgegebene Zeitverhalten der Spezifikation einhält.

Abbildung 2 – ASIC Design Flow

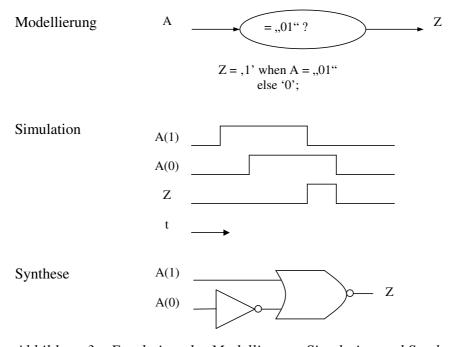

In der Abbildung 3 sind die Ergebnisse der Modellierung, der Simulation und der Synthese dargestellt. Die Modellierung wird meistens mit einem Texteditor realisiert. Durch die Simulation werden die Signalabläufe in einer grafischen Form dargestellt. Nach der Synthese entsteht eine Gatter und Flip-Flop Schaltung.

Abbildung 3 – Ergebnisse der Modellierung, Simulation und Synthese

# 1.4 Testbench-Strukturen

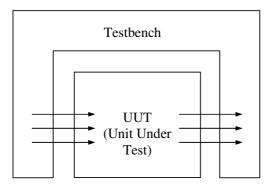

In dem derzeit angewandten Entwicklungsablauf, wird das ASIC in eine Testumgebung eingebaut. Die Testumgebung wird auch Testbench genannt. Die Komplexität des entwickelnden ASICs wirkt sich direkt auf die Komplexität der Testbench aus. Üblicherweise kann der ASIC selbst in Funktionsblöcke unterteilt werden, wobei in der ersten Testphase die Funktion der einzelnen Teile überprüft wird. In weiterer Folge werden die Blöcke miteinander verbunden und getestet. Zum Schluss wird die Überprüfung des gesamten ASIC vorgenommen. Normalerweise benötigt jede Testphase eine eigene Testbench.

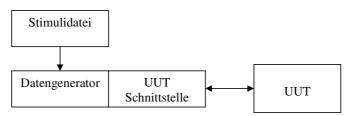

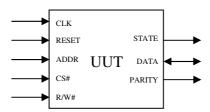

Das zu testende ASIC wird auch UUT (Unit Under Test) genannt. Das Zusammenspiel der Testbench mit UUT wird in der Abbildung 4 dargestellt.

Abbildung 4 – Zusammenspiel der Testbench mit der UUT

Die Testbench ist mit den Eingängen und Ausgängen der UUT verbunden, generiert verschiedene Testsignale an den Eingängen der UUT und bewertet die Reaktion des Designs. Um Verständnisprobleme aufdecken zu können, sollte die Testbench von anderen Entwicklern erstellt werden, als das ASIC selbst. Der Entwickler einer solchen Testbench muss sich also sehr genau mit der zu erwarteten Funktion des ASICs auseinandersetzen, um möglichst realistische Szenarien zu erstellen und alle wichtigen Funktionen auch auszutesten. Der Aufwand für eine solche Testumgebung ist daher bei komplexeren ASICs sehr hoch und erreicht in vielen Fällen den zeitlichen Aufwand, der zur Erstellung des gesamten ASIC Designs notwendig war. Eine Garantie, dass ein so getestetes ASIC später seinen Dienst fehlerfrei ausführt, gibt es nicht. Immer wieder kommt es vor, dass bestimmte Kombinationen nicht in der Testbench berücksichtigt waren. Dies kann zu langwieriger Fehlersuche, kostspieligem Redesign und Verzögerungen bei der Produktfertigstellung führen.

Die Testbench-Strukturen können in zwei Gruppen gegliedert werden: in die herstellerabhängigen Simulationswerkzeuge mit Testbench Funktionalität und in die VHDL Testbench-Strukturen.

Die Simulationswerkzeuge bieten oft die Funktionalität an, womit die ASIC Entwicklungen getestet werden können. Durch die Simulator Befehle können gezielt die Signalwerte gesetzt werden. Die Möglichkeiten sind meistens begrenzt. Die Erweiterung der Funktionalität ist vom Hersteller abhängig. Durch den Austausch der Simulationswerkzeuge können die erfassten Stimulidaten nicht mehr verwendet werden.

Die VHDL Testbench-Strukturen können unterschiedliche Komplexitätsstufen erreichen. Es fängt an mit einem einfachen VHDL-Code um endet mit komplexen VHDL Bibliotheken. Die Testbench Funktionalität deckt dementsprechend sehr begrenzt oder sehr umfangreich die Anforderungen einer komplexen Simulation. Ein Nachteil der komplexen Testbench-Strukturen ist, dass sie viel Rechnerleistung benötigen. Aber mit geeigneter Hardware und Software ist es möglich die gewünschte Leistung zu erzielen. Ein weiterer wichtiger Aspekt der Testbench-Strukturen ist der Aufbau der Stimulibefehle. Die leicht lesbaren Stimulibefehle müssen meistens von Testbench stark verändert werden, bevor an die Eingänge der UUT geführt werden. Die Stimulibefehle, die ohne Veränderungen an die Eingänge der UUT geführt werden können, sind kaum lesbar. Die Entscheidung, welche Stimulibefehle verwendet werden, liegt bei dem Testbench Entwickler. Wenn weniger Rechnerleistung zur Verfügung steht und die Stimulibefehle nachträglich mit einem Texteditor nicht verändert werden sollen, dann sind die Stimulidaten nahe Stimulibefehle zu empfehlen.

Für kleine ASIC Entwicklungen, wie z.B. Prototypen, wird als Testbench ein einfacher VHDL-Code verwendet. Die Funktionalität der Testbench ist nur auf die Weitergabe der Eingabedaten, auch Stimulidaten genannt, an die UUT begrenzt. Die Stimulidaten werden direkt in der Testbench angegeben. Ein Nachteil solcher Testbench ist, dass nach jeder Änderung der Stimulidaten, der VHDL-Code neu übersetzt werden soll. Der VHDL-Code kann sehr groß werden, der Überblick über die Stimulidaten geht verloren. Die Wiederverwendbarkeit der Testbench ist kaum gegeben.

Durch die Auslagerung der Stimulidaten in externe Dateien, kann der VHDL-Code von Stimulidaten befreit werden. Die Stimulidaten werden in eine Textdatei gespeichert und beinhalten alle Werte, die für die Versorgung der UUT notwendig sind. VHDL bietet die Funktionalität um Dateien zu lesen und zu schreiben. Damit ist es möglich, ein Datengenerator Modul zu realisieren, womit die Stimulidaten aus den Dateien sequenziell gelesen und die UUT weitergegeben werden. Der Datengenerator wird über eine Schnittstelle mit der UUT verknüpft und liefert die Bitmustern an die Eingänge der UUT. Da die Stimulidaten in einem binären Format dargestellt sind, sind die Stimulidateien schwer zu lesen. Eine solche Testbench-Struktur ist in der Abbildung 5 dargestellt.

Abbildung 5 – Einfache Testbench-Struktur

Durch die Einführung von Pseudobefehlen können die binären Stimulidaten in einer lesbaren Form dargestellt werden. Um die Pseudobefehle interpretieren zu können wird ein weiteres Modul benötigt. Das Modul interpretiert die Pseudobefehle und generiert die notwendigen binären Stimulidaten. Ein solches Modul zu realisieren ist sehr schwierig und für andere

Applikationen ist nicht wieder verwendbar. Nach der Realisierung oder nach Änderungen soll neu übersetzt werden.

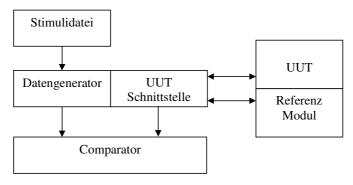

Eine Weiterentwicklung der Testbench ist die Einführung eines Comparators. Die UUT Ausgangsignale und die Referenzdaten werden den Comparator weitergegeben. Die Referenzdaten können entweder aus einer Datei gelesen werden oder von einem Referenzmodul erstellt werden. Wenn die Referenzdaten in eine Datei gespeichert sind, sollen diese vor dem Testlauf berechnet und erfasst werden. Das ist oft nicht einfach. Wenn ein Referenzmodul verwendet wird, dann soll die UUT nachgebaut werden. Das ist doppelter Entwicklungsaufwand. Der Comparator liefert eine Reportdatei, die mit verschiedenen Werkzeugen ausgewertet werden kann. Der Datengenerator, die UUT Schnittstelle, das Referenzmodul und der Comparator sind in VHDL realisiert und müssen nach der Realisierung oder nach Änderungen neu übersetzt werden.

Abbildung 6 – Testbench-Struktur mit Comparator

## 1.5 Related Works

## 1.5.1 Kommerzielle Werkzeuge

Es gibt am Markt bereits Firmen, die kommerziellen Werkzeuge für ASIC-Tests anbieten. Diese werden in den folgenden Abschnitten beschrieben. Sie sind meistens sehr teuer oder sie beschränken sich auf einem Simulationswerkzeug oder auf ein Betriebssystem.

#### Full Circuit Ltd - VHDL TestBench Tool

Die Firma "Full Circuit Ltd" entwickelt Software und Hardware-Lösungen für die Bahn. Unter anderem hat das Programm "VHDL TestBench Tool" entwickelt. "VHDL TestBench Tool" ist eine Microsoft Excel Anwendung. Diese besteht aus einer Microsoft Excel Dokumentvorlage, einem Microsoft Excel Makro und einem VHDL-Template. Das Werkzeug ermöglicht eine benutzerfreundliche Eingabe und Darstellung der Signalwerte. Die graphische Darstellung der Signale wird von Microsoft Excel unterstützt. Bussignale können nicht dargestellt werden. Ein wesentlicher Vorteil ist, dass die Regeln der Testdaten Definitionen, durch Excel Formeln unterstützt werden können. Die Angabe von komplexen Zyklendefinitionen ist ebenfalls sehr leicht durchführbar. Das Werkzeug generiert auf Grund der definierten Ein- und Ausgangssignalen einen VHDL-Code. Solange keine

Signaldefinition Änderungen gemacht werden, wird der Code nur einmal übersetzt. Die erfassten Testdaten werden in eine Datei gespeichert, die bei der Durchführung des Tests, aus der Datei gelesen werden. Aufgrund seiner Microsoft Excel Abhängigkeit ist es nur unter Microsoft Windows verfügbar. Eine detailliertere Beschreibung ist in [Ful04] angeführt.

#### **SOC** central – TestWizard

Die Firma SOC Central mit den Produkten TestWizard und SimCluster bieten dem Benutzer eine Testbench Umgebung, womit VHDL, Verilog oder C Testbench erstellt werden können. Unter anderem werden Eigenschaften wie Zufallsdatengenerierung, benutzerdefinierte Strukturen und Listen, funktionale Domain Analyse, usw. angeboten. Es ist nur für die Betriebssysteme Solaris und Linux verfügbar. Eine detailliertere Beschreibung ist in [SOC04] angeführt.

### **Mentor Graphics – Seamless**

Die Firma Mentor Graphics entwickelt Lösungen für automatisiertes Elektronik Design. Das Produkt Seamless bietet eine Verifikation der Hardware und Software gleichzeitig. Bevor ein Hardware-Prototyp überhaupt entstanden ist, kann das Werkzeug die Hardware simulieren und damit den Zusammenspiel von Hardware und Software testen. Damit ist es möglich die Hardware und Software Schnittstellen Fehler frühzeitig festzustellen und zu isolieren. Die Fehler in dieser Entwicklungsphase zu erkennen reduziert die Kosten, die Entwicklungszeit, die Anzahl der Prototypen und die Risiken der Entwicklung.

Software und Hardware werden oft von unterschiedlichen Entwicklern realisiert. Deswegen werden oft Performanceprobleme bei der Interkommunikation zwischen der Software und Hardware auftreten. Seamless unterstützt die Erkennung der Performanceprobleme.

Zum Zeitpunkt des ASIC-Tests müssen die Software und ein voll funktionsfähiges Modell des Systems zur Verfügung stehen. Um eine Aussage über die Richtigkeit des entwickelnden Systems zu bekommen, ist es wichtig einen großen Teil der Software bereits fertig zu haben. Aber je größer der Software, desto langsamer die Simulation. Um die Simulation zu beschleunigen, wurde für die Abarbeitung der Software ein ISS (Instruktion-Set-Simulator) entwickelt. Der ISS interpretiert sehr schnell die Befehle und steuert damit die Hardware. Die Hardware wird über das Bus-Funktional-Modell angekoppelt. Das simuliert das elektrische Verhalten des Prozessors. Jedes mal, wenn der ISS einen neuen Befehl bearbeitet, sendet der ISS einen Befehl an das Bus-Funktional-Modell. Dieses setzt den Befehl in einen elektrischen Signal um und liefert die aus der Hardware gelesenen Daten an den ISS zurück. Jede Signaländerung in der Schaltung wird vom Simulator verfolgt. Die Verzögerungszeiten der Bausteine und der Leitungen werden auch berücksichtigt.

Seamless ist ein sehr mächtiges Werkzeug, aber die benötigte Hardware und Software Ressourcen sind komplex und teuer. Nur große Firmen können sich das leisten. Eine detailliertere Beschreibung ist in [Men04] angeführt.

# 1.5.2 Freie Werkzeuge

Die freien Werkzeuge für ASIC-Tests sind meistens Werkzeuge von Universitäten, die sehr an Universitätsbedürfnisse angepasst sind. Diese werden in den folgenden Abschnitten beschrieben.

#### TU Wien - Hofstätter Testbench

Im Rahmen einer Diplomarbeit [Hof97] an der TU Wien Institut der Computertechnik hat Hr. DI. Michael Hofstätter im Jahre 1997 bereits ein Testbench Konzept entwickelt und sämtliche VHDL Bibliotheken realisiert, womit die VHDL Module testen können. Die Testbench ermöglicht mit einem geringen Entwicklungsaufwand, Testdaten aus einer Stimulidatei der UUT zuzufügen und die Ergebnisse auszuwerten.

Die Testbench besteht aus Testbench-Kontrollblock, ASIC Specific Block, Datengenerator, Takt Generator, Datenbewertung Modul und Referenzmodul. Der Testbench-Kontrollblock steuert sämtliche Module der Testbench. Die Steuerungsbefehle sind in einer Kommandodatei gespeichert und sie werden sequenziell abgearbeitet. Der ASIC Specific Block ist das einzige Modul, das für jede Testbench neu erstellt werden soll. In diesem Modul werden die ASIC spezifischen Befehle definiert. Der Datengenerator generiert die Stimulidaten und das Timing. Er liest die Stimulibefehle aus einer Datei und versorgt die Eingangssignale der UUT. Das Datenbewertung Modul vergleicht die Istwerte mit den Sollwerten und erstellt eine Reportdatei. Die Auswertung der Reportdatei wird mit zusätzlichen Werkzeugen realisiert. Das Referenzmodul simuliert die gleiche Funktionalität wie die UUT. Dadurch ist es möglich im Datenbewertungsmodul die Istwerte mit den Sollwerten zu vergleichen.

Die Testbench ist sehr mächtig und benutzerfreundlich. VHDL-Kenntnisse sind jedoch notwendig. Ein sinnvoller Einsatz des Konzeptes ist ab einem mittelgroßen Projekt aufwärts zu empfehlen.

## Universität Erlangen Nürnberg – VHDL Testbench-Generator

Die Universität Erlangen Nürnberg Lehrstuhl für Rechnergestützten Schaltungsentwurf hat einen Online VHDL Testbench-Generator in der Programmiersprache C entwickelt. Um eine Testbench zu generieren ist es ein korrekter VHDL Entity Code des überprüfenden Systems notwendig. Das Entity Code wird in eine Web Maske eingegeben und nach einer kurzen Zeit wird die Testbench angezeigt. Der wesentliche Nachteil dieser Lösung ist, das nur das VHDL-Code generiert wird und keine Testdaten. Eine detailliertere Beschreibung ist in [Erl04] angeführt.

#### **Doulos – VHDL Testbench**

Die Firma Doulos hat einen Online Testbench-Generator in der Programmiersprache Perl entwickelt. Der VHDL-Code wird in eine Web Maske eingegeben und nach einer kurze Zeit wird die Testbench angezeigt. Der wesentliche Nachteil dieser Lösung ist, das nur der VHDL-Code generiert wird und keine Testdaten. Eine detailliertere Beschreibung ist in [Dou04]

angeführt.

# 1.5.3 Vergleich der Werkzeuge

Die erwähnten Werkzeuge können in zwei Gruppen klassifiziert werden:

- 1. Komplexe Werkzeuge: die sehr viel Funktionalität abdecken können und damit das Testen sehr stark unterstützen. Die Nachteile solcher Werkzeuge sind die hohen Kosten und die Komplexität des Einsatzes. Die Einarbeitungszeit ist hoch, die benötigten Schnittstellen sind komplex. Die Werkzeuge sind meistens auf die Bedürfnisse von Chipherstellen abgeschnitten und deswegen sind für einen allgemeinen Einsatz nicht geeignet.

- 2. **Primitive Werkzeuge:** die schon bei mittelgroßen Anwendungen die Anforderungen nicht mehr erfüllen können.

Folgende Tabelle liefert einen Überblick über einigen wichtigen Merkmalen der Werkzeuge:

| Werkzeug             | Vorteile                              | Nachteile                                    |

|----------------------|---------------------------------------|----------------------------------------------|

| Full Circuit Ltd:    | - Eingabe und Visualisierung in       | - Betriebssystem Microsoft Windows           |

| VHDL TestBench Tool  | Microsoft Excel                       |                                              |

|                      | - Formel- und Zyklen- Definitionen    |                                              |

|                      | werden unterstützt                    |                                              |

| SOC central:         | - Zufallsdatengenerierung             | - Betriebssystem Sun Solaris und Linux       |

| TestWizard           | - Benutzerdefinierte Strukturen und   | - Hardware und Software Ressourcen sind      |

|                      | Listen                                | komplex und teuer                            |

|                      | - funktionale Domain Analyse          |                                              |

| Mentor Graphics:     | - Software und Hardware Zusammenspiel | - Testbar nur mit einer fertigen Software    |

| Seamless             | testbar                               | und ein voll funktionsfähiges Modell des     |

|                      | - Performanceanalyse                  | Systems                                      |

|                      |                                       | - Hardware und Software Ressourcen sind      |

|                      |                                       | komplex und teuer                            |

| TU Wien:             | - Sehr mächtig, jahrelange Testbench- | - Hoher Initialaufwand                       |

| Hofstätter Testbench | Erfahrung wurde eingebracht           | - VHDL Kenntnisse notwendig                  |

|                      | - Leicht lesbare Testroutinen         |                                              |

|                      | - Skalierbar                          |                                              |

| Universität Erlangen | - Das Werkzeug wird im Web Angeboten, | - Generiert nur die Hülle einer rudimentären |

| Nürnberg:            | deshalb keine lokale Installation ist | Testbench                                    |

| VHDL Testbench-      | notwendig                             |                                              |

| Generator            |                                       |                                              |

| Doulos:              | - Das Werkzeug wird im Web Angeboten, | - Generiert nur die Hülle einer rudimentären |

| VHDL Testbench       | deshalb keine lokale Installation ist | Testbench                                    |

|                      | notwendig                             |                                              |

# 1.6 Aufgabenstellung

Die Überprüfung von einem VHDL-Modell stellt einen nicht zu unterschätzenden Anteil der gesamten Entwicklungszeit dar. Die Unterstützung der Simulationswerkzeuge ist in den meisten Fällen nicht ausreichend. Deshalb wird eine geeignete Testumgebung benötigt. Die Testumgebung hängt sehr stark vom entwickelnden ASIC ab. Aber es gibt immer eine ähnliche Entwicklungsrichtlinie der Testumgebung. Es wird immer mit Stimulidaten gearbeitet, diese Stimulidaten werden an den testenden Komponenten weitergeleitet, die Ergebnisse der testenden Komponenten werden mit den Referenzdaten verglichen und ausgewertet. Die Stimulidaten werden oft mit einem Texteditor bearbeitet und in einer Textdatei abgespeichert. Wenn sehr viele Stimulidaten erfasst werden, wird die Textdatei unübersichtlich. Wenn noch zusätzlich die Schnittstellen zu den überprüfenden Komponenten geändert werden, müssen diese Änderungen auch im Testbench berücksichtigt werden. Aber damit werden die Stimulidaten inkonsistent und werden sehr wahrscheinlich auch die Verbindungen mit Komponenten inkonsistent.

Der Schwerpunkt dieser Diplomarbeit ist ein Werkzeug zu realisieren, womit das Erstellen, Modifizieren und Dokumentieren der Testbench und der Stimulidaten unterstützt werden können. Das Werkzeug wird Testbench-Generator genannt. Der modulare Aufbau des Testbench-Generators, sowie eine Sammlung von APIs (Application Programming Interface) sollen die Weiterentwicklung des Werkzeuges ermöglichen. Die genaue Spezifikation und das Konzept sind im Kapitel 2 beschrieben.

# 2 Testbench-Generator Design

Ausgehend von eine Sammlung Überlegungen, die die Entwicklung einer Testbench und die Erfassung der Stimulidaten erleichtern, und zwei Testbench-Strukturen, präsentiert in den nächsten Abschnitten, wurde das Design des Testbench-Generators realisiert. Das Design beschreibt das Datenmodell und die Architektur des Testbench-Generators.

# 2.1 Testbench-Generator Spezifikation

Die Funktionalität des Testbench-Generators kann grundsätzlich in Eingabe- und Ausgabefunktionalität gegliedert werden.

Die Eingabefunktionalität ist zuständig für die Eingabe aller Daten, die von einer Testbench benötigt werden. Die Eingabe erfolgt über ein grafisches Interface, wobei folgende Merkmale als Schwerpunkte behandelt werden:

- 1. Erstellung von Signalverläufen

- 2. Überprüfung der zeitlichen Relationen zwischen den einzelnen Signalverläufen

- 3. Zusammenfassung aller Signale zu Befehlen

- 4. Aneinanderkettung von mehreren Befehlen zu einer Testroutine

- 5. Nachträgliches Modifizieren, Einfügen, Löschen sämtlicher konfigurierbarer Parameter

Die Ausgabefunktionalität ist für die Generierung der Dateien zuständig. Die generierten Dateien sind die HDL Programme, die Stimulidateien, die Konfigurationsdateien und die Dokumentationen. Folgende Merkmale werden als Schwerpunkte behandelt:

- 1. VHDL Testbench + Patternfile

- 2. Verilog Testbench + Patternfile

- 3. ASCII Ausgabe der Befehlssequenzen

- 4. Programmsequenzen automatisch dokumentieren

- 5. LATEX Macro der Signalverläufe

# 2.1.1 Eingabefunktionalität

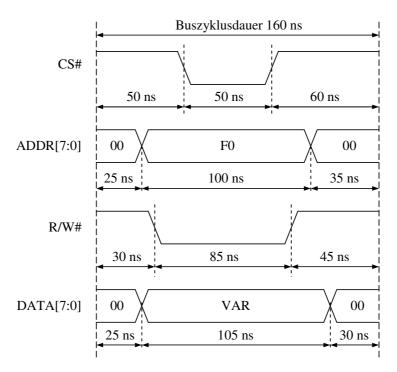

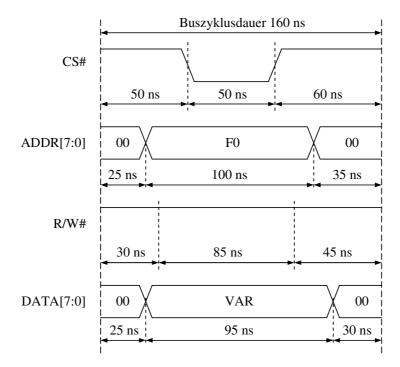

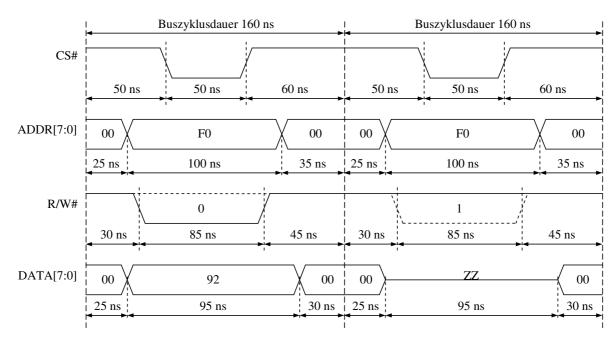

#### **Signal definition**

Die Eingabeprozeduren unterstützen die Erfassung der Signalen oder der Signalbussen. Zur Definition eines Signals oder eines Signalbusses werden im Allgemeinen mehrere Parameter benötigt: Signalname, Signalanzahl, Zykluszeiten, Buszyklusdauer, Default-Werte für inaktive Zustände, usw. Der Signalname bezeichnet das zu charakterisierende Signal (z.B. CS#, DATA, usw.). Die Signalanzahl wird unterschieden, ob es sich um eine einzige Leitung

oder um einen Bus handelt und aus wie vielen letzterer besteht. Mit Hilfe der Zykluszeiten werden alle Zeitpunkte innerhalb eines Buszyklusses, zu denen ein Pegelwechsel der betrachteten Leitung erfolgt, genau festgelegt. Anhand dieser Zeiten wird definiert, wann ein Signal aktiv, bzw. inaktiv ist. Die Zykluszeiten aller Signale müssen sich jeweils in Summe genau zur Dauer des Buszyklusses ergänzen. Jedes Signal kann individuell einen oder mehrere Zeitpunkte aufweisen, zu denen der Wert bzw. Pegel des Signals in ein Ausgangsfile protokolliert wird. Dadurch soll der automatische Vergleich von Patternfiles zu verschiedenen Zeitpunkten in einem Designprozess ermöglicht werden. Weiters sind während der Dauer eines Buszyklusses die einzelnen Signale nur zu definierten Zeiten gültig. In den restlichen so genannten inaktiven Zeitpunkten, nimmt das jeweilige Signal einen definierten Default-Pegel an der für die restliche Betrachtung und Handhabung fixiert wird. Der aktive Teil des jeweiligen Signals wird später entweder bei der Befehlsdefinition (z.B. Chip Select Werte, Byte Enable Pegel, usw.) oder aber gar erst bei der Aneinanderkettung der einzelnen Befehle als Parameter (z.B. DATA, R/W, usw.) festgelegt. Innerhalb einer Buszyklusdauer kann ein Befehl auch mehrmals hintereinander einen aktiven Zustand annehmen. In diesem Fall sind für dieses Signal mehrere Variablen zur Beschreibung nötig.

#### **Befehlsdefinition**

Für jeden einzelnen zu definierenden Befehl müssen für die Dauer eines Befehlszyklus jeweils alle Signale getrieben werden. Wird z.B. der Akkumulator-Register einer zu testenden Unit beschrieben oder gelesen, so kann hierfür ein Befehl ACC VAR1, VAR2 definiert werden. Für diesen Befehl werden die Adresssignale während des aktiven Bereichs auf den fixen Wert des Akkumulator Registers eingestellt. Weiters wird das Chip Select Signal zum aktiven Zeitpunkt fix auf logisch Null gelegt. Das Label ACC dient zur Kennzeichnung des Befehls und muss sich von allen anderen Befehlen in der Bezeichnung unterscheiden. Der Parameter VAR1 könnte z.B. den aktiven Zustand der R/W# Signalleitung aufnehmen und würde erst später bei der Befehlsaneinanderkettung festgelegt werden. Ebenso könnte VAR2 die entsprechende Variable für den aktiven Teil der Daten Signalleitungen darstellen. Für den Befehl ACC VAR1, VAR2 würde somit folgende Festlegung entstehen:

| Signal | Wert  |

|--------|-------|

| CS#    | 0     |

| ADDR   | 0x0F0 |

| R/W#   | VAR1  |

| DATA   | VAR2  |

Tabelle 1 – Befehl ACC

Zu diesem Zeitpunkt ist bereits keinerlei Information über das zeitliche Signalverhalten mehr vorhanden. Dies wird gänzlich von der unterliegenden Signaldefinitionsschicht übernommen.

### Befehlsaneinanderkettung zu einer Testroutine

Die zuvor definierten Befehle können in dieser Schicht zu einer Testroutine aneinandergefügt werden. Erst jetzt werden die gesamten Stimulidaten für die Stimulidatei, die bereits

basierend auf der Signaldefinition erstellt wurden, generiert. Die Stimulidatei besteht aus aneinander gefügten Stimulidaten.

### Modifikationsmöglichkeiten

Um die Entwurfsgestaltung und Handhabung des Testbench-Generators möglichst komfortabel zu gestallten, sind zahlreiche Möglichkeiten zum nachträglichen Editieren, Einfügen und Löschen von Befehlen, Befehlssequenzen und einzelnen Signalparametern vorzusehen. Hierbei wird vor allem die Modifikation in einer Abstraktionsschicht die entsprechenden Auswirkungen in den anderen Schichten erzeugt. Wird z.B. die Anzahl der Signalbits einer Leitung bei der Signaldefinition geändert, so soll dies auch Auswirkungen in der Befehlsdefinition- und Testroutinen- Schicht bewirken.

# 2.1.2 Ausgabefunktionalität

### VHDL u. VERILOG Testprogramm und Patternfile

Aus den eingegebenen Daten erstellt der Testbench-Generator wahlweise entweder ein VHDL oder ein VERILOG Testprogramm, das sämtliche Datenoperationen über Dateizugriffe der Stimulidatei (Stimulidaten und Referenzdaten) durchführt. Das Portmapping wird vom Testbench-Generator unterstützt. Sowohl das VHDL Testprogramm als auch das VERILOG Testprogramm werden mit denselben Stimulidateien versorgt.

## Latex Macro der Signalverläufe

Um das Timing des Buszyklusses gleich automatisch dokumentieren zu können, wird der Buszyklus als Latex Macro abgespeichert. Dadurch werden die Signalverläufe direkt als Waveforms dargestellt und können somit leichter verifiziert werden.

#### **ASCII Ausgabe der Befehlssequenzen**

Während eines Testlaufs werden in der Regel die simulierten Waveforms manuell auf ihre Funktionalität kontrolliert. Um hierfür einen Überblick gewährleisten zu können, werden die angelegten Testsequenzen mitdokumentiert. Die Befehlsfolge wird ASCII mäßig exportiert.

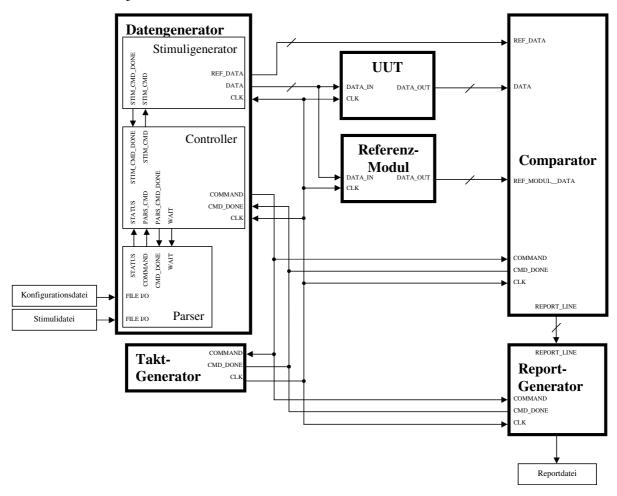

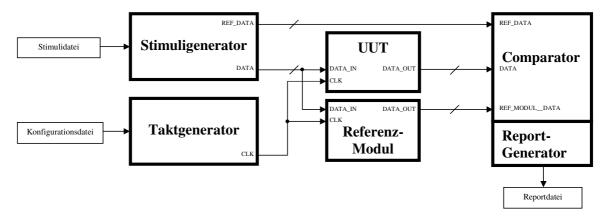

## 2.2 Testbench-Struktur mit Controller

In diesem Abschnitt präsentierte Testbench ist in der Lage sehr komplexe Simulationen durchzuführen. Das Blockschaltbild der Testbench ist in der Abbildung 7 präsentiert und besteht aus folgenden Modulen:

- 1. **Parser:** parst die Konfigurationsdatei und Stimulidatei.

- 2. **Controller:** steuert die Testbench durch die Steuerungsbefehlen.

- 3. **Stimuligenerator:** stellt die Stimulidaten der UUT und des Referenzmoduls, bzw. die Referenzdaten dem Comparator zur Verfügung.

- 4. **Taktgenerator:** liefert den Systemtakt.

- 5. Comparator: wertet die Ausgabedaten der UUT aufgrund der Referenzdaten aus.

- 6. **Reportgenerator:** speichert die Simulationsergebnisse in eine Textdatei ab.

- 7. **UUT:** der zu testenden Einheit.

- 8. **Referenzmodul:** liefert die Solldaten.

Die Testbench Module sind parametrisierbar. Ein Parameter ist z.B. die Periode des Taktgenerators. Diese werden bei der Initialisierung der Testbench gesetzt, wobei bestimmte Parameter können jeder Zeit mitverändert werden.

Abbildung 7 – Testbench-Struktur mit einem Controller

Der Datengenerator hat zwei wesentliche Aufgaben. Erstens die Initialisierung und die Steuerung der Testbench Modulen und zweitens die Versorgung der UUT und des Referenzmoduls mit Stimulidaten, bzw. die Versorgung des Comparators mit den zu erwartenden Werten. Die Initialisierung der Module erfolgt zu Beginn der Simulation anhand der Konfigurationsdatei. Der Datengenerator liest die Steuerungsbefehle aus der Konfigurationsdatei und leitet die Befehle über die COMMAND Leitung an den beteiligten Modulen weiter. Die erfolgreiche Übernahme der Werte, wird über die CMD\_DONE Leitung bestätigt. Nach der Initialisierung der Testbench, wird die Simulation durchgeführt. Die Module können auch während der Simulation neu konfiguriert werden. In diesem Fall sind Steuerungsbefehle zwischen den Stimulibefehlen eingetragen. die Sobald

Steuerungsbefehl in den Stimulidaten vorkommt, wird ein Steuerungsvorgang eingeleitet. Die Werte werden über die COMMAND Leitung an den beteiligten Modulen weitergeleitet und über die CMD\_DONE Leitung wird eine Bestätigung abgeholt. Die Versorgung der UUT und des Referenzmoduls mit den Stimulidaten, bzw. der Comparator mit den Referenzdaten, werden anhand der Stimulibefehle aus der Stimulidatei durchgeführt. Die Stimulibefehle werden aus der Stimulidatei gelesen, in Stimulidaten, bzw. in den Referenzdaten konvertiert und anschließend an die DATA, bzw. REF\_DATA Leitungen geführt.

Der Comparator übernimmt die Ausgabedaten der UUT und des Referenzmoduls, bzw. die Referenzdaten vom Datengenerator. Die Werte werden verglichen und an den Reportgenerator weitergeleitet. Der Reportgenerator überprüft seine Eingänge und erfasst die Daten in eine Reportdatei. Welche Daten mitgeschrieben werden, wird durch den Reportgenerator spezifischen Parameter gesteuert. Der Taktgenerator liefert den Takt an allen Modulen. Dieser wird ebenfalls über die COMMAND Leitung gesteuert. Die UUT, bzw. das Referenzmodul werden nicht beschrieben. Sie sind die Resultate der ASIC Entwicklungen und haben eine klar definierte Schnittstelle nach Außen.

[Hof97] beschreibt eine ähnliche Testbench-Struktur und kann für die Erweitung der Testbench-Struktur paar Ideen liefern.

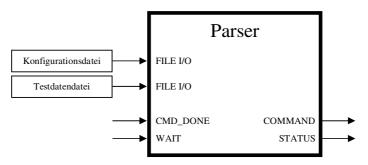

#### 2.2.1 Parser

Der Parser hat die Aufgabe die Befehle aus der Konfigurationsdatei und Stimulidatei zu lesen und den Controller zur Verfügung stellen. Die Konfigurationsdatei beinhaltet die Initialisierungsbefehle, womit die Module, inklusiv der Parser, am Anfang der Simulation initialisiert werden. Die Stimulidatei beinhaltet die Stimulidaten der UUT, des Referenzmoduls, die Referenzdaten des Comparators und weitere Steuerungsbefehle. Die zwei Dateien sind Textdateien und können mit herkömmlichen Texteditoren bearbeitet werden.

Abbildung 8 – Parser Modul

Die Testbench wird mit den Steuerungsbefehlen aus der Konfigurationsdatei initialisiert. Nach der Initialisierung der Testbench werden die Befehle aus der Stimulidatei sequenziell eingelesen. Die eingelesenen Befehle werden über die COMMAND Leitung als Zeichenkette an den Controller weitergeleitet. Auf der Leitung CMD\_DONE wird die erfolgreiche Ausführung der Befehle vom Controller signalisiert. Das zeitliche Verhalten wird somit, bis auf eine Ausnahme, durch die CMD\_DONE Leitung bestimmt. Als Ausnahme gilt die WAIT

Leitung, welche dazu verwendet werden kann, den Parser vom Controller vorübergehend anzuhalten. Die Zustände des Parsers werden über die STATUS Leitung dem Controller zur Verfügung gestellt.

#### **Schnittstelle**

Die Schnittstelle des Parsers ist in der Abbildung 8 dargestellt und besteht aus folgenden Leitungen:

- COMMAND: ist von Typ String und dient zur Übermittlung der Befehle als Zeichenkette an den Controller. Die Zeichenketten bestehen aus dem Befehlswort und weiteren Parametern. Die Befehle sind modulspezifisch und werden bei der Beschreibung jedes Moduls spezifiziert.

- 2. **CMD\_DONE:** ist von Typ Std\_Logic. Wenn der Befehl vom Controller übernommen wurde, wird vom Controller über diese Leitung ein Impuls erzeugt. Damit signalisiert dieser, dass die COMMAND Leitung mit dem nächsten Befehl angelegt werden kann.

- 3. WAIT: ist von Typ Boolean. Wenn auf dieser Leitung der Wert TRUE anliegt, wird mit den Parsen so lange gewartet, bis auf diese Leitung vom Controller wieder den Wert FALSE gesetzt wird. Mit dieser Leitung wird signalisiert, dass der Controller intern beschäftigt ist und keine neue Befehle übernehmen kann. Dies kann z.B. dann auftreten, wenn einem Stimulibefehl ein Signalwertebereich zugewiesen wurde, und diesen Wertebereich der Stimuligenerator zuerst auflösen muss, dann die einzelnen Werte dem Stimulibefehl zuweisen und die Stimulibefehle schließlich ausführen muss.

- 4. **STATUS:** ist von Typ String und signalisiert den Zustand des Parsers. Je nach dem welchen Zustand der Parser annimmt, wird der Controller seine Tätigkeiten durchführen. Wenn z.B. der Parser in der Initialisierungsphase ist, wird der Controller warten, bis der Parser fertig ist. Folgende Zustände kann der Parser annehmen:

- a. I: Die Initialisierung des Parsers wird durchgeführt.

- b. C: Ein Befehl zum Verarbeiten liegt an der COMMAND Leitung.

- c. E *Fehlermeldung*: Ein Parserfehler ist aufgetreten. Die Fehlermeldung wird auch mitgeliefert.

- d. R: Die Bearbeitung der Stimulidatei ist abgeschlossen.

#### Konfigurationsdatei

In der Konfigurationsdatei werden die Initialisierungsbefehle der Module abgespeichert. Sind modulspezifische Befehle, also Befehle die nicht an die UUT, bzw. an das Referenzmodul bestimmt sind, sondern an den anderen Testbench Modulen. Welche Befehle in der Konfigurationsdatei vorkommen dürfen und wie die Befehle ausschauen, werden in der

Beschreibung der einzelnen Module definiert.

#### Stimulidatei

Die Stimulidatei beinhaltet die Befehle, die bei der Simulation ausgeführt werden sollen. Die Steuerungsbefehle und die Stimulibefehle werden gemischt angewendet. Dadurch ist es möglich in der Simulationsphase bestimmte Testbench Parameter zu verändern und modifizierte Simulationsbedingungen zu erzeugen. Welche Steuerungsbefehle in der Stimulidatei vorkommen dürfen und wie die Befehle ausschauen, werden in der Beschreibung der einzelnen Module definiert. Die Stimulibefehle beinhalten die Informationen, die für die Versorgung der Eingangssignale der UUT, bzw. des Referenzmoduls notwendig sind.

#### **Parameter**

Der Parser kann durch den folgenden Parameter konfiguriert werden:

- 1. KONFIGURATIONSDATEI string: Name der Konfigurationsdatei.

- 2. STIMULIDATEI string: Name der Stimulidatei.

#### **Befehle**

Der Steuerungsbefehl des Parsers setzt den STIMULIDATEI Parameter des Parsers. Dieser kann auch während der Simulation aufgerufen werden.

Syntax:

```

command ::= PARSER STIMULIDATEI string

```

#### **Fehlerbehandlung**

Wenn im Parser ein Fehler auftritt, bricht mit dem Parsen ab und setzt den STATUS Leitung auf "E". Folgende bekannte Fehler können auftreten:

- 1. **Konfigurationsdatei nicht vorhanden:** wenn die angegebene Konfigurationsdatei nicht im Dateisystem vorhanden ist.

- 2. **Stimulidatei nicht vorhanden:** wenn die angegebene Stimulidatei nicht im Dateisystem vorhanden ist.

- 3. **Konfigurationsdatei mit falschen Format:** wenn die Konfigurationsdatei einen falschen Format hat, bzw. unlesbar ist.

- 4. **Stimulidatei mit falschen Format:** wenn die Stimulidatei einen falschen Format hat, bzw. unlesbar ist.

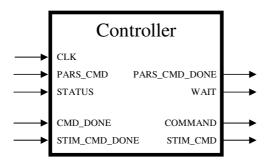

#### 2.2.2 Controller

Der Controller ist für die Steuerung der Testbench zuständig. Dieser unterscheidet zwischen den Steuerungsbefehlen und Stimulibefehlen und leitet sie weiter.

Die Steuerungsbefehle werden über die COMMAND Ausgangsleitung an den adressierten

Testbench Modulen, wie der Taktgenerator, der Comparator oder der Reportgenerator, weitergeleitet. Die Bestätigung von den Modulen, dass die Befehle angenommen wurden, wird über die CMD\_DONE Eingangsleitung gesendet. Da diese Leitung von mehreren Modulen betrieben werden können, ist es sehr wichtig, nach dem Senden der Bestätigung, das aktive Modul von der Leitung abzukoppeln. Der Controller wartet bis auf eine gewisse Zeit auf die Bestätigung. Es kann vorkommen, dass kein Modul den Befehl annimmt und damit wird die Fortsetzung der Befehlsverarbeitung verhindert. Die maximale Wartezeit ist ein Parameter der Controller und er ist jederzeit änderbar.

Die Stimulibefehle werden über die STIM\_CMD Leitung an den Stimuligenerator weitergeleitet. Wenn im Stimulibefehl ein Wertbereich angegeben ist, löst der Controller dieses auf und generiert Stimulibefehle mit Werten aus dem Wertebereich. In diesem Vorgang setzt die WAIT Leitung auf TRUE. Damit benachrichtigt den Parser, dass er keine neuen Befehle übernehmen kann, weil er beschäftigt ist.

Abbildung 9 – Controller Modul

## **Schnittstelle**

Die Schnittstelle des Controllers ist in der Abbildung 9 dargestellt und besteht aus folgenden Leitungen:

- 1. **STATUS:** Über diese Leitung wird der Controller über den Zustand des Parsers informiert. Es gibt vier Parserzustände. "I", wenn der Parser initialisiert wird. In diesem Fall ist der Controller in dem Wartezustand. "C", wenn ein gültiger Befehl am P\_COMMAND Leitung liegt. Der Controller liest den Befehl und verarbeitet ihn. "E", wenn im Parser ein Fehler aufgetreten ist. Der Controller schickt einen neuen Befehl dem Reportgenerator mit der Fehlermeldung. "R", wenn die Abarbeitung der Stimulidatei abgeschlossen ist. In diesem Fall wird der Stimuligenerator gestoppt.

- 2. PARS\_CMD: Diese Leitung ist der Gegenpool der COMMAND Leitung des Parsers. Sie ist vom Typ String und dient zur Übermittlung der Befehle vom Parser. Die Befehle werden als Zeichenkette übermittelt und sie bestehen aus einem Befehlswort und weiteren Parametern. Ein Teil der Befehle sind dem Controller adressiert und sie werden sofort verarbeitet. Die restlichen Befehle werden den adressierten Modulen weitergeleitet.

- 3. PARS\_CMD\_DONE: Diese Leitung vom Typ Std\_Logic ist der Gegenpool der

- CMD\_DONE Leitung des Parsers. Wenn der Controller den Befehl des Parsers übernommen hat, sendet dem Parser eine Bestätigung in Form eines Impulses zurück.

- 4. WAIT: Diese Leitung ist vom Typ Boolean. Wenn auf dieser Leitung der Wert TRUE anliegt, wird mit den Parsen so lange gewartet, bis auf diese Leitung vom Controller wieder den Wert FALSE gesetzt wird. Mit dieser Leitung wird signalisiert, dass der Controller intern beschäftigt ist und keine neue Befehle übernehmen kann.

- 5. **STIM\_CMD:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Stimulibefehle an den Stimuligenerator. Die Befehle werden als Zeichenkette übermittelt und sie bestehen aus einem Befehlswort und weiteren Parametern.

- 6. **STIM\_CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Übernahme des Befehls vom Stimuligenerator wird über diese Leitung mit einem Impuls bestätigt.

- 7. **COMMAND:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Befehle an den anderen Modulen. Die Befehle werden als Zeichenkette übermittelt und sie bestehen aus einem Befehlswort und weiteren Parametern.

- 8. **CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Übernahme des Befehls von einem Modul wird über diese Leitung mit einem Impuls bestätigt.

- 9. CLK: Bei einer steigenden Flanke (0 → 1) an diesem Eingang, vom Typ Std\_Logic, werden die COMMAND und STIM\_CMD Leitungen neu gesetzt. Die PARS\_CMD\_DONE und WAIT Leitungen werden vom CLK nicht beeinflusst.

#### **Parameter**

Der Controller kann durch folgende Parameter konfiguriert werden:

**COMMAND\_TIMEOUT** time: Die maximal erlaubte Zeit zur Ausführung eines Befehls. Wenn die Zeit überschritten wird, wird der Controller eine Timeout Fehlerbehandlung einleiten. Wenn der Parameter den Wert 0 hat, wird nie ein Timeout Fehler ausgelöst.

# **Befehle**

Der Controller bezieht alle Befehle über die PARS\_CMD Leitung. Die Befehle sind Steuerungsbefehle und Stimulibefehle. Es gibt derzeit nur ein Steuerungsbefehl der dem Controller adressiert ist. Dieser setzt den COMMAND\_TIMEOUT Parameter des Controllers und kann auch während der Simulation aufgerufen werden.

#### Syntax:

```

command ::= CONTROLLER COMMAND_TIMEOUT time

```

Alle anderen Steuerungsbefehle werden an den anderen Modulen weitergeleitet. Die Stimulibefehle werden vom Controller des Stimuligenerators vorbereitet und weitergeleitet. In den meisten Fällen ist keine Vorbereitung notwendig. Eine Vorbereitung ist notwendig, wenn

die Stimulibefehle mit einem Wertbereich gesetzt sind. In diesem Fall wird der Stimulibefehl vom Controller in einzelne Stimulibefehle aufgesplittert und nur dann dem Stimuligenerator weitergeleitet.

# Fehlerbehandlung

Ein möglicher Fehler ist das Setzen von fehlerhaften Parametern. Diese treten unmittelbar nach einem Aufruf des CONTROLLER Befehls auf. Vor dem Einsatz der neuen Parameter, werden diese überprüft. Wenn das Timeout keine gültige Zahl ist, werden die Anweisungen ignoriert und der Controller arbeitet wie zuvor weiter. Ein weiterer Fehler ist, wenn ein Timeout der Befehlsverarbeitung ausgelöst wird. In diesem Fall wird der nächste Befehl geholt und die Simulation wird fortgesetzt. Jeder auftretende Fehler bewirkt eine Fehlermeldung in der Reportdatei.

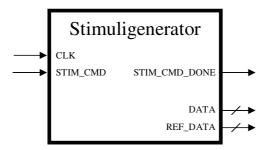

# 2.2.3 Stimuligenerator

Der Stimuligenerator generiert, anhand der Stimulibefehle, die Stimulidaten für die Eingänge der UUT und des Referenzmoduls, bzw. die Referenzdaten für den Comparator. Der Controller liefert dem Stimuligenerator die Befehle über die STIM\_CMD Leitung. Der Stimuligenerator verarbeitet die Stimulibefehle, erstellt die Stimulidaten und sendet jeweils nach jedem Befehl eine Bestätigung dem Controller über die STIM\_CMD\_DONE Leitung zurück. Die DATA und REF\_DATA Leitungen werden mit den Stimulidaten versorgt. Diese repräsentieren symbolisch die Schnittstelle zu UUT und zu Referenzmodul, bzw. zu Comparator. Die DATA Leitungen werden an die UUT und wenn vorhanden an das Referenzmodul angeschlossen. Die REF\_DATA Leitungen werden an dem Comparator angeschlossen.

Abbildung 10 – Stimuligenerator Modul

#### **Schnittstelle**

Die Schnittstelle des Stimuligenerators ist in der Abbildung 10 dargestellt und besteht aus folgenden Leitungen:

1. **STIM\_CMD:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Stimulibefehle vom Controller an den Stimuligenerator. Die Befehle werden als Zeichenkette übermittelt und sie bestehen aus einem Befehlswort und weiteren Parametern.

- 2. **STIM\_CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Ausführung des Befehls wird dem Controller über diese Leitung mit einem Impuls signalisiert.

- 3. **DATA:** Die DATA Leitungen repräsentieren die Eingangsschnittstelle der UUT und des Referenzmoduls. Sie werden mit Signalen des gleichen Datentyps und der gleichen Breite, wie die Eingänge der UUT und des Referenzmoduls, ersetzt.

- 4. **REF\_DATA:** Die REF\_DATA Leitungen stellen die Ausgangsschnittstelle der UUT und des Referenzmoduls dar. Sie werden mit Signalen des gleichen Datentyps und der gleichen Breite, wie die Ausgänge der UUT und des Referenzmoduls, ersetzt. Der Comparator wird über diese Leitungen mit den Referenzdaten versorgt.

- 5. **CLK:** Bei einer steigenden Flanke (0 → 1) an diesem Eingang, vom Typ Std\_Logic, werden die DATA, REF\_DATA oder COMMAND Leitungen neu gesetzt. Die STIM\_CMD\_DONE und WAIT Leitungen werden vom CLK nicht beeinflusst.

#### **Befehle**

Der Stimuligenerator erhält keine Steuerungsbefehle, nur Stimulibefehle. Diese werden in Stimulidaten umgewandelt und an die UUT, an das Referenzmodul und an den Comparator weitergegeben.

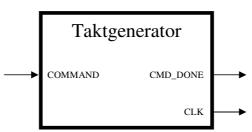

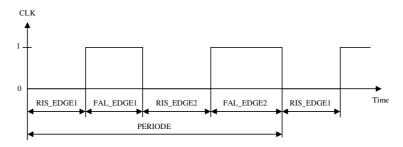

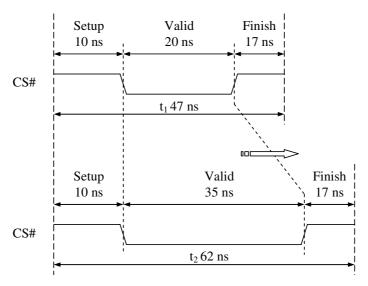

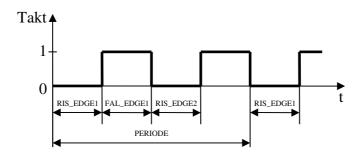

# 2.2.4 Taktgenerator

Der Taktgenerator erzeugt eine Impulsfolge am CLK Ausgang. Die Periode und die Dauer der Impulse innerhalb der Taktperiode sind einstellbar. Es können mehrere Impulse pro Periode angegeben werden, um Bausteine, die Mehrpulstakt benötigen, versorgen zu können. Alle Parameter sind während der Laufzeit veränderbar. Die Parameter des Taktgenerators werden durch die Steuerungsbefehle gesetzt. Die Steuerungsbefehle werden über die COMMAND Leitung übermittelt, die Bestätigung, dass der Befehl angenommen wurde, wird über die CMD\_DONE Leitung gesendet.

Abbildung 11 – Taktgenerator Modul

#### **Schnittstelle**

Die Schnittstelle des Taktgenerators ist in der Abbildung 11 dargestellt und besteht aus folgenden Leitungen:

1. **COMMAND:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Befehle als Zeichenkette vom Controller an den Taktgenerator.

- 2. **CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Ausführung des Befehls wird dem Controller über diese Leitung mit einem Impuls signalisiert.

- 3. **CLK:** Diese Leitung ist vom Typ Std\_Logic und liefert ein periodisches Taktsignal. Das zeitliche Verhalten ist in der Abbildung 12 dargestellt. Die Zeitangaben der steigenden und fallenden Flanken sind parametrisierbar. Die Parameter werden durch Steuerungsbefehle verändert.

Abbildung 12 – Taktsignal zeitliche Verhalten

#### **Parameter**

Der Taktgenerator kann durch den folgenden Parameter konfiguriert werden:

- 1. **PERIODE** time: Periodendauer. Sie ist auch während der Simulation änderbar.

- 2. **RIS\_EDGE1** time: Zeit bis zur steigenden Flanke des ersten Impulses. Sie ist auch während der Simulation änderbar.

- 3. **FAL\_EDGE1** time: Zeit bis zur fallenden Flanke des ersten Impulses. Sie ist auch während der Simulation änderbar.

- 4. **RIS\_EDGE2** time: Zeit bis zur steigenden Flanke des zweiten Impulses. Sie ist auch während der Simulation änderbar.

- 5. **FAL\_EDGE2** time: Zeit bis zur fallenden Flanke des zweiten Impulses. Sie ist auch während der Simulation änderbar.

#### **Befehle**

Der Taktgenerator bezieht die Steuerungsbefehle über die COMMAND Leitung und wird durch das Befehlswort CLOCK adressiert. Die Steuerungsbefehle setzen die Parameter des Taktgenerators und können auch während der Simulation aufgerufen werden. Um unerwünschte Nebeneffekte bei dem Wechsel der Zeitangaben zu vermeiden, erfolgt die Umschaltung erst nach beendetem Taktzyklus.

#### Syntax:

### **Fehlerbehandlung**

Die wahrscheinlichsten Fehler sind das Setzen von fehlerhaften Parametern. Diese treten unmittelbar nach einem Aufruf des CLOCK Befehls auf. Vor dem Einsatz der neuen Parameter, werden diese überprüft. Wenn die Summe der RIS\_EDGE und FAL\_EDGE Zeiten mehr als die angegebene Periode ist, werden die Anweisungen ignoriert und der Taktgenerator arbeitet wie zuvor weiter. Jeder auftretende Fehler bewirkt eine Fehlermeldung in der Reportdatei.

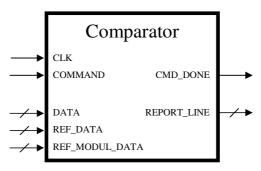

# 2.2.5 Comparator

Der Comparator vergleicht die Ausgänge der UUT mit den Referenzdaten. Das Ergebnis wird an den Reportgenerator weitergeleitet. Die Referenzdaten können vom Stimuligenerator oder vom Referenzmodul stammen, wobei die Werte vom Stimuligenerator favorisiert werden. Die Parameter des Comparators werden durch die Steuerungsbefehle gesetzt. Die Steuerungsbefehle werden über die COMMAND Leitung übermittelt, die Bestätigung, dass der Befehl angenommen wurde, wird über die CMD\_DONE Leitung gesendet.

Abbildung 13 – Comparator Modul

#### **Schnittstelle**

Die Schnittstelle des Comparators ist in der Abbildung 13 dargestellt und besteht aus folgenden Leitungen:

- 1. **COMMAND:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Befehle als Zeichenkette vom Controller an den Comparator.

- 2. **CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Ausführung des Befehls wird dem Controller über diese Leitung mit einem Impuls signalisiert.

- 3. **CLK:** Taktsignal für Datensynchronisation.

- 4. **DATA:** Die Ausgangssignale der UUT werden an diesen Leitungen gelegt.

- 5. **REF\_MODUL\_DATA:** Die Ausgangssignale des Referenzmoduls werden an diesen Leitungen gelegt. Wenn kein Referenzmodul angeschlossen ist, werden diese Leitungen nicht verwendet.

- 6. **REF\_DATA:** Die Referenzdaten des Stimuligenerators werden an diesen Leitungen gelegt.

7. **REPORT\_LINE:** Die Ergebnisse des Vergleichsvorgangs werden an diesem Ausgang im String Format ausgegeben.

#### **Parameter**

Der Parser kann durch den folgenden Parameter konfiguriert werden:

**TOLERANCE** time: Toleranzzeit, in der die Signale unterschiedlich sein dürfen.

#### **Befehle**

Der Reportgenerator bezieht die Steuerungsbefehle über die COMMAND Leitung und wird durch das Befehlswort REPORT adressiert. Die Steuerungsbefehle setzen die Parameter des Reportgenerators und können auch während der Simulation aufgerufen werden.

Syntax:

command ::= COMPARATOR TOLERANCE time

## **Fehlerbehandlung**

Die wahrscheinlichsten Fehler sind das Setzen von fehlerhaften Parametern. Diese treten unmittelbar nach einem Aufruf des COMPARATOR Befehls auf. Vor dem Einsatz der neuen Parameter, werden diese überprüft. Wenn die Toleranz keine gültige Zeit ist, werden die Anweisungen ignoriert und der Comparator arbeitet wie zuvor weiter. Jeder auftretende Fehler bewirkt eine Fehlermeldung in der Reportdatei.

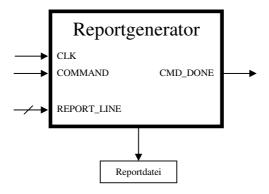

# 2.2.6 Reportgenerator

Der Reportgenerator sammelt Informationen aus der Testbench und erstellt eine Reportdatei. Die Informationen stammen hauptsächlich vom Comparator, die über die REPORT\_LINE Leitung ankommen. Die Parameter des Comparators werden durch die Steuerungsbefehle gesetzt. Die Steuerungsbefehle werden über die COMMAND Leitung übermittelt, die Bestätigung, dass der Befehl angenommen wurde, wird über die CMD\_DONE Leitung gesendet.

Abbildung 14 – Reportgenerator Modul

#### Schnittstelle

Die Schnittstelle des Reportgenerators ist in der Abbildung 14 dargestellt und besteht aus folgenden Leitungen:

- 1. **COMMAND:** Diese Leitung ist vom Typ String und dient zur Übermittlung der Befehle als Zeichenkette vom Controller an den Reportgenerator.

- 2. **CMD\_DONE:** Diese Leitung ist vom Typ Std\_Logic. Die Ausführung des Befehls wird dem Controller über diese Leitung mit einem Impuls signalisiert.

- 3. **CLK:** Taktsignal für Datensynchronisation.

- 4. **REPORT\_LINE:** Über diese Leitung werden die Nachrichten im String Format den Reportgenerator übermittelt.

### Reportdatei

Der Reportgenerator schreibt die eintreffenden Nachrichten in die Reportdatei. Diese ist eine Textdatei und kann mit Texteditoren gelesen werden. Die Formatierung des Inhalts ist von der Implementierung des Reportgenerators abhängig. Das Resultat der Simulation wird in der Reportdatei festgehalten.

#### **Parameter**

Der Parser kann durch den folgenden Parameter konfiguriert werden:

- 1. **REPORTDATEI** string: Name der Reportdatei.

- 2. **LOGLEVEL** integer: Loglevel des Reportgenerators.

#### **Befehle**

Der Reportgenerator bezieht die Steuerungsbefehle über die COMMAND Leitung und wird durch das Befehlswort REPORT adressiert. Die Steuerungsbefehle setzen die Parameter des Reportgenerators und können auch während der Simulation aufgerufen werden.

#### Syntax:

## **Fehlerbehandlung**

Die wahrscheinlichsten Fehler sind das Setzen von fehlerhaften Parametern. Diese treten unmittelbar nach einem Aufruf des REPORT Befehls auf. Vor dem Einsatz der neuen Parameter, werden diese überprüft. Wenn die Reportdatei nicht angelegt werden kann oder wenn der Loglevel unbekannt ist, werden die Anweisungen ignoriert und der Reportgenerator arbeitet wie zuvor weiter.

## 2.3 Testbench-Struktur ohne Controller

In diesem Abschnitt präsentierte Testbench ist für kleine bis mittelgroße ASIC Entwicklungen geeignet. Die Testbench arbeitet nur mit Stimulibefehlen. Die Konfiguration der Module wird am Anfang der Simulation mit den Parametern aus der Konfigurationsdatei durchgeführt. Das Blockschaltbild der Testbench ist in der Abbildung 15 präsentiert und besteht aus folgenden Modulen:

- 1. **Stimuligenerator:** parst die Stimulidatei und stellt die Stimulidaten der UUT und dem Referenzmodul, bzw. die Referenzdaten dem Comparator zur Verfügung.

- 2. Taktgenerator: liefert den Systemtakt.

- 3. **Comparator mit Reportgenerator:** wertet die Ausgabedaten der UUT aufgrund der Referenzdaten aus und speichert die Ergebnisse in eine Textdatei ab.

- 4. **UUT:** der zu testenden Einheit.

- 5. **Referenzmodul:** liefert die Solldaten.

Abbildung 15 – Testbench-Struktur ohne Controller

Der Stimuligenerator ist für die Versorgung der UUT und des Referenzmoduls mit den Stimulidaten, bzw. für die Versorgung des Comparators mit den Referenzdaten zuständig. Die Stimulidaten und die Referenzdaten werden aus den Stimulibefehlen generiert, welche in der Stimulidatei gespeichert sind. Die Stimulibefehle werden sequentiell aus der Stimulidatei gelesen, in Stimulidaten und in Referenzdaten konvertiert und anschließend an die DATA, bzw. REF\_DATA Leitungen geführt. Der Comparator übernimmt die Ausgabedaten der UUT und des Referenzmoduls, bzw. die Referenzdaten vom Stimuligenerator. Die Werte werden verglichen und das Resultat in eine Reportdatei geschrieben. Der Taktgenerator liefert den Takt der UUT und dem Referenzmodul. Die UUT, bzw. das Referenzmodul werden nicht beschrieben. Sie sind die Resultate der ASIC Entwicklungen und haben eine klar definierte Schnittstelle nach Außen.

## 2.4 Stimulibefehl Modelle

Die Stimulibefehle können verschiedene Modelle haben. In diesem Abschnitt werden drei

Varianten präsentiert.

#### 2.4.1 Stimulibefehl Modell 1

Der Stimulibefehl ist als eine Bitfolge dargestellt. Die Bitfolge besteht aus den Stimulidaten der Eingangsleitungen und aus den zu erwartenden Werten (Referenzwerte) der Ausgangsleitungen der UUT. Die zu erwartenden Werte sind mit einem "R" gekennzeichnet. Das Kennzeichen wurde wegen die IN/OUT Signalen eingeführt, da diese Signale abwechselnd entweder mit Stimulidaten versorgt oder mit den zu erwartenden Werten verglichen werden. An der letzten Stelle des Befehls wird die Dauer des Befehls mitgespeichert. Für jeden Pegelwechsel eines Signals ist ein neuer Befehl notwendig. Der Vorteil solcher Befehle ist, dass sie sehr schnell verarbeitet werden können. Für zeitkritische Entwicklungen ist eine ideale Lösung. Der Nachteil ist, dass die langen Bitfolgen schwer lesbar sind.

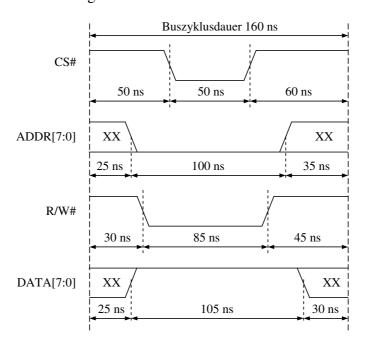

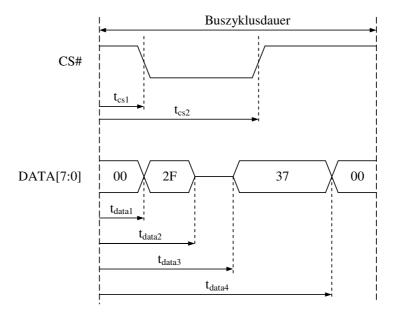

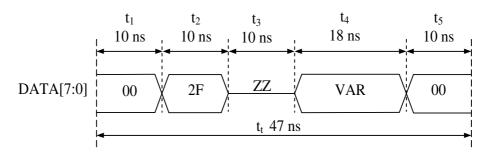

Beispiel: Der zeitliche Ablauf der Signale aus der Abbildung 16 wird in der Tabelle 2 als eine Sequenz von Stimulibefehlen dargestellt.

Abbildung 16 – Signalabläufe einer Buszyklus

| CS | ADDR     | RW | DATA     | Time |

|----|----------|----|----------|------|

| 1  | XXXXXXXX | 1  | XXXXXXXX | 25ns |

| 1  | 00000000 | 1  | 11111111 | 5ns  |

| 1  | 00000000 | 0  | 11111111 | 20ns |

| 0  | 00000000 | 0  | 11111111 | 50ns |

| 1  | 00000000 | 0  | 11111111 | 15ns |

| 1  | 00000000 | 1  | 11111111 | 10ns |

| 1  | XXXXXXXX | 1  | 11111111 | 5ns  |

| 1  | XXXXXXXX | 1  | XXXXXXXX | 30ns |

Tabelle 2 – Stimulibefehle der Variante 1

Nach jedem Pegelwechsel des Timingdiagramms wird ein neuer Befehl angelegt. Die

Bitpositionen der Signale bleiben immer an der selber Stelle. Im Beispiel wird die CS Leitung immer mit dem Wert aus der Position 1 der Bitfolge versorgt. Wenn die Zeitangabe am Ende des Befehls nicht definiert wurde, dann wird sofort der nächste Befehl ausgeführt.

### 2.4.2 Stimulibefehl Modell 2

Der Stimulibefehl besteht aus einem Signalnamen und aus einer Bitfolge. Der Signalname ist die Bezeichnung einer Leitung der UUT. Wenn die Leitung eine Eingangsleitung ist, besteht die Bitfolge aus den Stimulidaten der Eingangsleitung. Wenn die Leitung eine Ausgangsleitung ist, besteht die Bitfolge aus den zu erwartenden Werten der Ausgangsleitung. Die zu erwartenden Werte sind mit einem "R" Zeichen gekennzeichnet. Das Kennzeichen wurde wegen der IN/OUT Signalen eingeführt, da diese Signale abwechselnd entweder mit Stimulidaten versorgt oder mit den zu erwartenden Werten verglichen werden. Die Befehle werden sequenziell ausgeführt. Für jeden Pegelwechsel eines Signals ist ein neuer Befehl notwendig. Zwischen zwei Pegelwechsel wird die Befehlverarbeitung mit einem WAIT Statement angehalten. Der Vorteil solcher Befehle ist, dass sie sich nur auf einzelne Signale beziehen, nur bei Pegelwechsel der einzelnen Signale aufgerufen werden sollen. Der Nachteil ist, dass die langen Befehlslisten schwer lesbar sind.

Beispiel: Der zeitliche Ablauf der Signale aus der Abbildung 16 wird in der Tabelle 3 als eine Sequenz von Stimulibefehlen dargestellt.

| Signal | Wert     |

|--------|----------|

| CS     | 1        |

| ADDR   | XXXXXXX  |

| RW     | 1        |

| DATA   | XXXXXXX  |

| WAIT   | 25ns     |

| ADDR   | 00000000 |

| DATA   | 11111111 |

| WAIT   | 5ns      |

| RW     | 0        |

| WAIT   | 20ns     |

| CS     | 0        |

| WAIT   | 50ns     |

| CS     | 1        |

| WAIT   | 15ns     |

| RW     | 1        |

| WAIT   | 10ns     |

| ADDR   | XXXXXXX  |

| WAIT   | 5ns      |

| DATA   | XXXXXXX  |

| WAIT   | 30ns     |

*Tabelle 3 – Stimulibefehle der Variante 2*

Nach jeden Pegelwechseln des Timingdiagramms wird ein neuer Befehl angelegt. Der Befehl beinhaltet nur ein einziges Signal. Wenn gleichzeitig mehrere Pegelwechsel stattfinden, werden dementsprechend mehrere Befehle erstellt.

### 2.4.3 Stimulibefehl Modell 3

Der Stimulibefehl wird als einen Pseudobefehl dargestellt. Das Erzeugen von Stimulidaten aus dem Befehl ist wesentlich komplexer, als im Modell 1 und 2. Jeder Befehldefinition wird mit einem HDL Prozess modelliert. Der Vorteil solcher Befehle ist, dass sie sehr kompakt und leicht zu lesen sind. Der Nachteil ist, dass die Verarbeitung der Befehle viel Rechenleistung benötigt.

Beispiel: ACC 0,0x92

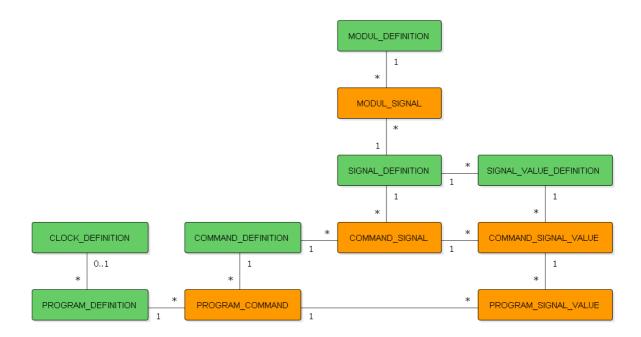

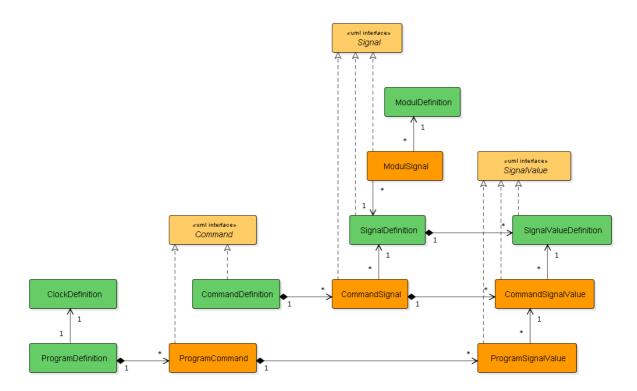

## 2.5 Testbench-Generator Datenmodell

Im folgenden Abschnitt wird das Datenmodell des Testbench-Generators definiert. Ein wichtiger Aspekt des Modells ist die redundanten Informationen zu vermeiden. Eine nachträgliche Änderung soll auf alle abhängigen Objekte Auswirkung haben.