The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# Diagnosis and Maintenance in an Integrated Time-Triggered Architecture

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Doktors der technischen Wissenschaften

unter der Leitung von

O. Univ.-Prof. Dr. Hermann Kopetz Institut für Technische Informatik 182

eingereicht an der

Technischen Universität Wien Fakultät für Informatik

von

Philipp Peti Matr. - Nr. 9625740 Rittergasse 1/2/10, A-1040 Wien

Wien, im September 2005

# Diagnosis and Maintenance in an Integrated Time-Triggered Architecture

The use of electronics in automotive and avionic industry accounts for numerous improvements with respect to system safety, fuel economy, passenger comfort, and system costs. In last years, however, the development of effective diagnostic systems stayed behind the recent increase of electronic systems in modern means of transportation. In combination with shrinking geometries this issue has lead to a dramatic increase of transient system failures that cannot be traced. This so called trouble-not-identified phenomenon is a significant problem with major economic implications due to false maintenance actions resulting in increased warranty costs and decreased customer satisfaction.

In this thesis we look at diagnosis in the context of integrated architectures, since integrated architectures, as already partly deployed in avionics, promise massive cost savings due to the multiplexing of hardware resources among different application subsystems. Furthermore, the resulting reduction of wiring and connectors results in dependability improvements. For this reason, integrated architectures are gaining more and more momentum also in the automotive domain in order to resolve the pending "one function - one control unit" problem.

In order to cope with industry demands on diagnosis, as part of this thesis a framework is introduced for error detection and subsequent identification of the field replaceable units causing system malfunction. Such a framework provides generic diagnostic services to be parameterized according to the developer's needs and thus avoids costly redesign of individual diagnostic solutions at application level.

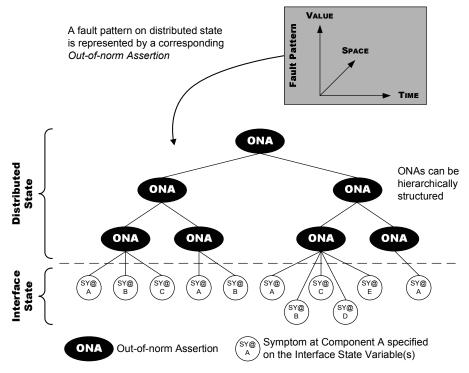

Based on industrial requirements, a maintenance-oriented fault model is presented. This fault model takes the component-based nature of today's distributed embedded systems into account. According to this model each experienced failure is classified with respect to the field replaceable units of the system and stops the recursion of the fault-error-failure chain at a level suitable for maintenance. The pivotal strategy of the diagnostic architecture is the establishment of a holistic view on the system by operating on the distributed state established via the underlying core services. To capture the characteristics of the fault-induced distributed state changes in the value, space, and time domain, we introduce the concept of out-of-norm assertions in order to discriminate between different types of faults that are affecting the operation of the distributed system. In the introduced framework, for the specification of the diagnostic mechanisms timed automata are used.

For the transport of diagnostic information a dedicated virtual network is established. The key advantage of such an encapsulated network dedicated to diagnosis is the fact that real-time traffic is not compromised in any way and no probe effects can be introduced. Based on the maintenance-oriented fault model this diagnostic information is then processed to determine the health status of the field replaceable units of the system. The result supports the service technician in the decision process whether a field replaceable unit remains in the system or will be replaced.

The proposed methods are implemented and evaluated in a prototype setup of the integrated time-triggered architecture. In this prototype setup the feasibility of the proposed architecture is investigated. Furthermore, fault injection campaigns have been carried out, to analyze the effects of faults on the distributed state of state time-triggered core network and to validate claims of the diagnostic architecture.

# Diagnose und Wartung in einer integrierten zeitgesteuerten Architektur

Der Einsatz von Elektronik in der Automobil- und Flugzeugindustrie hat zu zahlreichen Innovationen im Bereich der Sicherheit, der Antriebstechnik, des Passagierkomforts sowie zu einer Reduktion der Systemkosten geführt. In den letzten Jahren hat allerdings die Entwicklung effizienter on-board Diagnosesysteme dem technischen Fortschritt auf anderen Gebieten nicht Stand gehalten. Mit dem Anstieg von transienten Fehlerraten von IC's aufgrund der höheren Integration hat diese Entwicklung zu einer signifikanten Erhöhung von nicht reproduzierbaren Fehlern mit weit reichenden wirtschaftlichen Konsequenzen geführt.

In Rahmen dieser Arbeit wird Diagnose im Kontext von integrierten Architekturen untersucht, da integrierte Architekturen, wie bereits teilweise in der Flugzeugindustrie eingesetzt, massive Kosteneinsparungen durch das Multiplexen von Hardware Ressourcen zwischen den verschiedenen Applikationssubsystemen erlauben. Weiters ermöglicht die Reduktion von Steckern und Kabelverbindungen eine erhebliche Verbesserung in Hinblick auf die Zuverlässigkeit des Systems. Aus diesem Grund gewinnen integrierte Systemarchitekturen auch in der Automobilindustrie immer mehr an Bedeutung, insbesondere um das vorherrschende "eine Funktion - ein Knoten" Problem zu lösen.

Um den industriellen Diagnoseanforderungen zu genügen, wird als Teil dieser Arbeit eine Rahmenungebung vorgestellt, welche die online Fehlererkennung und Identifikation der im Feld austauschbaren Systemkomponenten unterstützt. Es werden generische Diagnoseservices zur Verfügung gestellt, die nach den Anforderungen der Entwickler parametrisiert werden können. So wird ein aufwendiges und kostenintensives Re-design von individuellen Diagnoselösungen auf Applikationsebene vermieden.

Ein zentrales Element der Arbeit ist die Definition eines wartungsorientierten Fehlermodells. Dieses Fehlermodell berücksichtigt die typische Komponentenstruktur heutiger verteilter eingebetteter Systeme. Nach diesem Modell wird jeder aufgetretene Fehler nach den austauschbaren Einheiten des Systems klassifiziert. Damit wird die Rekursion der "Fault-Error-Failure" Kette auf einer für die Wartung passenden Ebene gestoppt. Die Schlüsselstrategie der vorgestellten Diagnosearchitektur ist die Operation auf dem verteilten Zustand des Systems. Um die Charakteristik von fehlerinduzierten Zustandsänderungen in Wert, Zeit, und Raum einzufangen, wird das Konzept der Out-of-Norm Assertions eingeführt, um zwischen den verschiedenen Fehlerklassen zu unterscheiden. Für die Spezifikation der Diagnosemechanismen werden Zeit-Automaten benutzt.

Zum Transport der Diagnosenachrichten wird ein der Diagnose a priori zugeordnetes virtuelles Netzwerk verwendet. Der Hauptvorteil eines solchen gekapselten Netzwerkes besteht darin, dass andere Echtzeitnachrichten nicht beeinflusst werden und somit kein "Probe Effekt" entstehen kann. Die Diagnoseinformationen werden anschließend nach dem wartungsorientierten Fehlermodell verarbeitet, um den Zustand der austauschbaren Systemkomponenten festzustellen. Das Resultat des Analyseprozesses dient dem Wartungstechniker im Entscheidungsprozess, ob eine Systemkomponente getauscht werden muss.

Die entwickelten Methoden wurden im Rahmen eines Prototyps der integrierten zeitgesteuerten Architektur implementiert und evaluiert. In diesem Prototypenaufbau wurde die Durchführbarkeit der vorgeschlagenen Architektur untersucht. Weiters wurden Fehlereinstreuungsexperimente ausgeführt, um die Effekte von Fehlern auf den verteilten Zustand des unterliegenden zeitgesteuerten Systems zu analysieren und Behauptungen der Diagnosearchitektur zu validieren.

# Contents

| 1 Introduction |     |         |                                                                                                                                                 |    |  |

|----------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|                | 1.1 | Object  | tives and Contribution of the Thesis                                                                                                            | 3  |  |

|                | 1.2 | Struct  | ure of the Thesis                                                                                                                               | 6  |  |

| <b>2</b>       | Bas | ic Con  | cepts                                                                                                                                           | 7  |  |

|                | 2.1 | Time    |                                                                                                                                                 | 7  |  |

|                | 2.2 | State   |                                                                                                                                                 | 10 |  |

|                |     | 2.2.1   | The Concept of State                                                                                                                            | 10 |  |

|                |     | 2.2.2   | Ground State                                                                                                                                    | 11 |  |

|                | 2.3 | Comp    | onent $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                   | 11 |  |

|                |     | 2.3.1   | Software Component                                                                                                                              | 12 |  |

|                |     | 2.3.2   | System Component                                                                                                                                | 13 |  |

|                | 2.4 | Interfa | ace                                                                                                                                             | 15 |  |

|                |     | 2.4.1   | Software Interfaces                                                                                                                             | 15 |  |

|                |     | 2.4.2   | Message Interfaces                                                                                                                              | 18 |  |

|                | 2.5 | Depen   | $dability \ldots \ldots$ | 20 |  |

|                |     | 2.5.1   | Fault, Error, Failure                                                                                                                           | 21 |  |

|                |     | 2.5.2   | Fault-Tolerance                                                                                                                                 | 21 |  |

|                |     | 2.5.3   | Fault and Error Containment                                                                                                                     | 22 |  |

| 3              | Rel | ated W  | Vork 2                                                                                                                                          | 25 |  |

|                | 3.1 | Error   | and Anomaly Detection                                                                                                                           | 25 |  |

|                |     | 3.1.1   | Error Detection using Assertions                                                                                                                | 25 |  |

|                |     | 3.1.2   | Anomaly Detection                                                                                                                               | 26 |  |

|                |     | 3.1.3   | Comparative Evaluation                                                                                                                          | 27 |  |

|                | 3.2 | Prever  | ntive vs. Corrective Maintenance                                                                                                                | 27 |  |

|                | 3.3 | Auton   | notive Diagnosis and Maintenance                                                                                                                | 29 |  |

|                |     | 3.3.1   | Automotive Infrastructure                                                                                                                       | 29 |  |

|                |     | 3.3.2   | Diagnostic Infrastructure                                                                                                                       | 31 |  |

|                |     | 3.3.3   | Role of Diagnosis                                                                                                                               | 33 |  |

|   |                | 3.3.4 OSEK/VDX                                                                                |

|---|----------------|-----------------------------------------------------------------------------------------------|

|   | 3.4            | Avionic Diagnosis and Maintenance                                                             |

|   |                | 3.4.1 On-bard Maintenance System                                                              |

|   |                | 3.4.2 ARINC 653                                                                               |

|   | 3.5            | Setting the Focus on Transients                                                               |

|   |                | 3.5.1 The Trouble Not Identified Phenomenon                                                   |

|   |                | 3.5.2 Shift in Technology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 44$ |

|   |                | 3.5.3 Lasting Consequences on Business Realities                                              |

|   | 3.6            | The Heinrich Pyramid and Related Models                                                       |

|   | 3.7            | Analysis Techniques                                                                           |

|   |                | 3.7.1 Threshold-Based Techniques                                                              |

|   |                | 3.7.2 Probabilistic Networks                                                                  |

|   |                | 3.7.3 Model-Based Diagnosis                                                                   |

| 4 | $\mathbf{Svs}$ | tem Model 57                                                                                  |

|   | 4.1            | Physical and Functional Structuring                                                           |

|   |                | 4.1.1 Functional System Structuring                                                           |

|   |                | 4.1.2 Physical System Structuring                                                             |

|   |                | 4.1.3 Namespace of the Integrated Architecture                                                |

|   |                | 4.1.4 Architectural Services                                                                  |

|   | 4.2            | Core Services                                                                                 |

|   | 4.3            | High Level Services                                                                           |

|   |                | 4.3.1 Encapsulation Service                                                                   |

|   |                | 4.3.2 Virtual Network Service                                                                 |

|   |                | 4.3.3 Gateway Service                                                                         |

|   |                | 4.3.4 Fault-Tolerance Service                                                                 |

|   |                | 4.3.5 Diagnosis and Maintenance Service                                                       |

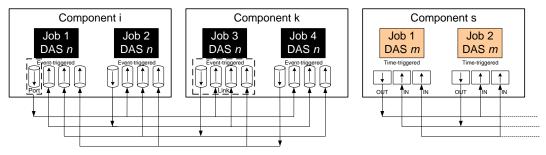

|   | 4.4            | Component Structure                                                                           |

|   | 4.5            | Design Flow                                                                                   |

|   | 4.6            | Dependability                                                                                 |

|   |                | 4.6.1 Hardware Fault Model                                                                    |

|   |                | 4.6.2 Software Fault Model                                                                    |

|   |                | 4.6.3 Distinction between Heisenbugs and Transients                                           |

| 5 | Dia            | gnosis Model 78                                                                               |

| 0 | 5.1            | Requirements                                                                                  |

|   | 5.2            | Overview and Strategy                                                                         |

|   | 5.3            | The Maintenance-Oriented Fault Model                                                          |

|   |                |                                                                                               |

|   |     | 5.3.1  | Unit of Replacement                             | 83   |

|---|-----|--------|-------------------------------------------------|------|

|   |     | 5.3.2  | Fault Classification                            | . 84 |

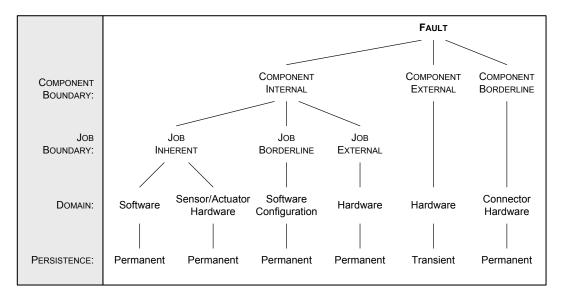

|   |     | 5.3.3  | The Component Fault Model                       | 85   |

|   |     | 5.3.4  | The Job Fault Model                             | 86   |

|   |     | 5.3.5  | Assumptions behind the Fault Model              | . 87 |

|   | 5.4 | Suital | pility Analysis                                 | . 88 |

|   |     | 5.4.1  | Component Fault Model                           | . 88 |

|   |     | 5.4.2  | Job Fault Model                                 | . 94 |

|   | 5.5 | Out-o  | f-Norm Assertions                               | 96   |

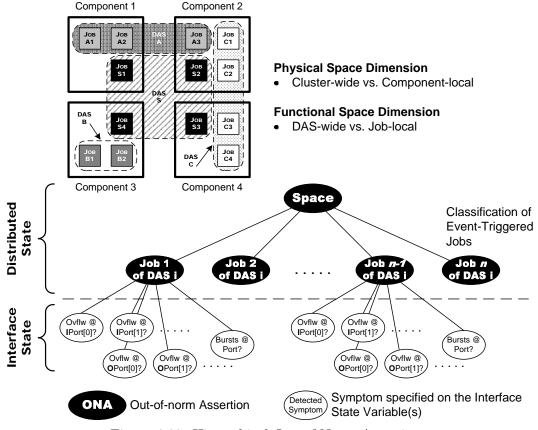

|   |     | 5.5.1  | Distributed State                               | 96   |

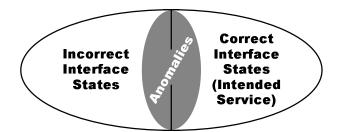

|   |     | 5.5.2  | Definition of Out-of-Norm Assertions            | 102  |

|   | 5.6 | The V  | Virtual Diagnostic Network                      | 106  |

|   |     | 5.6.1  | Properties of the Virtual Diagnostic Network    | 106  |

|   |     | 5.6.2  | The Structure of the Virtual Diagnostic Network | 108  |

|   |     | 5.6.3  | The Diagnostic Message Format                   | 109  |

|   | 5.7 | Specif | fication and Execution                          | 110  |

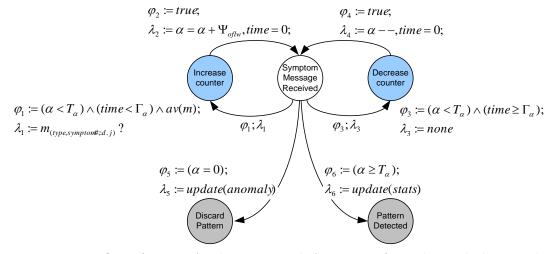

|   |     | 5.7.1  | The Timed Symptom/Analysis Automaton            | 111  |

|   |     | 5.7.2  | Symptom Specification                           | 112  |

|   |     | 5.7.3  | Analysis Specification                          | 116  |

|   |     | 5.7.4  | Execution of the Timed Automata                 | 119  |

|   | 5.8 | Detec  | tion at Component Level                         | 120  |

|   |     | 5.8.1  | The Allocation and Virtual Network Layer        | 121  |

|   |     | 5.8.2  | Gateway Layer                                   | 122  |

|   |     | 5.8.3  | Fault-Tolerance Layer                           | 123  |

|   |     | 5.8.4  | Message Classification Layer                    | 123  |

|   |     | 5.8.5  | Application Programming Interface Layer         | 123  |

|   | 5.9 | Analy  | rsis                                            | 124  |

|   |     | 5.9.1  | Diagnostic DAS                                  | 124  |

|   |     | 5.9.2  | Determining the Replacement Strategy            | 127  |

|   |     | 5.9.3  | Applying Out-of-Norm Assertions                 | 128  |

| 6 | Imp | olemen | ntation of the DECOS Architecture               | 132  |

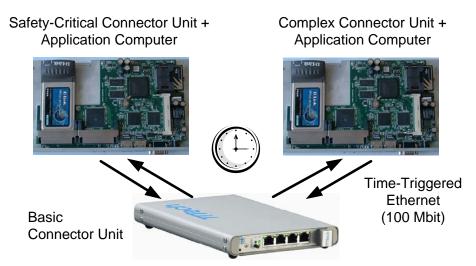

|   | 6.1 | The F  | Prototype Setup                                 | 133  |

|   |     | 6.1.1  | Hardware Setup                                  | 133  |

|   |     | 6.1.2  | Software Setup                                  | 135  |

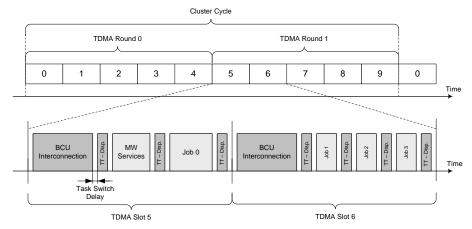

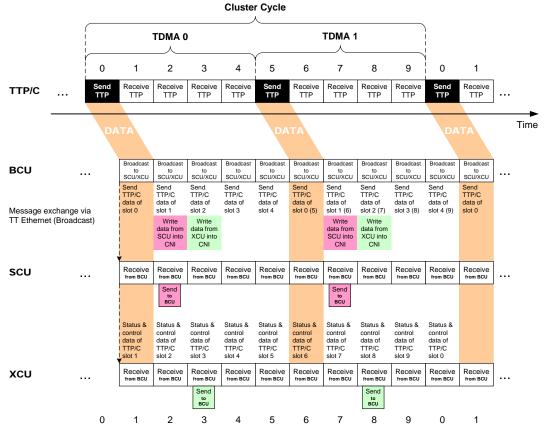

|   |     | 6.1.3  | Hierarchical Network - Interconnection Scheme   | 137  |

|   |     | 6.1.4  | Automotive Example                              | 138  |

|    |       | 6.1.5   | Implementation of the Virtual Network Service                                                 |            |

|----|-------|---------|-----------------------------------------------------------------------------------------------|------------|

|    | 6.2   |         | Diagnostic Framework                                                                          |            |

|    |       | 6.2.1   | Specification of Out-of-Norm Assertions                                                       |            |

|    |       | 6.2.2   | Code Generation                                                                               |            |

|    |       | 6.2.3   | Deployment and Execution                                                                      |            |

|    | 6.3   | • •     | tom Detection                                                                                 |            |

|    |       | 6.3.1   | Job-Inherent Faults                                                                           |            |

|    |       | 6.3.2   | Job Borderline Faults                                                                         |            |

|    |       | 6.3.3   | Component Borderline Faults                                                                   |            |

|    |       | 6.3.4   | Component Internal Faults                                                                     |            |

|    |       | 6.3.5   | Component External Faults                                                                     |            |

|    | 6.4   |         | sis $\ldots$ |            |

|    |       | 6.4.1   | Design of the Analysis Job                                                                    |            |

|    |       | 6.4.2   | Analysis Data Structures                                                                      |            |

|    |       | 6.4.3   | Determination of Component Borderline Faults                                                  |            |

|    |       | 6.4.4   | Determination of Job-Inherent Faults                                                          |            |

|    |       | 6.4.5   | Determination of Job Borderline Faults                                                        | . 179      |

| ,  | Sele  | ected I | Experiments and Results                                                                       | 185        |

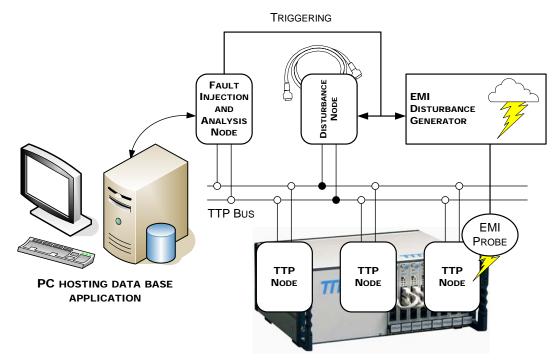

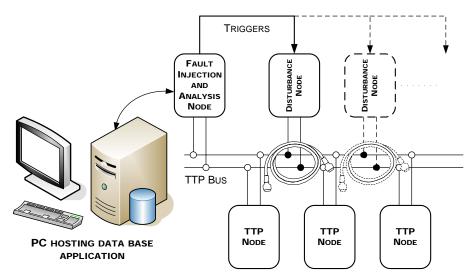

|    | 7.1   | The F   | Fault Injection Framework                                                                     | . 185      |

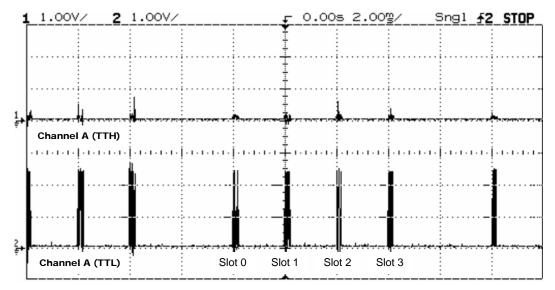

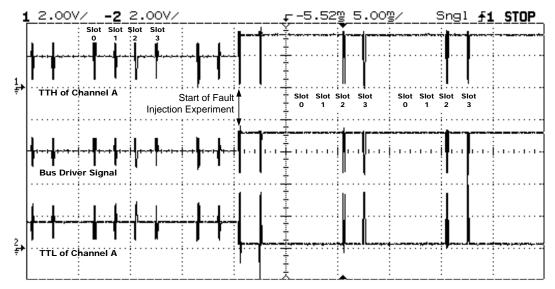

|    |       | 7.1.1   | Cluster Description                                                                           | . 187      |

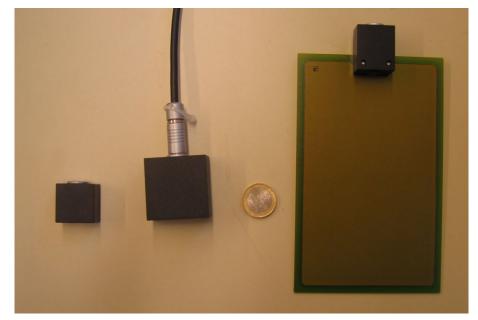

|    |       | 7.1.2   | The NSG 1025 Fast Transient/Burst Generator                                                   | . 187      |

|    |       | 7.1.3   | The TTTech TTP-Disturbances Node                                                              | . 189      |

|    | 7.2   | Analy   | rsis of Component External Failures                                                           | . 190      |

|    |       | 7.2.1   | Hypotheses                                                                                    | . 190      |

|    |       | 7.2.2   | Experimental Setup                                                                            | . 191      |

|    |       | 7.2.3   | Results                                                                                       | . 191      |

|    |       | 7.2.4   | Interpretation and Discussion                                                                 | . 193      |

|    | 7.3   | Analy   | rsis of Component Borderline Failures                                                         | . 196      |

|    |       | 7.3.1   | Hypotheses                                                                                    | . 196      |

|    |       | 7.3.2   | Experimental Setup                                                                            | . 197      |

|    |       | 7.3.3   | Results                                                                                       | . 197      |

|    |       | 7.3.4   | Interpretation and Discussion                                                                 | . 200      |

| 3  | Cor   | nclusio | n                                                                                             | 203        |

| 3i | bliog | graphy  | ,                                                                                             | 207        |

| Cι | ırric | ulum    | Vitae                                                                                         | <b>231</b> |

|    |       |         |                                                                                               |            |

# List of Figures

| 2.1  | Sparse Time Base                                              | )      |

|------|---------------------------------------------------------------|--------|

| 2.2  | The Concept of Ground State                                   | L      |

| 2.3  | The Four Contract Levels                                      | 3      |

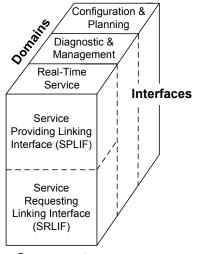

| 2.4  | Structuring of Interfaces                                     | 7      |

| 2.5  | Linking Interfaces                                            | )      |

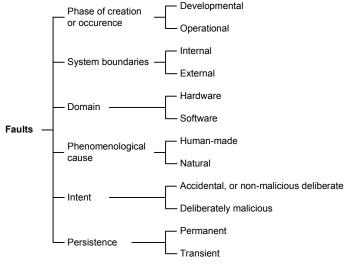

| 2.6  | Elementary Fault Classes                                      | L      |

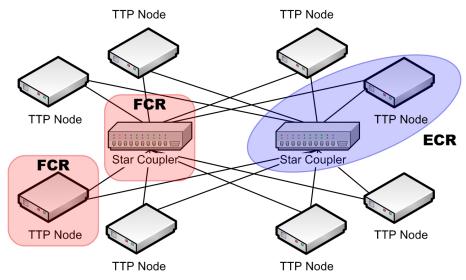

| 2.7  | FCRs and ECRs in the Time-Triggered Architecture              | ł      |

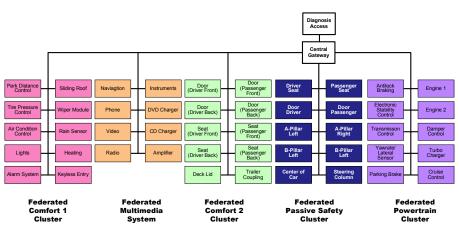

| 3.1  | The Electronic Infrastructure of a Luxury Car 30              | )      |

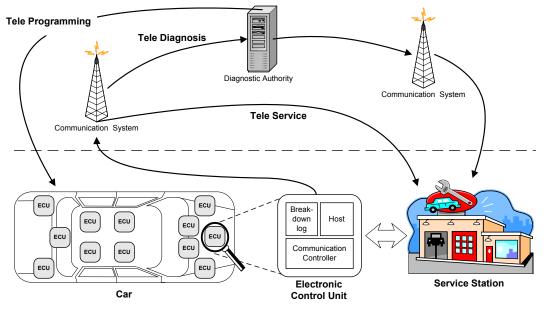

| 3.2  | Automotive Diagnostic Infrastructure                          | 2      |

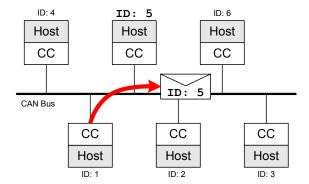

| 3.3  | Diagnostic Deficiencies of CAN: Masquerading 34               | ł      |

| 3.4  | Scrubbing Techniques                                          | 3      |

| 3.5  | The TNI Phenomenon                                            | L      |

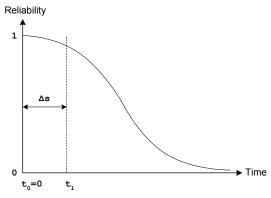

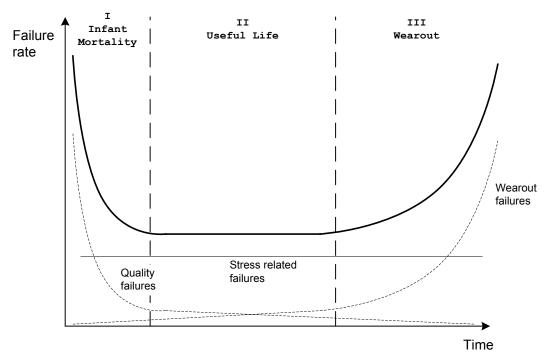

| 3.6  | Bathtub Curve                                                 | ł      |

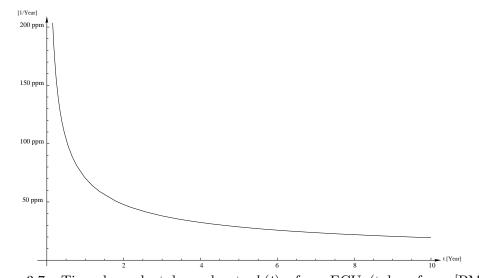

| 3.7  | Time-dependent Hazard Rate of an ECU                          | 5      |

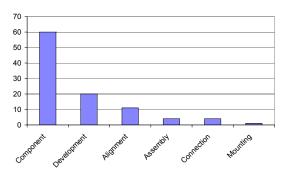

| 3.8  | Pareto Plot of ECU Failures                                   | 3      |

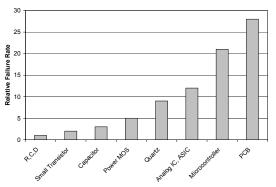

| 3.9  | Components as Failure Causes                                  | 3      |

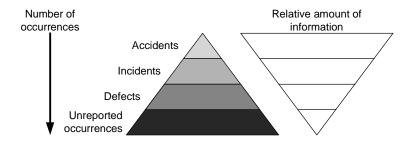

| 3.10 | The Heinrich Pyramid                                          | 3      |

| 3.11 | Air Safety Information Model based on the Heinrich Pyramid 49 | )      |

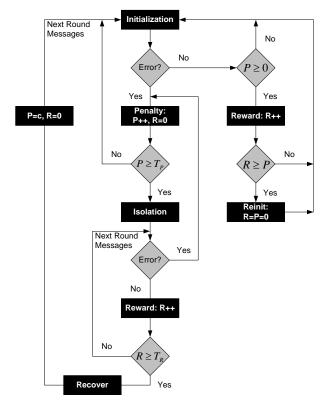

| 3.12 | Two Level Threshold-Based Algorithm                           | )      |

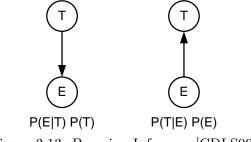

| 3.13 | Bayesian Inference                                            | 3      |

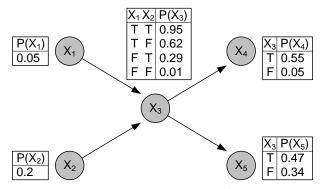

| 3.14 | Bayesian Network Example                                      | ł      |

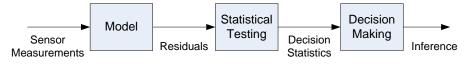

| 3.15 | Model-Based Diagnosis Stages                                  | ;<br>; |

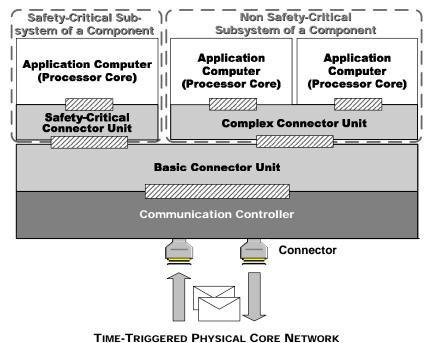

| 4.1  | The DECOS Integrated System Architecture                      | 3      |

| 4.2  | Virtual Network Service                                       | ;      |

| 4.3  | Physical and Virtual Gateways in an Automotive Application 69 | )      |

| 4.4  | The DECOS Component Model                                     | )      |

| 4.5  | Design Flow                                                   | 3      |

| 4.6  | Immediate Impact of a Developmental Software Fault            | 3      |

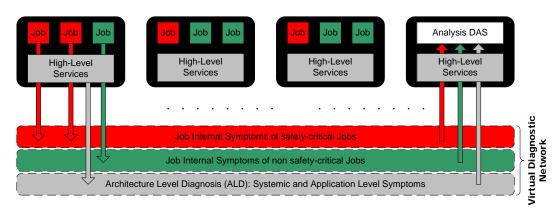

| 5.1          | Overview of the Diagnostic Infrastructure                                                 |

|--------------|-------------------------------------------------------------------------------------------|

| 5.2          | Classification of Diagnosis                                                               |

| 5.3          | The Fault-Error-Failure Chain                                                             |

| 5.4          | Component Fault Model                                                                     |

| 5.5          | Job Fault Model                                                                           |

| 5.6          | Overview of the Maintenance-Oriented Fault Model                                          |

| 5.7          | Interface State                                                                           |

| 5.8          | Sparse Time Base                                                                          |

| 5.9          | Summarized Fault Patterns                                                                 |

| 5.10         | State Space                                                                               |

| 5.11         | Definition of Out-of-Norm Assertion                                                       |

| 5.12         | Assessment Process                                                                        |

| 5.13         | Self-Checking vs. Cross-Checking                                                          |

| 5.14         | Constraints on the Interface State                                                        |

| 5.15         | The Virtual Diagnostic Network                                                            |

| 5.16         | The Diagnostic Message Format                                                             |

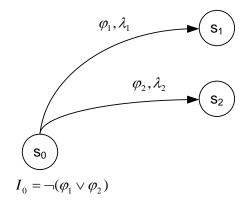

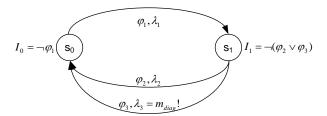

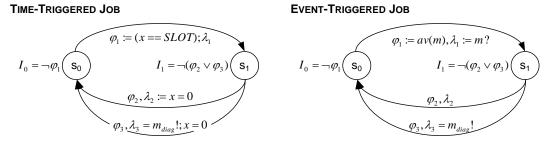

| 5.17         | A Timed Symptom/Analysis Automaton                                                        |

| 5.18         | Systemic Symptom Detection                                                                |

| 5.19         | Application-Specific Symptom Detection                                                    |

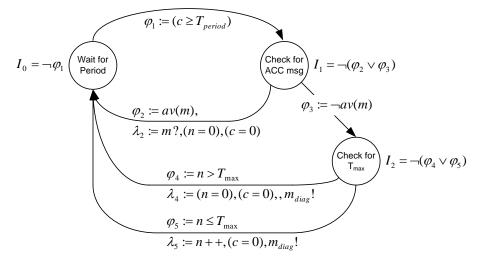

| 5.20         | Adaptive Cruise Control - Error Detection at the Receiver 115                             |

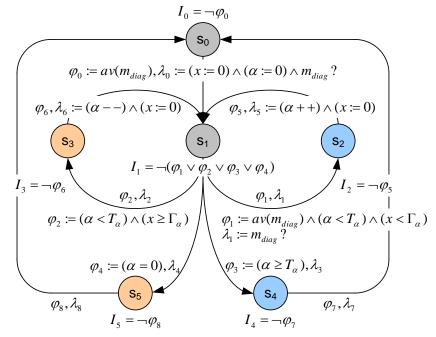

| 5.21         | Timed Analysis Automaton                                                                  |

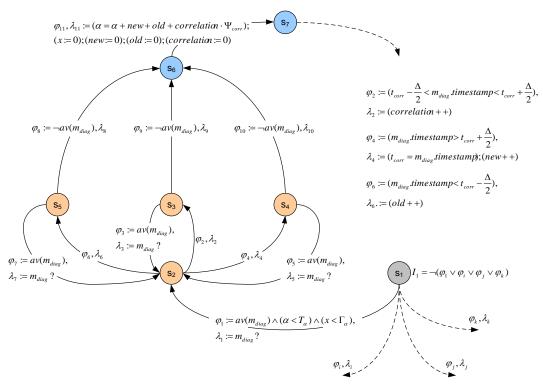

| 5.22         | Correlation of Information                                                                |

| 5.23         | Execution Step of the Timed Automaton                                                     |

| 5.24         | Timed Automata Execution on the Sparse Time Base $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

| 5.25         | Layers of a Connector Unit of a DECOS Component                                           |

| 5.26         | API Layer                                                                                 |

| 5.27         | The Diagnostic DAS                                                                        |

| 5.28         | LRU Assessment Process                                                                    |

| 5.29         | Determining the Maintenance Action for each Fault Class 128                               |

| 5.30         | Assessment of a Wearout Phenomenon                                                        |

| 5.31         | Judgment According to the Three Dimensions                                                |

| 6.1          | The DECOS Prototype Cluster                                                               |

| 6.2          | The Independence of the Core Communication System                                         |

| 6.3          | A Prototype DECOS Component                                                               |

| 0.3<br>6.4   | BCU Interconnection Schedule                                                              |

| $0.4 \\ 6.5$ | Hierarchical Networks                                                                     |

| 0.0          |                                                                                           |

| Implementation of the Virtual Network Service                            |

|--------------------------------------------------------------------------|

| The Diagnostic Framework                                                 |

| Schedule of the Diagnostic Middleware Services                           |

| Execution on the Sparse Time Base                                        |

| Symptom Detection                                                        |

| Steering Wheel and Pedals                                                |

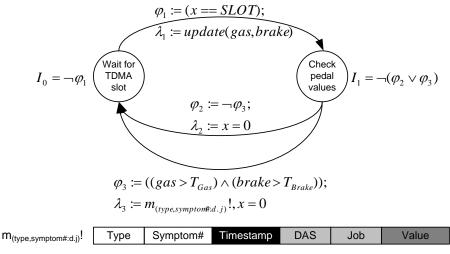

| Timed Automaton for Symptom: Both Pedals Pressed                         |

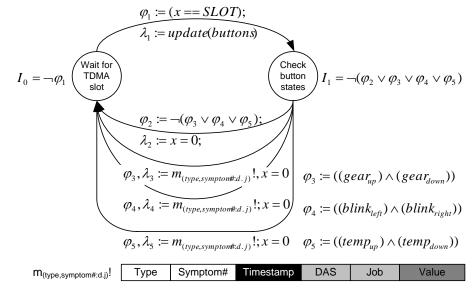

| Timed Automaton for Symptom: Out-of-Norm Buttons                         |

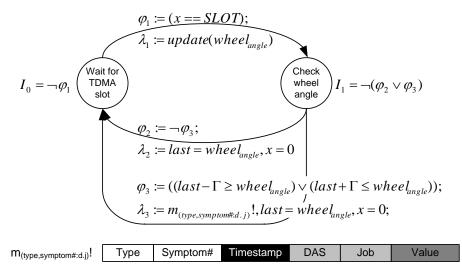

| Timed Automaton for Symptom: Out-of-Norm Steering Wheel Angle . 152      |

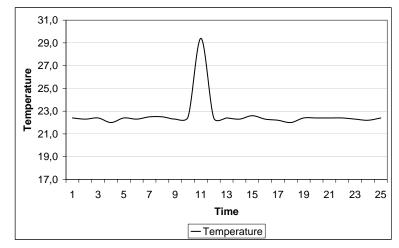

| Out-of-Norm Measurement of a Temperature Sensor                          |

| Job-inherent Symptom Detection                                           |

| Job Borderline Faults (Interarrival Time Specification)                  |

| TTP/C Message Status Field                                               |

| TTP/C Protocol Errors                                                    |

| Symptom for Component Borderline Faults                                  |

| Symptom for Component Internal Faults                                    |

| The Analysis Job                                                         |

| The Schedule of the Analysis Job                                         |

| Conceptual Model of the Data Structure for Component Analysis 168        |

| Conceptual Model of the Data Structure for Cluster Analysis $\ldots$ 169 |

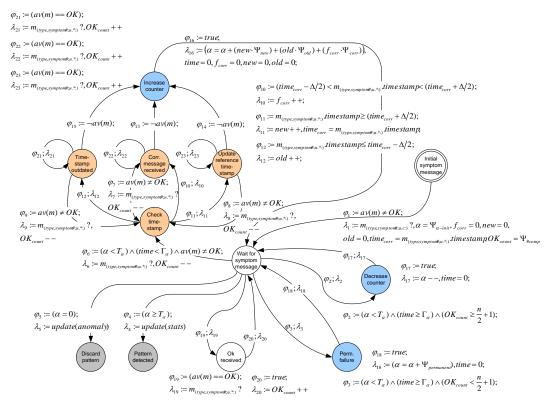

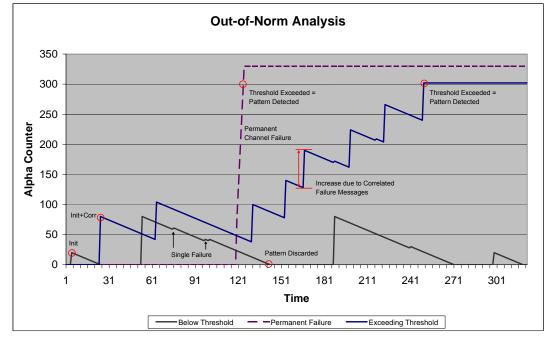

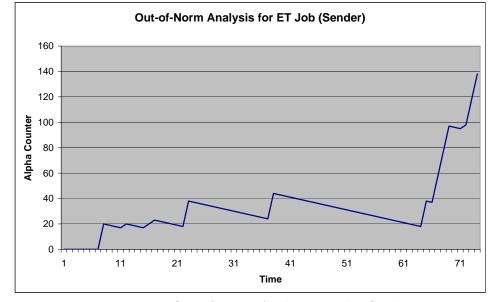

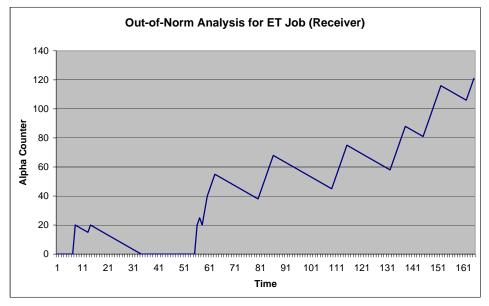

| Out-of-Norm Analysis: Component Borderline Faults                        |

| Out-of-Norm Analysis: Alpha Counter Strategies                           |

| Out-of-Norm Analysis: Job Inherent Faults                                |

| Diagnosis of Event-Triggered Virtual Networks                            |

| Hierarchical Out-of-Norm Assertions                                      |

| Out-of-Norm Analysis: Job Borderline Faults                              |

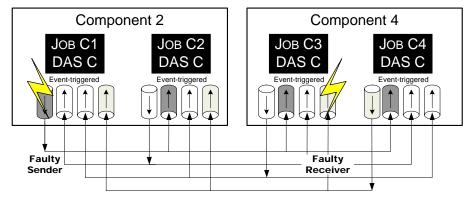

| Out-of-Norm Analysis: Faulty Sender                                      |

| Out-of-Norm Analysis: Faulty Receiver                                    |

| Setup of the Hardware Fault Injection Experiments                        |

| The NSG 1025 Fast Transient/Burst Generator                              |

| The Different Types of Probes of the EMI Testing Device 188              |

| The TTP-Disturbance Node                                                 |

| Setup for the EMI Fault Injection Experiments for Analyzing Compo-       |

| nent Failures                                                            |

| Setup for the Borderline Fault Injection Experiments                     |

| Fault Injection using the Disturbance Node                               |

|                                                                          |

| 7.8 | A Short Circuit injected on Channel A of the TTP | Bus. | <br> | 201 |

|-----|--------------------------------------------------|------|------|-----|

| 7.9 | A Bus Failure on Channel A dividing the Cluster. |      | <br> | 202 |

# Chapter 1

# Introduction

There is a significant trend in the automotive and avionics industry to increase the number of electronic devices in order to provide a functionality that goes beyond common mechanic/hydraulic systems. The reduction of cost, increased safety and reliability, reduced complexity, and enhanced quality of control are among the primary objectives of replacing conventional subsystems with electronic ones. Fly-by-wire airplanes like the Boeing 777/787 or the Airbus A320/330/340/380 series aircrafts show impressively the benefits and capabilities of state-of-the-art electronic devices and architectures [MS03]. Also in the automotive domain without the use of electronics in modern cars many features like anti-lock braking, stability programs, airbags, cruise control, intelligent motor management and many more would be impossible. With decreasing hardware costs and increased reliability of electronic devices this trend will continue even more in the future. For example, in the automotive domain it is estimated that more than 80% of all innovations now stem from electronics [LH02]. According to [Ber02] in the 2001 model year, electronics accounted for 19 percent of a mid-sized vehicle's cost, while the cost of the electronics in luxury vehicles can amount to more than 23 percent of the total manufacturing costs [LHD99, LH02].

However, despite all the benefits it is important to state that with the increasing use of electronic devices in transportation systems the likelihood of malfunctions and thus the numbers of defective electronic components will also increase.

Originally developed to provide simple open/short circuit and abnormal voltage level detection mechanisms, electronic diagnosis evolved into an integral part of every automobile. All modern cars are equipped with On-Board Diagnosis (OBD) systems (OBD-II in USA or EOBD in Europe). OBD, originally developed to continuously monitor the emissions of a car, provides now almost complete engine diagnosis and also monitors parts of the chassis, body electronics, and the control network of the vehicle [OM02].

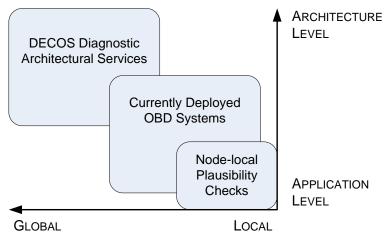

However, the development of effective diagnostic systems has stayed behind the recent increase of electronic systems in modern cars. One reason for the diagnostic deficiencies of modern OBD systems is the fact that diagnosis is often treated as add-on to communication systems rather than an integral part of the architecture [SSW00]. Consequently, the problem of the identification of faulty Electronic Control Units (ECUs) is one of the predominant challenges that needs to be solved.

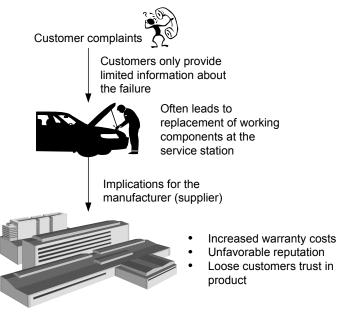

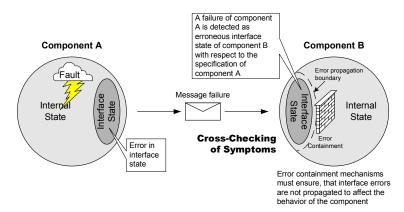

Though the breakdown logs of the ECUs inform the service technician about detected errors within the system, they do not assist the technician adequately in the identification process [Bar01]. Thus, fully functional units are replaced, or even worse, faulty ECUs remain unchanged in the system. These diagnostic deficiencies will become more and more obvious when X-by-wire solutions will be subject to mass production [Bre01]. Since a mechanic at a service station is no specialist in automobile electronics, the diagnostic system of the car must provide all necessary information that allows maintenance of faulty components. For this reason it must be possible in modern automotive electronic architectures to trace an entry in a breakdown log back to its source. If this is not possible, as a consequence, fully operational units will be replaced by mistake.

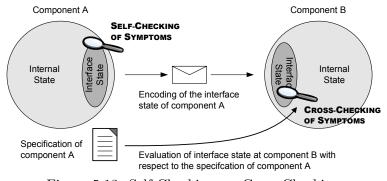

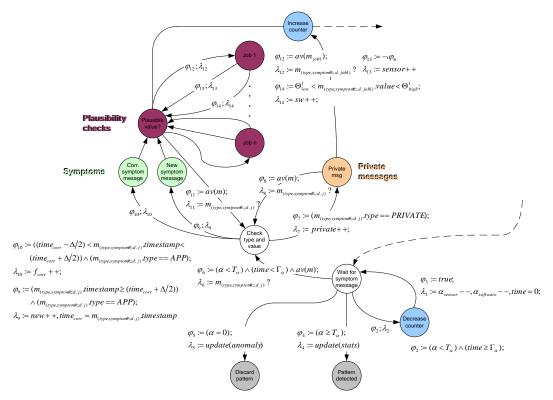

Many deployed OBD systems analyze the internal state of a component (e.g., plausibility checks) by applying embedded assertions in the application software in order to identify component errors. Assertions are a powerful and accepted mechanism in helping in the detection of application errors. However, such assertions operate in general only on the internal state of components. The inability to trace correlated failures of the nodes of a distributed system makes diagnosis prone to misjudgement about transient faults affecting the system. These so-called *cannot duplicate failures* frequently result in the replacement of operational Field Replaceable Units (FRUs) [TAP02, MRS<sup>+</sup>02, Scu98]. As a consequence, these spurious failures have a lasting effect on the customer's trust in the product and the reputation of the manufacturer.

In contrast to permanent component failures that have been massively reduced by improvements of the manufacturing process [PMH98], transient failures in electronic systems impose a serious problem to electronic system designers and manufacturers. The primary cause for the significant increase of soft error rates are shrinking geometries, lower power voltages and higher frequencies [Con02]. Furthermore, the likelihood of transient failures is also growing due to semiconductor process variations and manufacturing residuals. Consequently, what is required in distributed embedded systems, is a diagnostic subsystem with detection mechanisms focussing on transient failures. In particular, from a maintenance perspective, the most important diagnostic objective is the discrimination between transient failures induced from external and internal faults to put an end to unnecessary component replacements.

Today, in the automotive domain we find electronic system architectures that cannot be classified as either completely federated nor integrated. Typically, electronic systems in the car do not provide mechanisms to share an ECU among multiple applications and thus adhere to the federated systems design principle. However, for economic reasons, distributed application subsystems share typically the same communication infrastructure (e.g., a CAN network for the interconnection of the comfort electronics in a car). However, this system design has the significant drawback of increased complexity. Since reasoning of the behavior of a particular application requires the understanding of all other applications participating in the communication, this design makes it hard to comprehend the emerging interdependencies between applications. Furthermore, in case of failure, missing error containment capabilities make system integration and diagnosis a challenging and cost intensive task. Since integration responsibilities cannot easily be assigned, even the launch of new car models can be delayed. The "1 Function - 1 ECU" design philosophy that is characteristic for this system design approach leads to a dramatic increase of the numbers of ECUs due to the increased functionality of today's cars required by the expectations of the customers. For example, luxury cars can have more than 70 ECUs [Dei02]. Since such a high number imposes problems with respect to architecture complexity, wiring, mounting, resource duplication and many others, a reduction of the number of ECUs is of great interest.

Integrated architectures as already partly deployed in avionics [Aer91], promise also massive cost savings by addressing problems the automotive industry is currently facing. Integrated architectures are characterized by the possibility to share components among multiple applications. In addition, integrated systems permit an optimal interplay of application subsystems, reliability improvements with respect to wiring and connectors, and overcome limitations for spare components and redundancy management. An ideal future system architecture would thus *combine the complexity management advantages of the federated approach, but would also realize the functional integration and hardware benefits of an integrated system* [Ham03, p. 32]. The challenge is to devise an integrated architecture that provides a framework with generic architectural services for integrating multiple application subsystems within a single, distributed computer system, while retaining the error containment and complexity management benefits of federated systems.

# **1.1** Objectives and Contribution of the Thesis

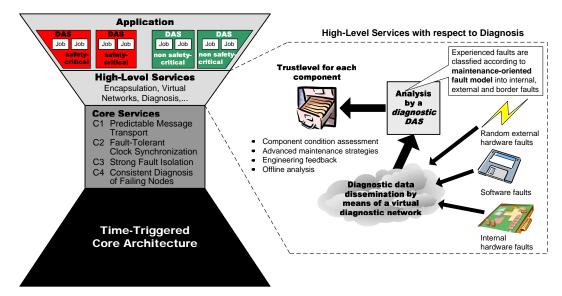

The main objective of this thesis is to devise generic diagnostic architectural services as part of a certifiable integrated architecture suitable for both ultra-dependable applications and those having less stringent dependability requirements in favor of increased flexibility. In the following, we will identify the primary objectives and contributions of the thesis.

#### Integrated Solution

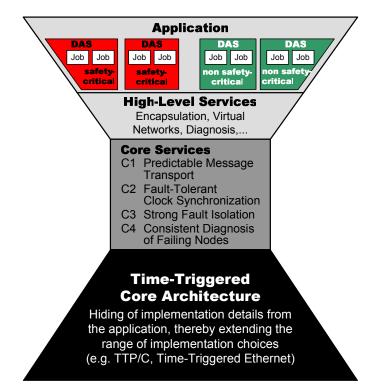

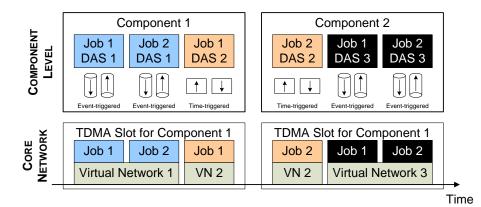

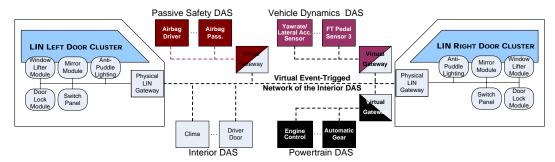

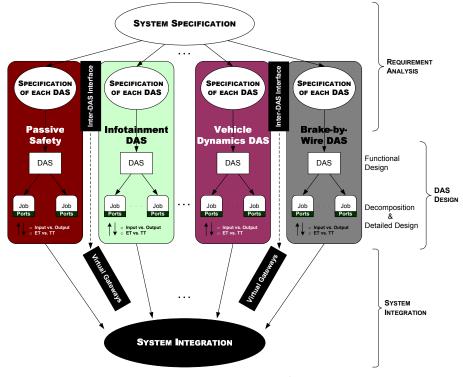

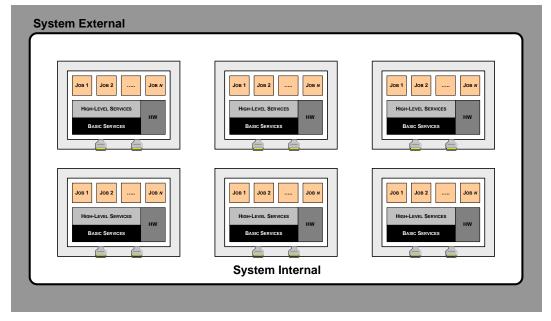

The DECOS architecture, as being developed in the course of the Sixth European Framework Programme, is designed to combine the benefits of the federated and integrated system design. The DECOS architecture [KOPS04] offers a framework for the development of distributed embedded real-time systems integrating multiple applications with different levels of criticality and different requirements concerning the underlying platform. Any time-triggered architecture that provides four basic services, i.e. predictable message transport, fault-tolerant clock synchronization, strong fault isolation, and consistent diagnosis of failing nodes, can be used as the core architecture for a DECOS integrated system. Based on these core services, high-level services are realized that are specific to an encapsulated application subsystem (e.g., brake-by-wire subsystem) and facilitate the development of applications by providing a stable interface to commonly used functionality thus reducing the complexity of application development. The encapsulation of application subsystems also facilitates independent development and system integration.

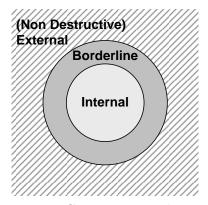

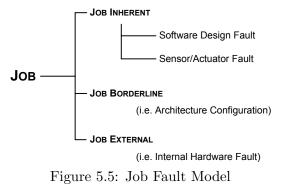

As part of the design of this integrated system architecture, a diagnostic infrastructure is devised that in contrast to many addendum solutions deployed today allows evolving beyond "best guess maintenance". Our solution provides a framework for both systemic and application-specific diagnosis. While systemic diagnosis focusses on the assessment of the health status of the underlying platform (e.g., physical components, connectors), application-specific diagnosis aims at revealing application inherent faults such as software and actuator/sensor faults. Since the DECOS architecture sharply separates application from architecture level, the systemic checks can be deployed independently from a particular application. By precisely defining the interface state of the applications, applications diagnosis can be handled in a generic manner outside the application functionality, as required by today's industrial demand for intellectual property protection (i.e. no modification of the application source code). This way only the application inherent complexity must be dealt with during application development but no additional complexity is introduced by the diagnostic subsystem.

A dedicated virtual network, i.e. an overlay network on top of the time-triggered physical core network, is used for the transport of diagnostic information. This way no interference with the real-time services or a probe effect due to hardware failures (e.g., loose contacts) can be introduced that might mislead the analysis process. Furthermore, such a pure virtual solution has also the benefit of keeping the associated costs to a minimum.

Another important fact is, that the proposed diagnostic solution does not restrict the choices of implementation of the analysis subsystem. Either a central or a distributed solution can be realized.

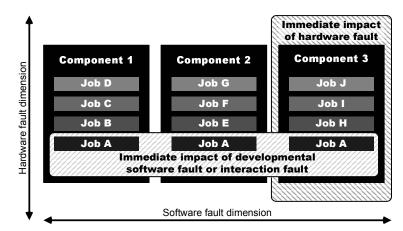

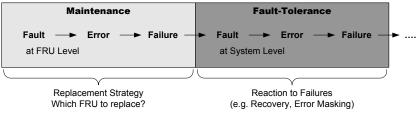

### A Fault Model for Maintenance

In order to tackle prevalent maintenance problems a maintenance-oriented fault model needs to be devised that takes the component-based nature of distributed systems into account. According to this model each experienced failure is classified according to the FRUs of the system. In integrated architectures, a one to one mapping between applications and physical components is no longer feasible. This has to be taken into account in a maintenance-oriented fault model that establishes a basis for a better understanding of the diagnostic problems of modern distributed systems and introduces a maintenance-specific fault classification. Consequently, the model stops the recursion of the fault-error-failure chain at a level suitable for maintenance. According to this model, the diagnostic analysis algorithms of the integrated architecture can assess the health state of each FRU and determine whether a change of a particular FRU can eliminate an experienced problem. The maintenance-oriented fault model is based on related literature, field data, and discussions with industrial partners.

Furthermore, this model forms also the conceptual foundation for the validation of the diagnostic mechanisms, e.g., by means of fault injection experiments. By injecting representative faults for every devised fault class (e.g., Electromagnetic Interference (EMI) for external transient faults) the accuracy of the detection and analysis mechanisms can be evaluated.

### Improved Accuracy of Diagnosis

Currently, industry has significant problems detecting and identifying electronic devices that cause system failures in electronic systems. This so called *Trouble Not Identified (TNI) phenomenon* is an increasing problem in automotive and avionic electronics with major economic implications [TAP02]. The lack of information provided by currently deployed OBD systems often results in unnecessary replacements of working components [MRS<sup>+</sup>02, TE01].

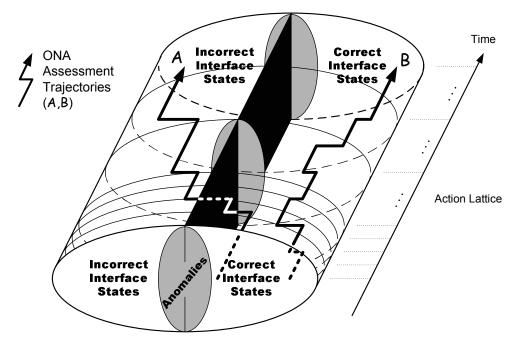

By operating on the distributed state of the system instead of the component local state correlation of detected failures is possible and thus an improved accuracy of the assessment process can be achieved. The exploitation of the knowledge of the physical and functional structure of the integrated system allows a finer granularity of the analysis that would not be possible in a federated computer system. By overcoming the "1 Function - 1 ECU" design, a discrimination between hardware and software is feasible. Furthermore, the strong fault isolation capabilities of the timetriggered core architecture simplify to answer the question which part of the system is to blame for the experienced malfunction. In combination with the availability of a global sparse time base, a correlation of failures based on their timestamps can be detected. The inclusion of the temporal, spatial and value domain ultimately helps to answer the question of the mechanics at the service station whether to remove a FRU or to leave it in the system.

#### **Advanced Maintenance Strategies**

In both avionics and in the automotive domain manufacturers envisage a shift from traditional corrective to preventive maintenance strategies to reduce costs and to provide optimal availability of the systems. As a prerequisite for the realization of preventive maintenance strategies, diagnostic mechanism are needed to judge about the health status of each replaceable part of the system. If advanced maintenance techniques like Condition-Based Maintenance (CBM) are envisaged, then new assessment

techniques for the condition of electronic devices need to be identified [PP01, TS01]. In order to adopt CBM for electronic systems suitable indicators for degradation or wearout must be identified and analyzed to detect deviations from sound operation. Since the increase of the transient failure rate is an acknowledged indicator for premature electronic component wearout [Con02], the integrated diagnostic architecture must be designed to continuously monitor the distributed state of the system, and thus detect and record any transient anomaly. This is especially important in case of fault-tolerant systems, where a level of redundancy must be maintained to ensure safe operation even in the case of failure (according to the fault hypothesis). Consequently, monitoring of the deployed fault-tolerance mechanisms is mandatory and a replacement of defective parts by the service technician must be enabled without making the owner of the system insecure, i.e. keep the user's trust in the product.

# **1.2** Structure of the Thesis

The thesis is structured as follows. In Chapter 2 an elaboration on the concepts of time, state, component, interface and dependability is presented. Related work in the field of diagnosis and maintenance is presented in Chapter 3. Both avionics and automotive diagnosis and maintenance techniques are discussed, in particular the OSEK and ARINC strategies. Furthermore, the increase of the transient failure rate of electronic devices and its consequences are subject to investigation. In addition, the related work section covers an overview on prevalent analysis techniques. The DECOS integrated architecture is presented in Chapter 4. We first discuss the structure of the architecture, core and high-level services, and detailed component structure. In addition, we present the design flow and the underlying dependability model including the fault hypothesis for the integrated DECOS architecture. The integrated diagnostic architecture is introduced in Chapter 5. We elaborate on the maintenance-oriented fault model, introduce out-of-norm assertions as the primary diagnostic mechanism operating on the distributed state, and discuss the virtual diagnostic network and analysis subsystem. In Chapter 6 a prototype implementation of the DECOS architecture is presented. We describe the prototype platform and the implementation choices. For the implementation the time-triggered protocol (TTP) is deployed as the time-triggered core architecture. Furthermore, we show how the different detection and analysis techniques are realized and discuss the performance of some of the implemented analysis algorithms. In Chapter 7 we present selected results from fault injection campaigns. Finally, the thesis is concluded in Chapter 8.

# Chapter 2

# **Basic Concepts**

The concepts of time, state, component, interface and dependability are fundamental in the design of dependable embedded real-time systems. This chapter elaborates on the close relationship between these concepts that constitute the conceptual foundation of this thesis.

First, we discuss the concept of time, since time must be treated as first-order quantity in the design of a real-time system. The following section provides an overview of the meaning of state and the close relationship between time and the concept of state. Furthermore, we elaborate on the difference between system components and software components as the building blocks of dependable distributed systems. Since both components interact with the environment via interfaces the subsequent part discusses software and messages interfaces. This chapter is concluded by presenting the concepts of dependability.

# 2.1 Time

Whitrow [Whi90] notes that our actual experience of time can be analyzed in terms of two fundamental relations: simultaneity and temporal order (or precedence). In respect of these, any event is judged to be either simultaneous with or else either earlier than or later than any other event [Whi90, p. 207]. Russell defined (in 1914) an instant as a set of events, any two of which are simultaneous and there is no other event which is simultaneous with them all. The existence of so defined instants was assumed. An event is said to be *at* a particular instant when it is a member of the set defining that instant. Temporal order of instants is then defined by stipulating that one is earlier than another if there is some event at the former that is earlier than some event at the latter. If neither instant is earlier than the other, then they are simultaneous (identical). The continuum of real time can be modeled by a directed timeline [Wie14, Rus36] consisting of an infinite set T of instants with the following properties [Whi90]:

- 1. T is a simply ordered set, that is, if p and q are any two instants, than either p is simultaneous with q, or p precedes q, or q precedes p, and these relations are mutually exclusive. Furthermore, if p precedes q and q precedes another instant r, then p precedes r, and q is said to be between p and r.

- 2. T is a dense set. This means, that, if p precedes r, there is at least one q which is between p and r.

- 3. T satisfies Dedekind's postulate, namely if  $T_1$  and  $T_2$  are any two non-empty parts of T such, that every instant of T belongs either to  $T_1$  or  $T_2$  and every instant of  $T_1$  precedes every instant of  $T_2$ , then there is at least one instant t such that any instant earlier than t belongs to  $T_1$  and any instant later that t belongs to  $T_2$ .

This prevalent mathematical picture of "standard time", namely that of a set of *instants* with a temporal precedence order < satisfying certain obvious conditions, can also be found in [vB83]. These conditions are:

- 1. Transitivity

- 2. Irreflexivity

- 3. Linearity

- 4. Eternity  $(\forall x \exists y : y < x, \forall x \exists y : x < y)$

- 5. Density  $(\forall x, y : x < y \rightarrow \exists z : x < z < y)$

The most obvious models that satisfy these axioms are the rational numbers  $\mathbb{Q}$  and the real numbers  $\mathbb{R}$ . These sets are dense, i.e. for any two numbers there is another number that lies between them. When replacing density by *discreteness* the integers  $\mathbb{Z}$  are the standard model of time [Mat88].

The abstract mathematical idea of time as a geometrical locus – the so-called spatialization of time – is one of the most fundamental concepts of modern science. Its psychological origin lies in our intuitive conception of time as one-dimensional. Our idea of time is thus directly linked with the fact that the process of thinking has the form of a linear sequence [Whi90]. This linear sequence consists of discrete acts of attention. Consequently, in the first instance, time is more naturally associated with counting, and hence with numbers, than with the linear continuum of geometry. The peculiarly close relation between time and counting has been emphasized both by philosophers of time and by philosophers of mathematics [AriCE].

An essential difference between concurrent models of computation is their modeling of time [Lee01]. Some models are very explicit by taking time to be a real number that advances uniformly, and placing events on a time line or evolving continuous signals along the time line. In other models time is taken to be discrete, while other models, even more abstract, take time to be merely a constraint imposed by causality [Lee01]. In the context of real-time systems a time model based on Newtonian time seems to be the best choice [Kop97].

Since a behavior, i.e. the temporal sequence of send operations of a system in relation to its previous receive operations, and any internal state that it retains  $[GIJ^+02,$ p. 83] can only be associated with a system if some notion of time is taken into account [Kop97] and time is also important for the introduction of the concept of a failure, organizing further definitions around a directed timeline that extends from the past into the future is justified [Kop97]: A cut of the timeline is an instant. Any occurrence that happens at an instant is called an *event*. Information that describes an event is called event information. Event information is non-idempotent and requires exactly-once semantics when transmitted to a consumer. The present instant, now, is a very special instant that separates the past from the future An *interval* on the timeline is defined by two instants, the start event and the terminating event of the interval. Any property of an object that remains valid during a finite duration is called a state attribute and the corresponding information state information. State information is idempotent and requires at-least-once semantics when transmitted to a consumer. A change of state is an event. An observation is an event that records the state of an object at a particular instant, the point of observation. An event observation can be expressed by the atomic triple (name, value, time).

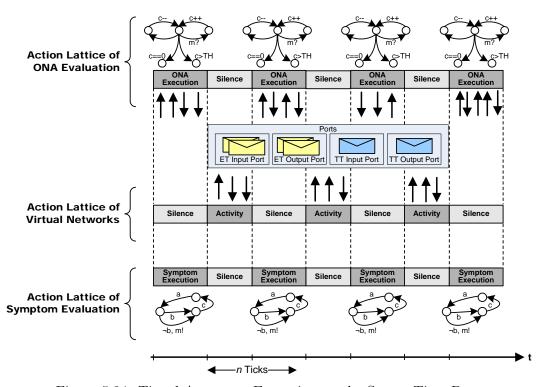

#### Sparse Time Base

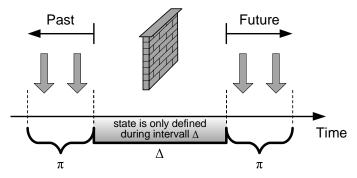

If the time-base of a distributed system is dense (the events are allowed to occur at any instant of the timeline), then it is in general not possible to generate a consistent temporal order on the basis of the time-stamps [Kop97]. Due to the impossibility of synchronizing clocks perfectly and the denseness property of real time, there is always the possibility that a single event is time-stamped by two clocks with a difference of one tick. By introducing the concept of a *sparse time base* this problem can be solved [Kop92]. In the sparse time model the continuum of time is partitioned into an

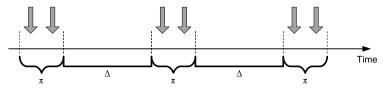

Figure 2.1: Sparse Time Base

infinite sequence of alternating durations of activity  $(\pi)$  and silence  $(\Delta)$  as shown in Figure 2.1. Thereby, the occurrence of significant events is restricted to the activity intervals of a globally synchronized action lattice. In this time model, the costly execution of agreement protocols can be avoided, since every action is delayed until the next lattice point of the action lattice [Kop92].

# 2.2 State

The notion of state is widely used in computer science, but when it comes to the exact definition of state, difficulties arise. Depending on the context of the scientist the definition varies. For example software engineers tend to describe the state of a system using the variables of the objects; system theoreticians try to explain the state of a system independently of its context.

#### 2.2.1 The Concept of State

In system theory, the notion of state is fundamental for the investigation of complex systems. In abstract system theory, the notion of state is introduced in order to separate the past from the future (decoupling). The idea is that if one knows what state the system is in, he could with assurance ascertain what the output will be [MT89, p. 45]. Hence, the state embodies all past history of the given system [MT89, p. 45]. Apparently, this definition of state by Mesarovic and Takahara is only meaningful, if the notion of past and future (time) is relevant for the considered system.

Other system theoreticians are in agreement with the above presented definition expressed in terms of time. For instance, Zadeh states informally that the *notion* of state of a system at any given time is the information needed to determine the behavior of the system from that time on [Zad69, p. 3].

By contrast, in the field of software engineering and object oriented programming languages the notion of state is closely related to the attributes of an object. In the Java programming language tutorial the state of an object is described as *everything that the software object knows* [CWH00]. This is consistent with the view of Szyperski, who explains in the context of Java that all state resides in the attributes of classes [Szy98, p. 219]. He further argues that a software component (e.g., a library) can make part of its state observable by exporting variables or inspection functions.

In the context of theoretical computer science Clarke defines the state as a *snap*shot or instantaneous description of the system that captures the values of the variables at a particular instant of time [CGP99, p. 13].

Another definition of the state of a system can be found in the DSoS (Dependable Systems of Systems) conceptual model. The model uses the concept of an internal data structure that synthesizes all cumulative effects of all receive operations at all input interfaces between the startup of the system and this given instant [GIJ<sup>+</sup>02, p. 85].

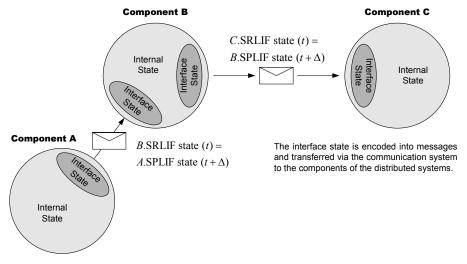

The *declared state* is the state of a subsystem, which is considered as relevant by the system designer for the future behavior of the subsystem (forward view). The *interface state* contains the history of the component that is relevant for the future behavior of the component as seen from this interface. Interface state is defined between the intervals of activity on the sparse time base [Kop92]. Interface state is a subset of the state of the component and should be accessible from the interface.

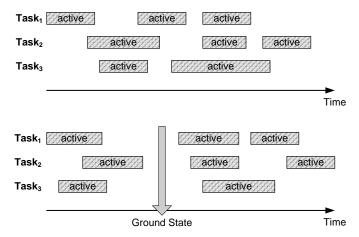

Figure 2.2: The Concept of Ground State

## 2.2.2 Ground State

The ground state of a node in a distributed system at a given level of abstraction is defined as a state where no task is active and where all communication channels are flushed, i.e. there are no messages in transit [AKC90, p. 1]. Consider a node that contains a number of concurrently executing tasks that exchange messages with each other and with the environment of the node. If a level of abstraction that considers the execution of a task as an atomic action is chosen, and the executions of the tasks are asynchronous, then the situation depicted in the upper section of Figure 2.2 can arise; at every point in real time, there is at least one active task, thus, implying that there is no point in real time when the ground state can be defined. In the lower part of Figure 2.2, there is an instant where no task is active and all the communication channels are empty, i.e. where the system is in the ground state. If a system is in the ground state, then the internal state is contained in its data structures and the program counter. The reintegration after a failure is simplified if a system periodically visits a ground state that can be used as a reintegration point [Kop97].

# 2.3 Component

A standard problem solving technique is the division of complex systems into nearlyindependent subsystems [Sim96]. This intuitive approach to manage complexity can be found in many engineering disciplines, where large systems are assembled from prefabricated components with known and validated properties. A component is regarded as a self-contained subsystem that can be used as a building block in the design of a larger system. An example of such components is the engine, gearbox, or wheel suspension in an automobile. The component can have a complex internal structure that is neither visible, nor of concern, to the user of the component. An ideal component should maintain its encapsulation when used in a larger context [KS03a].

One of the most apparent problems in the domain of computer systems relates to constructive design of large systems out of independently developed pre-validated components. In the following we investigate two different types of components and their definitions, namely *system components* and *software components*. At first various definitions of software components are presented. Most of these definitions are stated in the field of Component-Based Software Engineering (CBSE), which is concerned with the rapid assembly of software systems from pre-built components of independent vendors. The second part gives insight into the concepts of system components. A system component is a self-contained composite HW/SW subsystem that can be used as a building block in the design of a larger system. In contrast to software components, system components are time-aware and thus allow a meaningful definition of state.

#### 2.3.1 Software Component

In Component-Based Software Engineering (CBSE), which is concerned with the rapid assembly of systems from components [BW98], the opaque implementation of functionality is a fundamental idea that allows third-party composition. A component implements one or more interfaces that are imposed upon it, which reflects that the component satisfies certain obligations, so called contracts [HHG90, Hol92]. These contractual obligations ensure that independently developed components obey certain rules so that components interact (or cannot interact) in predictable ways, and can be deployed into standard build-time and run-time environments. A component-based system is based upon a small number of distinct component types, each of which plays a specialized role in a system and is described by an interface [BBBCD00]. CBSE usually sees a component as a replacement (reusable) unit like a commercial off-the-shelf commodity. The components with certified properties provide the basis for predicting the properties of systems built from components.

Various definitions of component in the context of CBSE can be found [KJH00]. Microsoft, for instance, defines a component as a piece of software, which is offering a service [WK94]. As defined by the OMG, a component is the minimal piece of functionality in a system or subsystem that can be removed without affecting the integrity of the system or subsystem [Was95]. Cuipke and Schmidt [CS96] concentrate on the context-independence of a component and D'Souza [DW99] defines components as reusable parts of software that can be adapted but not modified. Herzum and Sims [HS00] emphasize the autonomous deployment and collaboration of components. Wijnstra describes components as *units containing reusable functionality with explicit interfaces* [Wij01, p. 27].

Szyperski [Szy98] defines software components as binary units of independent production, acquisition, and deployment that interact to form a functioning system [Szy98, preface]. Insisting on independence and binary form is essential to allow

for multiple independent vendors and robust integration. Furthermore, Szyperski identifies three major forces in the field of CBSE: the OMG (corporate enterprise perspective) with CORBA-based standards, Microsoft (desktop perspective) with COM-based standards and Sun (Internet perspective) with Java-based standards. From an economic point of view Szyperski remarks that, compared with specific solutions to specific problems, components need to be carefully generalized to enable reuse in a variety of contexts. Solving a general problem rather than a specific one takes more work. Components are thus viable only if the investment in their creation is returned as a result of their deployment. In traditional software engineering processes, module development and testing is followed by systems integration and testing. This approach leaves room for errors that are merely a result of composition and which are not apparent at the level of individual components, but which should be detected during systems integration and testing. With third-party integration, the situation becomes more difficult, as integration testing of modules from different sources needs to be addressed. The resulting problem in an open market of independent component developers is the fact that the set of possible combinations is not even known to any one of the involved parties. Szyperski also addresses component safety as an important issue, namely that a component must not violate system-wide rules.

Kruchten's definition, though stated in the context of software component design, is a more general one. He defines a component as a non-trivial, nearly independent, and replaceable part of a system that fulfills a clear function in the context of a welldefined architecture. A component conforms to and provides the physical realization of a set of interfaces [Kru98, p. 1]. In a closer examination the properties of the definition are explained. The author states that a component is substitutable for any other component that realizes the same interfaces. Logical and physical cohesiveness of a component denotes a meaningful structural and/or behavioral part of a larger system. Furthermore a component represents a fundamental building block out of which systems can be designed and composed. Conformity of a component to a given interface means that it satisfies the contract specified by that interface and may be substituted in any context wherein that interface applies.

### 2.3.2 System Component

In contrast to the view of software engineering Kopetz defines a system component as a *self-contained composite hardware/softwares subsystem that can be used as a building block in the design of a larger system* [KS03a, p. 3]. In the context of embedded real-time systems a complete node seems to be the best choice for a component [Kop98], since the component-behavior can then be specified in the domains of value and time. Thus, a component is considered to be a self-contained computational element with its own hardware (processor, memory, communication interface, and interface to the controlled object) and software (application programs, operating system), which interacts with its environment by exchanging messages across Linking Interfaces (LIFs). In order to bring the advantages of component-based software engineering to embedded systems, the special domain characteristics of embedded systems have to be taken into account [MSZ01]. An ideal component should be an autonomous unit that maintains its encapsulation. Kopetz proposes various properties of such an ideal component, namely [Kop00]:

- A unit of service provision: A component must be a unit of service provision by offering services to the component's environment across a real-time service interface. In a distributed real-time system, the service consists of the timely processing and provision of the requested information.

- A unit for validation: The validation of the proper operation of a component in the value domain and in the temporal domain must be possible in isolation. The preconditions for the correct operation of the component, both in the domains of time and value, must be precisely specified in the interface specifications.

- A unit of error containment: All errors that occur inside a component must be detected before the consequences of these errors propagate across a component's interface. Otherwise, a defective component can falsify the operation of other components by the provision of corrupted output data across the component interface.

- A unit for reuse: A component should be a unit for reuse. This requires that the component has standardized interfaces to support the integration of the component in various system contexts.

- A unit of design and maintenance: A component should be a unit of design and maintenance. It is well known that system structures evolve along organization structures. If the work output of an organizational group is a nearly autonomous subsystem with well-specified interfaces, then the management of this group is simplified. The error containment boundaries around a component reduce the possibility of unforeseen consequences of software maintenance actions.

According to Kopetz an architecture is said to be *composable* with respect to a specified property if the system integration will not invalidate this property once the property has been established at the subsystem level [Kop97, p. 34]. Examples of such properties in the context of distributed real-time systems are timeliness and testability. The components are characterized by their physical parameters and the services they provide across well-specified interfaces. In a composable architecture, this integration should proceed without unintended side effects. From the point of view of the analysis of a composable architecture, it is reasonable to distinguish between the two service classes of an integrated distributed control system [Kop01, p. 227]: prior services and emerging services. A prior service of a component is the specified service that has been developed independently from the system it will be deployed. Prior services can be validated at component level and thus be available prior to the integration of the component into an integrated control system. In contrast to emerging services that result from the integration of components into a system. Such an integration generates new services that are more than the sum of the prior services.

In a distributed system, a given set of components compositionally realize emergent services by exchanging messages across LIFs. The emergent services refer to those properties of the system of components that are not explicitly properties of the components themselves, but come into existence by the interactions among the components across LIFs. Therefore, the communication system plays a central role in determining the composability of distributed computer architecture. For an architecture to be composable, it must adhere to the principles with respect to the real-time service interface as introduced in [KO02].

## 2.4 Interface

Usually an interface is referred to as a common boundary between two subsystems. Since architecture design is primarily interface design, the most important phase in the design of large system architecture is the layout and placement of the interfaces [Kop97, p. 77]. A correctly designed interface provides understandable abstractions, which capture the essential properties of the interfacing subsystems and hide irrelevant details (control, temporal, functional, and data properties).

#### 2.4.1 Software Interfaces

In software engineering, interface abstraction provides a mechanism to control the dependencies that arise between modules in a program or system [BBBCD00]. The theory is that information hiding makes modules substitutable (for example, with new versions of a component), and hence makes systems easier to change, at least insofar as module substitution is concerned. Bachmann et al. [BBBCD00] emphasize the importance to distinguish between abstract interfaces (those that are described independently of any implementation) and bound interfaces (those that are associated with an implementation) for certification, composition, and system analysis.

The idea of an *interface contract* has become prominent in CBSE research literature. A contract, as introduced in [HHG90] and extended in [Hol92], is a descriptive formal (or semiformal) language by which clauses in a programming context may be written to explicitly specify interactions among groups of objects (participants). These interface contracts are between two or more parties, which often negotiate the details of a contract before becoming signatories. Contracts prescribe normative and measurable behaviors on all signatories and can not be changed unless the changes are agreed to by all signatories. A component contract specifies a pattern of interaction rooted on that component. The contract specifies the services provided by a component and the obligations of clients and the environment needed by a component to provide these services. Contracts shift the focus from specification of

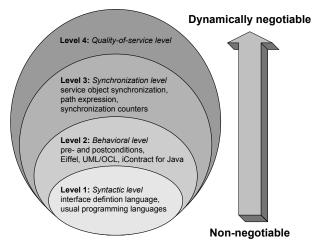

Figure 2.3: The Four Contract Levels

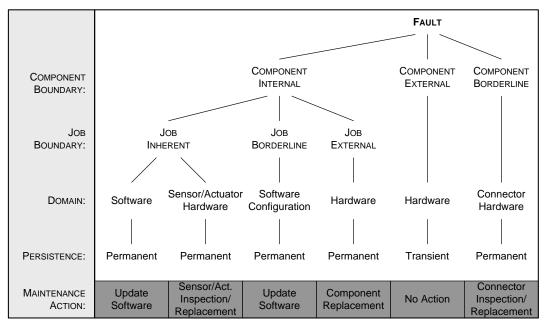

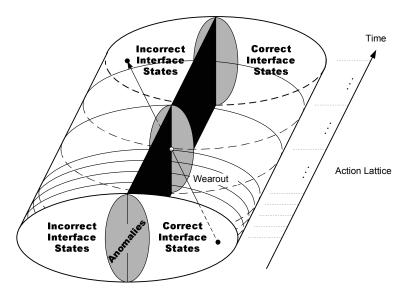

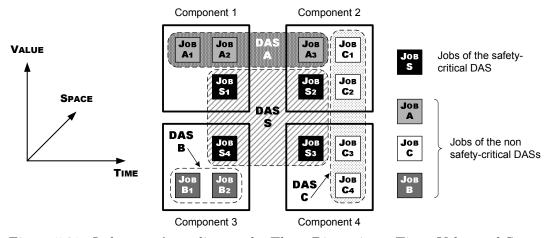

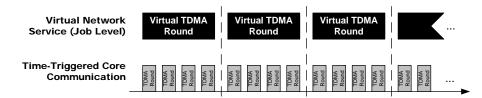

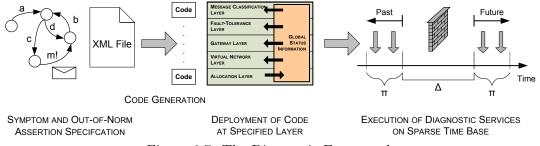

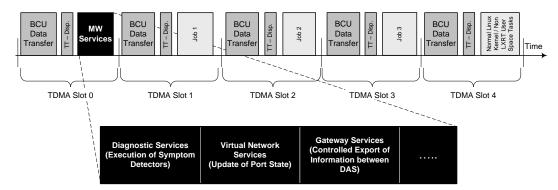

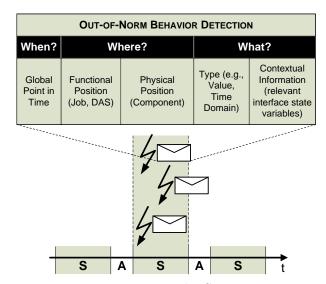

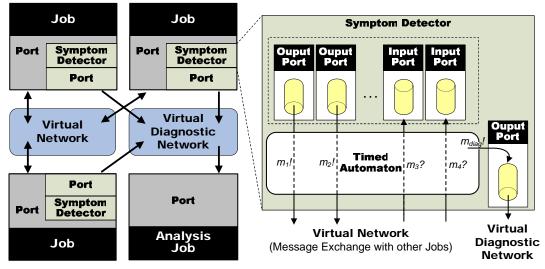

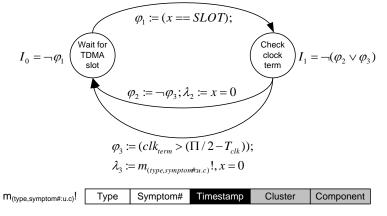

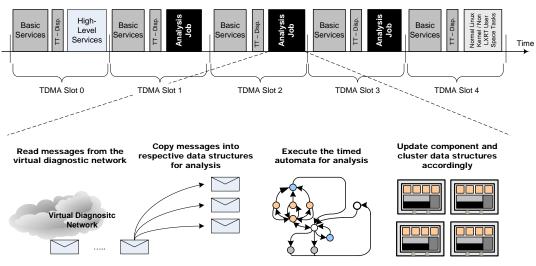

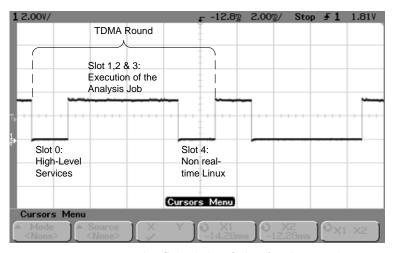

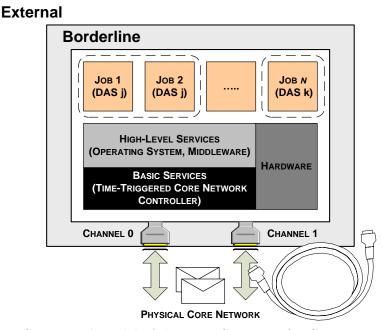

components to specification of patterns of interactions, and the mutual obligations of participants in these interactions.