Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothel der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

### Interface Design for Hardware-in-the-Loop Simulation of Real-Time Systems

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Doktors der technischen Wissenschaften

unter der Leitung von

O.Univ.-Prof. Dr. Hermann Kopetz und Dr. Wilfried Elmenreich als verantwortlich mitwirkendem Universitätsassistenten Institut für Technische Informatik 182

eingereicht an der

Technischen Universität Wien Fakultät für Informatik

von

Martin Schlager Matr. - Nr. 9725343 2641 Schottwien 103

| Wien, im Sept | ember 2007 | <br> |

|---------------|------------|------|

|               |            |      |

### Interface Design for Hardware-in-the-Loop Simulation of Real-Time Systems

#### Abstract

Hardware-in-the-Loop (HiL) simulation is a testing technique in which the environment of an (embedded) System-Under-Test (SUT) is simulated by an assigned HiL simulator. Thereby, the SUT interacts with the HiL simulator via the SUT's interface with its environment. The interaction between the SUT and the HiL simulator takes place in real time and is constrained by the temporal properties of the SUT. In the case where the SUT is a distributed system, consisting of several nearly-independent computers interacting with their environment in a collaborative way, the set-up of an HiL simulation is a non-trivial task requiring well-designed linking interfaces of the HiL simulator to enable predictable test runs.

This thesis proposes an approach towards the temporal decoupling of environmental simulation of the HiL simulator and the SUT, by using a time-triggered connection system acting as a temporal firewall. Using such an approach, it can be guaranteed that information flow between the HiL simulator and the SUT (and vice versa) is bound to a priori known latency and jitter. Furthermore, timing violations of an HiL simulation can be deterministically diagnosed and actions, avoiding detrimental consequences of such timing violations, can be initiated.

In contrast to traditional solutions to interfacing between the SUT and the HiL simulator, the presented approach allows temporal laxity of the HiL simulator, i. e., the execution of the simulation model (e. g., a Matlab/Simulink model) is individually performed by assigned components of a distributed HiL simulator while different components of the same HiL simulator are responsible for timely interfacing with the SUT.

The actual physical coupling of the SUT and the HiL simulator is established via an arbitrary transducer interface. This interface can be implemented using a physical transducer, a (standardized) digital transducer interface, or a so-called  $Smart\ Virtual\ Transducer\ (SVT)$  that mimics the behavior of a physical transducer. The thesis provides an outline of a generic HiL simulation framework, based on SVTs. The proposed framework is exemplarily applied to the verification of integrated systems.

### Schnittstellendesign für die Hardware-in-the-Loop Simulation von Echtzeitsystemen

#### Kurzfassung

Hardware-in-the-Loop (HiL) Simulation ist ein Testverfahren, bei der die Prozessumgebung eines zu testenden Systems (System-Under-Test (SUT)) durch einen HiL Simulator ersetzt wird. Dabei interagiert das SUT mit dem HiL Simulator über dieselbe Schnittstelle des SUTs, über welche das SUT mit der Umgebung interagieren würde. Diese Interaktion zwischen dem SUT und dem HiL Simulator findet in Echtzeit statt und hängt von den temporalen Eigenschaften des SUTs ab. Der Aufbau einer HiL Simulation erfordert daher einen sorgfältigen Entwurf der Schnittstellen, um vorhersagbare Testabläufe zu ermöglichen. Dies ist insbesondere dann der Fall, wenn es sich beim SUT um ein verteiltes System handelt, das sich aus mehreren voneinander (nahezu) unabhängigen, mit ihrer Umgebung interagierenden Computern zusammensetzt.

Diese Arbeit stellt einen Ansatz zur zeitlichen Entkopplung von Umgebungssimulation und SUT mittels zeitgesteuertem Adaptersystem (Connection System) und kontrollfehlerfreien Schnittstellen (Temporal Firewall) vor. Dadurch kann garantiert werden, dass der Informationsfluss von der Umgebungssimulation des HiL Simulators zum SUT (und vice versa) durch vorab bekannte Wartezeiten (Latencies) und Schwankungen (Jitter) bestimmt ist. Weiters können Zeitüberschreitungen (Timing Violations) einer HiL Simulation diagnostiziert, und negative Konsequenzen solcher Zeitüberschreitungen vermieden werden.

Im Vergleich zu traditionellen Lösungen vereinfacht der vorgestellte Ansatz die zeitlich korrekte Ausführung eines Simulationsmodells. So kann beispielsweise die (Schwankungen unterworfene) Berechnung eines Matlab/Simulink Modells auf einer Komponente eines verteilten HiL Simulators ausgeführt werden, während weitere Komponenten für die zeitgerechte Interaktion mit dem SUT verantwortlich sind.

Die tatsächliche physikalische Anbindung des SUTs an den HiL Simulator kann über verschiedene Messwandlerschnittstellen (*Transducer Interfaces*) aufgebaut werden. Diese Schnittstellen können in Form eines physikalisch existierenden Messwandlers, einer (standardisierten) digitalen Messwandlerschnittstelle, oder einer so genannten *Smart Virtual Transducer (SVT)* Komponente realisiert werden. Diese Arbeit stellt ein – auf der Verwendung von SVTs basierendes – HiL Simulationssystem, sowie die Verifikation von integrierten Systemen unter Verwendung dieses Simulationssystems vor.

#### Danksagung

Ich möchte mich bei meinem Betreuer und Institutsvorstand O.Univ.Prof. Dr. Hermann Kopetz bedanken, der mir ermöglichte, diese Arbeit im äußerst interessanten Arbeitsfeld des Instituts für technische Informatik der TU Wien zu verfassen und mir in ausgesprochen konstruktiver Arbeitsatmosphäre mit vielen wertvollen Anregungen zur Seite stand.

Ein großes Dankeschön möchte ich insbesondere auch meinem Kollegen, Wilfried Elmenreich, aussprechen, der durch wichtige Ideen, zahlreiche Diskussionen und kritische inhaltliche Auseinandersetzung mit dem Thema einen wesentlichen Einfluss auf die vorliegende Arbeit hatte. Außerdem möchte ich mich bei meinem zweiten Begutachter, Univ.Prof. Dr. Johann Blieberger, für wertvolle Anregungen und Tipps zur vorliegenden Arbeit bedanken.

Danken möchte ich auch zahlreichen Kollegen am Institut, die durch sehr gute Gespräche und freundschaftliche Unterstützung zum Resultat dieser Arbeit beigetragen haben. Namentlich bedanken möchte ich mich besonders bei Roman Obermaisser für die exzellente Zusammenarbeit im Bereich der Validierung integrierter Systeme. Weiters danke ich Gerhard Burger, Florian Skopik und Michael Wihsböck für die Implementierung der Case Studies, sowie Wilfried Elmenreich, Marlene Kritz, Ingomar Wenzel und Martina Sebastian für das gründliche Korrekturlesen der Arbeit. Bei Maria Ochsenreiter möchte ich mich für die großartige organisatorische Unterstützung im Laufe der Jahre sehr herzlich bedanken.

Mein Dank gilt weiters der Österreichischen Akademie der Wissenschaften, die diese Arbeit im Rahmen eines einjährigen Dissertationsstipendiums (DOC) großzügig unterstützte, sowie meinen Vorgesetzten und Kollegen in der Firma TTTech Computertechnik AG, namentlich Judith Sattlberger, Stefan Poledna, Tibor Gajdoš und Georg Stöger, die mir insbesondere im Zuge der Fertigstellung dieser Arbeit mit einem Höchstmaß an Flexibilität entgegengekommen sind.

Bei meinen Großeltern, meinen Eltern, Waltraud und Franz, und meinen Geschwistern, Thomas und Nicole, möchte ich mich an dieser Stelle ganz besonders bedanken. Sie haben mir durch ihre Liebe über Jahrzehnte ermöglicht, die Grundlage für diese Arbeit zu schaffen und standen mir stets unterstützend zur Seite. Weiters möchte ich Ingomar Wenzel, Jacek Ratzinger, Daniela Woditschka, Barbara Huber, Gerhard Krizovsky, Alexander Rudolf, Bernhard Rumpler und Natascha Vecsera meinen Dank für eine großartige Zeit, schöne gemeinsame Hobbys und langjährige freundschaftliche Verbundenheit aussprechen.

Diese Arbeit ist meinem Großvater, August Spanring, gewidmet.

# Contents

| 1 | $\mathbf{Intr}$ | oducti  | on                                           | 1  |

|---|-----------------|---------|----------------------------------------------|----|

|   | 1.1             | Motiva  | ation and Objectives                         | 1  |

|   | 1.2             | Relate  | d Work                                       | 3  |

|   | 1.3             | Contri  | bution                                       | 4  |

|   | 1.4             | Struct  | ure of the Thesis                            | 5  |

| 2 | Bas             | ic Teri | ns and Concepts                              | 7  |

|   | 2.1             | Real-T  | Time Systems                                 | 7  |

|   |                 | 2.1.1   | Classification of Real-Time Systems          | 8  |

|   |                 | 2.1.2   | Model of Time                                | 10 |

|   |                 | 2.1.3   | Messages                                     | 11 |

|   |                 | 2.1.4   | Characterization of Information Content      | 11 |

|   |                 | 2.1.5   | Distributed Systems                          | 13 |

|   | 2.2             | Interfa | ices                                         | 18 |

|   |                 | 2.2.1   | Interface State                              | 19 |

|   |                 | 2.2.2   | Interface Types                              | 20 |

|   |                 | 2.2.3   | High-Level versus Low-Level Interface Issues | 21 |

|   |                 | 2.2.4   | Temporal Firewall                            | 22 |

|   |                 | 2.2.5   | Connection System                            | 23 |

|   | 2.3             | Simula  | ation                                        | 23 |

|   |                 | 2.3.1   | Classification of Simulation                 | 25 |

|   |                 | 2.3.2   | HiL Simulation                               | 27 |

|   |                 | 2.3.3   | Validation and Verification                  | 27 |

|   | 2.4             | Smart   | Transducer (ST)                              | 31 |

|   |                 | 2.4.1   | Smart Transducer Interface (STI)             | 32 |

|   |                 | 2.4.2   | TTP/A – Principles of Operation              | 33 |

|   | 2.5             | Chapt   | er Summary                                   | 35 |

| 3 | ${ m HiL}$      | Simul   | ation                                        | 37 |

|   | 3 1             | Struct  | ure and Constituting Elements                | 37 |

|   |      | 3.1.1   | Elements of an HiL Simulator                                                                                                                                                                          | 37 |

|---|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 3.1.2   | Open-Loop versus Closed-Loop HiL Simulation                                                                                                                                                           | 40 |

|   |      | 3.1.3   | Developing an HiL Simulation                                                                                                                                                                          | 40 |

|   |      | 3.1.4   | $\label{eq:Multirate HiL Simulation} \mbox{Multirate HiL Simulation} $                                                                                                                                | 41 |

|   |      | 3.1.5   | Coupling of HiL Simulator and SUT $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                               | 42 |

|   |      | 3.1.6   | An Example                                                                                                                                                                                            | 43 |

|   | 3.2  | Requir  | rements                                                                                                                                                                                               | 46 |

|   |      | 3.2.1   | Technical Requirements                                                                                                                                                                                | 47 |

|   |      | 3.2.2   | Economic Requirements                                                                                                                                                                                 | 50 |

|   | 3.3  | Existin | ng Solutions                                                                                                                                                                                          | 51 |

|   |      | 3.3.1   | DSP Builder (Altera)                                                                                                                                                                                  | 51 |

|   |      | 3.3.2   | $LabVIEW\ (NI)\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 52 |

|   |      | 3.3.3   | Pi Autosim (Pi Technology)                                                                                                                                                                            | 53 |

|   |      | 3.3.4   | RTDS Simulator (RTDS Technologies)                                                                                                                                                                    | 54 |

|   |      | 3.3.5   | RT-LAB (Opal-RT) $\dots$                                                                                                                                                                              | 55 |

|   |      | 3.3.6   | rt<br>X Simulator (ADI)                                                                                                                                                                               | 56 |

|   |      | 3.3.7   | Simulator Mid-/Full-Size (dSpace) $\dots \dots \dots \dots$                                                                                                                                           | 57 |

|   |      | 3.3.8   | Tanto2 Test (Hitex)                                                                                                                                                                                   | 57 |

|   |      | 3.3.9   | xPC Target (MathWorks)                                                                                                                                                                                | 58 |

|   |      | 3.3.10  | Comparing the Existing Solutions                                                                                                                                                                      | 59 |

|   | 3.4  | Chapte  | er Summary                                                                                                                                                                                            | 61 |

| 4 | Inte | rface I | Design for HiL Simulation                                                                                                                                                                             | 63 |

|   | 4.1  | Ration  | aale                                                                                                                                                                                                  | 63 |

|   |      | 4.1.1   | Deterministic Interaction                                                                                                                                                                             | 63 |

|   |      | 4.1.2   | Distributed HiL Simulator                                                                                                                                                                             | 64 |

|   |      | 4.1.3   | Arbitrary Transducer Interfaces                                                                                                                                                                       | 66 |

|   |      | 4.1.4   | Monitoring $\ldots$                                                                                                                                                                                   | 69 |

|   | 4.2  | Archit  | ecture                                                                                                                                                                                                | 70 |

|   |      | 4.2.1   | Structure of HiL Simulator                                                                                                                                                                            | 71 |

|   |      | 4.2.2   | $\label{eq:hill} \mbox{HiL Simulator Node Interaction} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                                        | 72 |

|   |      | 4.2.3   | Backend Simulation Component (BSC)                                                                                                                                                                    | 73 |

|   |      | 4.2.4   | Frontend Simulation Component (FSC) $\dots \dots \dots$                                                                                                                                               | 73 |

|   | 4.3  | Smart   | Virtual Transducer (SVT) $\hdots$                                                                                                                                                                     | 75 |

|   |      | 4.3.1   | Structure                                                                                                                                                                                             | 75 |

|   |      | 4.3.2   | Interfaces                                                                                                                                                                                            | 76 |

|   |      | 122     | Types of SVTs                                                                                                                                                                                         | 77 |

|   |     | 4.3.4   | Prototypical Realization                                      |

|---|-----|---------|---------------------------------------------------------------|

|   | 4.4 | Revisi  | ng the Rationale                                              |

|   |     | 4.4.1   | Deterministic Interaction                                     |

|   |     | 4.4.2   | Distributed HiL Simulation System                             |

|   |     | 4.4.3   | Arbitrary Transducer Interfaces                               |

|   |     | 4.4.4   | Monitoring and Configuration                                  |

|   | 4.5 | Chapt   | zer Summary                                                   |

| 5 | Tes | ting of | Fan Integrated System 83                                      |

|   | 5.1 | Integr  | ated Architecture                                             |

|   |     | 5.1.1   | System Structure                                              |

|   |     | 5.1.2   | Communication Network                                         |

|   |     | 5.1.3   | Node Computers                                                |

|   |     | 5.1.4   | Environment                                                   |

|   | 5.2 | X-in-t  | he-Loop Testing                                               |

|   |     | 5.2.1   | Model-in-the-Loop (MiL)                                       |

|   |     | 5.2.2   | Software-in-the-Loop (SiL)                                    |

|   |     | 5.2.3   | Hardware-in-the-Loop (HiL)                                    |

|   | 5.3 | Virtua  | al Integration                                                |

|   |     | 5.3.1   | Structure of Virtual Integration Framework 89                 |

|   |     | 5.3.2   | Inputs to the Virtual Integration Framework 90                |

|   |     | 5.3.3   | Simulation on Virtual Integration Platform                    |

|   | 5.4 | HiL T   | esting                                                        |

|   |     | 5.4.1   | HiL Simulation Framework                                      |

|   |     | 5.4.2   | HiL Simulation with an Integrated System-Under-Test (ISUT) 96 |

|   |     | 5.4.3   | Exemplary Application                                         |

|   | 5.5 | Chapt   | ser Summary                                                   |

| 6 | Cas | se Stud | lies 101                                                      |

|   | 6.1 | Digita  | l Smart Transducer Gateway                                    |

|   |     | 6.1.1   | Problem Statement                                             |

|   |     | 6.1.2   | Elements                                                      |

|   |     | 6.1.3   | Implementation                                                |

|   |     | 6.1.4   | Conclusion                                                    |

|   | 6.2 | Contr   | ol Path Simulation                                            |

|   |     | 6.2.1   | Problem Statement                                             |

|   |     | 6.2.2   | Elements                                                      |

|   |     | 6.2.3   | Implementation                                                |

|               |                         | 6.2.4                     | Conclusion         |  |  |  |     | 113        |

|---------------|-------------------------|---------------------------|--------------------|--|--|--|-----|------------|

|               | 6.3                     | Rear P                    | Parking System     |  |  |  |     | 114        |

|               |                         | 6.3.1                     | Problem Statement  |  |  |  |     | 114        |

|               |                         | 6.3.2                     | Elements           |  |  |  |     | 115        |

|               |                         | 6.3.3                     | Implementation     |  |  |  |     | 116        |

|               |                         | 6.3.4                     | Conclusion         |  |  |  |     | 117        |

|               | 6.4                     | Chapte                    | er Summary         |  |  |  |     | 117        |

| 7             | Con                     | clusion                   | n                  |  |  |  |     | 119        |

|               | 7.1                     | HiL Si                    | mulation Framework |  |  |  |     | 119        |

|               | 7.2                     | Smart                     | Virtual Transducer |  |  |  |     | 120        |

|               | 7.3                     | Outloo                    | ok                 |  |  |  |     | 120        |

| Li            | st of                   | Acron                     | yms                |  |  |  |     | <b>121</b> |

| Bi            | bliog                   | raphy                     |                    |  |  |  |     | 125        |

| $\mathbf{Li}$ | List of Publications 13 |                           |                    |  |  |  | 139 |            |

| Cı            | ırricı                  | ılum $oldsymbol{	ext{V}}$ | Vitae Vitae        |  |  |  | :   | 141        |

# List of Figures

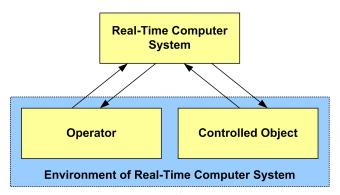

| 2.1  | Real-time system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

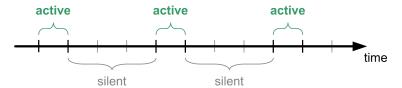

| 2.2  | Sparse time base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

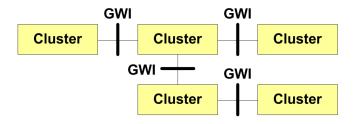

| 2.3  | Multi-cluster system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 |

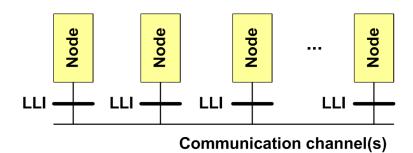

| 2.4  | Cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |

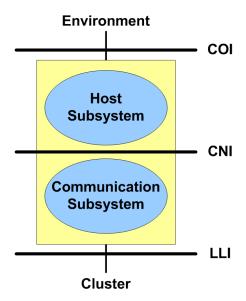

| 2.5  | Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

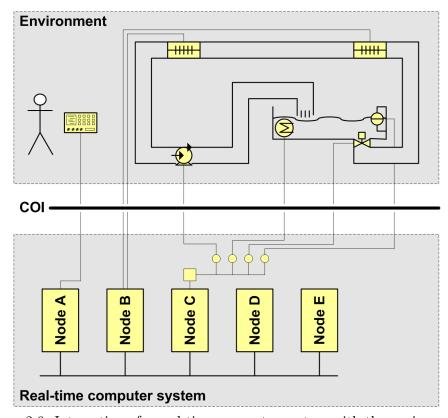

| 2.6  | Interaction of a real-time computer system with the environment $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

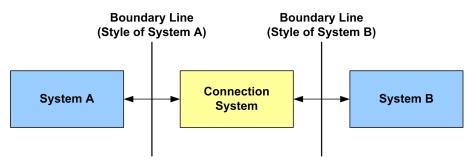

| 2.7  | Connection system with two boundary lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 |

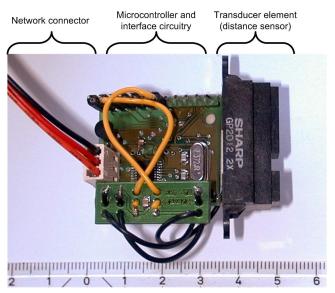

| 2.8  | Smart Transducer (Atmel 4433 microcontroller and Sharp IR distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | sensor, scale in cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32 |

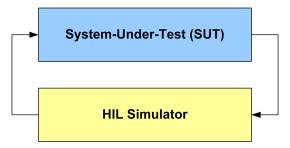

| 3.1  | Basic elements of an HiL simulation system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

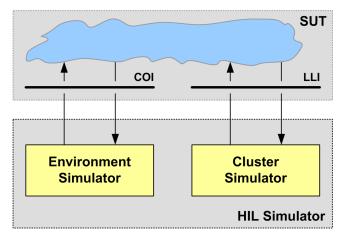

| 3.2  | Basic building blocks of an HiL simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

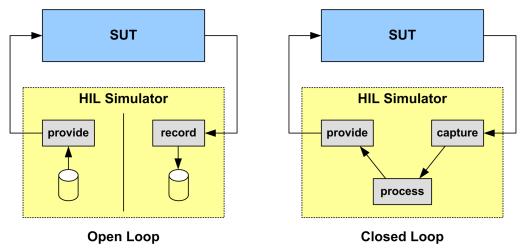

| 3.3  | Open-loop versus closed-loop HiL simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

| 3.4  | $\label{eq:Multirate HiL simulation} \mbox{Multirate HiL simulation}  \dots  $ | 42 |

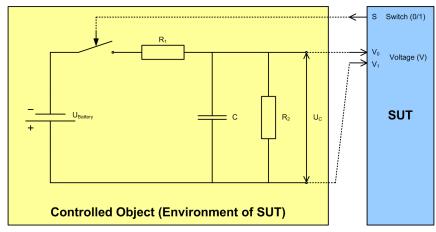

| 3.5  | Charging and discharging a capacitor (C) $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |

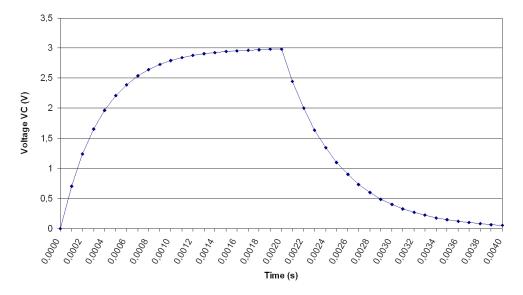

| 3.6  | Voltage characteristic $(U_C(t))$ of capacitor $(C)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45 |

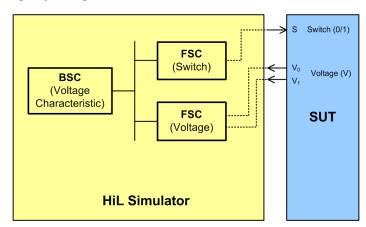

| 3.7  | Exemplary HiL simulator setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45 |

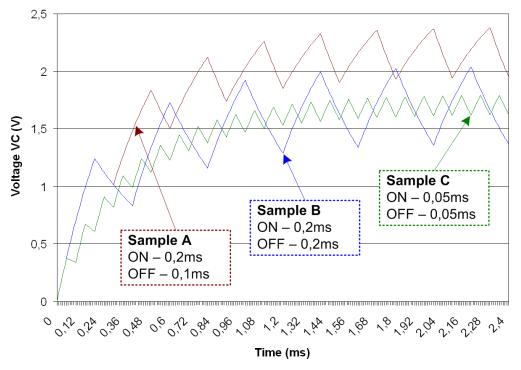

| 3.8  | Voltage characteristic $(U_C(t))$ of capacitor (C) with different switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

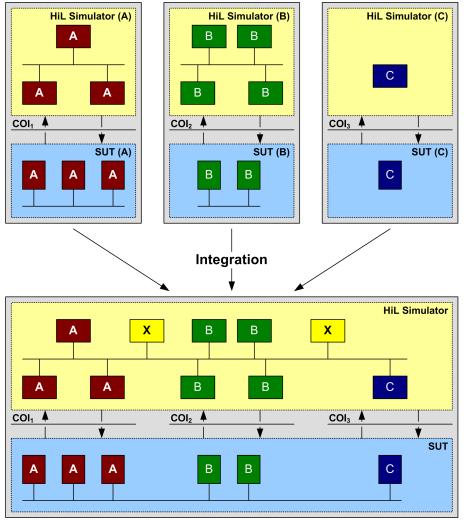

| 4.1  | Integration of different HiL simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65 |

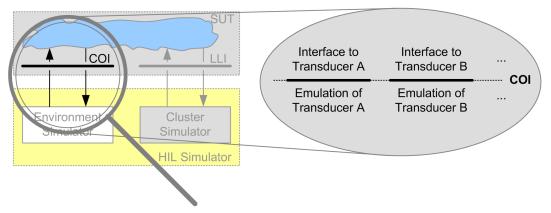

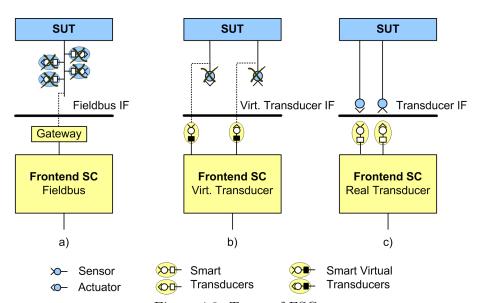

| 4.2  | Physical coupling across transducer interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67 |

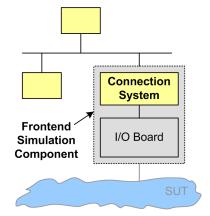

| 4.3  | Connection of a (legacy) I/O board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68 |

| 4.4  | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70 |

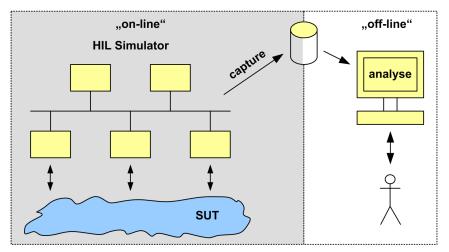

| 4.5  | Post simulation analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70 |

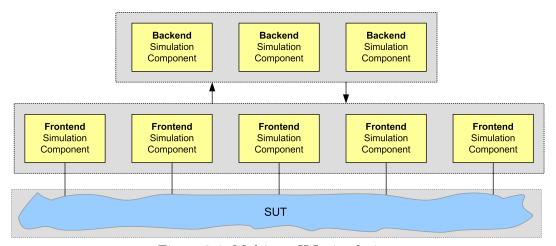

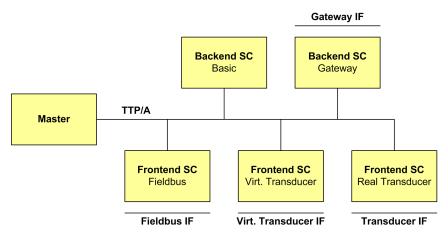

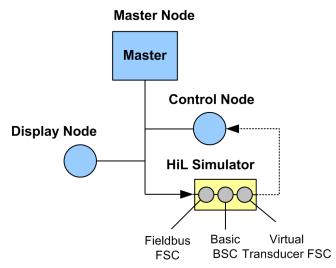

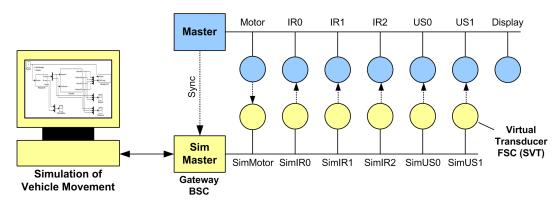

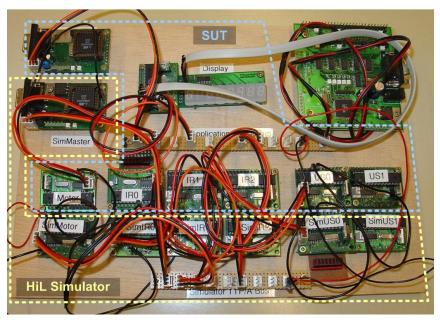

| 4.6  | Distributed HiL simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72 |

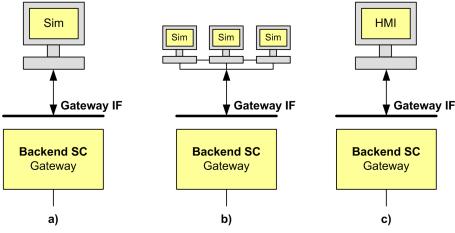

| 4.7  | Types of gateway Backend Simulation Components (BSCs) $\ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74 |

| 4.8  | Types of Frontend Simulation Components (FSCs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74 |

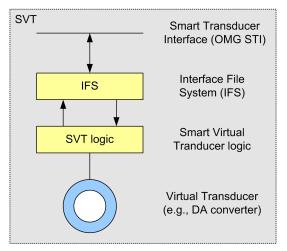

| 4.9  | Elements of an SVT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

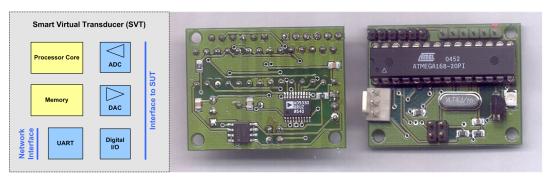

| 4.10 | Block diagram and prototype of an SVT with D/A converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78 |

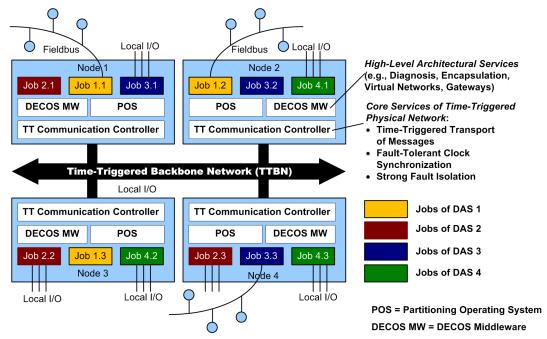

| 5.1  | Distributed system in the Dependable Embedded COmponents and                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Systems (DECOS) system architecture                                                                                                                       |

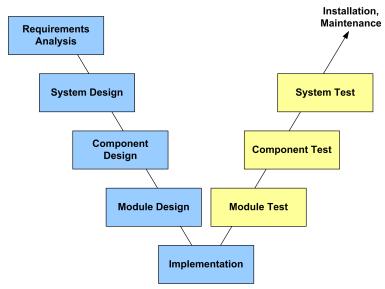

| 5.2  | V-model                                                                                                                                                   |

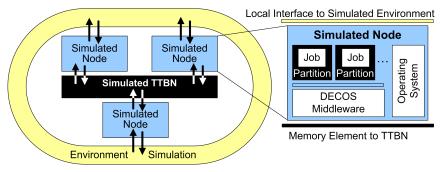

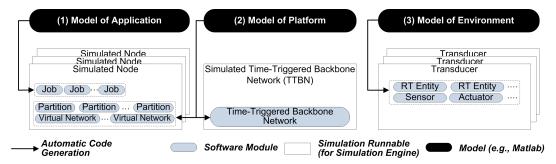

| 5.3  | System model of the simulated real-time system                                                                                                            |

| 5.4  | Model-based integration on virtual integration platform 90                                                                                                |

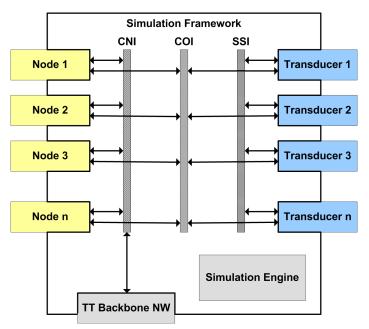

| 5.5  | Simulation framework                                                                                                                                      |

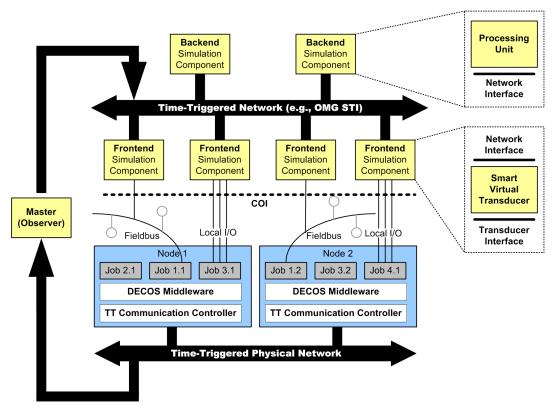

| 5.6  | HiL simulation with an integrated system                                                                                                                  |

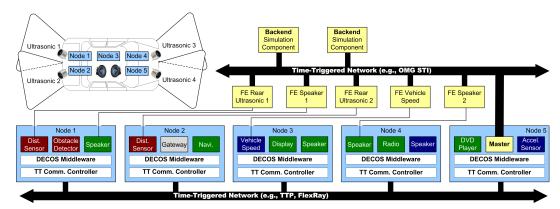

| 5.7  | Exemplary integrated system with HiL simulation                                                                                                           |

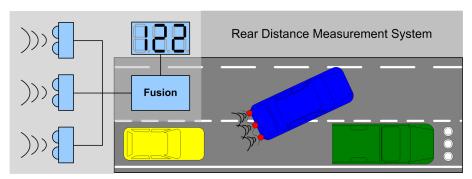

| 6.1  | Rear distance measurement system                                                                                                                          |

| 6.2  | HiL simulation of rear distance measurement system                                                                                                        |

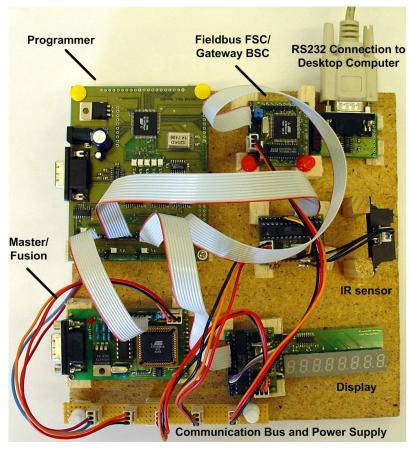

| 6.3  | Physical setup of rear distance measurement system                                                                                                        |

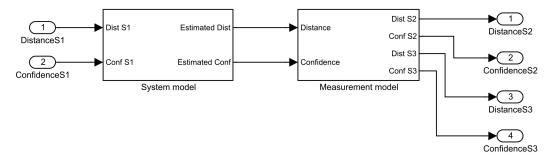

| 6.4  | Simulation block                                                                                                                                          |

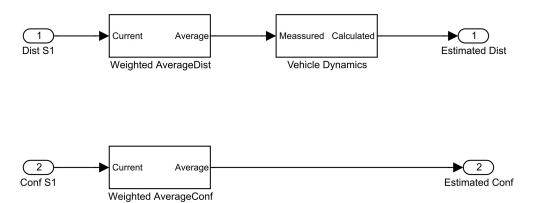

| 6.5  | System model block                                                                                                                                        |

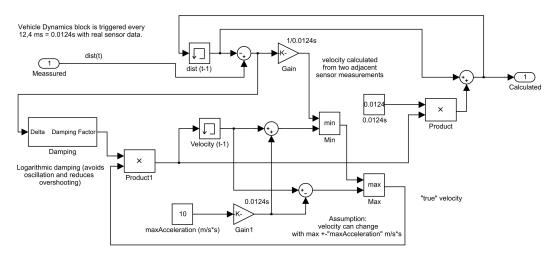

| 6.6  | Vehicle dynamics block                                                                                                                                    |

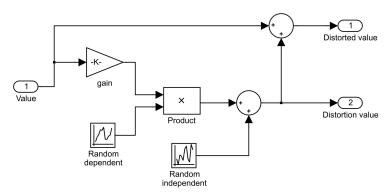

| 6.7  | Distortion block                                                                                                                                          |

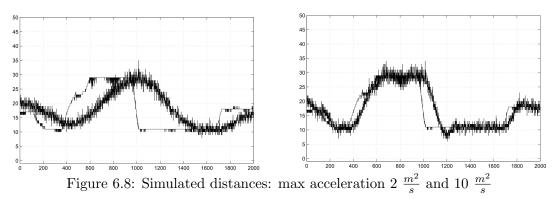

| 6.8  | Simulated distances: max acceleration $2 \frac{m^2}{s}$ and $10 \frac{m^2}{s} \dots \dots \dots \dots 107$                                                |

| 6.9  | Simulated disturbances: dependent and independent 107                                                                                                     |

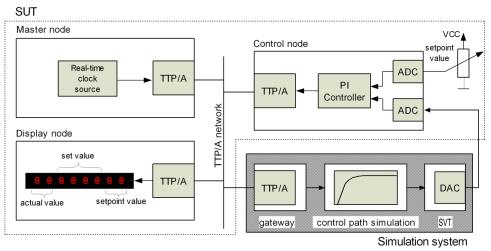

| 6.10 | Control path simulation system                                                                                                                            |

| 6.11 | HiL simulation of control path system $\dots \dots \dots$ |

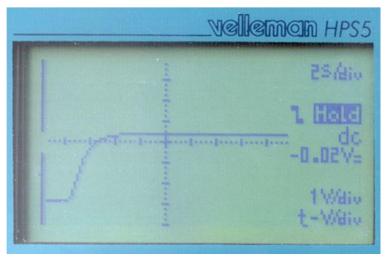

| 6.12 | Step response without controller (set value = setpoint value) $\dots \dots 113$                                                                           |

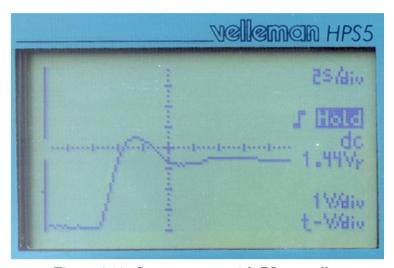

| 6.13 | Step response with PI controller                                                                                                                          |

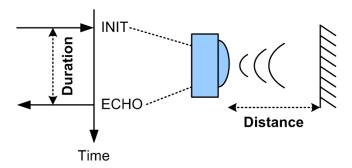

| 6.14 | Distance measurement with an ultra-sonic sensor                                                                                                           |

| 6.15 | HiL simulation of rear parking system                                                                                                                     |

| 6.16 | Physical setup of rear parking system                                                                                                                     |

# List of Tables

| 2.1 | Message classification $[JKK^+02]$    | 12  |

|-----|---------------------------------------|-----|

| 3.1 | Comparison of HiL simulation products | 60  |

| 6.1 | Cluster schedule                      | 112 |

### Chapter 1

### Introduction

Within the last decades, major advances in the semiconductor industry [EKRZ04, Fro04] have enabled the widespread application of embedded real-time systems. These systems have become an immanent part of our daily lives and can be found in many different domains such as the manufacturing, aerospace, automotive, railway, and consumer electronics markets. At present, embedded real-time systems contribute to a significant share of the innovations within these markets.

Hardware-in-the-Loop (HiL) simulation is a commonly used technique for validating embedded real-time systems prior to their actual deployment. An HiL simulation is an operational configuration of a System-Under-Test (SUT) and its respective environment. The SUT is (part of) a real-time system and can be a single embedded controller or a distributed system.

The application of HiL simulation as a validation technique of an embedded real-time system thrives on the fact that HiL simulation is closer to reality than any other simulation technique (e.g., Software-in-the-Loop (SiL)). HiL simulation makes it possible to test the system in rare but potentially hazardous situations without building costly prototypes and without endangering humans or the natural environment.

The construction of sophisticated HiL simulation systems is particularly relevant for embedded real-time systems that are used for safety-related tasks, e.g., fly-by-wire. Safety-related real-time systems must guarantee correct behavior in the presence of faults – even if the occurrence of these faults is very unlikely. The aerospace industry is an important innovation driver for safety-related real-time systems. These systems have been used in airborne equipment for many years. Recently, the auto-motive industry has also started employing safety-related systems.

#### 1.1 Motivation and Objectives

The development of a safety-related real-time system involves verification and validation techniques ensuring sufficient trust in the reliability of the system. As part of

validation, dynamic testing aims to remove errors within a system prior to its final deployment.

However, it is often difficult to test a real-time computer system performing control tasks in its natural environment because the conditions of the environment circumvent an accurate observation of the real-time systems interfaces. Furthermore, it may be very costly or even impossible to establish certain test conditions in the physical process environment of the real-time computer system.

Real-time simulation of the environment of a real-time computer system through a computer program as discussed within this thesis allows the observation and systematic modification of many relevant parameters. HiL simulation includes the actual physical real-time computer system and a simulation of the environment (of this real-time computer system). Thereby, an HiL simulator executes a model in real time which represents the behavior of the environment (i. e., traces of significant state changes at the interface between the environment and the real-time computer system). The interaction between the real-time computer system and the environmental simulation is constrained by properties of the real-time system, as well as by physical properties of the employed hardware.

HiL simulation is an approach that has been introduced by the aerospace and defense industries in the 1950s [NBAR04]. At this time, the high cost of HiL technology hindered its widespread use. During the past decades, accessibility of powerful computing resources to virtually every engineer and decreasing prices of simulation hardware led to adoption of HiL simulation to further domains such as industrial control applications or automotive systems.

Our aim is to introduce an HiL simulation framework that offers an instrument for the construction of predictable, cost effective, component based HiL simulators that can be applied in different industrial domains. A high potential for cost reduction through improved simulation and test techniques exists particularly in the automotive industry, which is due to large production quantity and enormous cost implications of recalls. Furthermore, decreasing development cycles, i.e., shorter time-to-market, and stringent cost limitations within this industry require novel development approaches in order to stay competitive [VDA03].

As outlined in [SEW06], the benefits of HiL simulation for the development of real-time systems can be summarized as follows:

- Testing of early system prototypes in a simulated environment becomes possible.

- An artificial environmental situation can be constructed that is in line with a defined test scenario.

- Effective monitoring is possible because control values from the SUT are received by the environment simulator. These control values can be further processed or recorded.

- Once a simulation is set-up, it is possible to perform a large number of tests without significant cost implications.

1 Introduction 1.2 Related Work

• It is possible to develop a real-time system and to perform tests, even if the environment, i.e., the controlled object, is not accessible during development.

- It is possible to test the behavior of a real-time system in hazardous situations. In the real environment it could be very costly (e.g., crash test) or not even feasible/acceptable (e.g., emergency actions of an aircraft during flight) to guide the system into such situations.

- HiL simulation supports regression testing, i.e., different versions of a realtime system can be tested using the same test conditions in order to uncover regression bugs.

#### 1.2 Related Work

This thesis builds on two main areas of research: real-time systems and simulation. Both areas have been well covered within the scientific literature. Thus, a huge number of both, theoretical as well as application oriented publications is available.

A comprehensive summary on concepts regarding the design and analysis of real-time systems can be found in [Kop97, Liu00, Lap04]. With regard to dependable real-time systems, a fundamental study on the concepts of dependability is presented in [Lap92, ALRL04]. A system architecture for the construction of large dependable real-time systems is given by the Time-Triggered Architecture (TTA) [KB03]. The design of interfaces for real-time systems is tackled in [Krü97, KFMN99, KS03] and extensively discussed in the EU funded project Dependable Systems of Systems (DSoS) [AFI+00, JKK+02].

General concepts of simulation are comprehensively summarized in [Law06]. In [BCNN01] emphasis is put on discrete system simulation. Even the subarea of (real-time) HiL simulation and its application is very well covered in both, academia and industry, e. g., in [NI03, NBAR04, WLD+05, BSS05].

However, up to now there is a lack of research particularly focusing on interface design for HiL simulation. Current approaches largely target at improving the signal quality during an HiL simulation. For example various interfacing schemes for HiL simulation of power electronics applications are presented in [MFL<sup>+</sup>05].

In order to increase signal accuracy during an HiL simulation, a dual time step simulation method is proposed in [LGDL06, GLH06]. Thereby, a Field Programmable Gate Array (FPGA) is used with very small time steps for handling a switching circuit while the remaining simulation is executed by a conventional processor at a much larger time step. In [Jim05] an approach is presented that uses an averaging method to improve accurate acquisition of signals whilst generating realistic and fast feedback signals.

The HiL simulation methods mentioned in the previous paragraphs as well as commercially available products such as the dSpace Simulator<sup>1</sup> or the Opal RT-

<sup>&</sup>lt;sup>1</sup>http://www.dspace.com

1.3 Contribution 1 Introduction

LAB<sup>2</sup> aim to improve the accuracy of the coupling between the simulator and the SUT by providing fast devices (FPGAs).

Furthermore, many HiL simulation approaches focus on testing a single controller and only few solutions exist that explicitly target at HiL testing of a large distributed real-time system. In chapter 3, section 3.3 an analysis of commercially available HiL simulators is provided.

Simulation of the environment of a time-triggered real-time system is addressed through the implementation of a distributed discrete time environment simulator as outlined in [Sch95], and by research on cluster simulation [FRB97, Gal99]. In [Sch95], the need for interface tests is mentioned with respect to interfaces used for the coupling between the environment simulator and the SUT. Such tests require well specified interfaces.

#### 1.3 Contribution

This thesis outlines the structure and the constituting elements of an HiL simulation framework placing particular emphasis on predictable interaction between the HiL simulator and the SUT. Thus, a distinction between components of an HiL simulator performing a simulation of the environment of an SUT, and components that are being used to couple the HiL simulator and the SUT, is drawn.

The thesis elaborates on different approaches for establishing the physical coupling between SUT and HiL. Thereby, the new concept of a *Smart Virtual Transducer* (SVT) and the prototype implementation of an SVT are shown. An SVT is a hardware/software component employed to replace a physical sensor or actuator of the SUT. An SVT supports predictable interactions between an HiL simulator and an SUT via an arbitrary transducer interface.

Furthermore, the thesis outlines a possible application of the HiL simulation framework to large integrated systems. Therefore, it is exemplarily demonstrated how an HiL simulation can be used as part of an X-in-the-Loop testing process that encompasses Model-in-the-Loop (MiL), SiL, and HiL. Moreover, a simulation framework for virtual integration of an integrated system as part of SiL tests is presented.

In the presented HiL simulation framework, the execution of the simulation model (e.g., a Matlab/Simulink model) is individually performed by assigned components of a distributed HiL simulator while different components of the same HiL simulator are responsible for timely interfacing with the SUT. As an advantageous result of this separation, the execution of the simulation model is temporally decoupled from precise instants of interaction with the SUT as long as bound maximum execution times of single simulation steps are guaranteed.

The thesis presents a distributed HiL simulator that is (1) based on a timetriggered communication and process model and that (2) involves a strict separation of the execution of the simulation model and the interaction between this simulation

<sup>&</sup>lt;sup>2</sup>http://www.opal-rt.com

model and the SUT. The benefits of this approach are given as follows:

- The cognitive complexity of a simulation model (i. e., the amount of cognitive resources that are needed to understand the model [RS07]) is reduced by a decreased number of system variables and their dependencies. This is achieved by the introduction of loosely coupled HiL simulator components that interact across well-specified interfaces.

- It is possible to implement the HiL simulation model with discrete simulation methods that are in accordance to the non-blocking *simple task* (S task) [Kop97] execution scheme.

- Based on the concept of a temporal firewall [KN97], temporal laxity of the HiL simulator is facilitated. Temporal laxity of the HiL simulator means that jitter of a single simulation step does not influence the predictable instants of interaction between the HiL simulator and the SUT as long as the execution of a single simulation step is constrained by an upper-bound Worst Case Execution Time (WCET).

#### 1.4 Structure of the Thesis

The remainder of this thesis is structured as follows:

- Chapter 2 comprises an investigation on the basic terms and concepts that constitute the fundamentals of this thesis. Chapter 2 is partitioned into four subsections focusing on the relevant entities of real-time systems, interfaces, simulation, and Smart Transducers (STs), respectively.