The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

## Measurement-Based Timing Analysis of Applications written in ANSI-C

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Doktors der technischen Wissenschaften

unter der Leitung von

Univ.-Prof. Dr. Peter Puschner Institut für Technische Informatik 182

eingereicht an der

Technischen Universität Wien Fakultät für Informatik

von

Bernhard Rieder Matr.-Nr. 9325898 Forstgasse 16, 5500 Bischofshofen

Wien, im April 2009

# Measurement-Based Timing Analysis of Aplications written in ANSI-C

Since the development of the first electronic engine control systems the applications of electronic systems in cars have steadily increased. Currently there is a shift from mechanical safety-critical systems to networks of safety-critical embedded real-time systems which provide the potential for increased functionality and huge monetary savings. The increased functionality comes at the cost of increased complexity. The applications running in a modern luxury car come close to a total of 100 million lines of source code, distributed over networks of 70-100 microprocessor electronic control units (ECU) from different vendors.

To minimize errors in the design standardized architectures like AUTOSAR and communication buses like  $\operatorname{FlexRay}^{\mathbb{M}}$  or CAN are used to ensure the interoperability of modules. Model-checkers, verification and profiling tools are used to analyze the software of individual modules. The aspect of time is often underrated and many faults of control systems are a direct result of timing errors. During the last years a few timing analysis tools have emerged. Some of them use formal methods to calculate the execution-time of a task-based on a processor model, other tools use measurements to determine an estimate for the worstcase execution-time (WCET). Hybrid WCET analysis tools combine static analysis of the application source code, which makes this part of the analysis hardware independent, with execution-time measurements carried out on the target hardware to generate a hardware specific timing model of the analyzed application.

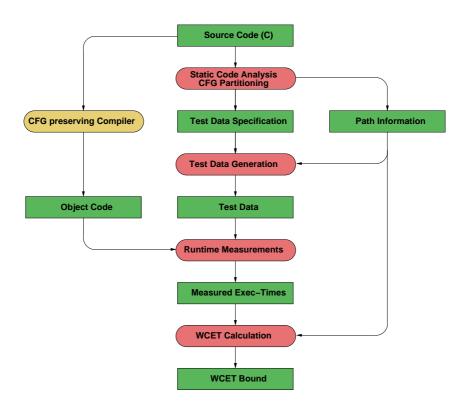

This work extends the hybrid timing analysis approach introduced during the MoDECS project to support loops, function calls and control-flow in logic AND and OR expressions which are required to measure the execution-time of industrial real-time applications. The revised hybrid WCET analysis approach comprises the following steps:

Static analysis is used on the ANSI-C source code to examine the program structure. C is commonly used in the implementation of control systems and the use of a high level language as input makes the analysis platform independent. During the static analysis functions are identified and either expanded like C++ inline functions or analyzed in a separate analysis run. Loops are also detected in this analysis step and checked for input data dependency. When required, which is when the number of iterations or the control-flow within the loop body depends on input data, the loop bound is determined using model checking. Last but not least additional control-flow paths which are generated by C short-circuiting of logic AND and OR expressions are analyzed and added to the control-flow graph.

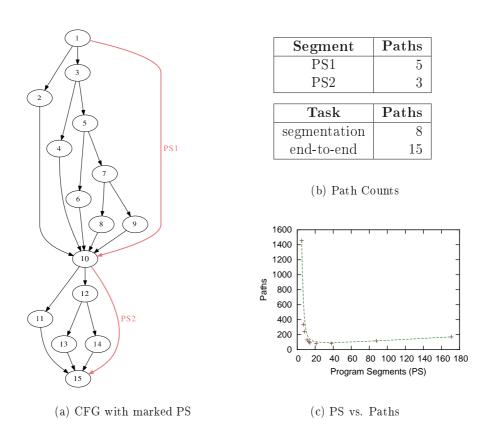

Control Flow Graph (CFG) Partitioning is used to automatically split programs into smaller program segments (PS) which can be analyzed with reasonable effort.

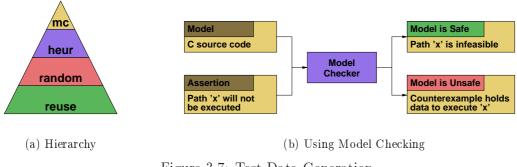

Test Data Generation is used to generate test data to cover all paths within a program segment. Paths that are not covered by random test data are examined using model checking. Model checking is an expensive process but it can be used to generate test data to force the execution of a specific path within a program segment or to identify infeasible paths.

*Execution Time Measurements* are used on all paths within each program segment except the paths identified as infeasible during the test data generation. This produces a timing profile containing the worst-case execution-time for each program segment.

Worst Case Execution Time (WCET) Calculation uses the structural information gained during the static analysis to combine the execution-times of individual program segments into a WCET bound for the whole analyzed application.

# Messbasierte Zeitanalyse von ANSI-C konformen Applikationen

Seit der Entwicklung der ersten elektronischen Motorsteuerungssysteme hat die Elektronik in immer schnelleren Schritten Einzug ins Automobil gehalten und ist derzeit dabei, sicherheitskritische mechanische Systeme abzulösen. Anstatt mechanischer Systeme werden jetzt verstärkt Netzwerke aus eingebetteten elektronischen Steuergeräten eingesetzt, welche erhöhte Funktionalität bei verringerten Kosten versprechen. Die erweiterte Funktionalität wird mit zunehmender Komplexität der Systeme erkauft. So beinhaltet die Elektronik eines modernen Luxusmodells heute in etwa 100 Millionen Zeilen an Programmquelltext, verteilt auf Netzwerke aus 70-100 software-gesteuerten Steuergeräten verschiedener Hersteller.

Um Fehler im Design durch mangelnde Interoperabilität zu vermeiden, setzt man auf verschiedene standardisierte Architekturen wie AUTOSAR und Netzwerke wie FlexRay<sup>™</sup> und CAN. Die Software in den Steuergeräten wird mittels Modellprüfern, Software-Verifikationsund Analysetools geprüft, wobei jedoch oft die Analyse des Zeitverhaltens vernachlässigt wird. In letzter Zeit wurden einige Werkzeuge zur Überprüfung des Laufzeitverhaltens von Software entwickelt, wobei ein Teil auf formale Methoden und abstrakte Prozessormodelle und der andere Teil auf Laufzeitmessungen an der Zielhardware setzt, um die maximale Ausführungszeit von Programmen (WCET) zu ermitteln. Hybride WCET Analyse verbindet plattformunabhängige statische Analyse des Anwendungs-Quellcodes mit Laufzeitmessungen, die die Ausführungszeit auf der Zielplattform messen und dadurch ein hardwareabhängiges Laufzeitprofil der Applikation erzeugen.

Diese Arbeit erweitert die hybride Zeitanalyse, die im Zuge des MoDECS Projektes entwickelt wurde, um Schleifen, Funktionsaufrufe und Kontrollflussentscheidungen in logischen UND und ODER Ausdrücken analysieren zu können, was für die Analyse industrieller Anwendungen unerlässlich ist. Die erweiterte WCET-Analyse besteht aus folgenden Schritten:

Statische Analyse des ANSI-C Quellcodes, um dessen Struktur zu ermitteln. C wird oft bei der Programmierung von Steuergeräten verwendet und macht als Ausgangsbasis für die Analyse diese plattformunabhängig. Während der Analyse werden Funktionsaufrufe erkannt und die aufgerufenen Funktionen ähnlich wie C++ inline-Funktionen expandiert oder in einer getrennten Analyse untersucht. Schleifen werden in der statischen Analyse erkannt und auf ihre Eingabedatenabhängigkeit untersucht. Bei eingabeabhängigen Iterationsbedingungen oder eingabeabhängigem Kontrollfluss in der Schleife wird in diesem Schritt auch deren maximale Iterationszahl mittels Modellprüfung bestimmt. Letztendlich werden bei der statischen Analyse noch logische UND- und ODER-Ausdrücke untersucht und im Kontrollflussgraph eingetragen.

Die Partitionierung des Kontrollflussgraph (CFG) teilt den CFG automatisch in kleinere Programmsegmente (PS) auf, die mit vertretbarem Aufwand analysiert werden können.

Die *Testdatengenerierung* dient dazu, Testdaten für alle möglichen Ausführungspfade in einem PS zu generieren. Modellprüfung wird benutzt, um Testdaten für Pfade zu finden, die durch die erzeugten Zufallsdaten nicht abgedeckt werden konnten und um Pfade die aufgrund der Codesemantik unausführbar sind als unausführbar zu identifizieen.

Laufzeitmessungen dienen zur Ermittlung der Ausführungszeit aller tatsächlich ausführbaren Pfade eines Programmsegments. Die Laufzeitmessungen erzeugen ein Ausführungszeitprofil jedes Programmsegmentes, das unter anderem auch die WCET des PS beinhaltet.

Die Berechnung eines Wertes für die maximalen Ausführungszeit (WCET) durch Kombination der einzelnen Laufzeitprofile wird unter Berücksichtigung der Strukturinformation aus der statischen Analyse durchgeführt, um die WCET der analysierten Applikation zu erhalten.

# Acknowledgements

First of all, I would like to thank my supervisor and professor Univ. Prof. Dr. Peter Puschner who encouraged me with his helpful advice and valuable support. He supported my work with valuable suggestions and without his help this thesis would not be finished yet. I would also thank my secondary advisor Univ. Prof. Dr. Jens Knoop for his willingness to evaluate this thesis on short notice and for his suggestions how to improve it. I am also grateful to the head of the department of the Institut für Technische Informatik, Real-Time Systems Group, O. Univ. Prof. Dr. Hermann Kopetz who made it possible to me to work in a highly motivated and motivating environment.

I would also like to thank all my current and former colleagues of the institute for interesting discussions after lectures in the institute or over the occasional cup of coffee in the kitchen. I also thank the administrative staff of the institute for shielding me from administrative overhead as good as possible.

Especially I would like to mention Dr. Ingomar Wenzel with whom I worked together on the *MoDECS* project, which provided a solid foundation for my research. Dr. Raimund Kirner was also an interesting partner for discussions and supported me with valuable advice and ideas. I would also like to thank Dr. Klaus Steinhammer who designed the hardware for the measurement device used for the HCS12 architecture in the *MoDECS* project who was a big moral uplifting in the final stages of this work.

As a personal note I thank my family and my friends for their support during the writing of this thesis.

The research for this thesis has been conducted during my employment as a research assistant at the Institut für Technische Informatik, Real-Time Systems Group within the Vienna University of Technology which was financed by the FIT-IT project "MoDECS-d – Model-based Development of distributed Embedded Control Systems" under project number 807144/7855 and the FFG project "ATDGEN – Automatic Test Data Generation for WCET Measurements" under project number 812653/1729-GLE/BLC.

# Contents

| 1        | Intr                       | oducti         | ion                                                   | 1  |  |  |

|----------|----------------------------|----------------|-------------------------------------------------------|----|--|--|

|          | 1.1                        | Motiv          | ation                                                 | 2  |  |  |

|          | 1.2                        | Contri         | ibution                                               | 3  |  |  |

|          | 1.3                        | Docur          | nent Structure                                        | 4  |  |  |

| <b>2</b> | Bas                        | Basic Concepts |                                                       |    |  |  |

|          | 2.1                        | The C          | Language Family                                       | 5  |  |  |

|          |                            | 2.1.1          | Drawbacks of ANSI/ISO-C for Embedded Programming      | 6  |  |  |

|          |                            | 2.1.2          | Language Features Support in this Thesis              | 7  |  |  |

|          | 2.2                        | Code           | Transformation and Representation                     | 9  |  |  |

|          |                            | 2.2.1          | Compilation                                           | 10 |  |  |

|          |                            | 2.2.2          | Lexical Analysis, Parse Tree and Abstract Syntax Tree | 10 |  |  |

|          |                            | 2.2.3          | Basic Block                                           | 11 |  |  |

|          |                            | 2.2.4          | Control Flow Graph                                    | 12 |  |  |

|          |                            | 2.2.5          | Path                                                  | 12 |  |  |

|          |                            | 2.2.6          | Dominator and Postdominator                           | 13 |  |  |

|          |                            | 2.2.7          | Program Segment                                       | 13 |  |  |

|          | 2.3                        | Target         | t Platform Complexity                                 | 13 |  |  |

|          |                            | 2.3.1          | Influences of the Operating System                    | 14 |  |  |

|          |                            | 2.3.2          | Influences of the Compiler                            | 16 |  |  |

|          |                            | 2.3.3          | Influence of the Target Hardware                      | 19 |  |  |

|          |                            | 2.3.4          | Hardware Optimization Techniques                      | 19 |  |  |

|          | 2.4                        | Softwa         | are Complexity                                        | 29 |  |  |

|          |                            | 2.4.1          | Software Metrics                                      | 30 |  |  |

|          |                            | 2.4.2          | Coding Guidelines                                     | 31 |  |  |

|          | 2.5                        | Summ           | nary                                                  | 32 |  |  |

| 3        | Execution Time Analysis 33 |                |                                                       |    |  |  |

|          | 3.1                        | Why 7          | Timing Analysis                                       | 33 |  |  |

|          | 3.2                        | Worst          | -Case Execution Time $(WCET)$                         | 35 |  |  |

|   | 3.3  | Timing analysis                                                                                                   | 36 |

|---|------|-------------------------------------------------------------------------------------------------------------------|----|

|   |      | 3.3.1 Anatomy of a WCET Analysis Framework                                                                        | 37 |

|   |      | 3.3.2 Syntax Analysis and CFG extraction                                                                          | 37 |

|   |      | 3.3.3 Static Analysis                                                                                             | 38 |

|   |      | 3.3.4 Dynamic Timing Analysis                                                                                     | 41 |

|   |      | 3.3.5 WCET Calculation                                                                                            | 46 |

|   | 3.4  | The Measurement-Based or Hybrid Timing Analysis Approach                                                          | 49 |

|   |      | 3.4.1 Assumptions and Prerequisites                                                                               | 50 |

|   |      | 3.4.2 Basic Idea - Guiding Measurements by Static Analysis                                                        | 51 |

|   |      | 3.4.3 Partitioning or Segmentation of the CFG                                                                     | 52 |

|   |      | 3.4.4 Test data generation                                                                                        | 54 |

|   |      | 3.4.5 Function Calls                                                                                              | 55 |

|   |      | 3.4.6 Simplified Data Flow Analysis                                                                               | 55 |

|   |      | 3.4.7 Loops                                                                                                       | 56 |

|   |      | 3.4.8 WCET Calculation Step                                                                                       | 56 |

|   |      | 3.4.9 Differences to MoDECS V2                                                                                    | 56 |

|   | 3.5  | Summary                                                                                                           | 57 |

| 4 | Exe  | cution-Time Analysis Framework                                                                                    | 59 |

|   | 4.1  | Development Environment                                                                                           | 59 |

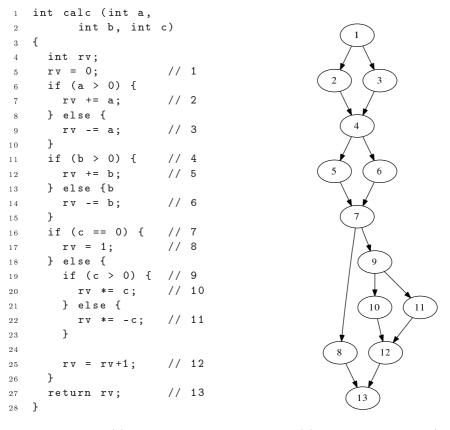

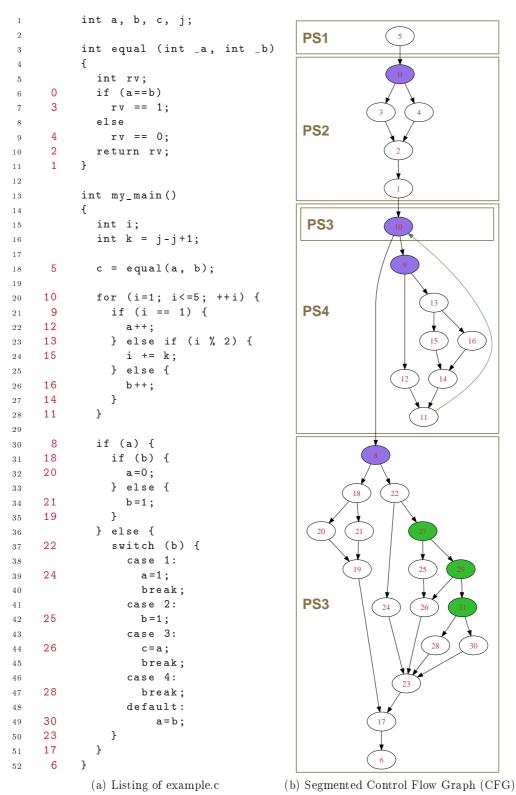

|   | 4.2  | Example Application                                                                                               | 59 |

|   | 4.3  | Input Parsing                                                                                                     | 61 |

|   | 4.4  | Code Generation                                                                                                   | 61 |

|   | 4.5  | CFG Generation                                                                                                    | 61 |

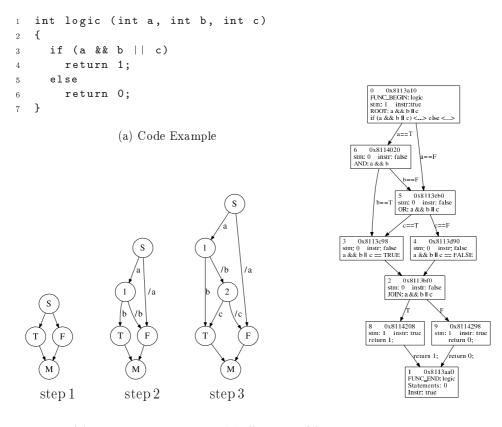

|   | 4.6  | Expression Paths                                                                                                  | 64 |

|   | 4.7  | Const Analysis                                                                                                    | 66 |

|   | 4.8  | Loop Analysis                                                                                                     | 67 |

|   |      | 4.8.1 Loop Categorization                                                                                         | 67 |

|   |      | 4.8.2 Loop Bound Analysis                                                                                         | 69 |

|   | 4.9  | Counting Paths Between Two Nodes                                                                                  | 70 |

|   | 4.10 | Dominator and Postdominator Tree                                                                                  | 73 |

|   | 4.11 | Segmentation                                                                                                      | 73 |

|   | 4.12 | Decision Tree (dtree)                                                                                             | 76 |

|   | 4.13 | Test Data Generation                                                                                              | 78 |

|   |      | 4.13.1 Reused Test Data                                                                                           | 78 |

|   |      | 4.13.2 Random Test Data $\ldots$ | 79 |

|   |      | 4.13.3 Model Checking                                                                                             | 80 |

|          | 4.14 | Manag                 | ging Test Data $\ldots \ldots $ 80 |

|----------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|          | 4.15 | Measu                 | rements                                                                                                                       |

|          |      | 4.15.1                | Generating Target and Module Code                                                                                             |

|          | 4.16 | Analys                | sis Tool Usage and Output                                                                                                     |

|          |      | 4.16.1                | Parameter File                                                                                                                |

|          |      | 4.16.2                | Command Line Arguments                                                                                                        |

|          |      | 4.16.3                | Tool Output                                                                                                                   |

|          | 4.17 | Summ                  | ary                                                                                                                           |

| <b>5</b> | Exp  | erimer                | nts 89                                                                                                                        |

|          | 5.1  |                       | etup                                                                                                                          |

|          |      | 5.1.1                 | Basic Block and Path Counts Explained                                                                                         |

|          |      | 5.1.2                 | Selection of Case Studies                                                                                                     |

|          |      | 5.1.3                 | Test Hardware and Development Software                                                                                        |

|          |      | 5.1.4                 | Target Software Layout and Host-Target Communication 97                                                                       |

|          | 5.2  | Descri                | ption and Goals of Tests Scenarios                                                                                            |

|          | 5.3  | Loops                 |                                                                                                                               |

|          |      | 5.3.1                 | General Loops                                                                                                                 |

|          |      | 5.3.2                 | General vs. Specialized Loop Handling                                                                                         |

|          |      | 5.3.3                 | Reduced Overestimation for 1:n-Loops                                                                                          |

|          | 5.4  | Functi                | on Inlining vs. Black-Boxing                                                                                                  |

|          | 5.5  | Contro                | Pl Flow in Expressions                                                                                                        |

|          | 5.6  | Result                | s                                                                                                                             |

|          |      | 5.6.1                 | Loops                                                                                                                         |

|          |      | 5.6.2                 | Function Inlining vs. Black-Boxing                                                                                            |

|          |      | 5.6.3                 | Control Flow in Expressions                                                                                                   |

|          | 5.7  | $\operatorname{Summ}$ | ary                                                                                                                           |

| 6        | Rela | ated W                | Vork 115                                                                                                                      |

|          | 6.1  | WCEI                  | Γ Analysis                                                                                                                    |

|          |      | 6.1.1                 | Static WCET Analysis                                                                                                          |

|          |      | 6.1.2                 | Measurement Based and Hybrid WCET Analysis                                                                                    |

|          |      | 6.1.3                 | Overview of Current WCET Analysis Tools                                                                                       |

|          | 6.2  | Improv                | ving the WCET                                                                                                                 |

|          |      | 6.2.1                 | WCET-Oriented Programming                                                                                                     |

|          |      | 6.2.2                 | Single-Path Conversion                                                                                                        |

|          | 6.3  | Model                 | Checking                                                                                                                      |

|          | 6.4  | Progra                | $\operatorname{Analysis}$                                                                                                     |

|                  | 6.5                        | Cache Analysis                             | 134 |  |

|------------------|----------------------------|--------------------------------------------|-----|--|

|                  | 6.6                        | Timing Anomalies                           | 135 |  |

|                  | 6.7                        | Other Publications related to this Work    | 138 |  |

|                  | 6.8                        | Conclusion                                 | 138 |  |

| 7                | Con                        | clusion and Outlook 1                      | 41  |  |

|                  | 7.1                        | Summary of Measurement-Based WCET Analysis | 141 |  |

|                  | 7.2                        | Lessions Learned                           | 142 |  |

|                  |                            | 7.2.1 Gained Experiences                   | 143 |  |

|                  | 7.3                        | Applications of Hybrid WCET Analysis       | 143 |  |

|                  | 7.4                        | Future Work                                | 144 |  |

| Bibliography 147 |                            |                                            |     |  |

| Index 165        |                            |                                            |     |  |

| A                | A List of Abbrevations 169 |                                            |     |  |

| в                | 3 Acknowledgements 171     |                                            |     |  |

# List of Figures

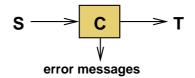

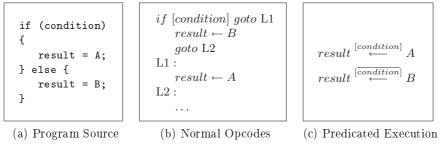

| 2.1  | Code generation for Logical AND and OR Short-Circuiting                                                                                                                          | 9  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The Compiler Abstraction                                                                                                                                                         | 10 |

| 2.3  | Illustration of Basic Concepts                                                                                                                                                   | 11 |

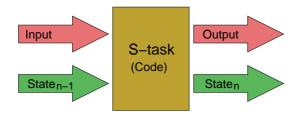

| 2.4  | The S-task model                                                                                                                                                                 | 16 |

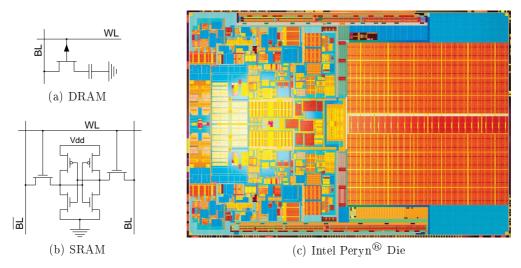

| 2.5  | DRAM vs. SRAM Cell and Processor Die with SRAM Cache                                                                                                                             | 21 |

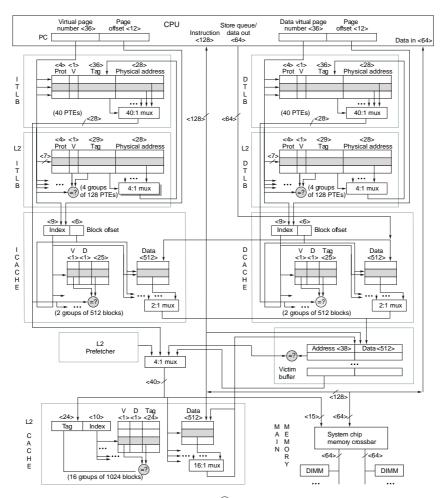

| 2.6  | AMD Opteron <sup>®</sup> Memory Hierarchy $\ldots \ldots \ldots$ | 22 |

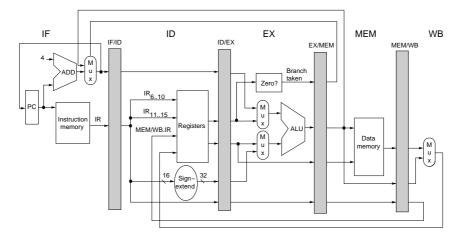

| 2.7  | Simple MIPS Pipeline                                                                                                                                                             | 23 |

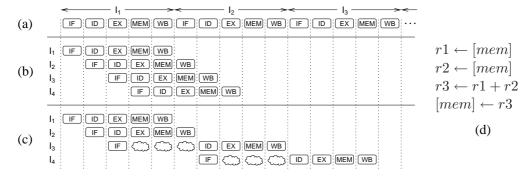

| 2.8  | Pipelined Execution of Instructions                                                                                                                                              | 24 |

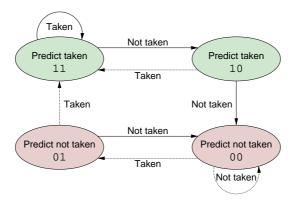

| 2.9  | 2-bit Branch Prediction                                                                                                                                                          | 26 |

| 2.10 | Normal Opcodes and Predicated Execution Opcodes                                                                                                                                  | 27 |

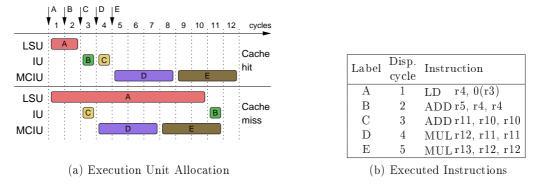

| 2.11 | Variable Execution Times on the Intel $^{\textcircled{R}}$ x86 Processor Family 2                                                                                                | 28 |

| 2.12 | A Timing Anomalie Example                                                                                                                                                        | 29 |

| 0.1  |                                                                                                                                                                                  |    |

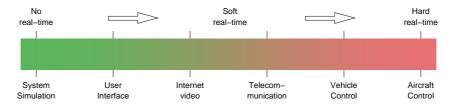

| 3.1  | 0 1                                                                                                                                                                              | 33 |

| 3.2  | 1                                                                                                                                                                                | 34 |

| 3.3  |                                                                                                                                                                                  | 36 |

| 3.4  |                                                                                                                                                                                  | 47 |

| 3.5  | Basic Hybrid WCET Analysis Approach                                                                                                                                              | 51 |

| 3.6  | Concept of CFG Partitioning                                                                                                                                                      | 53 |

| 3.7  | Test Data Generation                                                                                                                                                             | 54 |

| 4.1  | Running Example for Chapter 4                                                                                                                                                    | 60 |

| 4.2  | Basic CFG building algorithm                                                                                                                                                     | 63 |

| 4.3  |                                                                                                                                                                                  | 65 |

| 4.4  |                                                                                                                                                                                  | 66 |

| 4.5  |                                                                                                                                                                                  | 68 |

| 4.6  |                                                                                                                                                                                  | 70 |

| 4.7  |                                                                                                                                                                                  | 71 |

| 4.8  |                                                                                                                                                                                  | 72 |

| 4.9  |                                                                                                                                                                                  | 74 |

| =.0  |                                                                                                                                                                                  |    |

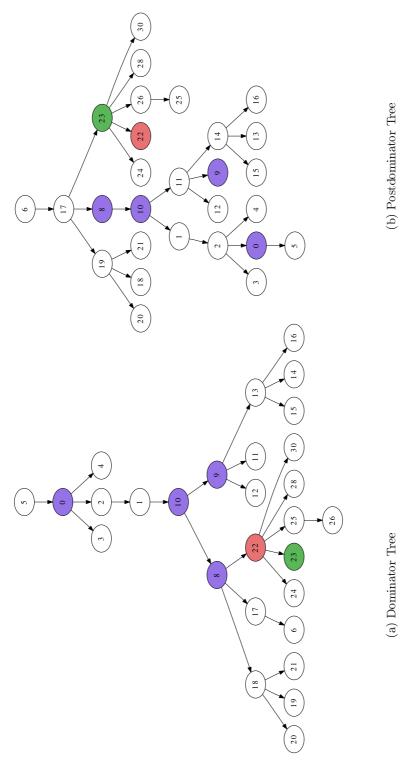

| 4.10 Segmentation Algorithm                                                        | 75  |

|------------------------------------------------------------------------------------|-----|

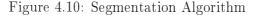

| 4.11 DTree for the Example Application                                             | 77  |

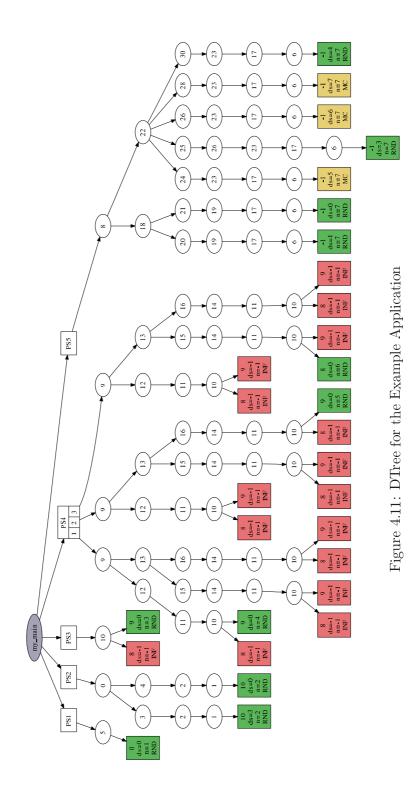

| 4.12 Random Value Distribution for Test Data Generation                            | 79  |

| 4.13 Model Checking to find a Path inside the Loop                                 | 81  |

| 4.14 Example xml Data File                                                         | 82  |

| 4.15 Generated Loadable Module                                                     | 83  |

| 4.16 Parameter File                                                                | 85  |

| 4.17 WCET analysis Tool Help Text                                                  | 86  |

| 4.18 WCET analysis Tool Version Information                                        | 87  |

| 4.19 Tool Output                                                                   | 88  |

| 5.1 Code Metrics Example                                                           | 90  |

| I                                                                                  |     |

| 5.2 Code generation options for industrial case studies $\ldots$ $\ldots$ $\ldots$ |     |

| 5.3 Olimex <sup>®</sup> LPC-H2138 Development Board and Programming Device .       | 95  |

| 5.4 Measurement Instructions                                                       | 98  |

| 5.5 Linker Command File for <i>Caller</i>                                          | 99  |

| 5.6 1:n-Loop with ET for Different Iterations                                      | 104 |

| 5.7 A complex 1:n Loop in the Binary Search Test Case                              | 105 |

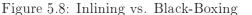

| 5.8 Inlining vs. Black-Boxing                                                      | 106 |

| 5.9 Handling of Expression Paths in V2 and V3                                      | 110 |

| 5.10 Listing of <i>fibcall</i> Case Study                                          | 113 |

|                                                                                    | 107 |

| 6.1 Comparison of Traditional and WCET-Oriented Programming                        |     |

| 6.2 Single Path Programming                                                        | 130 |

|                                                                                    |     |

| 6.3 Extraction of Bit-Vector Equations with CBMC                                   | 132 |

# List of Tables

| 5.1 | Description of Test Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Analyzeable Test Cases in V2 and V3 $\hfill \ldots \hfill \ldots \$ |

| 5.3 | Generic and Spezialized Loop Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4 | Comparison between Inlining and Black-Boxing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5 | Measurement Results for the Expression Path Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.6 | Effects of Control Flow in Expressions in Industrial Case Studies $\ . \ . \ . \ 111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1 | Overview of WCET Analysis Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.2 | Execution time of traditional and WCET-oriented Algorithms 129 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Chapter 1

# Introduction

The software systems of modern cars have reached a sizes of 100.000.000 lines of code and more [Cha09], implementing or controlling more than 2000 functions in premium cars and consuming 50 to 70 percent of the development costs of software/hardware subsystems of cars [LLS<sup>+</sup>07]. The software is distributed among multiple networks of up to 70 Electronic Control Units (*ECUs*) from different vendors which have to work together as a distributed real-time system. Today distributed real-time systems in cars are primarily used for non safety-critical functions, mainly because these systems are still young (the first car series to use the FlexRay<sup>®</sup> communication network was the BMW X5 in 2006) and the industry needs to evaluate their dependability. In aviation the Time Triggered Protocol (TTP<sup>®</sup>) is the first real-time communication protocol and it has been used in the cabin pressure control system of Airbus' superjumbo A380 since 2006.

It can be expected that distributed real-time systems will be used for safetycritical applications in the near future and are soon to replace mechanical and hydraulic subsystems. Current systems are time-triggered, which means that events are periodically transmitted over the communication channel rather than only when an event occurs. This ensures that the communication channel can handle multiple simultaneous events without event loss. The communication schedule, which specifies which node sends a data frame in a specific communication slot during a communication cycle is specified during system design, along with the definition of the individual data items within the frame. This approach provides a well-defined interface between communication nodes and facilitates composability and component-based design.

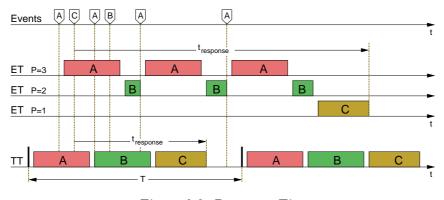

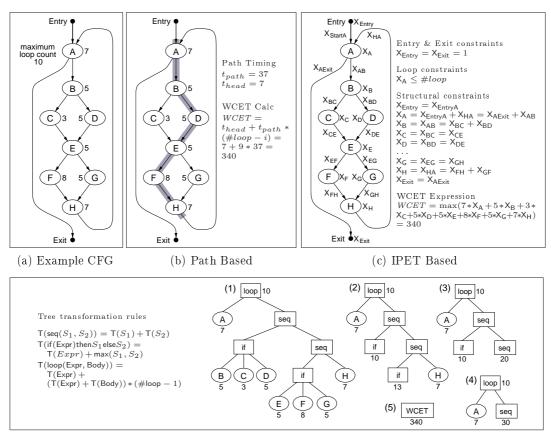

In well designed architectures not only the communication but also the task scheduling in each node is time-triggered and synchronous to communication cycles. This allows a safe calculation of the maximum delay between an event and the response caused by the controlling system. When an event occurs it is precisely known which node performs which sub-tasks of the event processing at which time, making the system fully predictable and easily to diagnose. The cycle time is shared between all running tasks. To ensure the execution of each task within a cycle, the sum of the Worst Case Execution Times (WCET) of all tasks has to be less than the cycle time. On small real-time systems, using only a single computation node, cycle-based approaches are also widely used since it is easier to ensure response times for time-triggered architectures than for event-triggered architectures. However, both approaches require the WCET to be known to ensure a maximum response time of the system. In time-triggered architectures the WCET is also required to

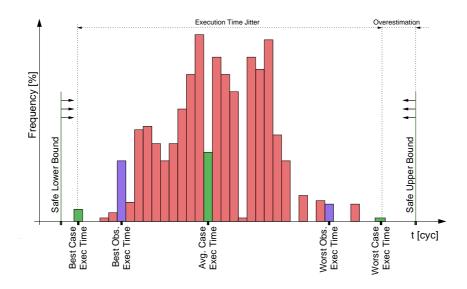

If the exact WCET is not known, which applies for most cases, an overestimation of the WCET, which is referred to as safe upper bound, can be used for system design. A popular approach to gain a "safe" upper bound for the execution-time is to perform measurements of the execution-time using "typical" test data or synthetic test data which is supposed to enforce an execution path through the program which generates the WCET. The result, which consists of the maximum of the measured execution-times plus a safety margin, is used as a "safe" upper bound for the WCET. Code generator tools like the Matlab<sup>®</sup>/TargetLink<sup>®</sup> toolchain offer to perform this task automatically. However, there are no guarantees that the WCET is equal or less than the worst observed execution-time plus the safety margin.

There exist many tools which allow the verification of the value domain of software, which means that the correct value of the result is checked. The time domain, which considers the timeliness of the result, is currently neglected. At the moment there exist only few tools for timing analysis. They are listed in Chapter 6. The majority of these tools are feasibility studies and research prototypes. Only a small fraction of the presented tools are commercially available, but they also have their shortcomings. To make things worse, some tools which operate on a low abstraction level like object code, can only be used for a specific target architecture. Concluding it can be said that the current state of (integrated) timing analysis tools is more than unsatisfactory.

## 1.1 Motivation

As the software portion in safety-critical areas of applications such as automotive or avionic applications is steadily increasing, the lack of applicable timing analysis tools, which can be embedded within an existing application development framework for (distributed) real-time applications, becomes an increasing safety issue and a major showstopper for the integration of embedded real-time systems in safety-critical systems.

The goal of this work is to develop a timing-analysis method and a prototype tool which is easy to use, operates on multiple target platforms and can be integrated into existing development processes to find a good approximation the WCET. Easy usage means that no extensive preparation like annotations or manual test data generation shall be necessary to perform timing analysis. A basic knowledge of the matter is however necessary to get reliable data. Platform independence is achieved by using the source code as basis for the analysis. Only a thin hardware dependent interface is required to perform the run-time measurements as well as basic knowledge of the bit size of the basic data types and the endianess of the target architecture. Easy integration can be achieved by a well defined interface of the execution-time analysis tool to other applications.

The developed execution-time analysis method is an extension to the measurement-based worst-case execution-time analysis (MBTA) method developed during the MoDECs Project [WRKP05] to support loops, function calls and control-flow paths within boolean AND (&&) and OR (||) expressions and the conditional expression operator (?:). The developed analysis tool is not intended as a general WCET analysis tool but to test the developed analysis method.

Hopefully the results of this work will help to improve the timing analysis process for embedded real-time applications.

## 1.2 Contribution

The major contributions of the measurement-based worst-case execution-time analysis method presented in this thesis are:

- 1. Avoidance of explicit hardware modelling and target platform independence<sup>\*</sup> Static execution-time analysis methods require a detailed hardware model of the processor to calculate the execution-time of a series of instructions. Dynamic methods execute the code on the target platform and obtain the execution-time using measurements. In cases where no detailed information about the target hardware is available static execution-time analysis cannot be performed while dynamic execution-time analysis is still possible.

- 2. Automatic control-flow generation for shortcut boolean expressions C defines a feature called short-circuit code, where boolean expressions are only evaluated as far as required. This speeds up calculation but also increases the number of possible execution paths. WCET analysis has to handle these expressions accordingly.

- 3. Parameterizable control-flow graph (*CFG*) partitioning<sup>\*</sup> The complexity of the analysis can be reduced by splitting the analyzed program into program segments (*PS*) as shown in Chapter 4. Increasing the number of PS reduces the number of required measurements but may lead to overestimations of the execution-time.

- 4. Automated test data generation using model checking<sup>\*</sup> Model checking can be used to generate the test data for all feasible paths or identify infeasible paths within a given program segment. The coverage of all feasible paths is a cornerstone of the proposed execution-time analysis method.

<sup>\*</sup>This has been contributed together with Ingomar Wenzel during the MoDECS project [WRKP05].

- 5. Detection of loop bounds using model checking In order to perform measurements of loops the loop bound has to be known. The proposed solution is to use model checking to find loop bounds [RPW08].

- 6. Automatic classification and measurement of loops Different loops require individual approaches for measurement, depending on the control-flow structure of their loop body and the loop iterator. The presented prototype can automatically detect different kinds of loops and perform the analysis accordingly.

- 7. Inlining of function calls to reduce control-flow of functions WCET estimates of functions may be shorter when the analysis considers the actual context of the function call, and not just the overall maximum execution time of the function. The presented prototype achieves this by inlining function code during the path-analysis phase of the WCET analysis on demand.

### **1.3** Document Structure

This thesis is structured as follows:

Chapter 2 discusses basic features of the C programming language, basics of compiler construction and how the complexity of the analysis is influenced by the operating system, the compiler and the target hardware. Then, Chapter 3 discusses the basics and different approaches of execution-time analysis and proposes a novel measurement-based execution-time analysis (*MBTA*) method. Following, Chapter 4 explains how the proposed MBTA method is realized within the prototype application. In Chapter 5 the individual experiments conducted with the WCET analysis prototype and why they were chosen are described, followed by a short discussion of the results. Chapter 6 explains similar work and their relation to this thesis. Finally, Chapter 7 concludes this work and summarizes the findings from the MTBA method, the prototype implementation and the conducted experiments. The chapter ends with an outlook which shows ideas for further reseach.

# Chapter 2

# **Basic Concepts**

This chapter gives a closer look at the different C standards and explains terms and concepts frequently used in this thesis. In this chapter it is also shown what makes timing analysis difficult and how the target platform, the operating system and the source code influence the complexity of the analysis. The influence of coding guidelines for automotive and avionic applications on execution-time analysis is also examined in this chapter.

### 2.1 The C Language Family

The C Programming Language has been continuously evolving since its early beginnings in 1969. The following paragraphs give a short overview about the different versions of C and explains which features of the different versions are supported in the timing analysis framework prototype presented in this thesis.

### K&R C

The first edition of "The C Programming Language" [KR78] was published in 1978 by Brian Kernighan and Dennis Ritchie. The name of the language "C" was derived to indicate that C was designed to be a successor of the "B" programming language. Even after C was standardized by ANSI (in 1989) and ISO (in 1990) K&R C still was considered the de-facto standard since it was supported with all its features by the majority of the compilers. The style of function definitions used by this early version of C is not supported by the timing analysis framework.

#### C89 and C90

After a six year lasting standardization process the C standard was ratified by the American National Standards Institute as ANSI X3.159-1989 "Programming Language C" [C89]. This version, commonly referred to as ANSI-C or C89 was adopted by the International Organization for Standardization (ISO) as ISO/IEC 9899:1990 [C90], which is referred to as C90 with only minor modifications. Since this standard is currently used for the majority of embedded applications the execution-time analysis tool presented in this thesis is currently based on this standard.

#### C99

The ISO/IEC 9899:1999 Standard [C99] which adds C++-style comments, inline functions and variadic macros (macros with a variable number of arguments) was adopted by ANSI in early 2000 and is referred to as *C99*. As the extensions are usually not used for embedded and real-time programming, the language extensions provided by C99 are not supported by the timing analysis framework presented in this thesis.

#### $\mathbf{C}++$

C++ which was standardized in 1998 and revised 2003 is an object-oriented extension to C. The name "C++" is an allusion to the ++-operator of C and indicates that C++ is an enhanced successor of C. Due to its heavy use of polymorphism and dynamic memory C++ is not suited for embedded and real-time applications and therefore not considered in this thesis.

### 2.1.1 Drawbacks of ANSI/ISO-C for Embedded Programming

The C standard leaves important aspects undefined and includes features that are not suited for embedded or real-time programming. Some important problems of standard compliant ANSI/ISO-C code are listed below. A detailed list of undefined and platform dependent or implementation specific behavior can be found in the Annex J of the ISO/IEC C99 standard [C99].

#### **Undefined Size of Data Types**

The C definitions of integer data types are very vague. For instance a char is composed of any number of bits as long as the number of bits is larger than or equal to eight. Also the binary layout (big endian, little endian, or even gray) is unspecified. This restricts platform independence and portability and requires deep knowledge about the target platform. As a result the operators working on integers are not be well-defined, too. There are some libraries and target specific headers trying to overcome this limitation and defining datatype like SINT8, UINT8, SINT16, ... etc., but each vendor has his own concepts and there is no standard way to write platform independent code.

#### **Undefined Handling of Errors**

Like the integer types some error conditions are undefined. What happens on divisions by zero or on illegal memory access operations? This behavior is mostly operating system dependant. Therefore not only precise knowledge about the target hardware but also detailed information about the target operating system is necessary in order to describe the complete semantics of C programs.

#### Weak Type Checking