Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

Universität Wien Vienna University of Technology

TECHNISCHE

Diploma Thesis

### **PCI Express based Embedded System**

System Specification, Design, Simulation and Implementation

realized to attain the academic degree of "Diplom-Ingenieur" under the supervision of

o.Univ.- Prof. Dr. Dietmar Dietrich and Dipl.-Ing. Herbert Nachtnebel as the supervising assistant

*applied at the* Technical University of Vienna Department of Electrical Engineering Institute of Computer Technology (E384)

*in cooperation with* SIEMENS AG Austria Department of Program and System Engineering (PSE), Chip, Electronic and Software (CES) *under the supervision of* Dipl.-Ing. Majid Ghameshlu

> *by* Faraj Nassar 0326747 Leopoldauer Platz 19 1210 Vienna

Vienna, October 2007

To My Family

The platform of Today's PC consists of many local buses with different requirements, to allow the communication of different devices with each other. Nowadays, many of these modern electronic devices are demanding a high bandwidth, even higher than what already existing input and output (IO) bus systems can deliver, of most interest is the Peripheral Component Interconnect (PCI) bus. These bus systems are reaching their practical limits and are facing serious problems and shortcomings that prevent them from being able to provide the bandwidth and features needed by the electronic industry, which keeps needing to an increased bandwidth as well as to a simple electrical connectivity.

All these factors together have motivated the engineering of a new IO bus system, the so-called Peripheral Component Interconnect Express (PCIe), which has been adopted as a general purpose IO device interconnect in different applications, such as desktop, server, mobile, workstations, computing and communication platforms.

Within this diploma work, the theory of PCIe was summarized and presented in monthly-based presentations (PCIe tutorial). Some of the available PCI Express Intellectual Property (IP) solutions in the market were studied and compared.

In addition to that, a PCIe-based embedded data communication system was specified, designed, simulated, and synthesized. This system utilizes the Xilinx Microblaze soft processor core, the Xilinx PCIe core, and the Philips PX1011A physical layer.

Data communication between the designed PCIe-based intelligent Endpoint device (in the PCIe topology) and the system memory, as well as the Central Processing Unit (CPU), through the Root complex, was simulated.

Keywords: IP, Microblaze, PCI, PCIe Core, PCIe Endpoint, On Chip Peripheral Bus (OPB), OPB IPIF, OPB to PCIe Bridge, Philips PX1011A PHY, USER LOGIC.

Die Architekturen heutiger PCs bestehen aus vielen Bussystemen mit unterschiedlichen Anforderungen, welche die Kommunikation der unterschiedlichen Geräte miteinander erlauben. Heutzutage verlangen viele dieser modernen elektronischen Geräte eine hohe Bandbreite, oft höher als es die verfügbaren Eingangs- und Ausgangsbussysteme erlauben. Die größte Bedeutung hat die Peripheral Component Interconnect (PCI) Busfamilie, aber auch diese Bussysteme erreichen ihre praktischen Grenzen und beinhalten ernsthafte Probleme und Mängel, welche verhindern, dass die, durch die elektronische Industrie geforderte, immer höhere Bandbreite, und die einfache elektrische Anbindung erreicht werden.

Alle diese Faktoren zusammen haben die Entwicklung eines neuen IO Bussystems motiviert, dem sogenannten Peripheral Component Interconnect Express (PCIe) Bus, welcher als universelles Eingangs- und Ausgangsbussystem in den unterschiedlichsten Anwendungen, wie Desktopcomputer, mobile Endgeräten, Workstations, sowie Rechen- und Kommunikationsplattformen eingesetzt wird.

Im Rahmen dieser Diplomarbeit wurde die Theorie von PCIe zusammengefasst und in monatlichen Präsentationen vorgestellt (PCIe Tutorial). Einige der vorhandenen PCIe Intellectual Property (IP) Lösungen im Markt wurden untersucht und verglichen.

Zusätzlich wurde ein PCIe basiertes embedded Datenübermittlungssystem spezifiziert, entworfen, simuliert und synthetisiert. Dieses System verwendet den Xilinx Microblaze Processor Core, den Xilinx PCIe Core und die Philips PX1011A physikalische Ebene.

Außerdem wurde die Datenkommunikation zwischen dem entworfenen PCIe basierten intelligenten Endpunkt-Gerät (in der PCIe Topologie) und dem Systemspeicher, sowie der Zentraleinheit (CPU), durch den Verbindungsblock, simuliert.

Stichwörter: IP, Microblaze, PCI, PCIe Core, PCIe Endpunkt, On-chip Peripheral Bus (OPB), OPB IPIF, OPB zur PCIe Brücke, Philips PX1011A PHY, USER LOGIK.

This PCI Express based Embedded System was conducted as a Master thesis work in the field of Microelectronics, in cooperation with the Institute of Computer Engineering at the Technical University of Vienna and the program and System Engineering (PSE) Department, Chips, Electronics and Software (CES) Division of SIEMENS AG Austria.

First of all, I would like to express my deepest thanks to Mr. Johann Notbauer (M.Sc.), for giving me the opportunity to carry out this project in his department at SIEMENS, under the direct supervision of Mr. Majid Ghameshlu (M.Sc.), who consistently helped me do my best, due to his wide experience in this field. Many thanks to Mr. Ghameshlu for being patient and helpful all the time.

I am also grateful for the support and help provided by my colleagues at SIEMENS AG Austria.

I also want to express my appreciation to Mr. Herbert Nachtnebel (M.Sc.) for being my direct supervisor at the Technical University of Vienna, and for his support and contribution to this work.

In addition, I want to thank Prof. Dietmar Dietrich, the Head of the Computer Engineering Institute at the Technical University of Vienna, and Prof. Gottfried Strasser, professor at the Institute of Solid State Electronics and the Technical Director of the Microstructure center of the Technical University of Vienna, for being my examiners.

Finally, I want to thank my family and friends for their constant encouragement and support.

### Contents

#### 1 Introduction

- 1.1 Objectives 1

- 1.2 Method, Software and Hardware 1

- 1.3 Tasks and Time Plan 2

- 1.4 Outline 3

#### 2 PCI Express Theory

- 2.1 Evolution of IO Bus Systems 4

- 2.2 Peripheral Component Interconnect (PCI) 5

1

- 2.2.1 PCI Architecture 5

- 2.2.2 PCI Key Features 7

- 2.2.3 PCI practical Limitations and challenges 7

4

- 2.3 Peripheral Component Interconnect Express (PCIe) 8

- 2.3.1 PCIe Introduction 8

- 2.3.2 PCIe Topology 9

- 2.3.3 PCIe Key Features 10

- 2.3.4 PCIe Architecture 10

- 2.3.5 PCIe Future Prospective 16

#### **3** PCIe Endpoint (EP) Design 17

- 3.1 Design Overview 17

- 3.2 Philips PX1011A PHY 22

- 3.2.1 Block Diagram 22

- 3.2.2 Operation Principle 22

- 3.2.3 Interfaces 23

- 3.3 Xilinx PCIe Core 26

- 3.3.1 Functionality and Features 27

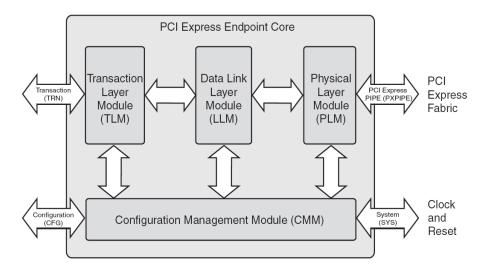

- 3.3.2 Block Diagram and Functionality 28

- 3.3.3 Core Interfaces 29

- 3.3.4 Core Generation and Configuration 39

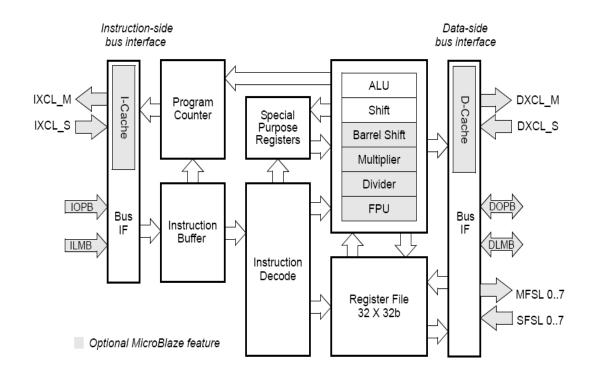

- 3.4 Xilinx Microblaze Soft Processor Core 42

- 3.4.1 Microblaze Block Diagram 42

- 3.4.2 Microblaze Interfaces 43

- 3.4.3 Local Memory Bus (LMB) 44

- 3.4.4 On-Chip Peripheral Bus (OPB) 44

- 3.5 Microblaze PCIe Peripheral 46

- 3.5.1 OPB to PCIe Bridge 47

- 3.5.2 On-chip Peripheral Bus Intellectual Property Interface (OPB IPIF) 51

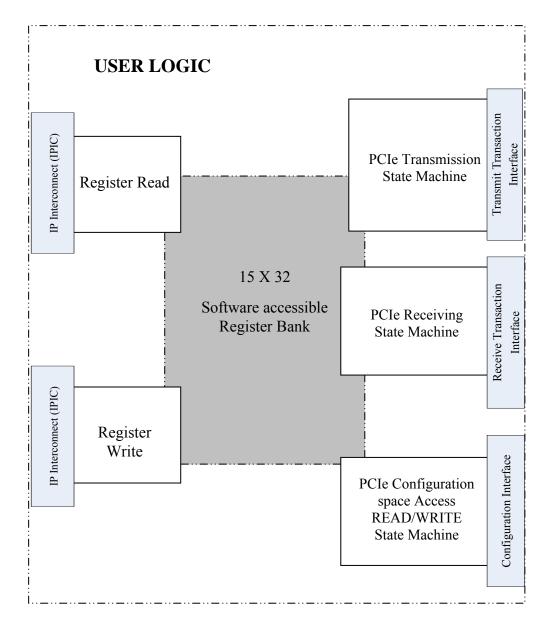

- 3.5.3 USER LOGIC Model 53

- 3.5.3.1 Register Read 56

- 3.5.3.1 Register Write 56

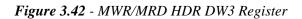

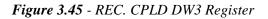

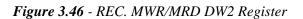

- 3.5.3.3 Software accessible Register Bank 57

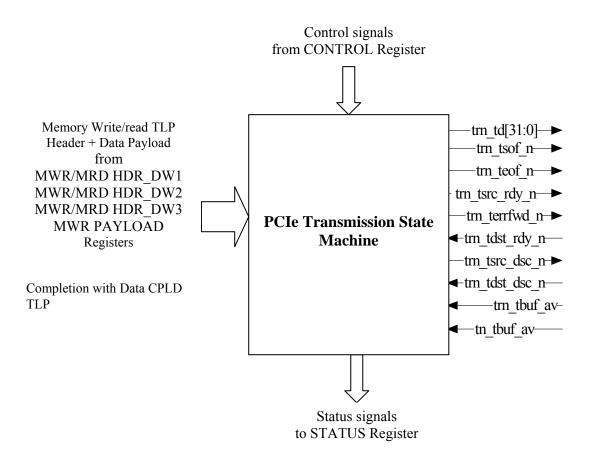

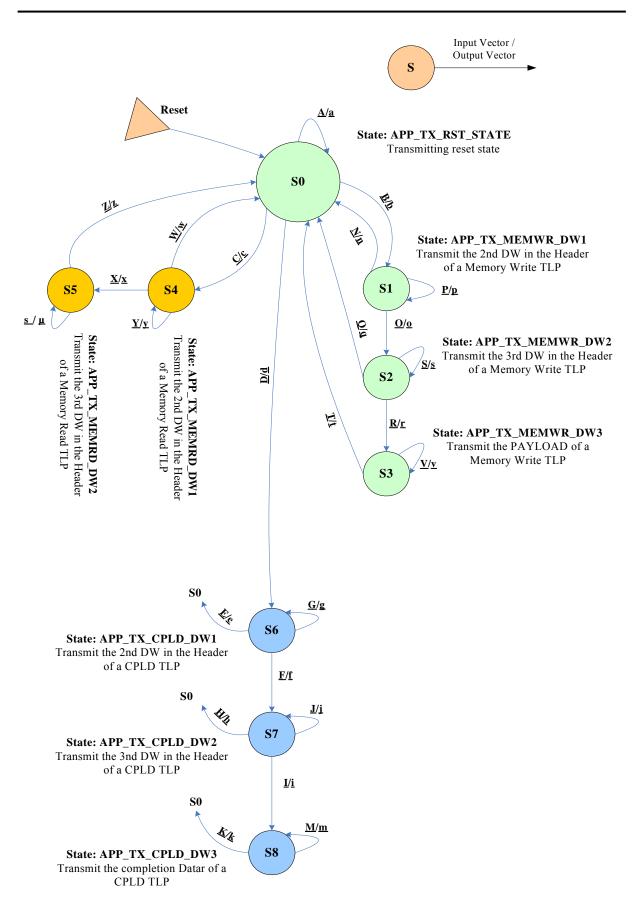

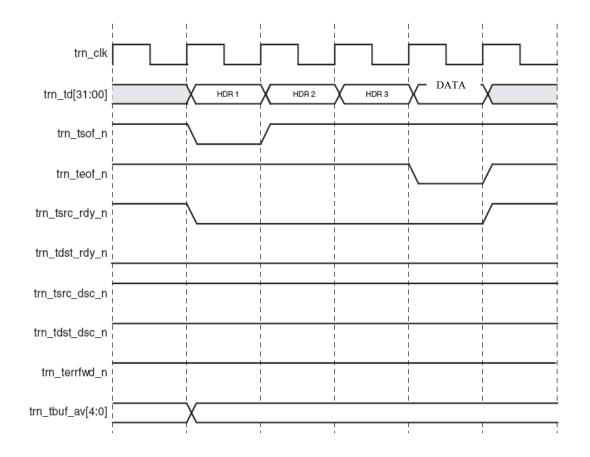

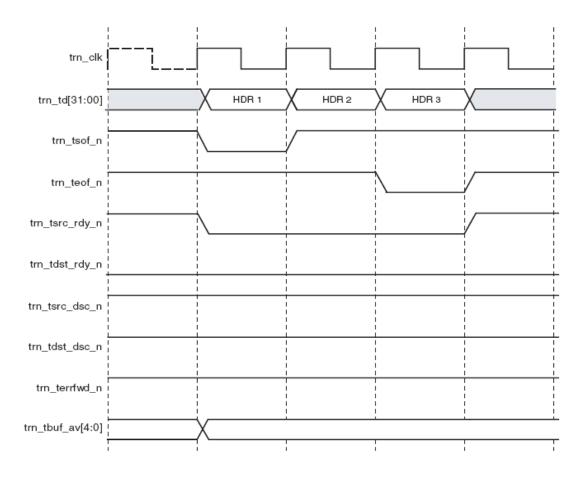

- 3.5.3.4 PCIe Transmission State Machine 65

- 3.5.3.5 PCIe Receiving State Machine 70

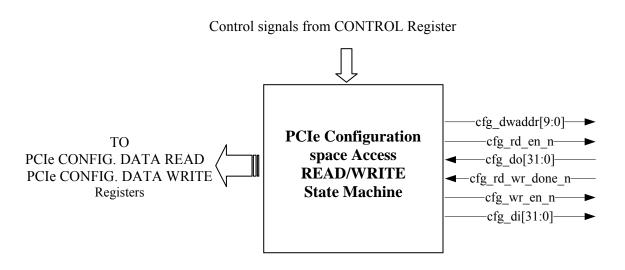

- 3.5.3.6 PCIe Configuration space Access READ/WRITE State Machine 735

#### 4 PCIe Endpoint Simulations 80

- 4.1 PCIe Testbench 80

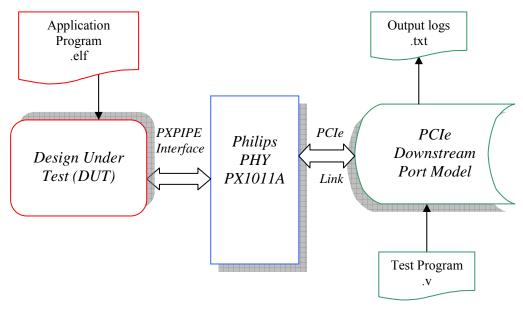

- 4.1.1 Philips PHY Simulation Model 81

- 4.1.2 Xilinx PCIe Downstream Port Simulation Model 81

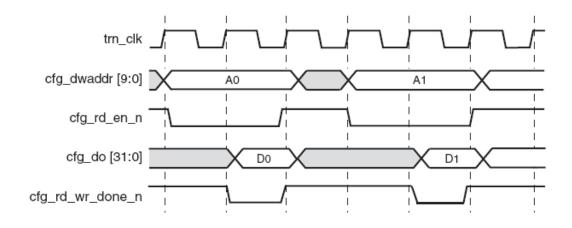

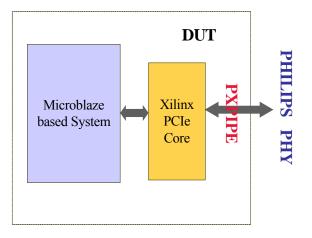

- 4.1.3 Design Under Test (DUT) 83

- 4.1.3.1 Xilinx PCIe PIPE IP Simulation Model 83

- 4.1.3.2 Microblaze based System Simulation Model 84

- 4.2 C Application Program 84

- 4.3 Simulation Flow 94

- 4.4 Test Cases Summary 104

- 5 PCIe Endpoint Implementation 106

- 6 Conclusion and Future Work 107

#### Appendix A: PCI Express IP Providers 108

Appendix B: Xilinx WebCases 121

Appendix C: Project Directory Structure 122

**Bibliography 124**

### List of Acronyms and Abbreviations

| <b>A</b><br>ACK/NAK<br>AGP<br>ASIC<br>ASPM<br>Attr        | Acknowledged /Not Acknowledged<br>Accelerated Graphics Port<br>Application Specific Integrated Circuits<br>Active State Power Management<br>Attribute                                                                                |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>B</b><br>BAR<br>BE<br>BIOS<br>BRAM                     | Byte<br>Base Address Register<br>Byte Enable<br>Basic Input Output System<br>Block Random Access Memory                                                                                                                              |

| C<br>CA<br>CES<br>CFG<br>CMM<br>CPI<br>CPLD<br>CPU<br>CRS | Completer Abort<br>Chips, Electronics and Software<br>Configuration interface<br>Configuration Management Module<br>Completion without data<br>Completion with Data<br>Central Processing Unit<br>Configuration Request Retry Status |

| D<br>DDR<br>DLLP<br>DLMB<br>DMA<br>DUT<br>DW, DWORD<br>E  | Dual Data Rate<br>Data Link Layer Packet<br>Data Local Memory Bus<br>Direct Memory Access<br>Design Under Test<br>Doubleword                                                                                                         |

| ECRC<br>EDK<br>EISA<br>ELF<br>EOF<br>EP                   | End to End Cyclic Redundancy Check<br>Embedded Development Kit<br>Extended Industry Standards Architecture<br>Executable linked Format<br>End-of-Frame<br>Endpoint                                                                   |

#### F

| FIFO     | First In First Out                     |

|----------|----------------------------------------|

| Fmt      | Format                                 |

| FPGA     | Field Programmable Gate Arrays         |

| FSB      | Front Side Bus                         |

| FSL      | Fast Simplex Link                      |

|          |                                        |

| G        |                                        |

| Gbytes/s | Gigabytes per second                   |

| Gbps     | Giga bit per second                    |

|          |                                        |

| H        |                                        |

| HDD      | Hard Disk Drive                        |

| HDL      | Hardware Description Language          |

| HDR      | Header                                 |

| I        |                                        |

| I<br>ICH | IO Controller Hub                      |

| IDE      | Integrated Drive Electronics           |

| ILMB     | Instruction Local Memory Bus           |

| IO       | Input and Output                       |

| IP       | Intellectual Property                  |

| IPIC     | IP Interconnect                        |

| IPIF     | Intellectual Property Interface        |

| ISA      | Industry Standards Architecture        |

|          | •                                      |

| ISE      | Integrated Software Environment        |

| К        |                                        |

| Kbytes   | 2 <sup>10</sup> Bytes                  |

| - )      | j tit                                  |

| L        |                                        |

| LCRC     | Link Cyclic Redundancy Check           |

| LLM      | Data Link Layer Module                 |

| LMB      | Local Memory Bus                       |

| LTSSM    | Link Training and Status State Machine |

| LVDS     | Low Voltage Differential Signal        |

|          |                                        |

| M        |                                        |

| M.Sc.    | Master of Science                      |

| MAC      | Media Access Controller                |

| Mbytes/s | Megabytes per second                   |

| MCH      | Memory Controller Hub                  |

| MGTs     | Multi-Gigabit Transceivers             |

| MSI      | Message Signalled Interrupt            |

| 0        |                                        |

| 0        |                                        |

| OPB      | On-Chip Peripheral Bus                 |

| OPB IPIF | OPB Intellectual Property Interface    |

|          |                                        |

#### Р

| PCI             | Peripheral Component Interconnect         |

|-----------------|-------------------------------------------|

| PCI-SIG         | PCI-Special Interest Group                |

| PCI-X           | Peripheral Component Interconnect-X       |

| PCIe            | Peripheral Component Interconnect Express |

| PHY             | Physical                                  |

| PIPE            | Physical Interface for PCI Express        |

| PLD             | Programmable Logic Device                 |

| PLI             | Programming Language Interface            |

| PLM             | Physical Layer Module                     |

| PLPs            | Physical Layer Packets                    |

| PPM             | Programmed Power Management               |

| PXPIPE          | Philips PHY Specification PIPE            |

| 0               |                                           |

| <b>Q</b><br>QDR | Quad Data Rate                            |

| QoS             | Quality of services                       |

| 200             |                                           |

| R               |                                           |

| R               | Reserved                                  |

| RAM             | Random Access Memory                      |

| RISC            | Reduced Instruction Set Computer          |

| RTL             | Register Transfer Level                   |

| RX              | Receiver                                  |

| S               |                                           |

| SC              | Successful Completion                     |

| SCSI            | Small Computer System Interface           |

| SDK             | Software Development Kit                  |

| SDRAM           | Synchronous Dynamic Random Access Memory  |

| SOF             | Start-of-Frame                            |

| SYS             | System interface                          |

| т               |                                           |

| T<br>TC         | Traffic Class                             |

| TD              | TLP Digest                                |

| TLP             | Transaction Layer Packet                  |

| TLM             | Transaction Layer Module                  |

| TPI             | Test Programming Interface                |

| TRN             | Transaction interface                     |

| TXPLL           | Transmitter Phase Locked Loop             |

| TX              | Transmitter                               |

| U               |                                           |

| UR              | Unsupported Request                       |

| USB             | Universal Serial Bus                      |

|                 |                                           |

VVESAVideo Electronics Standards AssociationVHDLVHSIC-HDL Very High Speed Integrated Circuit Hardware description<br/>Language

#### Chapter 1 Introduction 1

#### Chapter 2 PCI Express Theory 4

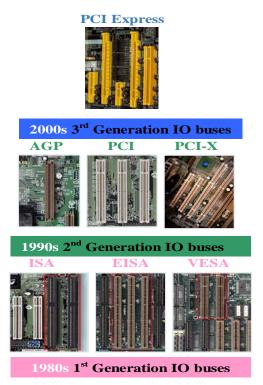

Figure 2.1 - Evolution of IO bus systems 4

- Figure 2.2 An Example of 33 MHz PCI Bus Based System [ABS04] 6

- Figure 2.3 An Example of 66 MHz PCI Bus Based System [ABS04] 6

- Figure 2.4 PCI Express Link [ABS04] 8

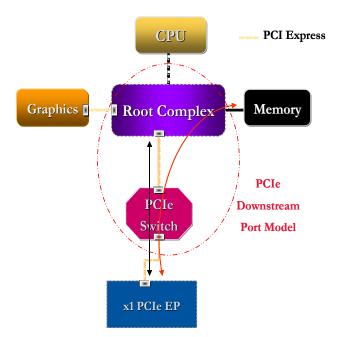

- Figure 2.5 PCI Express Topology 9

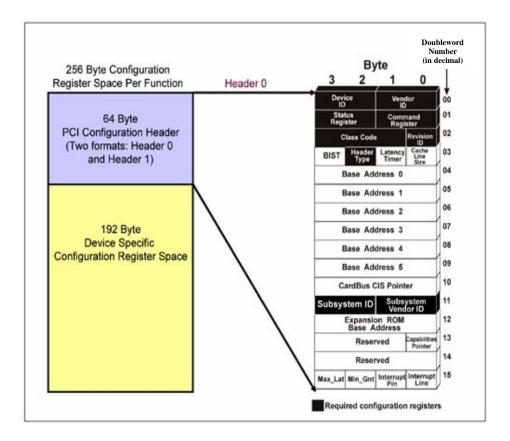

- Figure 2.6 PCI Configuration Model [ABS04] 11

- Figure 2.7 PCI Express Architecture 12

- Figure 2.8 PCI Express TLP Assembly/Disassembly 12

- Figure 2.9 Header for a 32-bit Memory Write TLP 13

#### Chapter 3 PCIe Endpoint Design 17

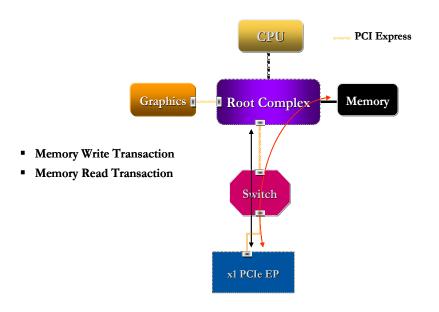

- Figure 3.1 Basic Memory Transactions 17

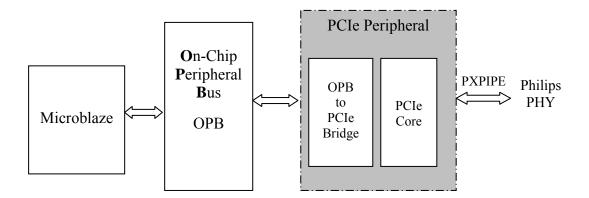

- Figure 3.2 Endpoint Design 19

- Figure 3.3 Xilinx Virtex-5 LXT PCI Express Endpoint Block [UG197] 19

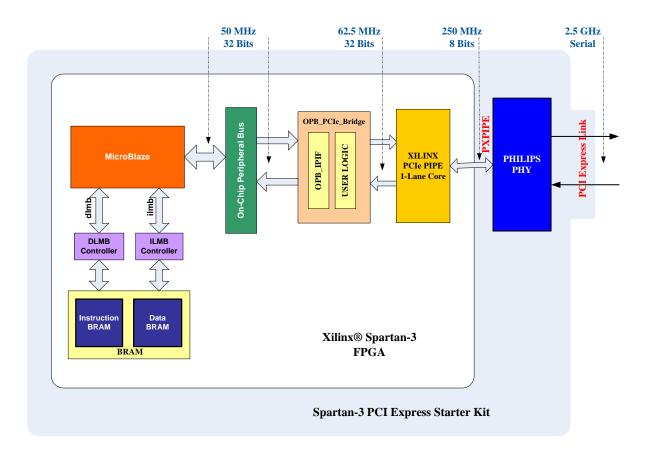

- Figure 3.4 Spartan-3 PCI Express Starter Kit [Xilinx] 20

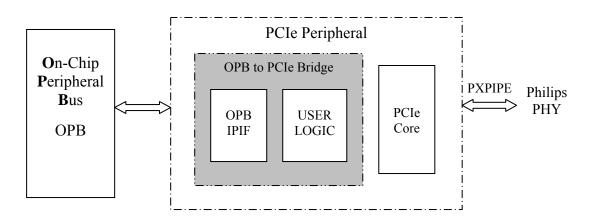

- Figure 3.5 Complete PCIe Endpoint Device 21

- Figure 3.6 Block Diagram of PX1011A [GL05] 23

- Figure 3.7 PCIe Differential Transmitter/Receiver [ABS04] 24

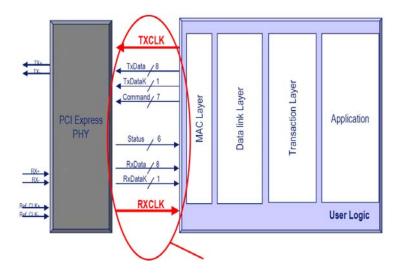

- Figure 3.8 PIPE Interface [PPHY] 25

- Figure 3.9 PXPIPE Interface [PPHY] 25

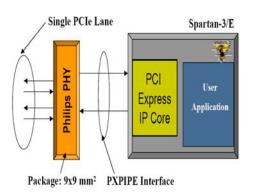

- Figure 3.10 Two-chip Solution [XP05] 27

- Figure 3.11 Top-level Functional Blocks Diagram and Interfaces of Xilinx PCIe Core [XUG167] 28

- Figure 3.12 PCIe Configuration Space [XUG167] 30

- Figure 3.13 PCIe Component Name [XUG167] 39

- Figure 3.14 PCIe ID Initial Values [XUG167] 39

- Figure 3.15 PCIe Base Address Registers (BARs) Configuration 40

- Figure 3.16 PCIe Capabilities and Device Capabilities Register Configuration [XUG167] 41

- Figure 3.17 PCIe Link Capabilities Register Configuration [XUG167] 41

- Figure 3.18 PCIe Advanced Settings [XUG167] 42

- Figure 3.19 Microblaze Block Diagram [XUG081] 43

- Figure 3.20 Local Memory Bus (LMB) 44

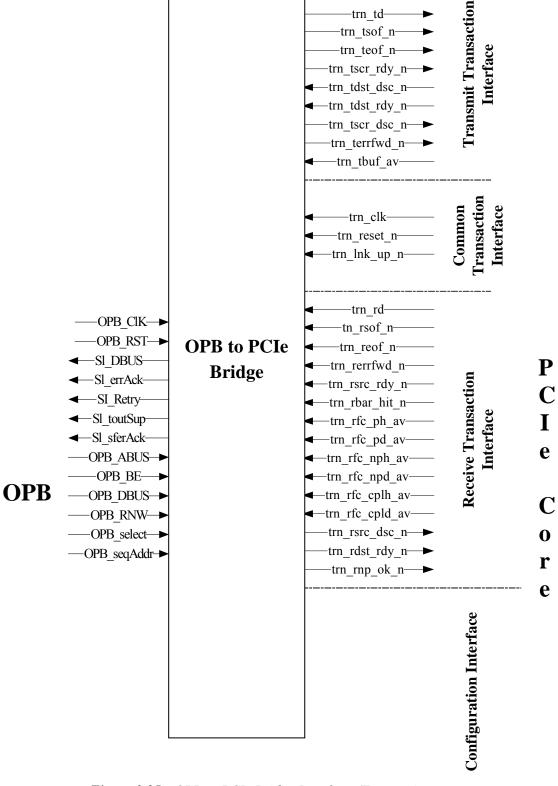

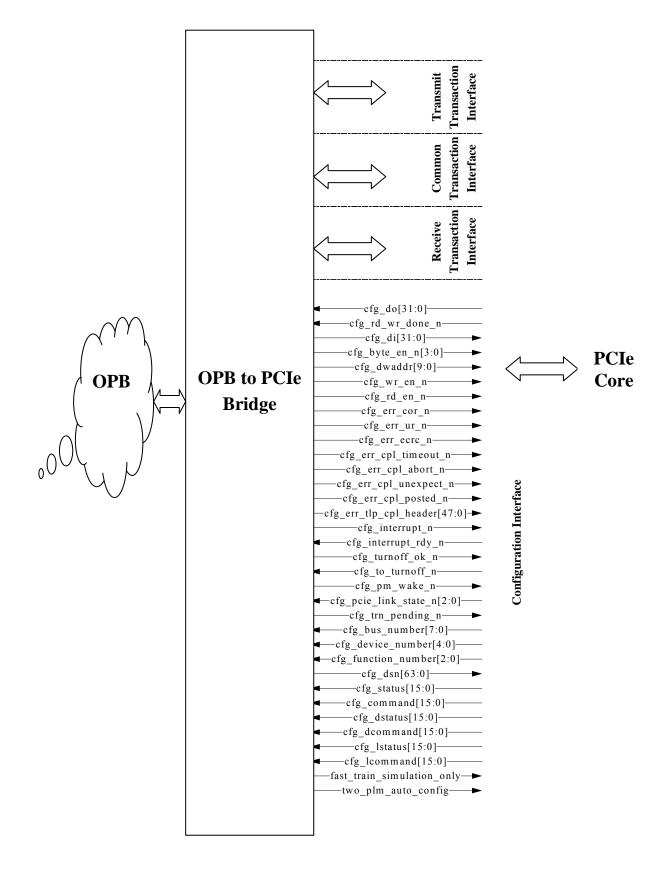

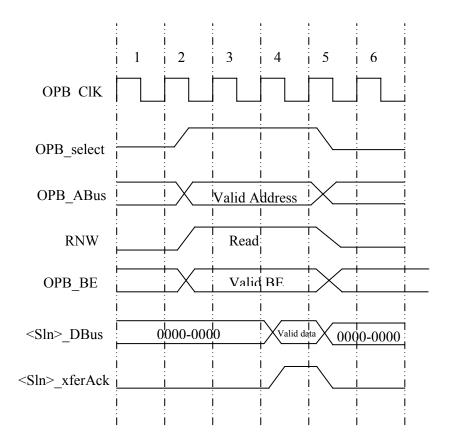

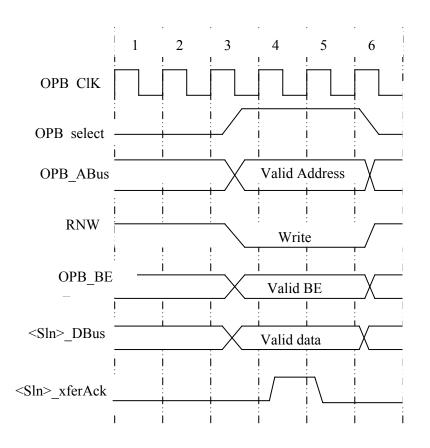

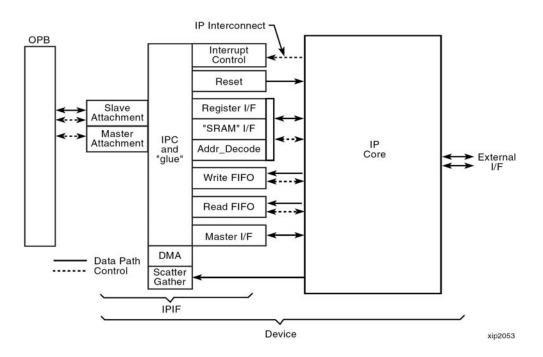

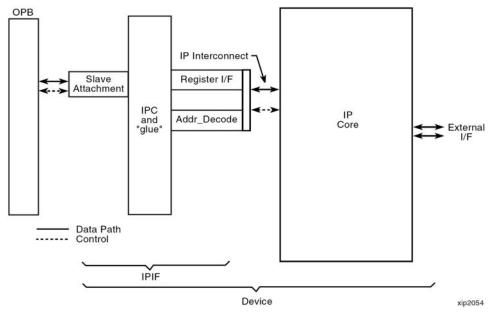

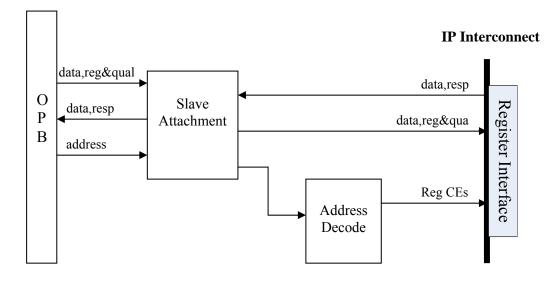

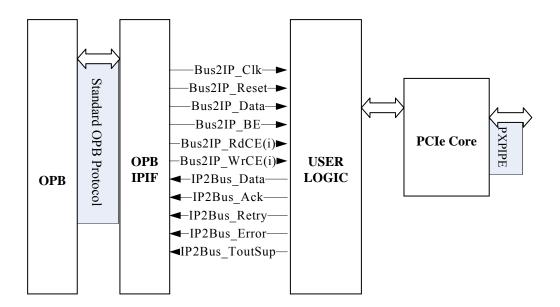

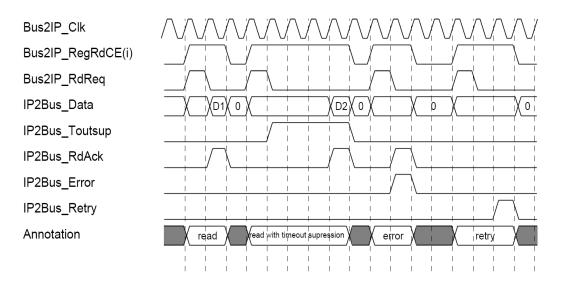

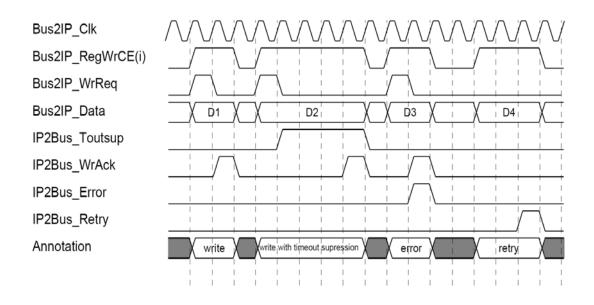

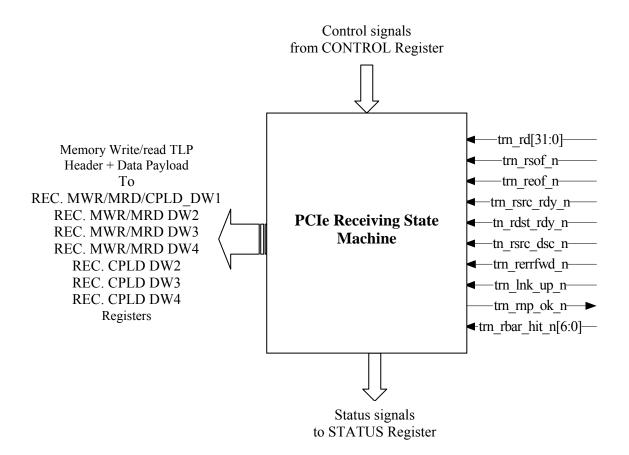

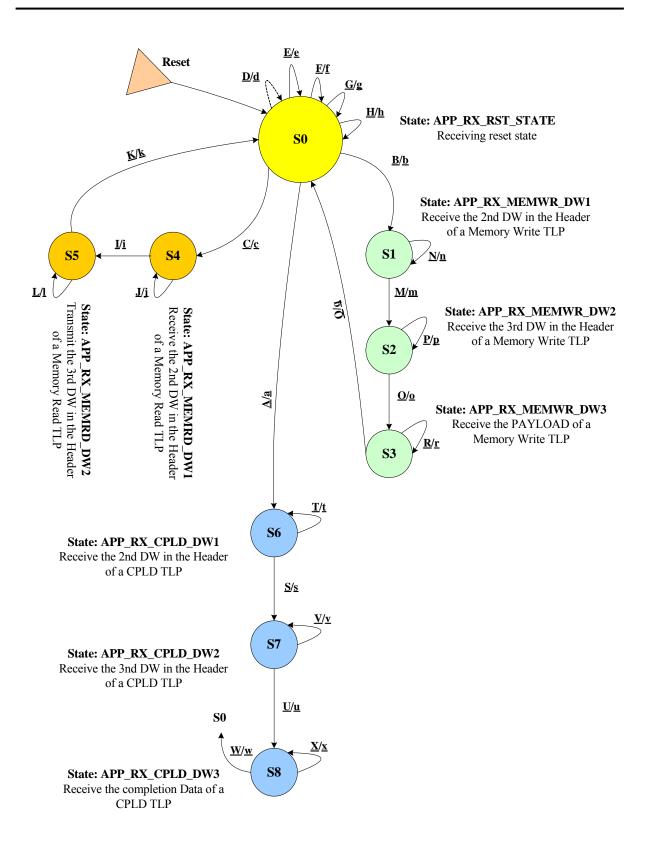

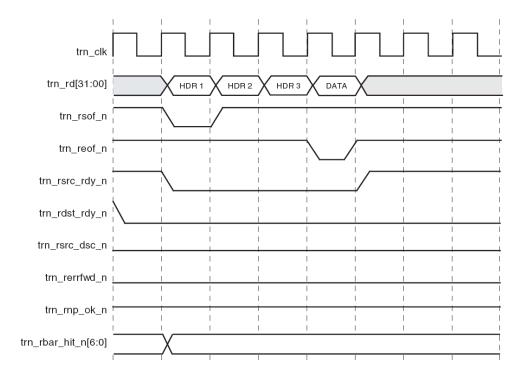

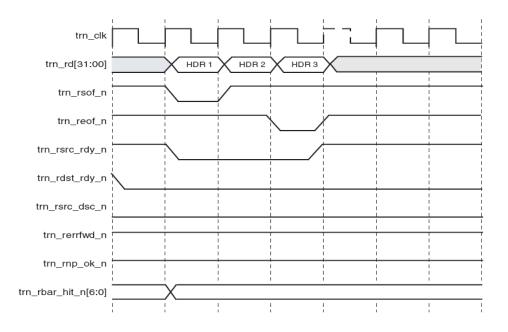

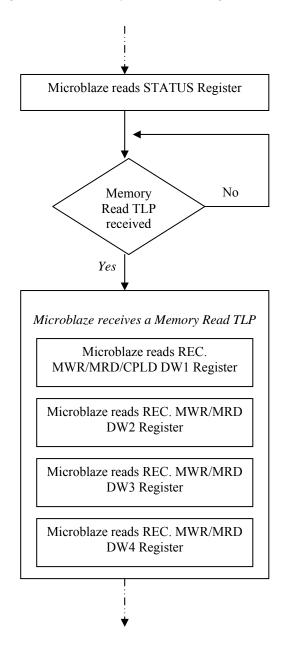

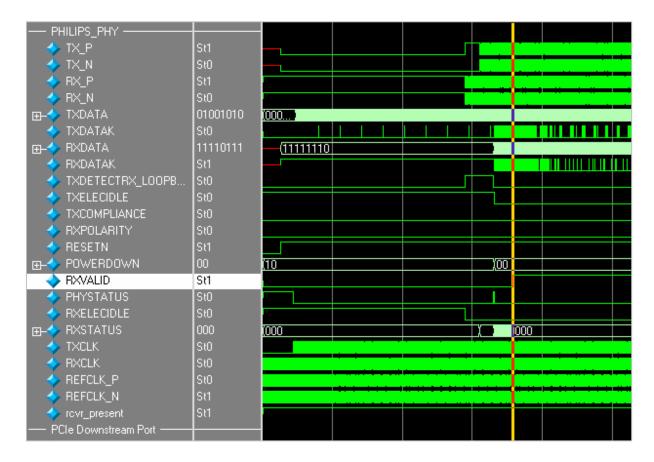

Figure 3.21 - OPB Slave Attachment [XTZ02] 45 Figure 3.22 - PCIe Peripheral Attachment as Slave [XTU02] 46 Figure 3.23 - PCIe Peripheral 47 Figure 3.24 - OPB to PCIe Bridge 47 Figure 3.25 - OPB to PCIe Bridge Interfaces/Transaction Interfaces 48 Figure 3.26 - OPB to PCIe Bridge Interfaces/Configuration Interfaces 49 Figure 3.27 - Basic OPB Read Transaction [XTU02] 50 Figure 3.28 - Basic OPB Write Transaction [XTU02] 51 Figure 3.29 - Full Set of OPB IPIF Features [XTU02] 52 Figure 3.30 - OPB IPIF Features for Register Access [XTU02] 52 Figure 3.31 - OPB IPIF Top-level Block Diagram, Register Interface Only [XDS414] 53 Figure 3.32 - USER LOGIC Interfaces 54 *Figure 3.33* - *Read Transaction from IP that utilizes Register Decodes [XDS414]* 55 Figure 3.34 - Write transaction to IP that utilizes Register Decodes [XDS414] 56 Figure 3.35 - USER LOGIC Internal structure 57 Figure 3.36 - Register Bank, Base Address and Offset are in Hexadecimal 58 Figure 3.37 - Registers Big-Endian Format [XUG081] 58 Figure 3.38 - STATUS Register 58 Figure 3.39 - CONTROL Register 59 Figure 3.40 - MWR/MRD HDR DW1 Register 60 Figure 3.41 - MWR/MRD HDR DW2 Register 62 Figure 3.42 - MWR/MRD HDR DW3 Register 62 Figure 3.43 - REC. MWR/MRD/CPLD DW1 Register 63 Figure 3.44 - REC. CPLD DW2 Register 63 Figure 3.45 - REC. CPLD DW3 Register 64 Figure 3.46 - REC. MWR/MRD DW2 Register 64 Figure 3.47 - PCIe Transmission State Machine 66 Figure 3.48 - PCIe Transmission State Machine State Diagram 68 Figure 3.49 - Memory Write TLP with a 3 DW Header and Payload [XUG167] 69 Figure 3.50 - Memory Read TLP with a 3 DW Header without Payload [XUG167] 70 Figure 3.51 - PCIe Receiving State Machine 71 Figure 3.52 - PCIe Receiving State Machine State Diagram 73 Figure 3.53 - Received 32-bit Addressable Memory Write TLP [XUG167] 74 Figure 3.54 - Received 32-bit Addressable Memory Read TLP [XUG167] 74 Figure 3.55 - PCIe Configuration Space Access READ/WRITE State Machine 76 Figure 3.56 - PCIe Configuration Space Access READ/WRITE State Machine State Diagram 78 Figure 3.57 - Reading of PCIe Configuration Space [XUG167] 79 **Chapter 4** PCIe Endpoint Simulation 80

#### Figure 4.1 - PCIe Testbench Top-level 80

Figure 4.2 - PX1011A Packaged Model [PUG05] 81

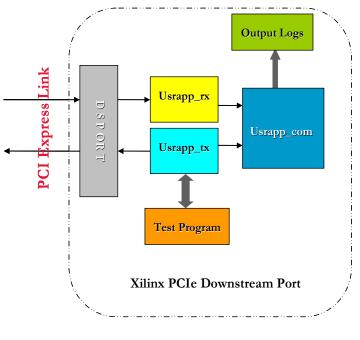

- Figure 4.3 PCIe Downstream Port Model 82

- Figure 4.4 Functional Block Diagram of the PCIe Downstream Port Model 82

- Figure 4.5 Top level of DUT Model 83

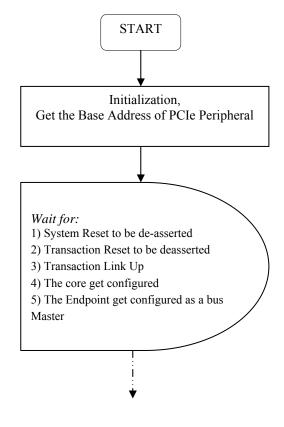

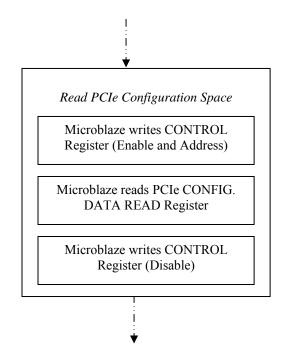

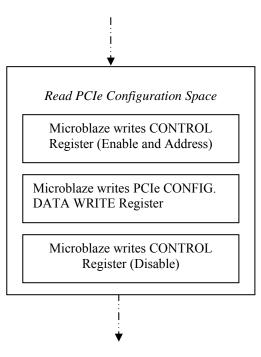

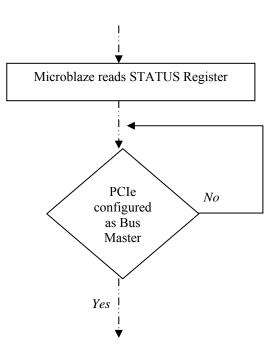

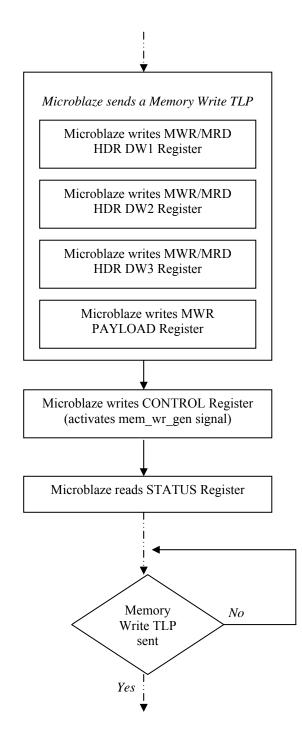

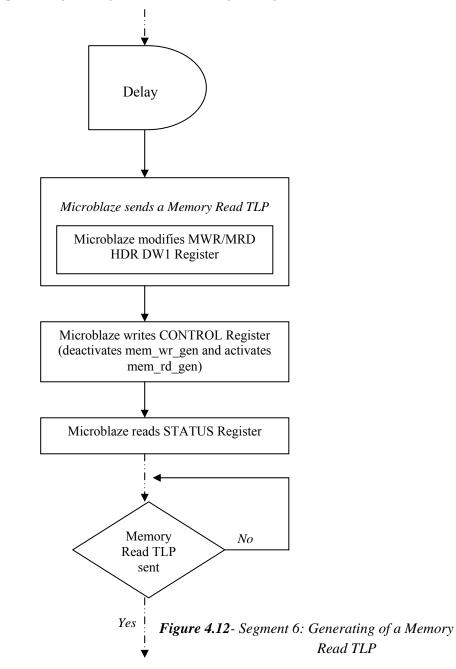

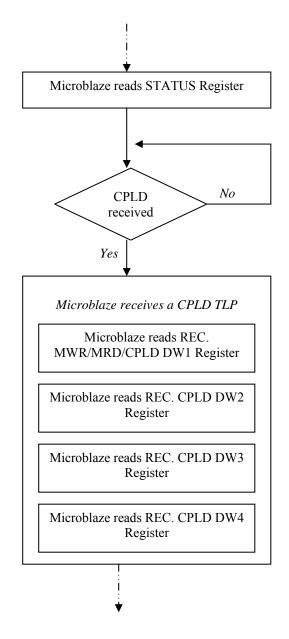

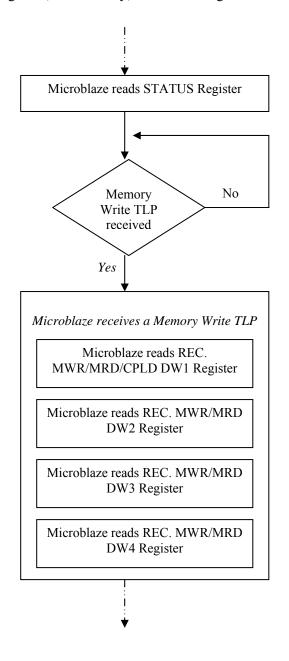

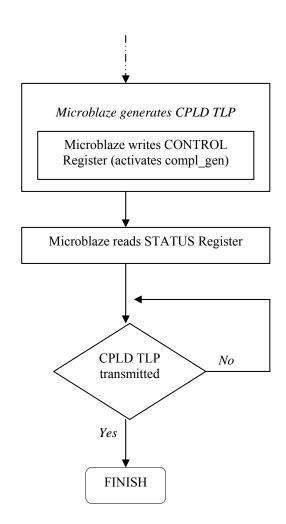

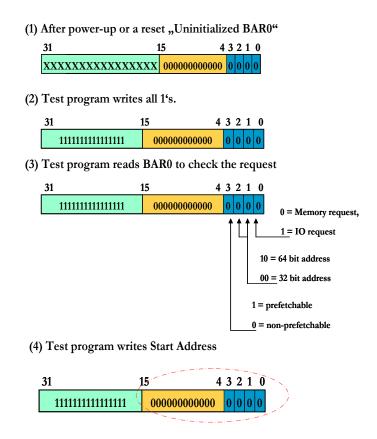

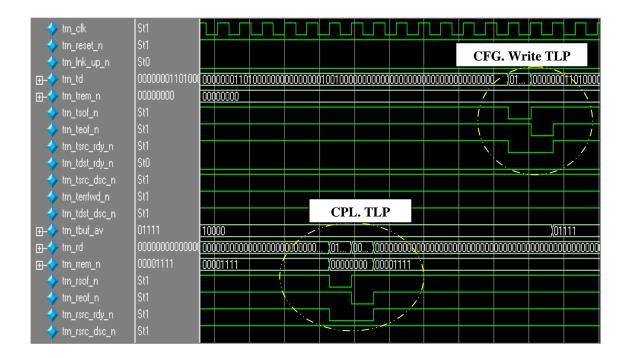

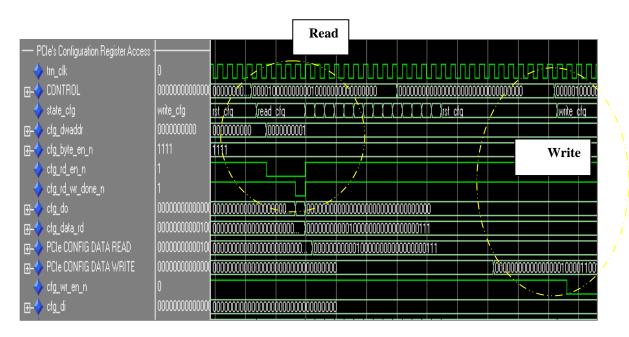

Figure 4.6 - Top-level of Microblaze Based System Simulation Model 84 Figure 4.7 - Segment 1: Initialization and Configuration of the PCIe Core 85 Figure 4.8 - Segment 2: PCIe Core Configuration Space Read 86 Figure 4.9 - Segment 3: PCIe Core Configuration Space Write 86 Figure 4.10 - Segment 4: Bus Master Enable 87 Figure 4.11 - Segment 5: Generating of a Memory Write TLP 88 Figure 4.12 - Segment 6: Generating of a Memory Read TLP 89 Figure 4.13 - Segment 7: Receiving of a CPLD 90 Figure 4.14 - Segment 8: Receiving of a Memory Write TLP 91 Figure 4.15 - Segment 9: Receiving of a Memory Read TLP 92 Figure 4.16 - Segment 10: Generation of a CPLD TLP 93 Figure 4.17 - Simulation Flow Stage 1 94 Figure 4.18 - Symbol Lock/PXPIPE Waveforms 95 Figure 4.19 - PCIe Downstream Port Waveforms 96 Figure 4.20 - Simulation Flow Stage 1 (Continued) 96 Figure 4.21 - Setting of PCIe Configuration Space 97 Figure 4.22 - Transmission Output Logging 98 Figure 4.23 - Reception Output Logging 98 Figure 4.24 - Transmitting Output Logging/Writing BAR0 Starting Address 99 Figure 4.25 - Waveforms of Configuration Write and CPL TLPs 99 Figure 4.26 - Simulation Flow Stage 2 100 Figure 4.27 - PCIe Core Configuration Space Access Waveforms 100 Figure 4.28 - Simulation Flow Stage 3 101 Figure 4.29 - Simulation Flow Stage 3 Waveforms 102 Figure 4.30 - Simulation Flow Stage 4 Waveforms 102 Figure 4.31 - Simulation Flow Stage 4 103 Figure 4.32 - Test Cases 1 and 2 104

#### 5 PCIe Endpoint Implementation 106

#### 6 Conclusion and Future Work 107

#### Appendix A: PCIe IP Providers 108

Figure A.1 – PCIe IP Providers 108

#### Appendix B: Xilinx WebCases 121

#### Appendix C: Project Directory Structure 122

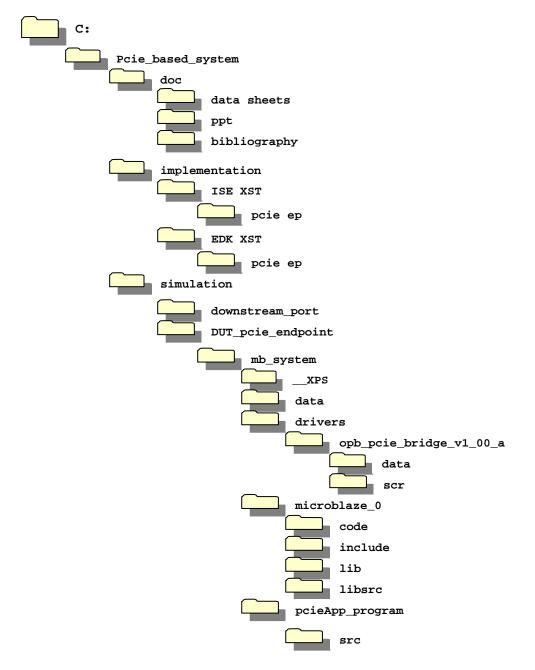

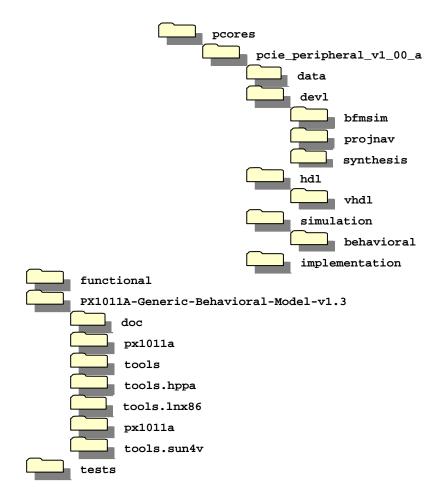

*Figure C.1* - *Project Directory Structure* 122 *Figure C.1* - *Project Directory Structure (Cont.)* 123

#### **Bibliography 124**

#### Chapter 1 Introduction 1

Chapter 2 PCI Express Theory 4

#### Chapter 3 PCIe Endpoint Design 17

- Table 3.1 PHY Interfaces to the PCIe Link 24

- Table 3.2 Philips PHY Interfaces to the Xilinx PCIe Core [KPE05] 26

- Table 3.3 PCIe Core Specification [XUG167]

27

- Table 3.4 PXPIPE Transmit Data Interface Signals [XUG167] 31

- Table 3.5 PXPIPE Receive Data Interface Signals [XUG167]

31

- Table 3.6 Clock and Reference Signals [XUG167] 31

- Table 3.7 PXPIPE Command Interface Signals [XUG167]

32

- Table 3.8 PXPIPE Status Interface Signals [XUG167]

32

- Table 3.9 Xilinx PCIe PIPE Endpoint Core Transaction Receive Interfaces [XUG167]

34

- Table 3.9 Xilinx PCIe PIPE Endpoint core Transaction Receive Interfaces (Cont.) [XUG167]

35

- Table 3.10 Xilinx PCIe Core Configuration Interfaces [XUG167]

36

- Table 3.10 Xilinx PCIe PIPE Endpoint Core Configuration Interfaces (Cont.) [XUG167]

37

- Table 3.10 Xilinx PCIe PIPE Endpoint Core Configuration Interfaces (Cont.) [XUG167]

38

- Table 3.11 OPB Global Signals45

- Table 3.12 OPB Interface Signals 45

- Table 3.12 OPB Interface Signals (Cont.) 46

- Table 3.13 PCIe Transmission State Machine Transition Table

67

- Table 3.14 PCIe Receiving State Machine Transition Table

72

- Table 3.15 Registers Mapped Directly onto the Configuration Interface of the Core

75

- Table 3.16 PCIe Configuration Space Access READ/WRITE State Machine Transition Table

77

#### Chapter 4 PCIe Endpoint Simulation 80

#### 5 PCIe Endpoint Implementation 106

Table 5.1 - Device Utilization 106

#### 6 Conclusion and Future Work 107

#### Appendix A: PCIe IP Providers 108

- Table A.1 Features of Physical Layer and Data Link Layer 110

- Table A.1 Features of Physical Layer and Data Link Layer (Cont.) 111

- Table A.1 Features of Physical Layer and Data Link Layer (Cont.)

112

- Table A.2 Features of the Transaction Layer 113

- Table A.2 Features of the Transaction Layer (Cont.) 114

- Table A.2 Features of the Transaction Layer (Cont.) 115

- Table A.2 Features of the Transaction Layer (Cont.) 116

- Table A.3 General Key Features 117

- Table A.3 General Key Features (Cont.) 118

- Table A.3 General Key Features (Cont.) 119

- Table A.3 General Key Features (Cont.) 120

#### Appendix B: Xilinx WebCases 121

Table B.1 - WebCase Summary 121

#### Appendix C: Project Directory Structure 122

Table C.1 - Project Directory Structure

122

**Bibliography 124**

## 1 Introduction

#### 1.1 Objectives

The main purpose of this diploma work is to demonstrate the capabilities of the third generation IO Interconnect bus system, the so-called PCI Express. To achieve this purpose, two sub-objectives are aimed to:

- Preparing a kind of PCIe tutorial (PowerPoint- Presentation) for the fast entry in the PCI Express technology. These presentations provide the Know-How required for someone to use this technology for the fist time. In addition, some of the available solutions in the market for the implementation of PCI Express are to be studied, discussed and compared.

- Designing of a PCI Express-based embedded system for customer reference. In this system an intelligent Endpoint device, employing this technology, should be able to write a double word (DW = 32 bits) to a location within the system memory and read this data back. This system should also enable data communication between the CPU through the Root Complex and this Endpoint device.

#### 1.2 Method, Software and Hardware

*PCI Express theory* has been acquired through an extensive reading of two reference books. Namely, the PCI Express System Architecture and PCI System Architecture by MindShare, Incorporated. The PCI Express Base Specification v1.0 - 2002 and others were additional valuable references as well.

*XILINX*, which leads the Programmable Logic Device (PLD) market, one of the fastest growing segments of the semiconductor industry, was the source of most of the used Intellectual Property (IP) solutions, which are functions designed for the implementation in the Field Programmable Gate Array (FPGA) devices. Throughout this documentation the Intellectual Property will be referred to as *IP*. Xilinx provides many of these ready optimized and compiled IP solutions. Xilinx accompanies these with data sheets, manuals and detailed descriptions, which provide a paramount help. For the use of the available development tools, Xilinx reports several tutorials and demos, which were extensively used to assist the designing of the embedded system. Xilinx also gives the opportunity for consultancy and technical supporting, through what it calls webcases. During this diploma work, several webcases were opened, discussed, and successfully solved with engineers from this company.

*Xilinx PCI Express Physical Interface for PCI Express (PIPE) Endpoint 1-Lane IP core* was used to implement the protocol layers of the PCI Express architecture. In the remainder of this documentation, this core will be referred to as *PCIe core*.

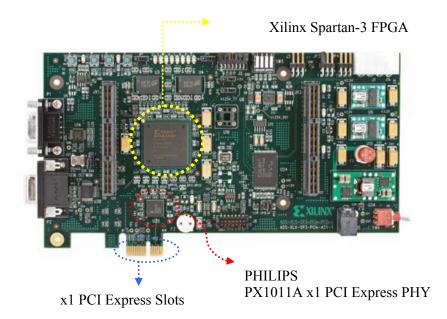

An evaluation licence of this core was received in a package, along with the Spartan-3 PCI Express Starter Kit. On which the designed system is to be implemented. The core was generated, configured and customized using the Xilinx CORE generator.

The Xilinx Spartan-3 FPGA and Philips PX1011A PHY demonstrate a two-chip solution for designing such a system. The Microblaze processor soft core IP was embedded in the Endpoint, to make it an intelligent device. The Microblaze based embedded system and the PCIe PIPE core, are to be implemented in the Spartan-3 FPGA.

The XPS (Xilinx Platform Studio), a part of Xilinx EDK (Embedded Development Kit) 8.2i, and the SDK (Software Development Kit) were used to design the Microblaze based system.

PX1011A PHY is a discrete chip used to implement the physical layer of the PCIe protocol. For the simulation, a behaviour model of this chip was received as a packaged model from NXP Semiconductors. This model interfaces the simulation tool using the Verilog HDL Programming Language Interface (PLI).

Xilinx provides a complete PCIe simulation testbench. In a customized version of this testbench and with the help of the simulation tool ModelSim SE, the whole system was simulated.

Synplify Pro 8.1 and ISE (Integrated Software Environment) 8.2i were used to synthesize the PCI Express based Embedded System.

ISE 8.2i was used to prepare the implementation of the design in the Xilinx programmable logic device.

#### 1.3 Tasks and Time Plan

The tasks carried out were divided into two parts: a theoretical part regarding the theory of PCI Express and the preparing of the power point presentations, and a practical part regarding the implementation of the data transfer system. These two main tasks were further divided into the following subtasks:

- PCI Express theory: reading, studying and researching

- Preparation of PCIe tutorial and presentations to the chip design team at Siemens.

- Overview of the different available PCIe IP solutions in the market, studying and comparing.

- Specification of a microprocessor system (Microblaze) with PCIe links.

- Implementation of the system in Register Transfer Level (RTL) using Very High Speed Integrated Circuit Hardware description Language (VHSIC-HDL or VHDL).

- Software development for the data transfer.

- Simulation and functionality verification.

- FPGA prototyping including measurements (optional).

- Documentation of the work, including an experience report.

This project was accomplished in four phases, over duration of 8 months.

#### 1.4 Outline

After the brief introduction in chapter one, chapter two will summarize the most important aspects of the PCI Express bus system. It starts with a short introduction to the evolution of IO bus systems. In this chapter, the PCI bus architecture, its key features, practical limitations, challenges and shortcomings are discussed. Furthermore, the PCIe bus system is introduced. Its topology and architecture are then discussed. The functionality of each layer in the PCIe architecture is finally illustrated through an example of a Memory Write Transaction.

Chapter three is dedicated to the design of a PCI Express based Endpoint. First, an overview of the design is given. The Microblaze based Endpoint device is presented next. The complete design is overviewed. Then all the components and IPs building up the system are discussed. The PX1011A PHY physical layer, its block diagram, operational principle and interfaces are demonstrated. After this, the PCIe core, its block diagram, functionality, features, interfaces, generation and configuration are discussed. The Microblaze core, its interfaces, the Local Memory Bus (LMB) and the On-chip Peripheral Bus (OPB) are also explained in this chapter. The final section of this chapter concentrates on the design of the Microblaze PCIe peripheral. This includes a detailed description of the developed OPB to PCIe Bridge, its internal structure, interfaces, and functionality.

Chapter four presents the simulation of the designed PCIe Endpoint. It introduces the simulation models of each functional block in this Endpoint device. In this chapter the PCIe Downstream Port simulation model provided by Xilinx is explained. Its integration into the PCIe Testbench is also demonstrated. Then, a detailed description of the C application program executed by the Microblaze is given. The next section in this chapter provides the simulation flow, followed by a summary of the conducted testcases.

Finally, chapter 5 brings some conclusions and highlights future work.

# 2 PCI Express Theory

#### 2.1 Evolution of IO Bus Systems

Since the 1980s till nowadays, many bus systems have been developed to serve different electronic devices, computing and communication platforms.

Figure 2.1 depicts the evolution of IO bus systems. The first IO buses generation, which is located at the bottom of the figure, was introduced in the 1980s, including the Industry Standard Architecture (ISA), which enables a very low bandwidth of 16.7 Mbytes/s, a sufficient one at that time. Extended ISA (EISA) and Video Electronics Standards Association (VESA) are other buses of this generation.

In the 1990s, the second IO buses generation was started with different buses. In 1993 the PCI 33 MHz bus was released. At that time, a 32-bit version of this bus was enough to deliver a bandwidth of 133 Mbytes/s, which met the bandwidth requirements of the available IO peripherals. A 64-bit version of this PCI bus delivers a bandwidth of 266 Mbytes/s [AS99].

However, due to the increase in the processor speeds and the bandwidth needs of new developed IO technologies, the PCI bus frequency was increased in 1995 from 33 to 66 MHz, to increase the bandwidth from 133 Mbytes/s to 266 Mbytes/s for a 32-bit PCI, and from 266 Mbytes/s to 533 Mbyte/s for a 64-bit PCI, correspondingly [ABS04].

Several practical limitations of the PCI 66 MHz bus and the emerging of new high end system technologies that continued asking for higher bandwidths led in 1999, to the releasing of a new generation of the PCI called the PCI-X bus.

Figure 2.1 - Evolution of IO bus systems

The PCI-X bus has frequencies of 66 and 133 MHz and enables a bandwidth up to 1.066 Gbytes/s. These frequencies were increased to 266 and 533 MHz in the first quarter of 2002, to increase the bandwidth provided up to 4 Gbytes/s [ABS04].

Another bus system in the second generation is the Accelerated Graphics Port (AGP). A x1 AGP bus, for example, enables a bandwidth of 266 Mbyte/s and a x8 AGP can enable a bandwidth of up to 2.1 Gbytes/s.

However, in order to meet the higher bandwidth requirements and to satisfy the bandwidth hungry devices, a new bus system was still needed.

The third and latest generation IO bus system is the PCIe, which was released in the second quarter of 2002. It evolved from the PCI and overcame the limitations of the PCI. The PCI Express (which is currently being adopted as general purpose IO devices interconnect in different applications) began shipping in standard desktop PCs in 2004. A x1 PCIe bus provides theoretically a bandwidth of 500 Mbytes/s, a x16 PCIe can provide up to 8 Gbytes/s, and a x32 provides 16 Gbytes/s [ABS04].

Next, the PCI bus system including its architecture, key features, practical limitations, and challenges will be explained.

After that, an illustration of the PCIe bus system architecture, key advantages, and future prospectives will follow.

#### 2.2 Peripheral Component Interconnect (PCI)

#### 2.2.1 PCI Architecture

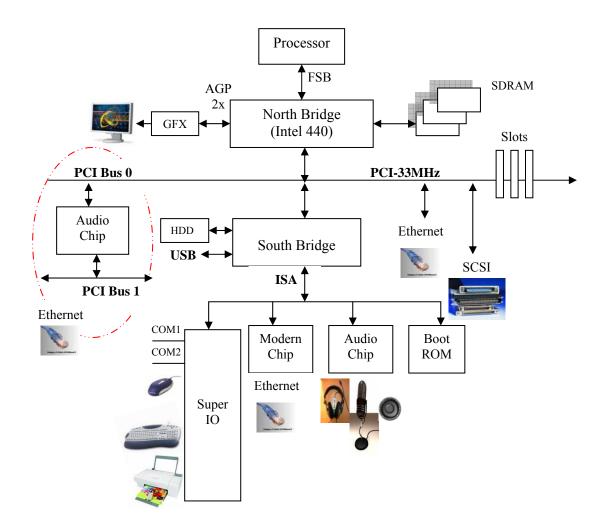

Figure 2.2 illustrates an example of a *33 MHz PCI* bus based system, which consists of a processor bus to PCI bus Bridge, called the *North Bridge*, to which the Accelerated Graphics Port (AGP), system memory, and the 33 MHz PCI buses are connected. The PCI bus is bridged to the ISA bus over the so-called *South Bridge*, to which additionally the Integrated Device Electronics bus (IDE) and the Universal Serial Bus (USB) are connected.

The PCI bus is a multi-drop parallel interconnect which uses a shared bus topology (the bus bandwidth is shared) to allow data communication among the different devices that share the bus including the CPU.

The PCI bus operating at 33 MHz and 32 bits provides a peak theoretical bandwidth of 132 Mbytes/s. A bandwidth of 266 Mbytes/s is possible by extending the bus to 64 bits [ABS04].

Theoretically, up to 32 devices can be connected on a PCI bus. Due to some signal timing restrictions, the PCI bus cannot support more than 10-12 loads (or 5-6 connectors); each connector is equivalent to 2 loads [ABS04]. However, it is possible to connect more devices to the PCI bus by implementing a PCI-to-PCI bridge, as depicted in figure 2.2.

Figure 2.2 - An Example of 33 MHz PCI Bus Based System [ABS04]

Figure 2.3 shows an example of a *66 MHz PCI* bus based system, in which the latest generation of Intel PCI chipsets is used, where North and South bridges are replaced with a Memory Controller Hub (MCH) and an IO Controller Hub (ICH), respectively. A Hub link connects both of these hubs together. The figure also shows each 66 MHz PCI bus is accessed over a P64H (PCI 64-bit Hub) bridge connected to the MCH via Hub Link buses.

Figure 2.3 - An Example of 66 MHz PCI Bus Based System [ABS04]

The 66 MHz PCI bus system supports a bandwidth requirement of 533 Mbytes/s, and one connector to which a device can be connected, while the PCI-X can support from 8 to 10 loads or 4 connectors at 66 MHz and 3 to 4 or 1 to 2 connectors at 133 MHz. The peak bandwidth achievable with 64-bit/133 MHz PCI-X is 1064 Mbytes/s. A further improvement to the PCI-X is the *PCI-X 2.0* bus, which supports either Dual Data Rate (DDR) or Quad Data Rate (QDR) data transport, and provides a peak bandwidth capability of 4256 Mbytes/s for a 64-bit 533 MHz effective PCI-X bus [ABS04].

#### 2.2.2 PCI Key Features

The PCI bus overcame the limitations of its predecessors and had several advantages over them.

Referring to figure 2.2, one can see a kind of partitioning into two hubs, the MCH and the ICH. Indeed, this provides a kind of processor independency and buffered separation. Separating the CPU local bus from the PCI bus, gives the ability to run simultaneous cycles on the CPU and PCI buses. It also allows the CPU local bus to increase its frequency accompanied by a change in the memory bus, independent of the PCI bus speed and loading.

The PCI bus provides a bus mastering connectivity, where the PCI devices arbitrate to access the bus and master the bus transaction directly instead of waiting for the CPU to serve them. This results in reducing the overall latency.

Another advantage of the PCI bus is the plug and play operation, which allows devices to be automatically detected and configured.

#### 2.2.3 PCI practical Limitations and challenges

The PCI bus has limited bandwidth capabilities, which makes it an unsatisfying choice for several applications, which require a higher bandwidth.

In the industry, two ways are followed to adapt the performance of a bus system to the devices' requirements: increasing the number of signals, or increasing the signal frequency. In both cases, the bus system reaches its limitations. Both solutions also add extra costs to the development phase.

The PCI bus's frequency cannot be scaled up, and its voltage cannot be scaled down. It faces some time restrictions and stringent signal routing rules.

The PCI bus implements a shared bus topology, in which many devices share the same bus. Some of these devices can monopolize more than 80% of the available PCI bus bandwidth.

PCI bus efficiency is reduced. This reduction is due to several factors:

- Masters and slaves are allowed to insert wait states in the bus cycle. Slower devices will make the transfer on the bus slower.

- The transfer size on the bus is not indicated, which leads to an inefficiency in the buffer management within both the master and slave devices.

- The handling of delayed transactions on the PCI bus is inefficient.

- The architecture of PCI follows strict ordering rules as defined by the PCI specification.

- The way the PCI architecture handles the interrupts is inefficient, because many devices share the same PCI interrupt signal, which imposes additional time latency in discovering which of these devices has generated the interrupt.

The PCI bus does not support real-time data transfer services. As many applications today require the data streaming from video and audio devices, the bus must set some priorities in processing these time-dependent data in a process called the Quality of Services (QoS).

This bus also does not provide advanced power management features, which are required by many modern electronic devices.

All these limitations and challenges have motivated the developing of a new IO bus generation. The PCI Express bus system was the result of the developments carried out by Intel. This PCIe bus system was brought to the market in 2004, and is now used as a general IO Interconnect in diverse applications.

The PCIe bus system is discussed next. Its topology, architecture and layer structure are explained.

#### 2.3 Peripheral Component Interconnect Express (PCIe)

#### 2.3.1 PCIe Introduction

Unlike the PCI bus, the PCIe bus is serial. Figure 2.4 shows a PCIe *Link*, which implements a high performance, high speed, point-to-point, dual simplex, low-pin-count and differential signalling Link for interconnecting devices. This bus system was developed to overcome the limitation of the original PCI bus.

Figure 2.4 - PCI Express Link [ABS04]

The PCIe link shown in the figure implements the physical connection between two devices. A PCIe interconnect is constructed of either a x1, x2, x4, x8, x12, x16 or x32 point-to-point link. A x1 Link has 1 *Lane* or 1 differential signal pairs in each direction, transmitter and receiver, with a total of 4 signals. Correspondingly, x32 Link has 32 Lanes or 32 signal pairs for each direction, with a total of 128 signals [ABS04].

PCIe employs a packet-based communication protocol with a split transaction. Communication in this bus system includes the transmission and reception of packets called Transaction Layer packets (TLPs).

The transactions supported by PCIe protocol can be grouped into four categories: Memory, IO, Configuration, and Message transactions.

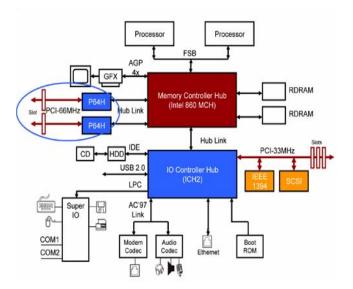

#### 2.3.2 PCIe Topology

The PCIe topology shown in figure 2.5 contains different components. A Root Complex, PCIe switches, PCIe Endpoints, Legacy Endpoints, and optional PCIe to PCI bridges.

The *Root Complex* connects the CPU and the memory to the PCIe fabric. For instance, an Intel chipset could be used as a Root Complex.

The main purpose of the Root Complex is to generate transaction and configuration requests on behalf of the CPU.

PCIe implements a switch-based topology in order to interconnect multiple devices. These *Switches* implement multiple, logical, and virtual bridges.

Shown in the figure are switches with one upstream port that points in the direction of the root complex, and two downstream ports, which point in the opposite direction. These switches can have any number of ports.

*PCIe Endpoint (EP)* is a device which can be a requester that originates a PCIe transaction or a completer that responds to a PCIe transaction addressed to it.

As mentioned above, these Endpoints can posses a x1, x2, up to x32 link. PCIe Endpoints are peripheral devices such as Ethernet, USB or graphic devices. *Legacy Endpoint* does not support all the transaction like the PCIe Endpoint.

In order to connect some PCI devices to the PCIe fabric, a PCIe to PCI Bridge must be used.

Figure 2.5 - PCI Express Topology

#### 2.3.3 PCIe Key Features

The shared bus topology used for PCI is replaced with a shared switch, which provides each device, with a direct access to the bus.

In a PCIe based system, unlike the parallel PCI bus system, data is sent serially in packet based protocol.

PCIe bus has an advantageous attribute of frequency and bandwidth scalability, because it implements a point-to-point interconnect, which limits the electrical load on the link, allowing transmission and reception frequencies to be scaled up. Multiple lanes can be used to increase the bandwidth of the PCIe link.

PCIe supports the same address spaces as PCI: memory, IO, and configuration address spaces. Additionally, it enhances the configuration address space by extending it from 256 Bytes to 4 Kbytes [PXS05].

The same transaction types supported by PCI and PCI-X are used by the PCIe. These include Memory Read and Memory Write, IO Read and IO Write, Configuration Read and Configuration Write. The PCIe bus also supports a new transaction type called Message transaction.

PCIe offers a new feature, called the Quality of Service (QoS). This new feature allows the routing of packets from different devices with different priorities.

PCIe uses a flow control mechanism. This ensures that the TLP won't be transmitted unless there is enough space in the receiving device.

PCIe uses Message Signalled Interrupt (MSI) style for handling interrupts. In order to interrupt the CPU, a Memory Write packet is used to write an interrupt vector to the Root Complex, which in-turn interrupts the CPU.

Other features supported by PCIe are the advanced power management features, which enable the design of low power mobile devices. PCIe also supports hot plug and hot swap features. Signalling of such features is carried out in-band using packet based messaging instead of side-band signals. This has the advantage of keeping the device pin count low.

PCIe applies the same programming model as PCI and PCI-X. It also has a configuration model which is compatible with PCI configuration model, shown in figure 2.6. It is also compatible with existing operating systems, bus enumeration and configuration software for PCI/PCI-X [ABS04].

#### 2.3.4 PCIe Architecture

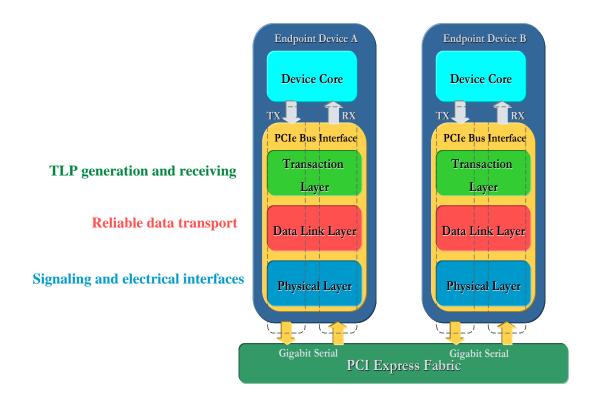

PCIe has a layered architecture as depicted in figure 2.7. It consists of the Transaction Layer, the Data Link Layer and the Physical Layer. On the top of these three layers resides the Software Layer, or device core. Each of these layers is further divided into two sections: transmitter and receiver.

The transmitter is responsible for processing the Transaction Layer Packets requested from the device core before being transmitted across the PCIe link. At the same time, the receiver processes the incoming TLPs before sending them to the device core.

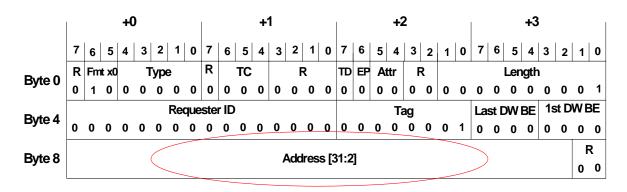

To demonstrate the functionality of PCI Express protocol and for the purpose of this diploma work, 32-bit addressable Memory Write/Read and Completion with Data (CPLD) TLPs will be considered.

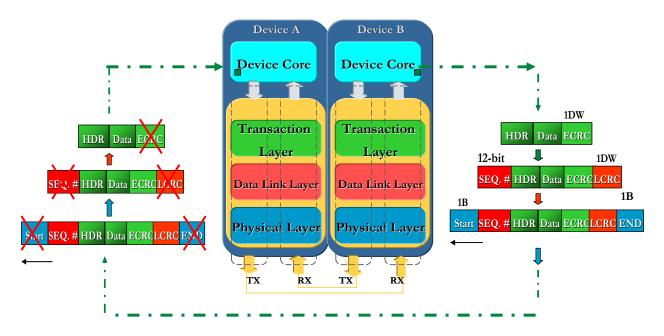

Figure 2.8 shows the assembly and disassembly of a PCIe TLP. It also illustrates the contribution of each layer to this TLP.

Figure 2.6 - PCI Configuration Model [ABS04]

The Memory Write TLP is considered to be a posted transaction where the requester transmits a request TLP to the completer. This in turn does not return a completion TLP back to the requester. Unlike the Memory Read TLP where the completer is supposed to return a completion TLP back to the requester. The completer returns either a Completion with Data (CPLD), if it is able to provide the requested data, or a Completion without data (CPl), if it fails to obtain the requested data.

Figure 2.7 - PCI Express Architecture [XP05]

In the illustration below, the core of device B issues a Memory Write request in order to write some data to a memory mapped location within device A.

Figure 2.8 - PCI Express TLP Assembly/Disassembly

#### **Device Core**

The core of device B, which could be the Root Complex core logic or Endpoint core logic, sends to the transaction layer the information required to assemble the TLP. This information contains the Header (HDR) and the Data Payload (if it exists), because some TLPs do not have data payload, as in the case of Memory Read TLPs.

The size of the Header can vary between 3 and 4 DWs depending on the TLP. 3 DWs are used for 32bit addressable Memory and CPLD TLPs, while the Header with 4 DWs is dedicated to 64-bit addressable Memory TLPs. The maximum size of the data payload is 4Kbytes (1024 DW) [ABS04].

Figure 2.9 depicts the Header of a 32-bit addressable Memory Write request to write data of 1 DW payload to a memory mapped location of 32-bit address within device  $A^1$ .

This Header consists of 3 DWs. In the case of 64-bit addressable Memory TLPs, one more DW is used. Bytes 12 to 15 must be added to the Header shown in the figure.

Figure 2.9 - Header for a 32-bit Memory Write TLP

The figure also shows the different fields in this Header. The following is a detailed explanation of each field:

- Byte0 [7]: *R* (Reserved bit): This bit should be set to zero.

- Byte0 [6:5]: *Fmt* (Packet Format) and Byte0 [4:0]: *Type* (TLP packet Type field) are used in a combination that specifies the transaction type, header size, and whether data payload is present or not (Byte0 [6:0]):

0000000b = Memory Read (3DW without data) 0100000b = Memory Read (4DW without data) 1000000b = Memory Write (3DW with data) 1100000b = Memory Write (4DW with data) 0001010b = Completion (3DW without data)1001010b = Completion (3DW with data)

- Byte1 [7]: *R* (Reserved bit): This bit should be set to zero.

- Byte1 [6:4]: *TC* (Traffic Class): These 3 bits are used to determine the traffic class to be applied to the TLP. There are seven different traffic classes. In this example, the default traffic class was applied to the transmitted TLP:

000 = Traffic Class 0 (Default Class) 001 = Traffic Class 1 010 = Traffic Class 2 011 = Traffic Class 3

- 100 = Traffic Class 4

- 101 = Traffic Class 5

- 110 = Traffic Class 6

- 111 = Traffic Class 7

- Byte1 [3:0]: *R* (Reserved bits): These bits should be set to zeros.

- Byte2 [7]: *TD* (TLP Digest Field Present): If set = 1, the optional 32-bit Cyclic Redundancy Check (CRC) field is included with this TLP. All receivers must check the presence of this field when this TD is set to 1.

- Byte2 [6]: EP (Poisoned data): When set = 1, the payload data with this TLP should be considered corrupted, although the transaction completes normally.

- Byte2 [5:4]: *Attr* (Attributes): Bit 5 = Relaxed ordering: If set = 1, the PCI-X relaxed ordering is enabled for this TLP. Otherwise, strict PCI ordering is used. Bit 4 = No Snoop.

- Byte2 [3:2]: *R* (Reserved bits): These bits should be set to zeros.

- Byte2 [1:0] and Byte3 [7:0]: *length*, TLP data payload transfer size (in DW). Maximum transfer size is 10 bits; 2<sup>10</sup> = 1024 DW (4Kbytes). Encoding [ABS04]:

$00\ 0000\ 0001b = 1DW \\ 00\ 0000\ 0010b = 2DW$

11 1111 1111b = *1023 DW* 00 0000 0000b = *1024 DW*

• Byte4 [7:0] and Byte5 [7:0]: *Requester ID*: Indicates the identification number of the device that generates the TLP. This number is indicated for the purpose of returning a completion TLP.

Byte4 [7:0]: *bus number*, Byte5 [7:3]: *device number and* Byte5 [2:0]: *function number*.

- Byte6 [7:0]: *Tag*: These bits are used to identify each transmitted request issued by the requester. Upon the sending of one request, the next sequential tag is assigned. By default, only 5 bits are used for this tag, which allows 32 outstanding transactions at a time. This number can be extended to 256 tags by having 8 bits used, when configuring the PCIe core by setting the extended tag bit in the PCIe control register = 1.

- Byte7 [7:4]: *Last DW BE*: These bits are used to qualify the bytes in the last sent DW. These byte enables are active high.

A value of "0" indicates that the concerned byte should not be written by the completer of the TLP. It is written otherwise. Since we have the valid transfer data are within only 1 aligned DW, the Last DW BE must be = 0000b.

- Byte7 [3:0]: *1st DW BE*: These bits are used to qualify the bytes in the first sent DW. Since we have the valid transfer data are within only 1 aligned DW, the 1st DW BE must be = 1111b.

- Byte8 [7:0], Byte9 [7:0], Byte10 [7:0] and Byte11 [7:2]: *Address*: 32-bit addressable memory mapped location. This targeted address is used to route the Packet in the PCIe fabric to the intended device.

- Byte11 [1:0]: R (Reserved bits): These bits should be set to zero. Doing so forces the 32-bit start address to be DW aligned.

In figure 2.8, the PCIe based transmitter and receiver are illustrated. The following is an explanation of the role each of the PCIe layers plays when transmitting and receiving TLPs.

#### **Transaction Layer**

The main functionality of the Transaction Layer is the generation of TLPs to be transmitted across the PCIe link and the reception of TLPs received from the PCIe link.

Transaction Layer employs the split transaction protocol, by associating the incoming completion TLP of a certain tag with the transmitted non posted TLP of the same tag.

In this layer, Transmission buffers are included to store the TLPs that wait to be transmitted as well as to store the received TLPs. This layer provides a flow control mechanism, ensuring that the TLP won't be transmitted unless there is enough space in the receiving device.

Also in this layer, the Quality of Service protocol is implemented, which prioritizes the transmission and receiving of TLPs.

The contribution of this layer to the transmitted packet is shown in figure 2.8. This layer appends a 32bit End to End Cyclic Redundancy Check (ECRC). This ECRC is generated based on the whole TLP from the first byte of the Header to the last byte of the data Payload, in order to check for CRC errors in the header and the data Payload. These 32 bits are stripped out of the incoming TLPs before being forwarded to the core of the receiving device (as shown in figure 2.8).

#### **Data Link Layer**

This layer is responsible for ensuring a reliable data transport on the PCIe link. The received TLP from the transaction layer is concatenated with a 12-bit sequence ID and a 32-bit Link CRC (LCRC) as shown in figure 2.7. The LCRC is calculated based on all the bytes within the TLP in addition to the sequence ID. These added bits are stripped out from the incoming TLP by the same layer in the receiving device before being transferred to the Transaction Layer (as shown in figure 2.8).

The Data Link Layer applies a replay mechanism (ACK/NAK) to ensure the transmission of the TLPs across the link. Before sending the TLP, it copies it into a replay buffer. The sequence ID is used to associate this copy with a received ACK/NAK Data Link Layer Packet (DLLP) from the targeted receiver.

This ACK/NAK packet indicates whether the transmitted TLP has been received with or without errors. If no errors are found, the reply buffer is cleared. Until then the stored TLP is sent again and again until it is received properly.

#### **Physical Layer**

The physical layer of a PCIe device is responsible for driving and receiving the Low Voltage Differential Signals (LVDS) at a high speed rate of 2.5 Gbps each way. It interfaces the device to the PCIe fabric. Such an interface is scalable to deliver a higher bandwidth. The physical layer supports for example x1, x2, x4, x8, x12, x16, and x32 lane widths.

The TLPs and DLLPs are transferred to this layer for the purpose of transmission across the link. This layer also receives the incoming TLPs from the link and sends them to the Data Link Layer.

In this layer the data clock is embedded using an 8b/10 encoding algorithm, in order to obtain the high data rate.

Figure 2.8 shows the contribution of this layer to the transmitted packets. It appends 8-bit Start and End framing characters to the packet before being transmitted. The physical layer of the receiving device in-turn stripes out these characters after recognizing the starting and ending of the received packet, and then forwards it to the Data Link Layer.

In addition to that, the physical layer of the transmitter issues Physical Layer Packets (PLPs) which are terminated at the physical layer of the receiver, such PLPs are used during the *Link Training and Initialization* process. In this process the link is automatically configured and initialized for normal operation; no software is involved. During this process the following features are defined: link width, data rate of the link, polarity inversion, lane reversal, bit/symbol lock per lane, and lane-to-lane deskew (in case of multi-lane link).

#### 2.3.5 PCIe future prospective

The current PCIe bus represents the first PCIe bus generation demonstrating a bandwidth capability of 2.5 Gbps. The second and third generations of this bus are expected in the future, and will have bandwidths of 5 Gbps and 10 Gbps, respectively [ABS04].

The layered architecture of PCIe allows such an increase in the bandwidth by redesigning the physical layer only. No modification is required on the other layers. Such architecture leaves the door open for using optical fibers for instance, as a medium to carry packets in the PCIe fabric.

# **3** PCIe Endpoint Design

#### 3.1 Design Overview

Figure 3.1- Basic Memory Transactions

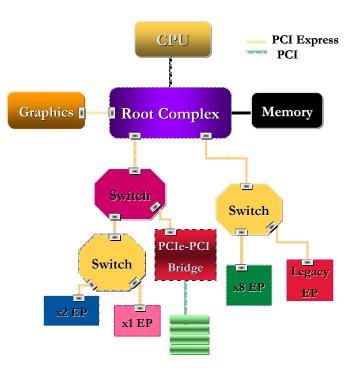

Figure 3.1 shows the PCIe topology again. For design purposes, the x1 PCIe Endpoint will be considered.

In this illustration, the Endpoint is an intelligent device which acts as a target for downstream TLPs from the CPU through the Root Complex and as an initiator of upstream TLPs to the CPU.

In this diploma work, the PCIe Endpoint was designed. This Endpoint generates or responds to Memory Write/Read transactions. Since the used PCIe core supports up to six 32-bit Base Address Registers (BARs) used to route the TLP [XUG167], the behavior of this Endpoint can be easily extended by reconfiguring this core to have memory and IO address spaces.

When the Endpoint acts as a receiver, the CPU issues a store register command to a memory mapped location in the Endpoint. This is done by having the Root Complex generate a Memory Write TLP with the required memory mapped address in the Endpoint, the payload size (a Doubleword in this design), byte enables and other Header contents. These will be discussed later in the device core section of this Endpoint.

This TLP moves downstream through the PCIe fabric to the Endpoint. Routing of the TLP in this case is based on the address within its Header. A termination of the transaction takes place when the Endpoint receives the TLP and writes the data to the targeted local register.

To read this data back, the CPU issues a load register command from the same memory mapped location in the Endpoint. This is done by having the Root Complex generate a Memory Read TLP with the same memory mapped address and other Header contents. This TLP moves downstream through the PCIe fabric to the Endpoint. Again, routing here is based on the same address within the Header.

Once the Endpoint receives this Memory Read TLP, it generates a Completion with Data TLP (CPLD). The Header of this CPLD TLP includes the ID number of the Root Complex, which is used to route this TLP upstream through the fabric to the Root Complex, which in-turn update the targeted CPU register and terminates the transaction.

The other way around, is to have the Endpoint act as a bus master and initiate a Memory Write TLP to write 1 DW to a location within the system memory. This TLP is routed upstream toward the Root Complex which in turn writes the data to the targeted location in the system memory.

If the Endpoint wants to read the data it has written, it generates a Memory Read TLP with the same address. The TLP is steered to the Root Complex, which in-turn accesses the system memory, gets the required data and generates a Completion with this data. This CPLD TLP is routed downstream to the Endpoint through the PCIe fabric. The Endpoint receives this TLP, updates its local register and terminates the transaction.

As mentioned in chapter 2, the PCIe core can be integrated in different devices composing the PCIe fabric. For instance, the core can be implemented in the Root Complex, in the PCIe switch, and in the PCIe Endpoint. For the purpose of this diploma work, the focus will be on designing a PCIe Endpoint.

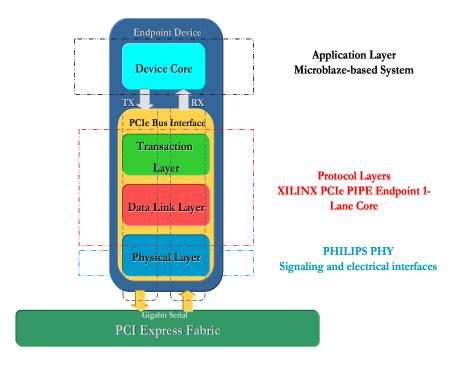

When designing a PCIe Endpoint, several issues have to be considered. Figure 3.2 shows the layered structure of a PCIe Endpoint device. In the figure, the way this Endpoint was designed is depicted.

The physical layer provides the electrical transceivers, which drive and receive the dual-simplex low voltage differential signals at the 2.5 Gbps data rate. There are two different solutions for the physical layer. In the first solution, this layer can be integrated with the other layers in the same chip. Doing so increases the complexity of this chip and provides a higher integration level. This integrated solution has one key advantage when designing using an FPGA. It uses less number of IO pins, which enables easier timing closure.

Figure 3.2 - Endpoint Design

An example of this integrated solution is offered by Xilinx in their newly introduced Xilinx Virtex-5 PCIe Endpoint block shown in figure 3.3.

Figure 3.3 - Xilinx Virtex-5 LXT PCI Express endpoint block [UG197]

Unlike the first solution mentioned above which is quite expensive, the second solution offers a low cost way of implementing the PCIe Endpoint. In this solution, the physical layer exists in one chip, and the other layers are designed in another chip.

In this two-chip solution, a smaller FPGA with external PHY can be used. Within this diploma work, the discrete PHY, PX1011A from Philips was used.

This PHY supports x1 PCIe designs. Having the practical bandwidth provided by x1 PCIe is 2.0 Gbps requires an internal interface of 8 bits runs at 250 MHz or an interface of 16 bits runs at 125 MHz. This solution has the disadvantage of higher number of IO pins.

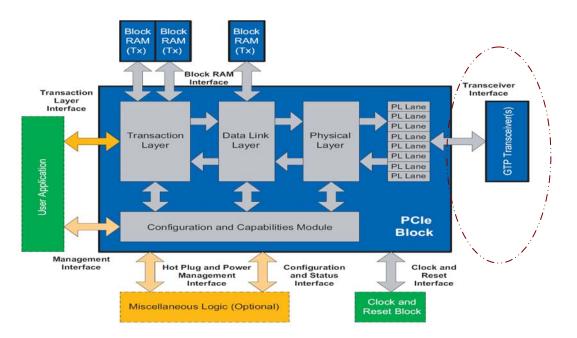

The protocol layers containing the logical sub-layer of the physical layer, the data link layer and the transaction layer are implemented using the Xilinx PCIe core.

A Microblaze based embedded system was built up to implement the Application layer of the designed PCIe Endpoint. In this Microblaze processor embedded system, the PCIe core is attached as a slave to the processor, which in-turn tries to access the configuration space of this core, reading from and writing to this space.

In the application layer, the Microblaze is responsible for sending the required Header and data payload to the transaction layer of the PCIe core, which generates a TLP and forwards it to the data link layer. The Data link layer appends a 12-bit sequence number and a 32-bit LCRC, to ensure a reliable data transport. The TLP is then forwarded to the physical layer to be transmitted across the PCIe link.

When a TLP is received by the PCIe Endpoint, the Header and the payload, if exists, will be forwarded to the Microblaze for further processing. The Microblaze also controls the transmitting and receiving of TLPs.

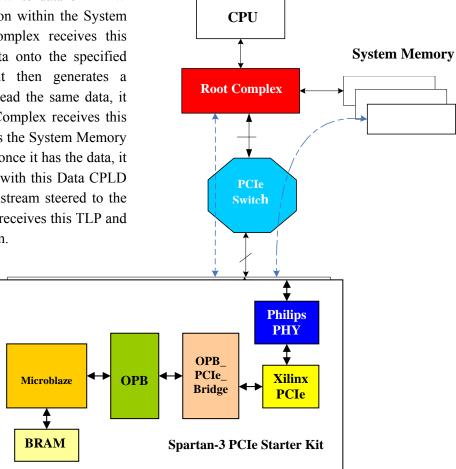

The protocol layers and the application layer are to be implemented on a Xilinx® Spartan-™3/E FPGA, as depicted in figure 3.4, which shows a Spartan-3 PCI Express Starter Kit from Xilinx.

Figure 3.4 - Spartan-3 PCI Express Starter Kit [Xilinx]

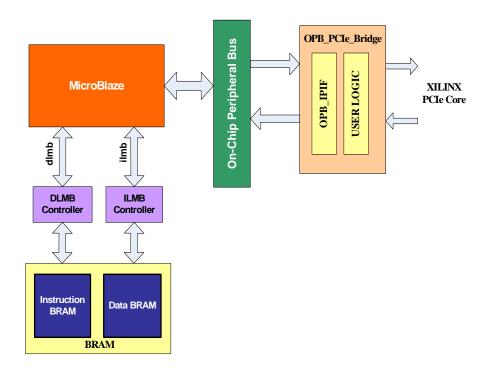

Figure 3.5 shows the complete designed PCIe Endpoint. This system embeds the Xilinx Microblaze, which implements a 32-bit Reduced Instruction Set Computer (RISC) and operates at a frequency of 50MHz. Having the Microblaze as a soft core processor enables the design of a unique and customized PCIe peripheral device to be connected as a slave to it.

Figure 3.5 - Complete PCIe Endpoint device

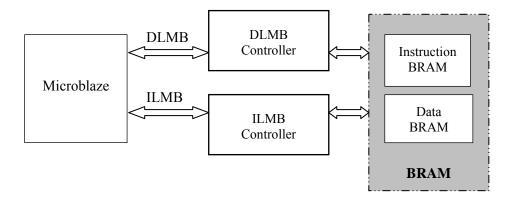

The Microblaze has different bus interfaces, connecting it with different peripherals. For example, the Local Memory Bus (LMB) allows the communication between the processor and the Block Random Access Memory (BRAM), which is initialized with the application program to be executed by the Microblaze.

The Microblaze has a Harvard structure, in which the BRAM consists of two sections, data and instructions. These sections are accessed by the processor through memory controllers over the local memory bus.

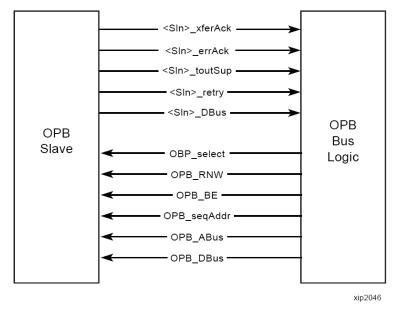

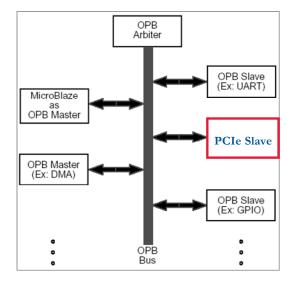

Xilinx On-Chip Peripheral Bus (OPB), which implements the IBM CoreConnect On-Chip Peripheral Bus, has two 32-bit separate paths for data and address. This bus is used to connect peripherals to the Microblaze, which masters the bus. Several peripherals can be attached to the Microblaze as slaves.

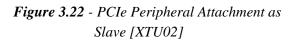

The PCIe core can not be directly connected to the OPB as a slave, because of the incompatibility of its interfaces with the OPB protocol. To fulfill this compatibility issue, a bridge was developed to bridge the OPB and the PCIe core.

This bridge interfaces the OPB with its standard protocol through the OPB Intellectual Property Interface (OPB IPIF) from one side, and the PCIe core through the USER LOGIC model from the other side. This USER LOGIC model implements the logic needed to transmit/receive TLPs across the PCIe link and to access the configuration space of the PCIe core. The PCIe core transaction interfaces are synchronized with a clock of 62.5 MHz generated from the core as indicated in the figure.

The PCIe core interfaces with the Philips PHY using the Philips PHY Specification Physical Interface for PCI Express (PXPIPE), defined by Philips Semiconductors, which implements an extended version of the Physical Interface for PCI Express (PIPE), defined by Intel. PXPIPE is a 250 MHz source synchronous interface, which provides two clocks, one for transmission, and the other for reception.

Depicted in the figure are the interfaces of Philips PHY to the PCIe link, which are the low voltage differential signals (LVDS) driven at a high data rate of 2.5 Gbps.

In the following sections of this chapter, the components building up the PCIe Endpoint device are discussed in details<sup>1</sup>.

# 3.2 Philips PX1011A PHY

Philips PHY is a standalone transceiver, which is optimized for usage with digital Application Specific Integrated Circuits (ASICs) and low cost FPGAs. This device implements a x1 PCIe physical layer. It provides a receiving bit error rate of less than  $10^{-12}$  and comes in a small package used for chip to chip communication [KPE06].

# 3.2.1 Block Diagram

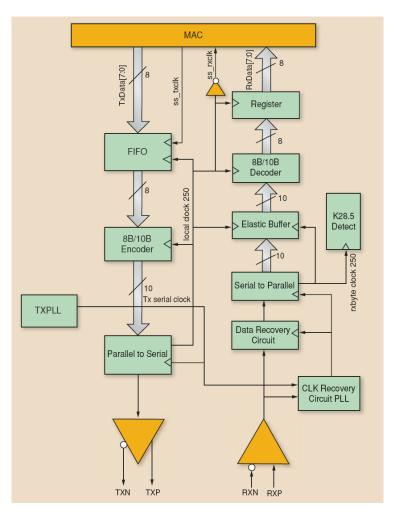

Figure 3.6 illustrates the block diagram of the PX1011A. It interfaces the Media Access Controller (MAC) of the physical layer of the protocol layers from the upper side, as well as the PCIe fabric from the other side.

# **3.2.2 Operation Principle**

For the transmission of TLPs, the PX1011A receives words of 8 bits from the MAC, accompanied by a control bit that indicates whether the 8-bit word is data or a control character. The data is clocked in at a rate of one word per cycle of a 250 MHz clock. A First in First Out (FIFO) is used to compensate the phase difference between the interfacing clock and the internal 250 MHz transmitting clock generated by the Phase Locked Loop of the transmitter (TXPLL).

The data is first buffered in a FIFO. For the purpose of a high transmission rate, the transmission clock of 2.5 GHz is embedded by decoding the data using an 8b/10b encoder. The resulting symbols of 10 bits are then serialized and differentially transmitted across the transmission line.

<sup>&</sup>lt;sup>1</sup> Excluding the PX1011A and the USER LOGIC, all the components are *IPs* provided by Xilinx

When the PX1011A receives the serial differential data from the transmission line, it recovers a clock from the incoming signal. This clock is used to sample the serial data. The sampled data is then forwarded to a serial to parallel converter, which converts the serial data into 10-bit symbols.

Once the 10-bit symbols are available, the symbol boundaries must be recognized. This is done by detecting a special 10-bit character called the "comma" character, which is used for symbol synchronization.

After the symbol synchronization, the synchronized 10-bit characters are passed through an elastic buffer that compensates the frequency difference between the recovered clock and the locally generated transmission clock. 8-bit data words are obtained by decoding the 10-bit symbols using an 8b/10 decoder. The resulting data is then stored in a register before being outputted to the protocol layers.

Figure 3.6 - Block diagram of PX1011A [GL05]

### 3.2.3 Interfaces

#### **Interfaces to PCIe Link**

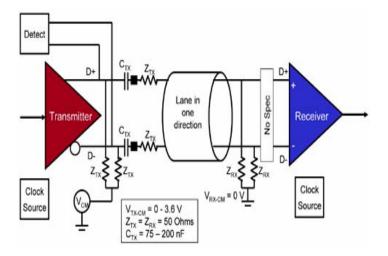

The electrical part of the PX1011A physical layer interfaces the PCIe fabric with two Low Voltage Differential Signals (LVDS) to drive and receive the high data rate data of 2.5 Gbps. Figure 3.7 shows the electrical characteristics of a PCIe signal. A positive difference between the D+ and D- lines indicates the transmission of logic "1", while a negative difference implies a logic "0" on the link. Having a voltage difference of zero leads to a high impedance "tri-state" link, and forces the link to stay in the electrical idle state [ABS04].

Table 3.1 summarizes the interfaces of this layer to the PCIe link.

Figure 3.7 - PCIe Differential Transmitter/Receiver [ABS04]

| Signal   | I/O | Description                      |

|----------|-----|----------------------------------|

| TX_P     | 0   | Positive transmission signal     |

| TX_N     | 0   | Negative transmission signal     |

| RX_P     | Ι   | Positive receiving signal        |

| RX_N     | Ι   | Negative receiving signal        |

| REFCLK_P | Ι   | Reference clock of 100 MHz       |

| REFCLK_N | Ι   | out of phase version of REFCLK_P |

| <b>Table 3.1</b> - PHY | Interfaces to | o the | PCIe Link |

|------------------------|---------------|-------|-----------|

|------------------------|---------------|-------|-----------|

### **Interfaces to PCIe core**

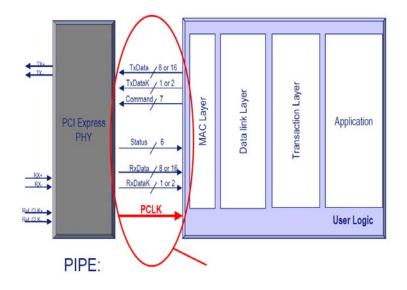

Figure 3.8 illustrates the PHY Interface for the PCI Express Architecture (*PIPE*), defined by Intel. This kind of interface assigns a single 250 MHz clock, referred to as PCLK in the figure. This clock synchronizes both the transmitting and receiving of data. This clock is outputted from the PHY as shown in the figure. Intel first introduced an 8-bit data interface.

Due to a timing budget problem, this interface was further improved to a 16-bit data interface. The newly introduced interface has the disadvantage of requiring more pins than the previous one and imposes an extra latency in converting from 16 to 8 bits.

Figure 3.8 - PIPE Interface [PPHY]

Philips Semiconductors provided a version of the PIPE interface named *PXPIPE*. This interface employs the source synchronous clocking. Instead of having one clock for both directions, it provides two clocks: one for transmitting and another for receiving, as shown in figure 3.9.

Figure 3.9 - PXPIPE Interface [PPHY]

The interface signals with the Xilinx PCIe core are summarized in table 3.2.

| Signal                                | I/O | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDATA[7:0]                           | Ι   | 8-bit transmit data from the FPGA to the PHY.                                                                                                                                                                                                                                                                                                    |

| TXDATAK                               | Ι   | Data or control for the symbols of transmit data. A value of "0" indicates a data byte; a value of "1" indicates a control byte.                                                                                                                                                                                                                 |

| RXDATA[7:0]                           | 0   | 8-bit receive data from the PHY to the FPGA.                                                                                                                                                                                                                                                                                                     |

| RXDATAK                               | 0   | Data or control for the symbols of receive data. A value of "0" indicates a data byte; a value of "1" indicates a control byte.                                                                                                                                                                                                                  |

| TXCLK                                 | Ι   | Source synchronous 250 MHz clock for transmit from the FPGA.<br>All the data and input signals to the PHY are synchronized to this clock                                                                                                                                                                                                         |

| RXCLK                                 | 0   | Source synchronous 250 MHz clock for received data bound for the FPGA.                                                                                                                                                                                                                                                                           |

| RXDET_LOOPB                           | Ι   | Enables the Philips PHY to begin a receiver detection operation or to begin loopback.                                                                                                                                                                                                                                                            |

| TXIDLE                                | Ι   | Forces Philips PHY TX output to electrical idle when asserted in all power states.                                                                                                                                                                                                                                                               |

| ТХСОМ                                 | Ι   | When high, sets the running disparity to negative. Used when transmitting the compliance pattern.                                                                                                                                                                                                                                                |

| RXPOL                                 | Ι   | Active high, signals the PHY to perform a polarity inversion on the receive data.                                                                                                                                                                                                                                                                |

| RESET_N                               | Ι   | Output Active low PHY reset from FPGA.                                                                                                                                                                                                                                                                                                           |

| PWRDWN1,<br>PWRDWN0                   | Ι   | <ul> <li>Power up or down the transceiver. Power states [1:0]:</li> <li>00 - P0, normal operation</li> <li>01 - P0s, low recovery time (2.5 μs), power saving state</li> <li>10 - P1, longer recovery time (64us max), lower power state</li> <li>11 - P2, lowest power state.</li> </ul>                                                        |

| RXVALID                               | 0   | Indicates symbol lock and valid data on RXDATA and RXDATAK                                                                                                                                                                                                                                                                                       |

| PHYSTATUS                             | 0   | Communicates completion of several Philips PHY functions,<br>including power management state transitions, and receiver<br>detection.                                                                                                                                                                                                            |

| RXIDLE                                | 0   | Indicates receiver detection of an electrical idle. This is an asynchronous signal.                                                                                                                                                                                                                                                              |

| RXSTATUS2,<br>RXSTATUS1,<br>RXSTATUS0 | 0   | Encodes receiver status and error codes for the received data stream<br>and receiver detection. Encoding [2:1]<br>000 - Received data OK<br>001 - 1 SKP added<br>010 - 1 SKP removed<br>011 - Receiver detected<br>100 - 8B/10B decode error<br>101 - Elastic Buffer overflow<br>110 - Elastic Buffer underflow<br>111 - Receive disparity error |

Table 3.2 - Philips PHY Interfaces to the Xilinx PCIe Core [KPE05]\*

\* The direction is defined from the perspective of the PHY.

## 3.3 Xilinx PCIe Core

The product name of this core is Xilinx PCIe Physical Interface for PCI Express (PIPE) Endpoint 1-Lane core.

This core implements a high performance serial Interconnect intellectual property, which is optimized for the use with the Spartan-3/3E device families of Xilinx, as indicated in table 3.3.

The table also shows some of the core's specifications, such as the complexity when targets the XC3S1000-4 device of the Xilinx Spartan-3 family.