Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# Diplomarbeit

#### Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

Ausgeführt zum Zwecke der Erlangung eines akademischen Grades eines Diplom-Ingenieurs Unter der Leitung von

Univ.Doz.Dipl.-Ing Dr.techn Alfred Pohl

Institut für Sensor und Aktuatorsysteme

Eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Christian Ernst 8926331 Petraschgasse 3/8 A-1020 Wien

# 1 Inhaltsverzeichnis

| 1 | Inha | altsverzeichnis                         | 2 |

|---|------|-----------------------------------------|---|

| 2 | Abs  | tract                                   | 6 |

| 3 | Beg  | riffe                                   | 7 |

|   | 3.1  | Analoge CCTV Kamera                     | 7 |

|   | 3.2  | Farbfernsehstandards                    | 7 |

|   | 3.2. | 1 PAL                                   | 7 |

|   | 3.2. | 2 NTSC                                  | 8 |

|   | 3.2. | 3 SECAM                                 | 8 |

|   | 3.3  | Y/C-Signal                              | 8 |

|   | 3.4  | FBAS                                    | 8 |

|   | 3.5  | Farbraum                                | 8 |

|   | 3.6  | Frame grabber / Video Capture Karte     | 9 |

|   | 3.7  | CCTV                                    | 9 |

|   | 3.8  | Äquidistanz von Videostreams            | 9 |

|   | 3.9  | Interlace Effekte                       | 9 |

|   | 3.10 | Deinterlacing 1                         | 0 |

|   | 3.11 | Weißabgleich 1                          | 0 |

|   | 3.12 | Event / Frame Puffer1                   | 0 |

|   | 3.13 | Bildspeicher 1                          | 0 |

|   | 3.14 | Digitale Auflösungen                    | 1 |

| 4 | Auf  | gabenstellung1                          | 2 |

|   | 4.1  | Aufbau – BSB – Schnittstellen           | 3 |

|   | 4.2  | Detailierte Aufgabenstellung            | 4 |

|   | 4.3  | Konstruktive Anforderung an den V-MUX 1 | 5 |

|   | 4.4  | Erweiterte Anforderungen                | 7 |

|   | 4.5  | Entwicklungsziel1                       | 8 |

| 5 | Bek  | annte Lösungen1                         | 8 |

|   | 5.1  | Marktanalyse1                           | 9 |

|   | 5.2  | Methoden                                | 9 |

|   | 5.2. | 1 Variante 1 2                          | 0 |

|   |      |                                         |   |

# DIPLOMARBEIT Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

|   | 5.2. | 2      | Variante 2                                         | . 21 |

|---|------|--------|----------------------------------------------------|------|

|   | 5.2. | 3      | Variante 3                                         | . 22 |

|   | 5.3  | Ana    | lyse                                               | . 23 |

|   | 5.4  | Ben    | nerkungen                                          | . 24 |

|   | 5.5  | Sch    | lussfolgerung                                      | . 25 |

| 6 | Arcl | hitekt | turüberlegungen                                    | . 26 |

|   | 6.1  | Ana    | loger Eingangsschalter                             | . 27 |

|   | 6.2  | Ana    | loges Videosignal                                  | . 28 |

|   | 6.2. | 1      | Synchrosignal                                      | . 28 |

|   | 6.2. | 2      | Bildsignal                                         | . 29 |

|   | 6.2. | 3      | Austastlücken                                      | . 29 |

|   | 6.2. | 4      | BAS                                                | . 29 |

|   | 6.2. | 5      | Auflösung                                          | . 29 |

|   | 6.2. | 6      | Abtastkennwerte für PAL VIDEO[1]                   | . 30 |

|   | 6.2. | 7      | Frequenzkennwerte PAL VIDEO[1]                     | . 30 |

|   | 6.2. | 8      | Elektrische Kennwerte PAL VIDEO[1]                 | . 30 |

|   | 6.2. | 9      | Signalform FBAS                                    | . 31 |

|   | 6.3  | Digi   | tales Videosignal                                  | . 31 |

|   | 6.3. | 1      | Digitalisieren nach CCIR 601                       | . 31 |

|   | 6.3. | 2      | Kennwerte Digitaler Videosignale nach CCIR 601 [1] | . 32 |

|   | 6.4  | Digi   | taler V- RAM Schalter                              | . 32 |

|   | 6.4. | 1      | Globales V-RAM                                     | . 32 |

|   | 6.4. | 2      | Diskretes V-RAM pro Kanal                          | . 33 |

| 7 | Arcl | hitekt | turauswahl                                         | . 34 |

|   | 7.1  | Bau    | teilermittlung                                     | . 35 |

|   | 7.2  | War    | ndlerbauteile                                      | . 35 |

|   | 7.2. | 1      | A/D-Wandler SAA7110 A                              | . 35 |

|   | 7.2. | 2      | D/A-Wandler SAA7185 B                              | . 36 |

|   | 7.3  | Spe    | icher                                              | . 36 |

|   | 7.3. | 1      | V-RAM HM530281W                                    | . 36 |

|   | 7.4  | Ste    | uerung                                             | . 37 |

|   | 7.4. | 1      | Steuereinheit MC68LC302PU16B                       | . 37 |

|    | 7.4. | .2 I <sup>2</sup> C BUS Controller PCF 8584 | . 37 |

|----|------|---------------------------------------------|------|

|    | 7.5  | Systemaufbau                                | . 38 |

| 8  | Sys  | stementwurf                                 | . 38 |

|    | 8.1  | Eingangsmodul                               | . 39 |

|    | 8.2  | Basismodul                                  | . 40 |

|    | 8.3  | Betriebsarten des Multiplexers              | . 41 |

|    | 8.3. | .1 Normaler Multiplexbetrieb                | . 41 |

|    | 8.3. | .2 Alarmaufschaltung                        | . 42 |

|    | 8.4  | Steuerung und Programmierung                | . 42 |

| 9  | Rea  | alisierung                                  | . 42 |

|    | 9.1  | Video-Out / Controller - Basisplatine       | . 43 |

|    | 9.2  | Video-Input - SIM-Modul                     | . 44 |

|    | 9.3  | Synchronisierung des Videosignals           | . 45 |

|    | 9.4  | I <sup>2</sup> C-Bus Schnittstelle          | . 45 |

|    | 9.5  | Mechanischer Aufbau                         | . 45 |

|    | 9.6  | Technische Daten                            | . 47 |

|    | 9.7  | Schnittstellen                              | . 48 |

|    | 9.7. | .1 Parametrierung                           | . 48 |

|    | 9.7. | .2 Alarmeingänge                            | . 49 |

|    | 9.7. | .3 Alarmausgang                             | . 49 |

|    | 9.7. | .4 Interne YUV-Schnittstelle                | . 49 |

| 10 | ) P  | Performance Analysen                        | . 50 |

|    | 10.1 | Erwartungen                                 | . 50 |

|    | 10.2 | Stakeholder des Tests                       | . 51 |

|    | 10.2 | 2.1 Support                                 | . 51 |

|    | 10.2 | 2.2 Außendiensttechniker                    | . 51 |

|    | 10.2 | 2.3 Projektingenieure                       | . 51 |

|    | 10.2 | 2.4 Vertriebspersonen                       | . 51 |

|    | 10.2 | 2.5 Benutzer                                | . 51 |

|    | 10.3 | Finden von Testmethoden                     | . 52 |

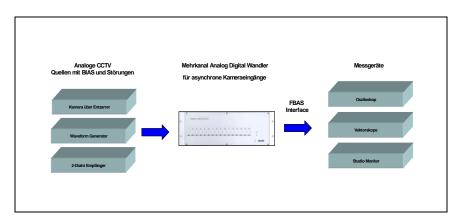

|    | 10.4 | Messplatzausstattung                        | . 53 |

|    | 10.5 | Testpunkte Methoden und Ergebnisse          | . 54 |

# DIPLOMARBEIT Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

| ۱r | ۱h | a | Itو۱ | 10 | r70 | 10 | h | nis |

|----|----|---|------|----|-----|----|---|-----|

|    |    |   |      |    |     |    |   |     |

| 10.  | 5 1    | FBAS Videosignal am Ausgang          | 54   |

|------|--------|--------------------------------------|------|

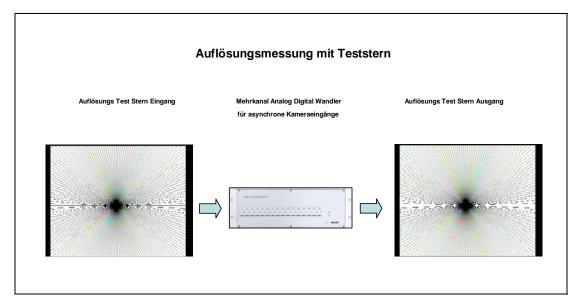

| 10.  | _      | Auflösung des Ausgangssignals        |      |

| 10.  |        | Eingangskanalverhalten               |      |

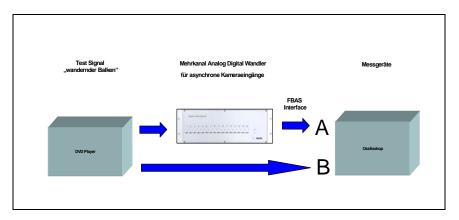

| 10.  |        | Eingangssignalverzögerung            |      |

|      |        |                                      |      |

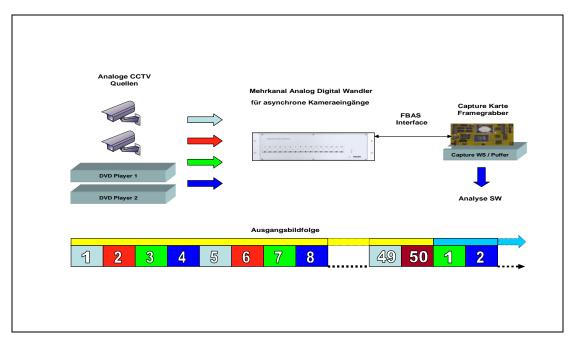

| 10.  |        | Äquidistanz der Bildfolge            |      |

| 10.  |        | Kontrolle der Bildfolge und Bildrate |      |

| 10.  |        | Alarmverhalten                       |      |

| 10.  |        | Störmeldungserkennung – Ausgabe      |      |

| 10.6 | Erke   | enntnisse                            | . 67 |

| 11 Z | usan   | nmenfassung                          | . 67 |

| 12 L | iterat | urverzeichnis                        | . 69 |

| 13 A | bbild  | lungsverzeichnis                     | . 70 |

| 14 T | abell  | enverzeichnis                        | . 71 |

| 15 A | nhar   | ng                                   | . 72 |

| 15.1 | Tes    | t cases versus Use Cases             | . 72 |

| 15.2 | Kon    | struktive Anforderungen              | . 74 |

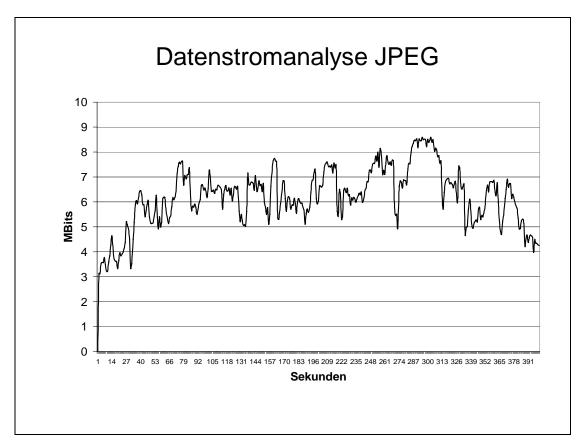

| 15.3 | Date   | enstromanalyse JPEG Bildgröße        | . 75 |

| 15.4 | Eva    | luierungsboard DPC7146 V2.3          | . 76 |

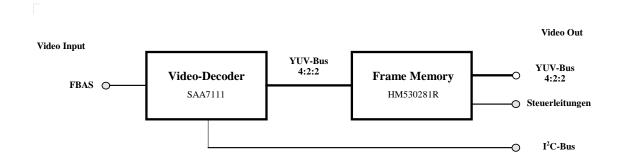

| 15.  | 4.1    | Blockschaltbild SIM-Modul            | . 76 |

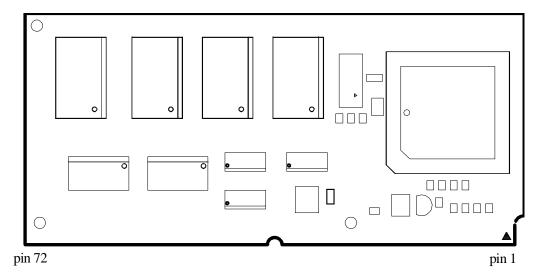

| 15.5 | SIM    | -Steckerbelegung (72 polig)          | . 77 |

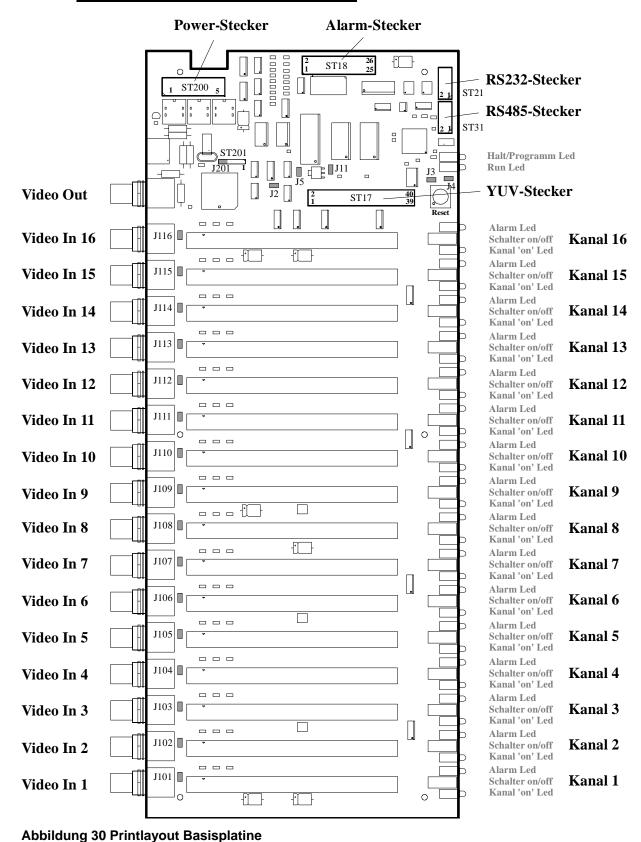

| 15.  | 5.1    | Printlayout                          | . 78 |

| 15.6 | Prin   | tlayout - Basisplatine               | . 79 |

| 15.7 | Ste    | ckerbelegungen                       | . 80 |

| 15.  | 7.1    | Alarm-Schnittstelle                  | . 80 |

| 15.  | 7.2    | RS232 Schnittstelle                  | . 80 |

| 15.  | 7.3    | YUV-Bus Stecker                      | . 81 |

# 2 Abstract

# Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge (V-MUX)

Diese Diplomarbeit beschreibt die Entstehung einer der Hauptkomponenten eines digitalen CCTV System von der Entwicklung bis zur Einführung in den Markt. In dieser Arbeit wird im speziellen auf die Eingangskomponente, der Digitalisierung und der Synchronisation von analogen Videosignalen eingegangen. Die Ausgangssignale werden dann ereignisbezogen mit entsprechender Bildrate an das digitale Speichersystem weitergegeben. Als erster Schritt steht die Marktanalyse, dann eine Machbarkeitsstudie, die Definition der Minimalanforderungen sowie die möglichen USP's einer Neuentwicklung. Die definierten Ziele werden dann anhand eines Prototyps verifiziert, um vor der Serienproduktion über ein Redesign entscheiden zu können.

# 3 Begriffe

Zum besseren Verständnis sollen wichtige Begriffe dieser Arbeit skizziert und erklärt werden.

## 3.1 Analoge CCTV Kamera

Von einer analogen CCTV [1] Kamera spricht man, wenn das Ausgangssignal der Kamera ein stufenloses nicht quantisiertes Signal liefert. Heute verwenden alle modernen analogen Kameras digitale Signalaufbereitungseinrichtungen innerhalb der Kamera, was bei einer nochmaligen Digitalisierung zu Artefakten durch starke Kontrastanhebung führen kann.

## 3.2 Farbfernsehstandards

Durch die unterschiedlichen regionalen Video Standards kommt es oft zu Problemen bei gemischtem Einsatz von analogen Kamerastandards in der Videoüberwachung. Im CCTV Bereich wo vorwiegend nicht modulierte Signale verwendet werden, kommen meist PAL und NTSC basierende Kameras zum Einsatz. Beide Systeme können nicht ohne weiteres gemischt betrieben werden.

#### 3.2.1 PAL

Mit PAL [2] (**P**hase **A**lternation **L**ine) werden jene Farbfernsehsignale bezeichnet, die in Europa, Afrika, Australien und teilweise in Asien und Südamerika verwendet werden. Die verbesserten Eigenschaften des PAL Signals gegenüber NTSC in der Farbstabilität kommen erst bei Übertragung und daher nur eingeschränkt im CCTV zur Geltung.

#### 3.2.2 NTSC

Mit NTSC [2] ( (National Television System Comitee) werden jene Farbfernsehsignale bezeichnet, die in Nord, Zentralamerika, teilweise in Südamerika, Japan und auf den Philippinen verwendet werden.

#### 3.2.3 SECAM

Mit SECAM [2]( (sequentiel à mémoire) werden jene Farbfernsehsignale bezeichnet, die in Frankreich und im ehemaligen Ostblock verwendet werden. Diese Form der Videoübertragung hat sich in der CCTV Überwachungstechnik nie durchgesetzt. Wesentlicher Unterschied zu PAL und NTSC ist die sequentielle Übertragung der monochrom- und Farbinformation.

# 3.3 Y/C-Signal

Wird das Farbsignal und das monochrome Videosignal getrennt verarbeitet spricht man von Y/C [2] oder S-Video. Die bessere Videoqualität konnte sich in der CCTV Technik nicht gegen den erhöhten Hardware Aufwand durchsetzen.

# 3.4 **FBAS**

Mit FBAS [2] wird das Farbfernsehsignal bezeichnet dass zum monochromen BAS (**B**ild- **A**ustast- und **S**ynchrosignal) noch die Farbinformation beinhaltet. Diese Signalform bildet in der CCTV Technik die Basis der analogen Videosignale.

# 3.5 Farbraum

Zur Charakterisierung von Farben in einem Koordinatensystem wird ein spezieller Raum definiert. Wird von einem menschlichem Betrachter ausgegangen, so werden meist drei Koordinatenachsen verwendet. Es sind etwa 30-40 Farbraumsysteme in Gebrauch. Um sich einen genauen Überblick der Farbräume schaffen zu können verweise ich auf im Verzeichnis angeführte Literatur zu diesem Thema.[1]

## 3.6 Frame grabber / Video Capture Karte

Als Frame grabber bezeichnet werden meist im PC eingesetzte analog zu digital Wandler Karten im Video Bereich. Diese Karten können FBAS Signale in digitale Videosignale zur PC basierenden Weiterverarbeitung umwandeln. Die in dieser Arbeit verwendeten Karten sind auf PAL Systeme optimiert.

#### **3.7 CCTV**

CCTV [2] (**C**losed **C**ircuit **T**ele**V**ision) ist die englische Bezeichnung für ortsgebundene Videoüberwachungsanlagen.

# 3.8 Äquidistanz von Videostreams

Findet in einem digitalisierten Videosignal die Bildfolge der Einzelbilder immer im gleichen zeitlichen Abstand statt, spricht man von Äquidistanz. Diese trivial erscheinende Forderung, wie sie im analogen Signal bindend ist, kann in der Digitaltechnik zu gunsten einfacherer Technik nicht eingehalten werden, ansonst wäre ruckeln bei der Anzeige die Folge.

# 3.9 Interlace Effekte

Ein analoges Videosignal besteht aus 50 Halbbildern, die innerhalb einer Sekunde ineinander verzahnt dargestellt werden. Diese Methode ist optimiert für die Darstellung der Videos auf analogen Röhrenmonitoren. Bei der Digitalisierung einzelner Halbbilder und nachfolgender Zusammensetzung kommt es zu Interlace- Effekten [1], die bei der Darstellung von Vollbildinformation aufwendig durch Interpolation eliminiert werden müssen.

# 3.10 **Deinterlacing**

Methode zur Eliminierung von Interlace- Effekten in der Videotechnik. Abhängig von den Einsatzbereichen gibt es verschiedene Möglichkeiten störende Interlace- Effekte aus einem Vollbild herauszurechnen.

## 3.11 Weißabgleich

Weißabgleich [2] wird ein Vorgang genannt, wo der CCD [2] Chip einer Farbvideokamera an die Beleuchtung der Umgebung angepasst wird. Dieser Vorgang ist meist eine automatische Prozedur der Kameraelektronik.

#### 3.12 Event / Frame Puffer

Bei Anwendungen von CCTV im Sicherheitsbereich ist es bei der Aufzeichnung von Videoinformationen oft wichtig Bilder vor dem Eintreffen eines Ereignissen aufgezeichnet zu haben, um einen Tatvorgang rekonstruieren zu können. Die Pufferung der Videos erfolgt meist im RAM der Capture Einheit

# 3.13 Bildspeicher

In der CCTV Überwachungstechnik werden oft sehr große, nicht flüchtige Speicher zur Aufnahme der Videoinformation verwendet. Bildspeicher werden in der Regel durch RAID [1] basierender Festplattenspeicher aufgebaut. Zur Aufnahme sehr großer Datenmengen, die meist bei Langzeitspeichern gebraucht werden, sind oft Bandsysteme eingesetzt.

# 3.14 <u>Digitale Auflösungen</u>

Beim Abtasten eines analogen Videosignals im PAL Format von maximal 625 Zeilen und einem sichtbaren Bereich von 575 Zeilen bedingt durch Zeilenrücklauf und Bildrücklauf ergibt sich eine maximale vertikale Auflösung von 575 für das Vollbild. Daraus resultieren folgende Formate für das Digitale Bild im 4:3 Format [1].

| Q CIF   | 176 x 144 |

|---------|-----------|

| CIF     | 384 x 288 |

| 2 CIF   | 704 x 288 |

| 4 CIF   | 704 x 576 |

| FULL D1 | 720 x 576 |

Tabelle 1 Auflösung digitaler Videobilder

# 4 Aufgabenstellung

Ziel dieser DA war die Realisierung eines **Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge** und die messtechnische Verifikation.

Ein digitales Videosystem bestehend aus Software und Hardwarekomponenten soll in all seinen Komponenten entwickelt werden. Die Anforderung an das Überwachungssystem soll für mindestens 5 – 10 Jahre Betriebszeit erfüllt bleiben. Das Gesamtsystem soll durch das Design in mehrere Teilbereiche und Projekte gegliedert werden können, damit ein mögliches Redesign nur Teilbereiche betrifft. Es ist besonderes Augenmerk auf die Definition der Schnittstellen zu den einzelnen Teilbereichen zu legen. Um Zeit zu sparen soll die Entwicklung nach Möglichkeit auch in einem Stufenprogramm realisiert werden können.

Das Gesamtkonzept des Digitalen Videosystems besteht aus

- Mehrkanal Wandlereinheiten (V-MUX)

- Capture-Einheiten,

- Übertragungseinheiten,

- Livebetrachtungseinheiten,

- Archivierungseinheiten und

- Rechercheeinheiten sowie

- Analogwiedergabeeinheiten

Das Videosystem soll kompatibel zu analogen Überwachungssystemen sein, um auch hybride Anlagen aufbauen zu können. Es soll möglich sein, das digitale Videosystem kombiniert mit analogen Systemen einzusetzen und parallel zu bedienen. Für den Bediener sollen sich keine wesentlichen Unterschiede bei der Bedienung von Analogen oder Digitalen Komponenten ergeben.

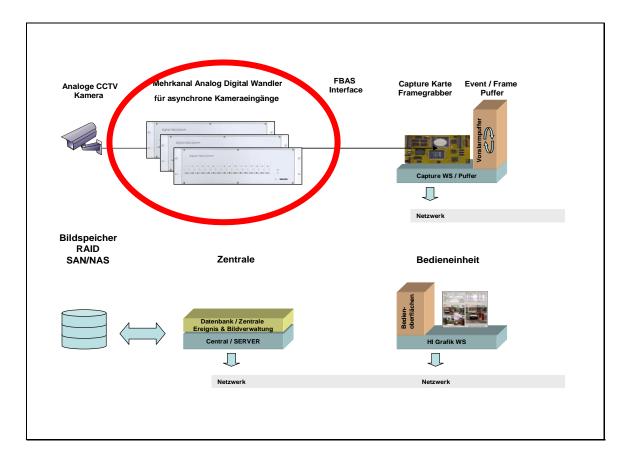

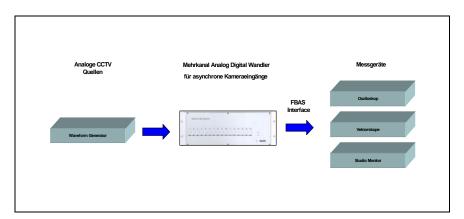

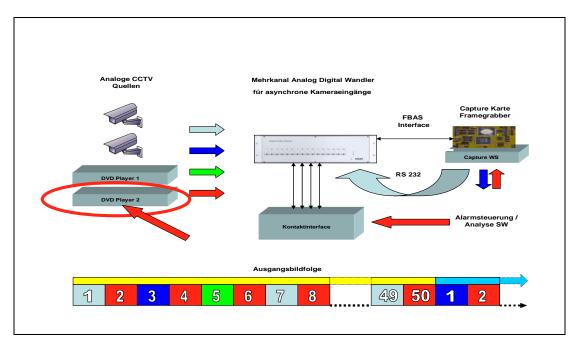

Eine der Basiskomponenten des gesamten Digitalen Videospeichersystems der Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge (im Kontext kurz als V-MUX bezeichnet) soll neu entwickelt und gebaut werden. Das nun folgende Blockschaltbild skizziert alle Komponenten des CCTV Systems und zeigt die Rolle und Position des V-MUX.

# 4.1 Aufbau – BSB – Schnittstellen

#### Abbildung 1 Hauptkomponenten eines CCTV Systems

# Hauptkomponenten einer CCTV Überwachungsanlage

- Analoge CCTV Kamera

- Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

- FBAS Interface

- Capture Karte Framegrabber

- Event / Frame Puffer

- Bedieneinheit

- Zentrale

- Bildspeicher

# 4.2 <u>Detailierte Aufgabenstellung</u>

Der Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge, im folgenden V-MUX genannt, soll in der Grundausführung 16 Videosignale nicht synchroner Eingänge (Videokameras) zyklisch oder nach Anforderung auf einen Videoausgang durchschalten. Die nun folgenden Anforderungen (ANF-\_) werden im Kapitel 10 Performance Analysen soweit möglich einzeln geprüft und getestet. Alle Anforderungen werden fortlaufend nummeriert aufgeführt um im Kontext leicht referenziert werden zu können. Der folgende Katalog ist aus Standardanforderungen eines digitalen Videosystems und speziellen projektbezogenen Anforderungen entstanden.

## **Anforderungskatalog V-MUX:**

| Die Grundausführung des V-MUX soll aus 16 Videoeingangskanälen bestehen.                                                                                                | ANF-1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Das Anschließen und die <b>zyklische</b> Durchschaltung von nichtsynchronen Kameras muss möglich sein.                                                                  | ANF-2  |

| Der V-MUX soll am Eingang Standard FBAS Signale verarbeiten können.                                                                                                     | ANF-3  |

| An den Video Eingängen des V-MUX sollen Standard <b>Farb- und auch Schwarzweiß</b> Kameras gleichzeitig und auch gemischt betrieben werden können.                      | ANF-4  |

| Das Design soll die Erweiterung auf den Anschluss von Y/C-Signalen vorsehen.                                                                                            | ANF-5  |

| Die <b>Kaskadierung</b> in 16 er Schritten bis auf 32 Videoeingangskanäle soll möglich sein.                                                                            | ANF-6  |

| <b>Alarmeingänge</b> und die <b>Signalisierung</b> der Kanalstörungen sind bei Kaskadierung, so wie bei der Basiseinheit auszuführen.                                   | ANF-7  |

| Der Videoausgang des Multiplexers soll einen konstanten, <b>synchronen FBAS Stream</b> von Videobildern liefern.                                                        | ANF-8  |

| Die Bildrate am Ausgang des V-MUX muss konstant auf <b>50 Halbbilder /s</b> gehalten werden um einen kontinuierlichen Videostrom zu erhalten.                           | ANF-9  |

| Jedes <b>einzelne Halbbild</b> des Videostroms am Ausgang des V-MUX muss von verschiedenen Kameras oder Videoquellen sein können.                                       | ANF-10 |

| Die maximale Bildrate pro Videokanal muss <b>ereignisgesteuert</b> über Alarmeingänge oder der seriellen Schnittstelle, bis auf 25 Halbbilder / s erhöht werden können. | ANF-11 |

| Die Bildrate soll von außen über potentialfreie <b>Alarm Kontakte</b> verändert werden können.                                                                          | ANF-12 |

| Die Bildrate soll von außen über die <b>serielle Schnittstelle</b> verändert werden können.                                                                             | ANF-13 |

# DIPLOMARBEIT Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

Aufgabenstellung

| Innerhalb einer Sekunde muss von einer angeforderten Kamera <b>mindestens 1 Bild am Ausgang</b> ausgegeben werden, unabhängig in welcher Betriebsart sich das Gerät befindet. Diese Forderung ist mit höchster Priorität zu verfolgen, da sie eine wichtige Projektanforderung repräsentiert.                        | ANF-14 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Die Ausgabe von Vollbildern muss möglich sein.                                                                                                                                                                                                                                                                       | ANF-15 |

| Die <b>Bildfolge</b> am Ausgang des V-MUX soll durch potential freie Alarmkontakte am V-MUX verändert und gesteuert werden können.                                                                                                                                                                                   | ANF-16 |

| Die <b>Bildfolge</b> am Ausgang des V_MUX soll durch die serielle Schnittstelle verändert werden können.                                                                                                                                                                                                             | ANF-17 |

| Die <b>Parametrierung</b> des V-MUX soll über eine serielle Schnittstelle erfolgen.                                                                                                                                                                                                                                  | ANF-18 |

| Es ist darauf zu achten, dass die <b>Äquidistanz</b> der Bildfolge von allen Kameras gegeben ist.                                                                                                                                                                                                                    | ANF-19 |

| Das Videosignal am <b>Ausgang</b> des V-MUX muss einem Standard <b>FBAS Signal</b> entsprechend CCIR-601 sein.                                                                                                                                                                                                       | ANF-20 |

| Das Design soll die Erweiterung auf die Ausgabe von Y/C-Signalen vorsehen.                                                                                                                                                                                                                                           | ANF-21 |

| Das Videosignal muss von einem am <b>Markt erhältlichen Framegrabber</b> , verarbeitbar sein, um im ersten Schritt des Gesamtkonzeptes die Videospeicherung ohne Neuentwicklung einer digitalen Framegrabberkarte realisieren zu können. Als Produktvorgabe soll eine MIRO DC20 oder DC30 Framegrabber Karte gelten. | ANF-22 |

| Die geforderte Video-Auflösung soll min. <b>704 (H) x 288 (V) pro Halbbild</b> betragen.                                                                                                                                                                                                                             | ANF-23 |

| Zwischen den einzelnen Schnittpunkten der Signalweitergabe soll ein einheitlicher <b>Farbraum</b> verwendet werden, um ohne aufwendige Transformationen und Transcodierungen auszukommen.                                                                                                                            | ANF-24 |

| Das Videosignal am Eingang soll innerhalb von 3dB ohne eine Störmeldung zu generieren variabel sein.                                                                                                                                                                                                                 | ANF-25 |

| Ein dem Videosignal <b>überlagerter Gleichstromanteil</b> , wie er oft zur Versorgung von Entzerrverstärkern innerhalb eines CCTV Systems verwendet wird, ist innerhalb der PAL Norm zu tolerieren.                                                                                                                  | ANF-26 |

| Syncverlust soll als Störmeldung pro Kanal über eine optische Anzeige erfolgen.                                                                                                                                                                                                                                      | ANF-27 |

| Die <b>Störmeldungen</b> sollen über die serielle Schnittstelle an das Sicherheitsmanagementsystem weitergegeben werden.                                                                                                                                                                                             | ANF-28 |

| Alle <b>Kanäle sind abschaltbar</b> auszuführen, um defekte Kameras oder Videoquellen leicht abschalten zu können.                                                                                                                                                                                                   | ANF-29 |

| Die <b>Verzögerung</b> zwischen Eingangssignal und Ausgangssignal soll kleiner als 100ms sein.                                                                                                                                                                                                                       | ANF-30 |

#### **Tabelle 2 Anforderungskatalog**

# 4.3 Konstruktive Anforderung an den V-MUX

Um die zu entwickelnde Baugruppe in einem modernen CCTV System zu betreiben, soll noch die Einhaltung folgender allgemeinen konstruktiven Anforderungen erwähnt werden.

# **Konstruktive Anforderungen V-MUX:**

| Steckeranschlüsse sollen in <b>BNC</b> ausgeführt werden                                                                                                              | K-ANF-1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Für die Stromversorgung sollen Standard Kaltgerätestecker verwendet werden.                                                                                           | K-ANF-2  |

| Die Kanten des Gehäuses sollen <b>entgratet</b> sein, um Verletzungen vorzubeugen.                                                                                    | K-ANF-3  |

| Die <b>serielle Schnittstelle</b> soll an der Basiseinheit angebracht, als 25 poliger D-SUB Stecker ausgeführt werden.                                                | K-ANF-4  |

| Es sind zur Abführung der <b>Verlustleistung</b> ausreichend Lüftungsschlitze vorzusehen. Die Umgebungstemperatur im Schrank soll bis zu max 40° betragen können.     | K-ANF-5  |

| Die <b>Einbautiefe</b> des V-MUX soll 40 cm nicht überschreiten, damit im Schrankinneren noch Patchkabel geführt werden können.                                       | K-ANF-6  |

| Alle abnehmbaren Teile sollen rastend oder schraubend befestig werden.                                                                                                | K-ANF-7  |

| Die Befestigung am Schrank soll mit Standard 19" Montagematerial erfolgen.                                                                                            | K-ANF-8  |

| Das Aufrüsten oder Herausnehmen von defekten Bauteilen soll in <b>kurzer Zeit</b> erfolgen können. Vorgabe: 30' für Tausch oder Aufrüsten eines Videokanals.          | K-ANF-9  |

| Die Anzeige und Schalter sollen an der Gerätefront ausgeführt werden.                                                                                                 | K-ANF-10 |

| Alle Modul Baugruppen sollen <b>steckbar</b> ausgeführt werden.                                                                                                       | K-ANF-11 |

| Der V_MUX soll für die <b>Montage</b> in einem 19" Schrank ausgelegt werden.                                                                                          | K-ANF-12 |

| Die <b>Kaskadierung</b> soll innerhalb einer Baugruppe erfolgen und nicht örtlich verteilt angeordnet werden, so dass der maximale Kabelweg 0,5m nicht überschreitet. | K-ANF-13 |

| Der V-MUX soll den geltenden Normen (5022 - B) für EMV entsprechen.                                                                                                   | K-ANF-14 |

| Die ÖVE Norm für industrielle Geräte soll eingehalten werden                                                                                                          | K-ANF-15 |

#### **Tabelle 3 Konstruktive Anforderungen**

# 4.4 Erweiterte Anforderungen

Zusätzlich zur im Punkt 4.2 und 4.3 beschriebenen Aufgabenstellung und Anforderungen an den V-MUX sind zum Aufbau eines digitalen CCTV Überwachungssystem, weitere in der vorliegenden Arbeit nicht erarbeitete Forderungen umzusetzen. Es sollen damit spätere und derzeit schon bekannte, Wünsche und Anforderungen leicht unter Einbeziehung des neu gebauten Geräts realisiert werden können.

Die V-MUX Einheit soll so konzipiert werden, dass sie vollständig, oder zumindest einzelne Module daraus, auch für ein durchgehend digitales Videoaufzeichnungssystem verwendet werden können. In den Designüberlegungen soll auf diese Forderung eingegangen werden, ohne dadurch den sehr engen Zeithorizont zu beeinflussen. Das Ziel der Entwicklung soll sein, dass ein neues Videoüberwachungssystem entsteht, welches ohne den Zukauf von Standard Framegrabbern auskommt. Der Im V-MUX generierte digitale Videostrom soll ohne weitere Decodierung auskommen und zur Verarbeitung im PC bereitgestellt werden. Eine breitbandig und möglichst bidirektionale digitale LVDS Schnittstelle soll den FBAS Ausgang sowie die serielle Steuerleitung des V-MUX in einem weiteren Entwicklungsschritt ersetzen. Alle für die Übertragung notwendigen Signale sollen daher in dieser Entwicklungsstufe schon auf Steckverbindungen vorhanden sein. Die Schnittstelle soll dann weiters auch für digitale Signalverarbeitung genutzt werden um Video Algorithmen hardwarenah implementieren zu können.

# 4.5 Entwicklungsziel

Um eine wirtschaftliche Umsetzbarkeit der Arbeitsergebnisse zu ermöglichen sind folgende nicht technische Entwicklungsziele zu beachten.

- USP (**U**nique **S**elling **P**ropositions) gegenüber der Konkurrenz

- Kurze Realisierungszeit

- Robust gegenüber zukünftige Technologien im Bezug auf Erweiterungen

- Skalierbarkeit (Designanforderung)

- Große Lifetime

- Servicefreundlich

- Bedienerfreundlich

- Schnittstelle zum PKE Leitsystem

# 5 Bekannte Lösungen

Basierend auf der Aufgabenstellung im Kapitel 4, die im wesentlichen einer konkreten Kundenanforderung entstammt, soll im nun folgenden Abschnitt analysiert werden, ob sich ein digitales Videoüberwachungssystem mit den geforderten Anforderungen aus zur Zeit am Mark erhältlichen Geräten aufbauen lässt. Wichtigste Anforderung die der Auswahl zu Grunde liegt, ist die Forderung auf Äquidistanz der Bildfolge und des schnellen Zugriffes auf Einzellalarmbilder. Ein weiterer wichtiger Aspekt liegt auf dem minimalen Hardware Aufwand und der damit verbundenen multiplikativen Kosten pro Kameraeingang.

Aus den am Markt befindlichen Geräten kann man erste Tendenzen in Richtung digitale Systeme erkennen, wobei ein Großteil noch auf analoge Bandmedien zur Aufzeichnung zurückgreift.

## 5.1 Marktanalyse

Aufgrund des großen Zeitdruckes bei der Projektrealisierung wurde die Marktanalyse auf Systeme vom Mitbewerb und auf schon etablierten Lösungen eingeschränkt. Noch nicht am Markt befindliche Systeme im Prototypstatus wurden bei der Marktanalyse nicht berücksichtigt, da ein zu großer Unsicherheitsfaktor in Bezug auf die Realisierung des Gesamtprojektes inakzeptabel war.

Zur quantitativen Bewertung der einzelnen Varianten wurde eine mittlere Anlage im CCTV Bereich angenommen. Dieses fiktive CCTV Überwachungssystem besteht aus 200 Kameras mit einer Alarmbildrate von mindestens 3 – 5 Bilder pro s in einer Auflösung von 2CIF (704x288).

Aus der Marktanalyse kristallisierten sich drei mögliche Varianten die zur Realisierung des Projektes herangezogen werden können heraus. Diese Varianten wurden bewertet und dann den Entscheidungsträgern präsentiert, um die weitere Vorgangsweise zu definieren.

## 5.2 Methoden

Die Verifikation der Probanden bezüglich der technischen Aspekte erfolgte durch Prüfung der Hauptanforderungen aus dem Kapitel 4. Für die Gesamtbewertung der einzelnen Produkte und Lösungen sind neben den technischen Bewertungen auch kommerzielle und für das Unternehmen strategische Argumente hinzugezogen worden. Die Präsentation des Ergebnisses erfolgte in Form einer Matrix.

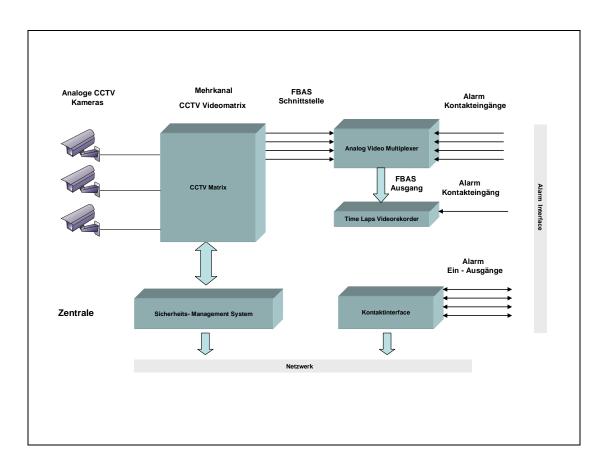

#### 5.2.1 <u>Variante 1</u>

Als bewährte und einfachste Variante ein CCTV Alarm- und Aufzeichnungssystem zu realisieren ist im folgenden Übersichtsbild zu sehen. Das System besteht aus einer analogen Video Matrix, an der die CCTV Kameras angeschlossen sind. Die Alarmvideoausgänge der Matrix werden am analogen Videomultiplexer angeschlossen. Ein Langzeit- Alarm Videorekorder zeichnet dann die relevanten Alarmvideos auf. Die Aufzeichnungssteuerung und das Umschalten der Bildraten erfolgt über potentialfreie Kontakte. Das schnelle Auffinden von gespeicherten Sequenzen ist bei dieser Variante nur von geschulten und erfahrenem Sicherheitspersonal möglich, da keinerlei Index Information mit den Alarmkontakten mitgeliefert wird, der das Auswerten erleichtern könnte.

Abbildung 2 Analoges CCTV System mit Management

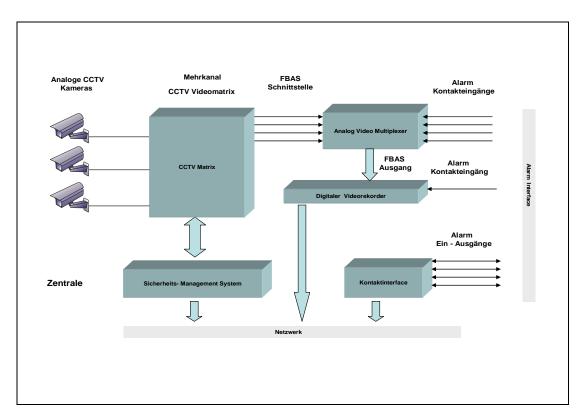

#### 5.2.2 Variante 2

Der aufwendigen und unübersichtlichen Recherche, konnte man durch Ersetzen des Time- Laps Videorekorders mit einem digitalen Videorekorder entgegnen. In dieser Variante, welche sehr viele Hersteller und Errichter von CCTV System als den Schritt in die digitale Technik gesehen hatten, sind außer der Veränderung des Speichermediums und der Konvertierung des analogen Videosignals in ein digitales Format keine konzeptionellen Erneuerungen passiert. Datenraten haben sich gegenüber einem analogen VCR durch die Digitalisierung nicht geändert. Der Kanalpreis ist durch teuere Speichermedien enorm gestiegen und brachte keine unmittelbar erkennbaren Vorteile. Nur Auswertungen konnten ab der Digitalisierung erheblich komfortabler und schneller erledigt werden. Ein Vorteil dieser Variante, der zu diesem Zeitpunkt noch nicht relevant war, ist die Möglichkeit der Verteilung des Systems und der Information innerhalb des Netzwerkverbundes.

**Abbildung 3 Hybrides CCTV System mit Management**

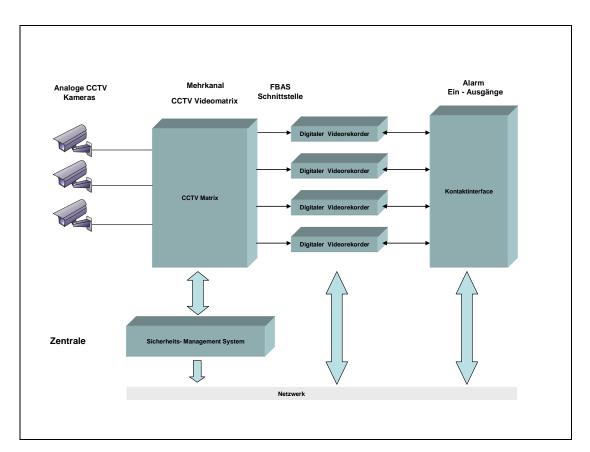

#### 5.2.3 Variante 3

Die einfachste Realisierung, ein digitales CCTV Videosystem mit den geforderten Anforderungen und optimaler Performance, wird technisch durch die Verwendung eines digitalen Aufzeichnungssystems pro Videokanal erreicht. Der leichten Handhabung bei der Recherche sowie dem übersichtlichen Aufbau steht ein astronomischer Preis entgegen. Die Anforderung der Äquidistanz und der minimalen Bildrate von 3-5 pro Kanal werden sofort erfüllt, da immer ein kontinuierlicher Datenstrom besteht. Der Aufbau von 200 Kanälen ist durch den enormen Platzbedarf, des Energiebedarfes und der Ausfallanfälligkeit der Anlage, keine in großer Stückzahl praktikable Lösung. Trotz dieser schier unüberwindlichen technischen Hürden gibt es Installationen dieser Variante in Hochsicherheitsbereichen.

**Abbildung 4 digitales CCTV System mit Management**

# 5.3 Analyse

Die Kriterien der kommerziellen und technischen Bewertung basieren zum Großteil auf den Anforderungen Kapitel 4.2 ergänzt mit allgemeinen Anforderungen von CCTV Systemen. Die Bewertung wurde im bekannten Schulnotensystem von 1 – 5 durchgeführt, wo 1 Sehr gut und 5 schlecht ist. Es wurden keine Projektspezifischen Zusatzfaktoren, wie definierte Kanalpreise oder maximale Packungsdichte berücksichtigt, da sonst Ausschlusskriterien entstanden wären. Die Bewertung erfolgte immer relativ zu den einzeln untersuchten Varianten.

| Nr | Bewertungskriterium                                       | V1 | V 2 | V 3 |

|----|-----------------------------------------------------------|----|-----|-----|

| 1  | Eingangskanäle mindestens 16                              | 3  | 4   | 1   |

| 2  | Kanalpreis                                                | 2  | 4   | 5   |

| 3  | Speicherpreis für ca 15 000 Alarmereignissen -Dauer 30"   | 1  | 5   | 5   |

| 4  | Wiederauffinden von Ereignissen                           | 5  | 3   | 1   |

| 5  | Verarbeitung von nichtsynchronen Kameras                  | 5  | 4   | 1   |

| 6  | Thermisches Verhalten                                     | 3  | 3   | 5   |

| 7  | Wartungsfreundlichkeit                                    | 5  | 3   | 4   |

| 8  | Mischen von Farb und SW Kameras                           | 4  | 4   | 1   |

| 9  | Kaskadierung und Packungsdichte pro Kanal                 | 3  | 2   | 5   |

| 10 | Alarmeingänge analog / digital                            | 4  | 2   | 1   |

| 11 | Lückenlose Aufzeichnung bei Kanalumschaltung              | 5  | 3   | 1   |

| 12 | Bildrate mindestens 5 Halbbilder /s pro Kamera            | 4  | 3   | 1   |

| 13 | Ereignisgesteuerte Erhöhung der Alarmbildrate             | 5  | 4   | 1   |

| 14 | Schnittstelle zu übergeordnetem Leitsystem                | 5  | 3   | 1   |

| 15 | Aufzeichnung eines neuen Alarmbildes innerhalb 1 Sekunde. | 5  | 5   | 1   |

| 16 | Aufzeichnung von Voralarmen                               | 5  | 3   | 1   |

| 17 | Auflösung der Aufzeichnung (mindestens 704 x 288)         | 4  | 3   | 1   |

| 18 | Individuelle Programmierbarkeit                           | 5  | 3   | 1   |

| 19 | Äquidistanz der Bildfolge                                 | 5  | 4   | 1   |

| 20 | Störempfindlichkeit                                       | 1  | 3   | 3   |

| 21 | Störmeldungen erkennen und anzeigen                       | 4  | 3   | 2   |

|    | Summe                                                     | 83 | 71  | 43  |

Tabelle 4 Ergebnisse der Marktanalyse

## 5.4 <u>Bemerkungen</u>

#### Variante 1

Bei Variante 1 ist eine Verzögerung bis zur Aufzeichnung des Ereignisses aufgrund des Konzeptes nicht zu vermeiden. Die Anforderung innerhalb einer Sekunde nach Auftreten eines Ereignisses ein Alarmbild gespeichert zu haben, kann mit dieser Methode nicht erfüllt werden.

Die Verzögerungen setzen sich bei dieser Variante aus 2 Komponenten zusammen:

- Bei analogen Multiplexern muss das neue Videosignal mindestens 5 10

Halbbilder lang am Schalter anstehen, damit ein stabiles Bild am

Ausgang ausgegeben wird.

- Nach Aktivieren der Aufzeichnung, braucht ein analoger Videorekorder

Zeit, bis Bilder gespeichert werden können. Bei einigen Modellen wurden

Verzögerungen im Sekundenbereich beobachtet.

#### Variante 2

Bei Variante 2 ist das Delay, zwischen Alarmzeitpunkt und dem ersten verwertbaren Alarmbild, verbessert. Bei dieser Variante entfällt das Einfädeln des Bandes bis zur Aufzeichnung, da auf Festplatten gespeichert wird. Der Anforderung innerhalb einer Sekunde ein verwertbares Bild zu erhalten, kann jedoch bei rentabler Eingangskanalzahl nicht gerecht werden. Ähnlich wie bei Variante 1 ergibt sich die Verzögerung aufgrund des Einschwingverhaltens des Analog Digital Wandlers am Eingang des digitalen Videorekorders, da die Bilder immer von anderen Kameras kommen. Einigermaßen stabile äquidistante Bilder mit einer Bildrate von 5 Bildern pro Sekunde erhielt man bei einer Kanalzahl von 2 – 3, was wirtschaftlich nicht vertretbar ist.

#### Variante 3

Die technisch optimale Lösung zur Erfüllung der Projektanforderung zeigt sich in Variante 3. Jeder analoge Videokanal wird ohne Multiplexer auf eine Framegrabberkarte geführt und dann digital gespeichert. Aufgrund der noch nicht so hohen Performance von handelsüblichen Framegrabberkarten gibt es eine Begrenzung der Framerate auf 25 Bilder pro Sekunde. Innerhalb einer Sekunde ein verwertbares Bild zu erhalten, stellte auch kein Problem dar. Was diese Variante jedoch zum Scheitern verurteilte, ist der hohe Leistungsverbrauch, die Anfälligkeit der rotierenden Medien innerhalb des Computers und nicht zu letzt der hohe Preis.

## 5.5 Schlussfolgerung

Eine Vielzahl der am Markt verfügbaren Videosysteme basierte auf analoge Komponenten, mit einer digitalen Schnittstelle zu einem übergeordneten Sicherheitsmanagementsystem. Die digitale, meist serielle Schnittstelle zu einem übergeordnetem Leitsystem war auch schon das Modernste, das ein solches System zu bieten hatte. Meist erfolgte die Alarmierung und Signalisierung nur über Relais und potentialfreie Kontakte. Erste Tendenzen hin zu einem voll digitalem System mit der geforderten Performance konnte in Variante 3 erkannt werden. Diese ist aufgrund der zu hohen Kosten in der Errichtung und Betrieb nicht wirtschaftlich einsetzbar. Zur Umsetzung des Projektes, und mit der Vision einen strategischen Vorteil gegenüber dem Mitbewerb zu generieren, sollte das Videoüberwachungssystem mit hauseigenen Produkten realisiert werden. Die dazu fehlende Hauptkomponente, der Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge mit der Steuerungs- und Aufzeichnungssoftware, soll neu entwickelt werden. Diese Neuentwicklung soll möglichst alle Vorteile der unterschiedlichsten Lösungen einbeziehen. Der Preis und der Hardwareaufwand, sowie die Wartungsfreundlichkeit, soll einen großen Abstand und USP zum Mitbewerb ergeben.

# 6 Architekturüberlegungen

Welche Konzepte führen zum Erfolg einer Neuentwicklung? Diese Frage stellte sich zu Beginn der Entwicklung. Wichtigste Hinweise waren zu diesem Zeitpunkt die Ergebnisse der Marktanalyse, und die Kundenanforderung des konkreten Projektes, wo zumindest die Eckdaten am Tablett lagen. Die Motivation war natürlich sehr groß, nicht nur die Anforderungen zu erfüllen, sondern gleich wegweisende Akzente zu setzen. Die Kreativität wurde nur durch den engen Zeithorizont in die Schranken gewiesen. Letztlich fiel die Entscheidung auf eine Kompromisslösung mit den Möglichkeiten einer schnellen Erweiterung.

Die wichtigsten Eckpfeiler waren die Erfüllung der schnellen Umschaltung beim Bildwechsel, um zumindest pro Sekunde 1 stabiles Alarmbild zu erreichen, und der modulare Aufbau des V-MUX, um Ausbauvariationen offen zu lassen. Konventionelle Video Multiplexer arbeiten in der Kanalumschaltung vollständig analog, ohne die einzelnen Kamerasignale zwischenzuspeichern, und verlieren in der Umschaltphase meistens mehrere Fields. Es liegt auf der Hand, dass diese Schwachstelle beim Design ausgeschaltet werden muss, damit die Kanalzahl auf ein Niveau gehoben werden kann, um gegen den Kanalpreis von analogen Bandsystemen anzukommen. Der zur Zeit der Entwicklung übliche Auflösungsstandard orientierte sich an den verwendeten analogen Aufzeichnungsgeräten. Die VHS Videorekorder im CCTV entsprechen einer digitalen Auflösung von CIF (Common Intermediate Format) mit 352 x 288 Pixel. Ziel ist es ein System zu bauen, das die analoge Auflösung von CCTV Systemen erreicht, und für Verbesserungen der Auflösung gerüstet ist. Kompromisse in Bezug auf den benötigten Speicherbereich und der Bandbreite sollen durch umschaltbare Bausteine gefunden werden.

In dem nun folgenden Kapitel werden Möglichkeiten vorgestellt, wie eine

Schwachstellen, sei es im Design oder im zu hohen Anschaffungspreis,

eingegangen.

Realisierung des digitalen V-MUX erfolgen kann. Ebenso wird auf eventuelle

# 6.1 Analoger Eingangsschalter

Alle Eingangskanäle werden zyklisch nach jedem Halbbild umgeschaltet. Ein stabiles Bild liegt bei starr synchronisierten Eingangskanälen im Optimalfall nach jedem Videoframe an.

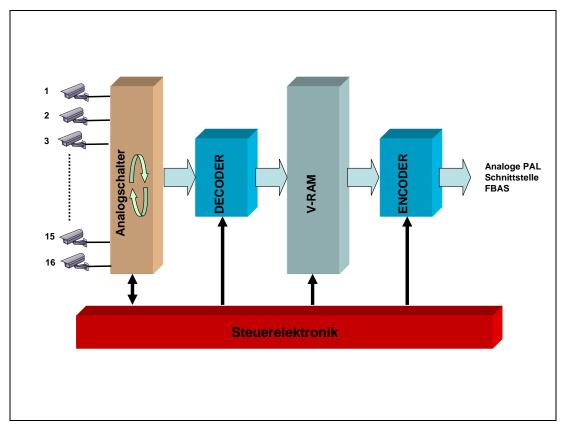

Abbildung 5 Analogschalter mit zentralem Video RAM

Das Umschalten der einzelnen Videokanäle ist bei dieser Methode nur mit synchronen Kameras möglich. Vorgabe im Kapitel 4 der Aufgabenstellung war, dass nur nach Methoden gesucht werden soll, die für den Anschluss von asynchronen Kameras geeignet sind. Eine Weiterverfolgung dieser Variante ist nicht ziel führend. Die Funktionsweise dieser Methode ist aber besonders gut geeignet, um das Umschaltverhalten konventioneller analoger Videomultiplexer zu erklären. Dazu sind einige Begriffe der analogen Videotechnik notwendig, die in den folgenden Absätzen beschrieben werden.

# 6.2 Analoges Videosignal

Bewegte Szenen aufnehmen um sie an einem anderen Ort wiederzugeben war seit der Erfindung von Paul Nipkow 1884 [9] möglich. Mit seiner Abtastscheibe schaffte er das theoretische Grundgerüst für Videoübertragung und Aufzeichnung. Schon damals war eines der wichtigsten Kriterien von Abtasten und Wiedergeben, dass Sender und Empfänger synchron und mit gleicher Geschwindigkeit gedreht werden. Basierend dieser Erfindung entwickelten sich verschiedenste Möglichkeiten ein Videosignal zu erzeugen. Ein Meilenstein der Kameraübertragungstechnik war die Röhrenkamera, wo alle mechanischen Teile einer Kamera eliminiert werden konnten, und die Grundsteine für Videoüberwachung gelegt wurden. Diese sehr aufwendige und teure Technik kam nur in Hochsicherheitsbereichen zum Einsatz. Erst durch die billigere und in Massen herstellbare CCD Chip Technik ist CCTV auch in Banken und Bürogebäuden möglich gewesen.

#### 6.2.1 Synchrosignal

Die von einer Videoquelle erzeugte Bildfolge muss auf der Anzeigeseite, sei es ein Monitor, oder wie in unserem Fall ein Videodecoder in gleicher Weise gelesen werden, wie sie in der Quelle erzeugt wurden. Diese so trivial erscheinende Anforderung ist oft nicht ganz einfach zu realisieren. Das aus Kompatibilitätsgründen über Jahre gleich gebliebene PAL verfügt zur Synchronisation der Horizontalen einen Impuls, der in jeder Zeile am Anfang 1,5 µs nach der vorderen Schwarzschulter positioniert ist. Die Synchronisation des Bildwechsels, der alle 20ms erfolgt, erfolgt in der so genannten Austastlücke. Das horizontale Synchronisationssignal von 4,7 µs Dauer, wird auf das 2,5 fache einer Zeilendauer verlängert, und signalisiert dann denn Vertikalen Bildwechsel[9] .

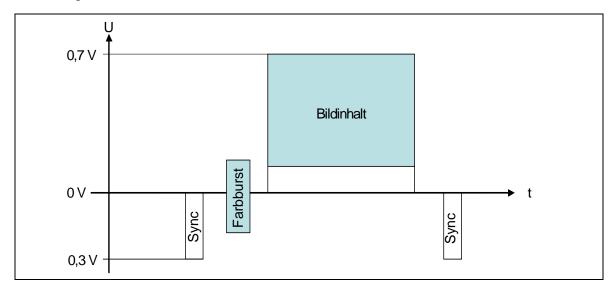

#### 6.2.2 Bildsignal

Die Darstellung der Bildsignale erfolgt durch Abbildung der Abtastwert mit analogen Werten. Der Wertebereich des Videosignals liegt bei einer Spannungsdifferenz von 0 bis auf 0,7 V, wobei 0V ein schwarzes Bild und 0,7V ein weißes Bild repräsentiert [9].

#### 6.2.3 Austastlücken

Historisch bedingte Zeit des Zeilensprungverfahrens von 12µs, wo der Elektronenstrahl von der rechten Seite des Bildrandes auf die Startposition am linken Rand springt [9] .

#### 6.2.4 <u>BAS</u>

Das auf der analogen Leitung messbare BAS Videosignal ist nun die Kombination aus Bild, Austast- und Synchronisationssignal.

#### 6.2.5 Auflösung

Für das PAL System stehen 625 Zeilen zu Verfügung, wo aber aufgrund der Austastung 25 Zeilen wegfallen. Die zur Bilddarstellung verwendbare Zeilenzahl ist auf netto 575 reduziert. Dieser obere Grenzwert reduziert sich wegen des Kellfaktors [9] von 0,67 auf 385 Linien die aufgelöst werden können. Das entspricht 193 Paaren von weißen und schwarzen Zeilen. Diese Reduktion der Auflösung ist physiologisch bedingt und berücksichtigt die Alias- Effekte bei der Abtastung von Strukturen die in die Nähe des Abtastrasters kommen. Die Verkleinerung der Zeilenauflösung um den Kellfaktor eliminiert diese Effekte.

#### 6.2.6 Abtastkennwerte für PAL VIDEO[1]

| Parameter                     | Erläuterung                                                                                                                                    | Wert   |    |                 |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|-----------------|

|                               |                                                                                                                                                |        |    |                 |

| Bildseitenverhältnis          |                                                                                                                                                | 4:3    |    |                 |

| Bildwechselfrequenz           | Anzahl der abgetasteten Vollbilder / s                                                                                                         | 25     | Hz | f <sub>w</sub>  |

| Bilddauer                     | Dauer der Abtastung eines Vollbildes T                                                                                                         | 40     | ms | $T_{w}$         |

| Halbbildfrequenz              | $fv = 2 - f_w$                                                                                                                                 | 50     | Hz | f <sub>v</sub>  |

| Halbbilddauer                 | Tv = 1 / fv = Tw / 2•Tv                                                                                                                        | 20     | ms | T <sub>v</sub>  |

| Bildaustastlücke              | Vertikale Austastlücke für Rücklauf des Elektronenstrahls bei Röhrenmonitoren                                                                  | 1,6    |    |                 |

| Zeilenzahl pro Vollbild       | Zeilen pro Vollbild                                                                                                                            | 625    |    | $n_B$           |

| Zeilenfrequenz                | Anzahl der Abgetasteten Zeilen pro<br>Sekunde                                                                                                  | 15.625 | Hz | f <sub>h</sub>  |

| Zeilendauer                   | Dauer der Abtastung einer Zeile $T_h = 1 / f_h$                                                                                                | 64     | μs | T <sub>h</sub>  |

| Aktive Zeilendauer            | Dauer der sichtbaren Zeile                                                                                                                     | 52     | μs | Ta              |

| Zeilenaustastlücke            | Horizontale Austastlücke für Rücklauf des Elektronenstrahls bei Röhrenmonitoren. Diese Lücke enthält Syncimpuls, Schwarzschulter und Farbburst | 12     | μs | T <sub>ah</sub> |

| Aktive Zeilen                 |                                                                                                                                                | 575    |    | $n_{Ba}$        |

| Dauer horizontaler Syncimpuls |                                                                                                                                                | 4,7    | μs |                 |

Tabelle 5 Abtastkennwerte für PAL Video

# 6.2.7 Frequenzkennwerte PAL VIDEO[1]

| Parameter          | Erläuterung                        | Wert |     |       |

|--------------------|------------------------------------|------|-----|-------|

|                    |                                    |      |     |       |

|                    |                                    |      |     |       |

| Videobandbreite    | Höchste im Videosignal vorkommende | 5    | MHz | $B_v$ |

|                    | Frequenz                           |      |     |       |

| Bandbreite der     | Bandbreite der Farbkomponenten     | 1,3  | MHz |       |

| Farbkomponenten    | U,V                                |      |     |       |

| Farbträgerfrequenz | Die Farbkomponenten werden auf den | 4,43 | MHz |       |

|                    | Farbträger moduliert und dann zum  |      |     |       |

|                    | FBAS addiert                       |      |     |       |

Tabelle 6 Frequenzkennwerte PAL VIDEO

# 6.2.8 Elektrische Kennwerte PAL VIDEO[1]

| Parameter         | Erläuterung                                                                                                     | Wert |    |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------|------|----|--|

|                   |                                                                                                                 |      |    |  |

| Weißpegel         | Der für den Bildinhalt mögliche Bereich liegt zwischen Weiß und Schwarzpegel                                    | 700  | mV |  |

| Schwarzpegel      |                                                                                                                 | 50   | mV |  |

| Austastpegel      | Wert unterhalb des Schwarzpegels für die Dunkeltastung des horizontalen und vertikalen Elektronenstrahlrücklauf | 0    |    |  |

| Sync- Signalpegel |                                                                                                                 | -300 | mV |  |

**Tabelle 7 Elektrische Kennwerte PAL VIDEO**

#### 6.2.9 Signalform FBAS

**Abbildung 6 FBAS Signalform**

## 6.3 Digitales Videosignal

Das analoge Videosignal wird mittels Pulscodemodulation PCM digitalisiert und aus dem kontinuierlichen analogen Videostrom ein diskreter digitaler Videostrom erzeugt. Verschiedene Methoden unterscheiden sich in Qualität und Bandbreite aufgrund unterschiedlichster Komprimierung und Datenreduktion. Die Digitalisierung des FBAS Signals kann komponentenweise oder als ganzes erfolgen. In der hier beschriebenen Arbeit wird das Komponentenverfahren angewandt, welches sich im CCTV etabliert hat. Es kann sowohl für PAL als auch für NTSC Signale angewendet werden.

#### 6.3.1 Digitalisieren nach CCIR 601

Die seit 1981 gültige Norm beschreibt die getrennte Digitalisierung von Leuchtdichtekomponenten und Farbkomponenten. Alle für die genormte Digitalisierung von Videosignalen erforderlichen Parameter werden in dieser Norm beschrieben und sind im Kap 6.3.2 zusammengefasst. Zur Reduzierung der Bandbreite werden generell 3 verschiedene Verfahren der Unterabtastung angewandt. In der CCIR 601 wird nur die 4:2:2 Variante genutzt die gegenüber der 4:4:4 Variante das Datenaufkommen um 30% reduziert[1].

#### 6.3.2 Kennwerte Digitaler Videosignale nach CCIR 601 [1]

| Parameter                                            | Erläuterung                          | Wert               |                       |                 |

|------------------------------------------------------|--------------------------------------|--------------------|-----------------------|-----------------|

|                                                      |                                      |                    |                       |                 |

| Abtastfrequenz                                       |                                      | 13,5               | MHz                   | f <sub>AY</sub> |

| Leuchtdichtesignal                                   |                                      |                    |                       |                 |

| Abtastfrequenz                                       |                                      | 6,75               | MHz                   | $f_{AC}$        |

| Farbdifferenzsignale                                 |                                      |                    |                       |                 |

| Abtastrate                                           | Anzahl der Abtastwerte je<br>Sekunde | 27x10 <sup>6</sup> |                       |                 |

| Codierung                                            |                                      | 8                  | Bit                   | N               |

| Bitrate                                              | Bitrate der seriellen                | 216                | 10 <sup>6</sup> Bit/s | r               |

|                                                      | Abtastung inklusive inaktiven        |                    |                       |                 |

|                                                      | Werten                               |                    |                       |                 |

| Aktive Bitrate                                       | Bitrate der seriellen                | 165,888            | 10 <sup>6</sup> Bit/s | r <sub>a</sub>  |

|                                                      | Abtastung nur aktive Werte           |                    |                       |                 |

| Abtastverfahren                                      |                                      | 4:2:2              |                       |                 |

| Zeilenzahl                                           | Anzahl der aktiven Zeilen            | 576                |                       |                 |

| Y-Abtastwerte                                        | Bei Abtastung der ganzen             | 864                |                       | n <sub>Y</sub>  |

|                                                      | Zeile inklusive Austastlücken        |                    |                       |                 |

| C <sub>B</sub> , C <sub>R</sub> – Abtastwerte        | Bei Abtastung der ganzen             | 432                |                       | N <sub>C</sub>  |

|                                                      | Zeile inklusive Austastlücken        |                    |                       |                 |

| Aktive Y- Abtastwerte                                | Nur aktive digitale Zeile            | 720                |                       | n <sub>Ya</sub> |

| Aktive C <sub>B</sub> , C <sub>R</sub> – Abtastwerte | Nur aktive digitale Zeile            | 360                |                       | N <sub>Ca</sub> |

| Dauer aktive digitale Zeile                          |                                      | 53,33              | μs                    |                 |

Tabelle 8 Kennwerte Digitaler Videosignale nach CCIR 601

# 6.4 <u>Digitaler V- RAM Schalter</u>

Damit vom A/D Wandler des V-MUX immer ein kontinuierliches, analoges Signal anliegt und keine Verzögerungen augrund des Einschwungvorganges beim Kanalwechsel entsteht, ist die Beste, jedoch kommerziell aufwendigste Lösung, an jedem Eingang des V-MUX einen A/D Wandler zu setzen. Das Problem der Synchronisation ist dadurch auch noch nicht gelöst. Zur Synchronisation der asynchronen Quellen gibt es auf digitaler Seite nun zwei Ansatzpunkte, wo diese stattfinden kann. Eine Möglichkeit ist es, ein großes Globales V-RAM, oder je Kanal ein V-RAM zu beschreiben, und dann synchron auszulesen.

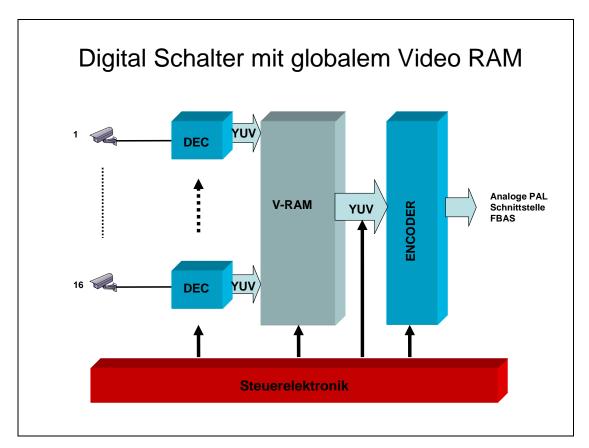

#### 6.4.1 Globales V-RAM

Alle bis zu 32 digitalen Videoströme beschreiben das V-RAM und werden synchron ausgelesen. Diese Möglichkeit der Synchronisation asynchron anstehender Videosignale bedeutet einen erheblichen Aufwand in der Verwaltung der Videoströme. Bei einer guten Umsetzung kommt man mit weniger V-RAM aus, da immer nur das Bild von der zur Ausgabe nächsten Kamera eingezogen werden muss.

Abbildung 7 Globales V-RAM als Schalter

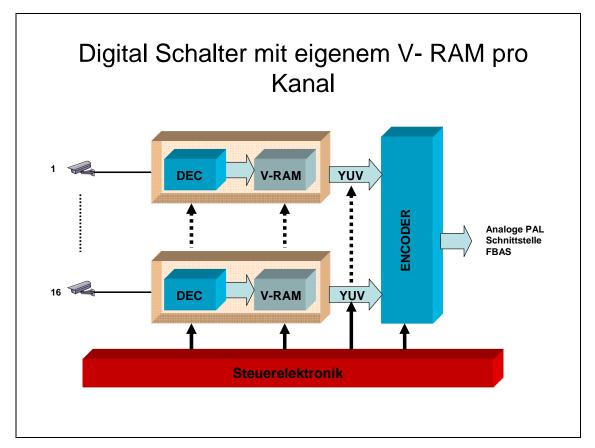

#### 6.4.2 <u>Diskretes V-RAM pro Kanal</u>

Beim überprüfen der Anwenderanforderungen, wo durchaus Wartungsfreundlichkeit, einfache Fehlerdiagnose und Modularität wichtige Punkte darstellten, ist die in diesem Abschnitt vorgestellte Methode zu bevorzugen. Jeder Kanal bildet ein abgeschlossenes System, wo jeder Kanal einen eigenen A/D Wandler und ein V-RAM hat. Am Ausgang des V-RAM steht zu jedem Zeitpunkt ein fertiges Videobild an, das vom Encoder ausgelesen werden kann. Einzig die Performance und die Lese Schreib Modi der verschiedensten V-RAM Bausteine müssen den Anforderungen entsprechen. Alle 20 ms muss ein gültiges Bild innerhalb der vertikalen Austastlücke von 1,6ms ausgelesen und vom Encoder gewandelt werden können, um am Ausgang einen kontinuierlichen analogen Videostrom zu erzeugen.

Abbildung 8 Diskretes V-RAM pro Videokanal

# 7 Architekturauswahl

Basierend dem theoretischen Grundkonzept soll nun eine Architektur gefunden werden, die nun auch dem praktischen Einsatz unter den Bedingungen des rauen Alltags standhält. Die Vorgabe des modularen Aufbaus lässt nun auch das schnelle Ein und Auslesen des V-RAM zu einer Kernthematik der Architektur werden. Beim durchforsten der Chiphersteller für A/D Wandler und V-RAM ist die Auswahl zu gunsten schneller Realisierung sehr bald eingeschränkt geworden. Aufgrund guter Erfahrung und Vertrautheit mit der Produktfamilie von Philips Semiconductors sind die Basiskomponenten für Video von Philips verwendet worden. Durch die sehr gute Kompatibilität und der versprochenen sehr schnellen lese Zyklen durch paralleles Auslesen, ist die Wahl für das V-RAM auf ein Produkt von Hitachi gefallen.

# 7.1 **Bauteilermittlung**

Bei Echtzeit Videoverarbeitung, wie bei der Realisierung des V-MUX gefordert ist, können nur hoch performante Bauteile zum Einsatz kommen. Nach der Recherche wurden die Hauptkomponenten in einem schnellen Verfahren geprüft, ob sie die geforderte Performance für bis zu 32 Kanäle im parallelen Betrieb erreichen. Zur Ermittlung der optimalen Modi und Betriebsarten der Bauteile wurde ein Evaluierungsboard DPC7146 V2.3 verwendet, wo die zur Realisierung angedachten Bauteile für A/D und D/A sowie die I²C Bus Steuerung vorhanden waren. Die mitgelieferte Software konnte dazu genutzt werden die optimalen Video Parameter der A/D und D/A Wandler zu ermitteln. Getestet wurde mit Testmethoden, die auch im Kapitel 10 angewendet werden.

## 7.2 Wandlerbauteile

#### 7.2.1 <u>A/D-Wandler SAA7110 A</u>

Der I<sup>2</sup>C – Bus gesteuerte Video Decoder SAA7110A [6] hat zur Signalaufbereitung verschiedenste Einheiten integriert. Die wichtigsten Parameter wie Sättigung, Kontrast, Helligkeit sowie der Farbraum können über den I<sup>2</sup>C Bus auch in Echtzeit gesteuert und variiert werden. Als analoges Signal kann sowohl ein Standard FBAS wie auch ein S-Video (Y/C) Signal angelegt werden. Die wichtigsten Kenngrößen sind:

- 2 Kanal pre-processing

- Automatische Verstärkungsregelung am Eingang

- Weißwert Kontrolle

- Horizontal und Vertikal Syncerkennung

- Helligkeit und Farbsignal Anpassung

- Automatische Erkennung von geradem und ungeradem Field

- 720 Abtastungen pro Zeile

- Spezielle Speicher Funktionen f

ür Schreib Operationen

- I2C BUS gesteuert

#### 7.2.2 D/A-Wandler SAA7185 B

Der I<sup>2</sup>C Bus gesteuerte CCIR kompatible SAA7184 and SAA7185B [7] digitale Video Encoder für digital YUV 4:2:2 auf analog PAL Video wird als Ausgabebaustein des V-MUX eingesetzt. Dieser Baustein ist kompatibel zum Decoder und kann ohne Farbraum Transformation das YUV Bus Signal encodieren. Die wichtigsten Kenngrößen sind:

- 16 Bit YUV Eingang

- Programmierbare horizontale und vertikale Sync Phase

- Helligkeit und Farbsignal Anpassung

- I2C-BUS gesteuert

## 7.3 Speicher

#### 7.3.1 <u>V-RAM HM530281W</u>

Das V-RAM HM 530281 wird direkt hinter dem Decoder Baustein situiert. Der Speicher kann beide Operationen (serielles Schreiben und schnelles, paralleles Auslesen) quasi zeitgleich ausführen. Die Leseoperation kann asynchron zum Schreiben erfolgen und ist damit zur Synchronisation der digitalen Signale am YUV Bus optimal geeignet. Der Chip kann mit einer Taktrate von bis zu 50 MHz betrieben werden und ergibt damit sehr geringe Delays zwischen Ein und Ausgang [3]. Wichtigste Kenngrößen sind:

- Völlig asynchrones serielles Schreiben und paralleles Lesen

- Interne Kontrolle der Speicheroperationen

- 50 MHz Schreib / Lese Zykluszeit

- 2 dimensionale Adressierung

- Video optimiert

### 7.4 Steuerung

#### 7.4.1 Steuereinheit MC68LC302PU16B

Die Wahl der Steuereinheit ist auf einen Prozessor gefallen, wo das Wissen aus vorherigen Entwicklungen voll einfließen konnte. Die Entscheidung fiel auf die CPU MC68LC302PU16B [11] von Motorola.

## 7.4.2 <u>I<sup>2</sup>C BUS Controller PCF 8584</u>

Die Kommunikation und der Datentransfer zwischen den Video Encoder und den Video Decoder Bausteinen erfolgen über ein serielles I²C-BUS Bussystem, das bei den ausgewählten Bausteinen integriert ist. Der I²C-BUS (Inter Integrated Circuit) ist ein bidirektionaler serieller 2-Draht Bus über den der gesamte Datenverkehr wie Adressierung, Schreib-/Lesesteuerung, Datenübertragung und Quittierung in 8-bit Steueranwendungen mit Mikrokontroller erfolgen kann. Auf zwei Leitungen, Taktleitung SCL (Serial Clock Line) und der Datenleitung SDA (Serial Data Line), findet der Informationsfluss zwischen den Bausteinen (die an den BUS angeschlossen sind) statt. Allen mit dem Bus verbundenen Bausteinen (das kann ein Mikrokontroller, ein LCD Treiber, ein Speicher, eine Tastatur, ein Decoder, oder ein Encoder sein) ist eine eindeutige Adresse zugeordnet. Der I²C-BUS ist ein echter Multi Master Bus mit einer Kollisionsdedektion. Die Datenübertragung erfolgt bitseriell, mit einem Quittierungsbit (ACK) am Ende der Sequenz mit einer Länge von 9 Taktimpulsen.

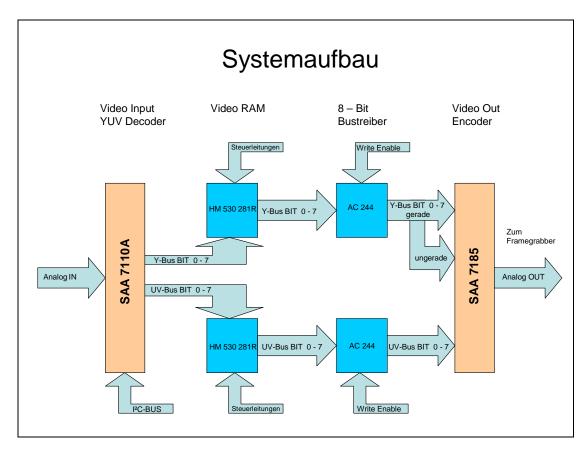

### 7.5 Systemaufbau

Abbildung 9 Systemaufbau

# 8 Systementwurf

Einen einzigen Kanal zu decodieren und auf der anderen Seite wieder zusammenzusetzen entspricht nicht ganz der Aufgabenstellung vom Kapitel 4. Mindestens 32 Kanäle müssen zentral verwaltet und synchron ausgegeben werden können. Durch das geschickte Aufteilen in funktionale Gruppen kann ein Mehrwert für Einsatzbereiche geschaffen werden, wo nicht immer von Vollbestückung ausgegangen wird. Diese in gewisser Weise kommerziell orientierten Gedanken sollen beim Systementwurf einfließen. Gibt es nun basierend dem Systemaufbau vom Kapitel 7.5 günstige Stellen, wo die Trennung der Kanäle erfolgen kann? Dieser komplizierten Fragestellung, mechanischer und elektrischer Natur wird im nun folgendem nachgegangen.

Ein modularer Aufbau mit Teilbestückungsmöglichkeit ohne mechanische Schwachstellen soll das Ergebnis sein. Da die Videosignale in unserem Fall ausschließlich asynchron anliegen, und um jedes Field zu erfassen, wurde jeder Videokanal mit einem eigenen Eingangsdecoder ausgestattet. Diese Methode soll gewährleisten, dass jedes Signal pro Eingang einwandfrei decodiert wird. Die Signale können dann ohne aufwendige Elektronik vom Decoder zum V-RAM weitergereicht werden.

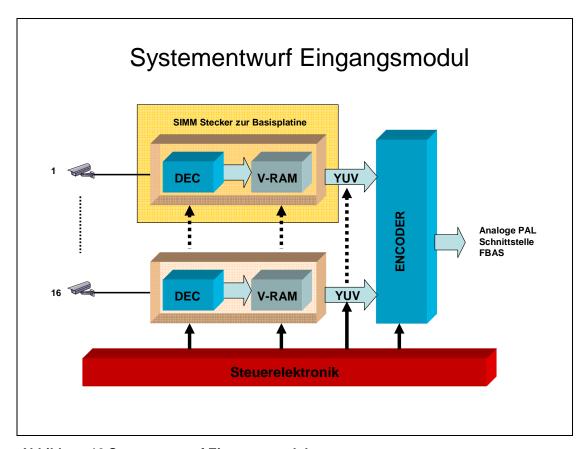

### 8.1 Eingangsmodul

Die Grundlagen des Synchronisierens von mehreren asynchron anliegenden Videokanälen wurden in den vorigen Kapiteln gelegt. Jeder Kanal soll mit einem A/D Wandler und dem zugehörenden Speicher ausgestattet werden. Bei der permanenten Platzierung der doch eher kostenintensiven Bauteile auf einer Basisplatine, auch wenn nicht immer alle Kanäle verwendet werden sollen, ist aus ökonomischen Gesichtspunkten nicht ziel führend. Angelehnt an eine Technik die aus der PC Welt kommt, da man dort weiß wie man mit teuren Modulen umgeht die nicht immer gebraucht werden, wurde auf eine Realisierung wie sie für SIMM Module Verwendung findet gesetzt. Jeder Videokanal bestückt mit einer separaten DEC-VRAM Einheit wo am Eingang das analoge Videosignal anliegt ist als eigene Platine ausgeführt. Die Verbindung zur Basisplatine wird über einen SIMM Sockel hergestellt. Am Ausgang jeder Platine liegt ein digitales YUV-Signal (4:2:2) an, das über einen BUS leicht verteilt werden kann. Jedes Eingangsmodul wird über den Steuerbus mit der Steuereinheit verbunden, welche dann die einzelnen Kanäle synchron auf die Encoder Einheit schaltet.

**Abbildung 10 Systementwurf Eingangsmodul**

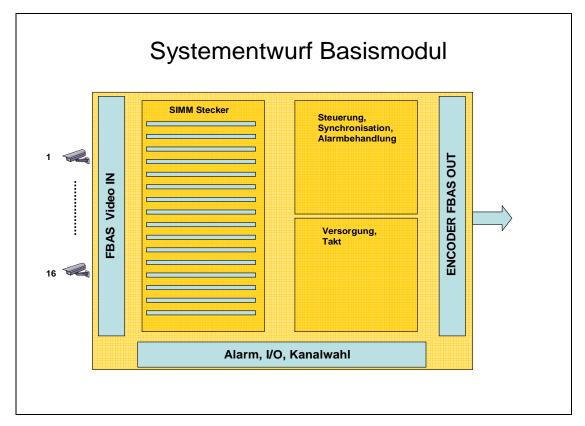

#### 8.2 Basismodul

Mechanisch anspruchsvolle Komponenten, wie die Videostecker,

Alarminterfaces und Kanalwahlschalter werden am Basismodul platziert. Die

Größe des Moduls ist durch die Forderung des 19" Einbaus vorgegeben.

Gedanken an eine Realisierung mit 32 Kanälen auf einer Platine wurden aus mehreren Gründen wieder verworfen. Einerseits ist der Platz für Wartungen sehr eng, anderseits ist eine 16 er Gruppe in der Videotechnik etabliert und die Mechanik sowie die Entflechtung der Leiterplatte bleiben überschaubar.

**Abbildung 11 Systementwurf Basismodul**

## 8.3 <u>Betriebsarten des Multiplexers</u>

Zur Grundfunktion der synchronen Ausgabe eines analogen Videostroms bestehend aus unterschiedlichen Kameras mit einer äquidistanten Bildfolge waren noch verschiedene Betriebsarten bei der Realisierung des V-MUX gefordert.

## 8.3.1 Normaler Multiplexbetrieb

Über den Kanalwahlschalter ausgewählte Kanäle fließen in den Synchronisationsprozess ein und werden im Normalbetrieb nacheinander äquidistant angeordnet und an den Encoder am Ausgang weitergegeben. Liegt am Eingang eines Kanals kein Videosignal an, so wird ein schwarzes Bild an den Encoder weitergegeben. Sind alle Kanalwahlschalter ausgeschaltet, wird ein Standard Farbbalken vom Encoder generiert und an den FBAS Ausgang gelegt.

#### 8.3.2 Alarmaufschaltung

Ausgangssituation ist der zuvor beschriebene Normalbetrieb. Wird nun über die Alarminterfaces ein Alarm detektiert, so ändert sich die Bildfolge des Normalbetriebes in der Form, dass der Alarmkanal bevorzugt behandelt wird. Jedem zweitem Bild der Normalfolge wird ein Bild des Alarmkanals vorangestellt. Bei mehreren gleichzeitigen Alarmen wird die Sequenz wie folgt zusammengestellt:

- Bild der Sequenz, gefolgt von allen Alarmkameras

- Nächstes Bild der Sequenz

- Alle Alarmkameras....

Steht für alle Kameras ein Alarm an, so ergibt sich schlussendlich wieder die Folge des Normalbetriebes.

## 8.4 Steuerung und Programmierung

Basierend des Grundprogrammes mit den beschriebenen Betriebsarten kann über die serielle Schnittstelle genau wie mit den Alarmkontakten die Bildfolge verändert werden. Zusätzlich kann auch das Basisprogramm für individuelle Projektanforderungen verändert werden. Das Programm bleibt im V-MUX gespeichert und kann nur durch Überschreiben oder Neuprogrammierung geändert werden.

# 9 Realisierung

Am Punkt der Realisierung angelangt scheint das Rennen schon gewonnen zu sein, da alle technischen Details geklärt sind und nur mehr das Entflechten als arbeitsintensiver Schritt ansteht. Für den Bau eines Prototyps trifft das zu, bei einer Serie sind oft Probleme der Verfügbarkeit von Bauteilen, die in mühsamer Kleinarbeit berechnet und ausgesucht worden sind ein Problem. Das Entwickeln eines neuen Produktes zur Marktreife bleibt spannend bis zum Lötbad. Nach dem Vortest, wo Essentials überprüft und im Extremfall Drahtbrücken als letzte

Schritte herangezogen werden, ist es geschafft und der Gesamtaufbau zur vollen Funktionalität kann beginnen.

## 9.1 Video-Out / Controller - Basisplatine

Das Herzstück der Basisplatine ist der Mikroprozessor MC68LC302 von Motorola, wo die Koordination und Steuerung des V-MUX stattfindet. Über die integrierte serielle Schnittstelle der Basisplatine wird das Steuerprogramm geladen und im Boot-Flash PROM abgelegt. Auf der Basisplatine sind die Alarmeingänge, I/O Ports, Steuertasten, Anzeige und Störmeldungs- LED und die BNC Buchsen situiert. Die Auswahl der einzelnen Komponenten erfolgt über den On- Board I2C-Controller. Zur Ausgabe des FBAS Videos werden die digitalen Videosignale gesteuert durch den Controller via YUV Bus auf den Encoder gelegt, wo dann die Signale in ein analoges Videosignal gewandelt werden.

Abbildung 12 Basisplatine

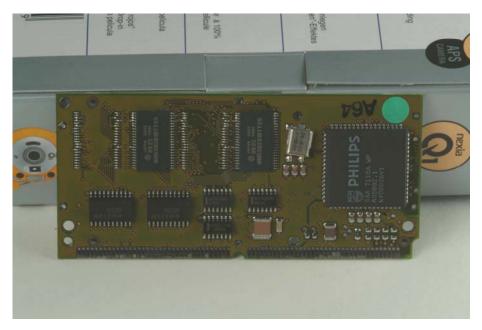

## 9.2 Video-Input - SIM-Modul

Der Video Decoder mit dem Frame Memory ist auf einem SIM (Single Inline Module) mit 72 pin Stecker aufgebaut. Das von der Basis Platine über Videoeingangverstärker geführte FBAS Signal wird durch den Decoder auf ein 16 Bit YUV Signal (CCIR-601) im 4:2:2 Format dekodiert. Pro Modul und Kanal wird ein Halbbild im V-RAM abgelegt. Optional kann das SIM auch für die Pufferung von Vollbildern in der vollen horizontalen Videoauflösung bestückt werden. Durch das asynchrone Auslesen des V-RAM zum jeweils benötigten Zeitpunkt wird dann über die Basiseinheit ein kontinuierlicher digitaler Videostrom am YUV-BUS erzeugt. Die Übergabe der ermittelten Videoparameter erfolgt vom Controller am Basisboard über den I<sup>2</sup>C-Bus.

Abbildung 13 Eingangsmodul Bauteilseite

## 9.3 Synchronisierung des Videosignals

Die Synchronisierung der asynchronen Videoquellen (Decoder) auf den gemultiplexten Videoausgang erfolgt durch das Frame Memory. Das Frame Memory gewährleistet ein asynchrones Schreiben und Lesen des Bildspeichers. Der Leseteil des Frame Memories wird vom Encoder auf der Basisplatine gesteuert.

## 9.4 <u>I<sup>2</sup>C-Bus Schnittstelle</u>

Die Konfigurierung des Decoders VIP (SAA7110) erfolgt über die I2C-Schnittstelle. Da die Video Chips nur über einen Adresspin zur Definierung der I2C Adresse verfügen, wird die I2C Clock auf dem entsprechenden SIM vom Controller über einen 4 aus 16 Decoder über eine Enable Leitung frei gegeben. Diese Schaltungstechnik ist dadurch möglich, weil die Video Chips nur im Slave-Mode arbeiten können.

## 9.5 Mechanischer Aufbau

Die V-MUX Basisplatine ist in einem EMV dichten Metallgehäuse eingebaut. Durch öffnen der Boden und Deckel Abdeckung kann die Kaskadierung der Geräte erfolgen. Das Aufstellen eines einzelnen V-MUX kann durch leichte Modifikationen der 19" Variante auch als Tischversion erfolgen. Die an der Seite angebrachten Metallwinkel dienen zur Befestigung in einem Standard 19" Schrank.

#### Front:

- 16 Tipptasten für jeden Eingang mit grüner LED Anzeige, zur individuellen Kanalabschaltung.

- 16 rote Alarm LED's

Abbildung 14 V-MUX Front geschlossen

**Abbildung 15 V-MUX Front offen**

#### Rückseite:

- 16 BNC FBAS Eingänge

- 1 BNC FBAS Ausgang

- Serielle Schnittstelle RS232 mit RJ45 Stecker oder DB9

- 16 Alarmeingänge über Schraubklemmen (2 Klemmen pro Eingang)

- 1 Alarmausgang, Relais mit erdfreiem Umschaltkontakt

#### Abbildung 16 V-MUX Rückansicht

#### **Interner Aufbau**

Der V-MUX besteht aus 16 Video Inputs als SIM und der Basisplatine mit dem Video-Encoder und dem Controller Prozessor 68LC302.

#### **Video Decoder Modul:**

- PAL Decoder

- Frame Memory mit YUV-Bus

#### Video Basisplatine:

- PAL Encoder

- Video Input Auswahl

- Alarmaufschaltung

- Steuerprozessor mit Flash-PROM, RAM, I<sup>2</sup>C Controller

## 9.6 Technische Daten

Die angegebenen technischen Daten sind die Tatsächlichen des realisierten Gerätes.

#### I/O Schnittstellen:

Videoeingang 1 bis 16

Videosignal: FBAS

• Eingangswiderstand:  $75\Omega$ , intern durch Jumper abschaltbar

Stecker: BNC

# DIPLOMARBEIT Mehrkanal Analog Digital Wandler für asynchrone Kameraeingänge

Realisierung

Videoausgang

Videosignal: FBAS

Ausgangswiderstand: 75Ω, intern durch Jumper abschaltbar

• Stecker: BNC

Schnittstelle für Alarmeingänge

Eingänge: CMOS Eingang mit internen Pull up

Widerstand,

Eingangswiderstand: 10kΩ, Pegel TTL

Stecker: Schraubklemmen

• Parametrierschnittstelle RS232

#### **Interner Bildspeicher:**

• je Kanal: Speicher für ein Halbbild (Option: Vollbild)

#### Versorgung:

Die Versorgung des Multiplexers erfolgt durch ein internes Netzgerät.

Stromaufnahme: +5V, vollbestückt ca. 5A

#### Umgebungsbedingungen:

#### Temperaturbereich:

- 0 bis +55 Grad (operating), keine direkte Sonnenbestrahlung

- -20 bis +70 Grad (non operating)

#### Feuchtigkeit:

20 bis 95% nicht kondensierend

## 9.7 Schnittstellen