The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## DISSERTATION

Experimental Characterisation of Smart Power Technology Devices Stressed by High Energy Pulses

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

o. Univ.-Prof. Dipl.–Ing. Dr. Erich Gornik am Institut für Festkörperelektronik E362

eingereicht an der Technischen Universität Wien, Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Matej Blaho Matrikelnummer 0126736 Hurbanova 185, 920 41 Leopoldov, Slowakei

Wien, im September 2005

# Kurzfassung

Die Zusicherung der Zuverlässigkeit von integrierten Halbleiterschaltungen (Integrated Circuits, ICs) ist eine der Hauptaufgaben in deren Konstruktion. Es gibt ein breites Spektrum von thermischen, mechanischen und elektrischen Belastungen, welche die Zuverlässigkeit von Halbleiterbauelementen beeinflussen. Um die verschiedenen Ausfallsmechanismen zu identifizieren, ist es notwendig die Bauelemente realen Tests zu unterziehen. Detaillierte Analysen der Testergebnisse führen zu einem besseren Verständnis der involvierten physikalischen Effekte. Dies wiederum trägt zur Spezifizierung von Entwurfsregeln bei, welche in Zukunft eine verbesserte Zuverlässigkeit bringen.

Eine der härtesten elektrischen Belastungen ist die elektrostatische Entladung (ElectroStatic Discharge, ESD). So eine Belastung kann einzelne Halbleiterbauelemente oder sogar den ganzen Mikrochip zerstören. Da dieser Vorgang oft von spezifischen Begleiterscheinungen (z.B. Ausbildung von Strompfaden) geprägt ist, ist ein experimenteller Zugang zum internen Verhalten der zu untersuchenden Bauteile von großem Interesse. Das transiente interferometrische Abbildungsverfahren (Transient Interferometric Mapping, TIM) ist ein leistungsstarkes Werkzeug, welches bereits mehrere Male das interne Bauteilverhalten aufgezeigt hat. Es erlaubt die Abbildung von Temperatur- und freien Ladungsträger Konzentrationsverteilungen und daher die Verfolgung von Strompfaden in den untersuchten Bauelementen. Während der letzten Jahre ist dieses interferometrische Abbildungsverfahren herangereift und kann nun zu komplexen Analysen des Bauteilverhaltens und auch zur Überprüfung von Bauelementmodellen herangezogen werden. Diese Methode wird in dieser Arbeit zur Analyse von Halbleiterbauelementen, welche in einer Smart Power Technologie (SPT) hergestellt sind, angewendet.

Zuerst wird die TIM-Methode zur detaillierten Analyse der SPT ESD-Schutzelemente angewendet. Drei Layout Variationen der npn Struktur wurden unter zwei ESD Belastungstypen (HBM und CDM) untersucht. In diesen Bauelementen wurden die ESD-Robustheit, die Homogenität des Stromflusses und die Lokalisierung von heißen Flecken und Fehlerstellen experimentell untersucht. Weiters wurden die Unterschiede im Betriebsverhalten von Bauelementen mit variiertem Layout analysiert. Die experimentellen Ergebnisse wurden mit den zweidimensionalen Bauteilsimulationen verglichen. Eine weitere Klasse der auf ESD-Robustheit untersuchten Bauelemente sind die Smart Power DMOS Transistoren. Die Ausbildung von Strompfaden in der aktiven Zone der Bauelemente und deren Entwicklung während eines Stress-Impulses ist im Detail analysiert worden. Es wurde experimentell nachgewiesen, dass sich die Strompfade in den Bauelementen bewegen. Mit Hilfe von zwei- und dreidimensionalen Bauteilsimulationen konnte der Mechanismus der Bewegung von Strompfaden verstanden werden.

Zum Abschluss wurde die TIM-Methode zur Untersuchung von DMOS-Transistoren im Millisekundenbereich verwendet. Die Eignung dieser Methode für solch Untersuchungen wurde erstmals aufgezeigt. Es wurde gezeigt, dass zur Analyse des Bauteilverhaltens in dieser Zeitskala es von Vorteil ist, nicht die gemessene physikalische Größe (Phasenverschiebung) sondern die zweidimensionale Leistungsdichte ( $P_{2D}$ ) zu verwenden, welche von der gemessenen Phasenverschiebung berechnet werden kann. Es wurde die Genauigkeit des  $P_{2D}$ -Bestimmungsvorganges analysiert. Der Vorgang der Berechnung der Oberflächentemperatur konnte ebenso beschrieben werden.

# Abstract

Assurance of the reliability of semiconductor integrated circuits (ICs) is one of the main tasks of the IC design. There is a broad spectrum of thermal, mechanical or electrical stresses, which influence the reliability of semiconductor devices. In order to identify various failure mechanisms it is therefore necessary to perform testing of the devices. Detailed analysis of the results afterwards yields an understanding of the effects involved. This in return helps in specification of design rules, which will in future guarantee an improved reliability.

One of the most severe electrical stresses is the electrostatic discharge (ESD). Such stress can be fatal for a semiconductor device, or even for the whole IC. As this event can be accompanied with specific phenomena, e.g. occurrence of current filaments, experimental access to the internal behaviour of investigated device is of great interest. Transient interferometric mapping (TIM) technique is a powerful tool, which already proved its capability to do the task several times. It allows mapping of the thermal and free-carrier concentration distributions and thus pursuing of the current paths in the studied devices. During previous years the technique has matured into the state that it can be applied for complex analysis of the device behaviour as well as for the verification of device models. The technique is utilised in this work for the analysis of semiconductor devices built within the smart power technology (SPT) process.

Foremost the TIM technique is applied for detailed analysis of the SPT ESD protection devices. Three layout variations of the npn structure are investigated under two types of ESD stress: HBM- and CDM-like. The ESD robustness, homogeneity of the current flow, localisation of hot spots and failures are experimentally studied in the devices. Differences in operation of the devices with varied layout are analysed. The experimental results are compared with the 2-dimensional device simulation.

Another class of studied devices are the smart power DMOS transistors, whose ability to withstand the ESD stress is investigated. The formation of current filaments in the device active area and their evolution during a stress pulse is in detail analysed. It is experimentally proved that the filaments move in the device. With a help of 2D and 3D device simulation the mechanism of filament movement is understood.

Finally the TIM technique is applied for the investigation of DMOS transistor operation in the *ms* time scale. Applicability of the technique for such kind of study is presented for the first time. It is demonstrated that for analysis of device behaviour in this time scale it is beneficial not to use the measured physical quantity (phase shift), but the 2D power dissipation density ( $P_{2D}$ ), which can be extracted from the experimentally obtained phase shift. Precision of the  $P_{2D}$  extraction procedure is analysed. Perspective way for calculation of surface temperature is discussed as well.

# Content

| Kurzfassung                                                       | ii |

|-------------------------------------------------------------------|----|

| Abstract                                                          | iv |

| Introduction                                                      | 1  |

| 1.1 Motivation                                                    | 1  |

| 1.2 Electrostatic discharge (ESD)                                 | 3  |

| 1.2.1 ESD models                                                  |    |

| 1.2.2 ESD protection                                              | 6  |

| 1.2.3 ESD testing                                                 | 9  |

| 1.3 Smart power DMOS                                              |    |

| Experimental Technique                                            | 17 |

| 2.1 Transient interferometric mapping technique                   | 17 |

| 2.1.1 Operating principle                                         | 17 |

| 2.1.2 Extraction of physical quantities from the phase shift      | 19 |

| 2.1.3 Experimental set-ups for Transient Interferometric Mapping  | 20 |

| 2.1.3.1 Dual beam Michelson interferometric set-up                | 20 |

| 2.1.3.2 Scanning heterodyne interferometric set-up                | 22 |

| 2.1.3.3 2-dimensional holographic set-up                          | 23 |

| 2.2 Sources of electrical stress                                  | 26 |

| 2.3 Auxiliary optical characterisation techniques                 | 28 |

| 2.3.1 Optical beam induced current (OBIC)                         |    |

| 2.3.2 Emission microscopy                                         | 28 |

| BCD ESD protection devices under TLP and vf-TLP stress            | 29 |

| 3.1 Devices                                                       | 29 |

| 3.2 Characterisation under DC operating conditions                | 30 |

| 3.3 Characterisation under pulsed (ESD-like) operating conditions | 34 |

| 3.3.1 Electrical characterisation                                 | 34 |

| 3.3.2 Optical characterisation                                    | 39 |

| 3.3.2.1 Device <i>D1</i>                                          | 39 |

| 3.3.2.2 Device <i>D2</i>                                          | 48 |

| 5.5.2.5 Device D5                                                 | 55 |

| 3.4 Summary                                                       | 54 |

| Investigation of the smart power DMOS transistors                 | 55 |

| 4.1 Investigation of the VDMOS devices under ESD-like stress                                                                                                                                                                                                               | 55  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1.1 Devices under study                                                                                                                                                                                                                                                  | 55  |

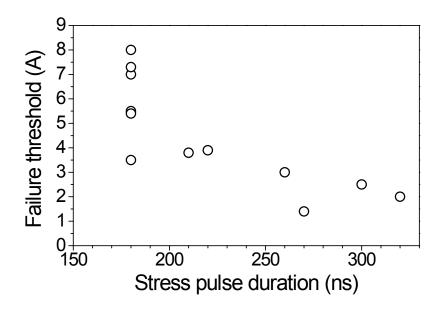

| 4.1.2 Electrical characterisation                                                                                                                                                                                                                                          | 58  |

| <ul> <li>4.1.2 Electrical characterisation</li> <li>4.1.3 Optical characterisation in the breakdown regime (the parasitic BJT transistor is not active)</li> <li>4.1.4 Optical characterisation in the snapback regime (the parasitic BJT transistor is active)</li> </ul> | 62  |

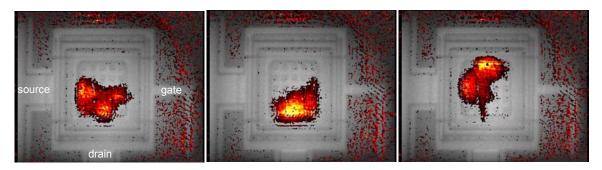

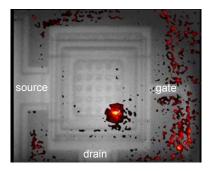

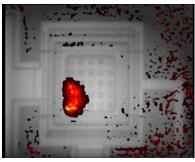

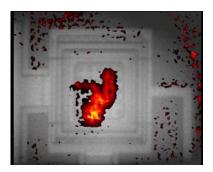

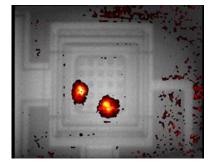

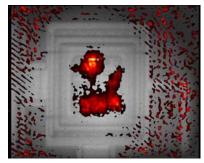

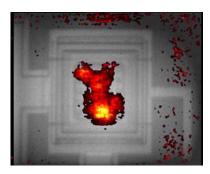

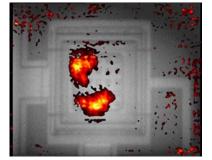

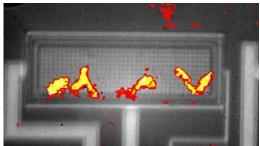

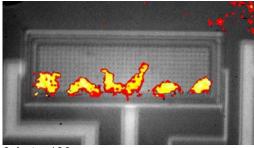

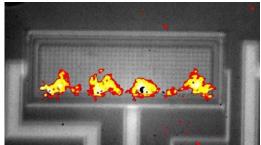

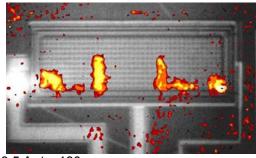

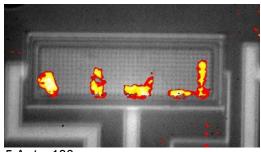

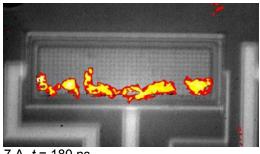

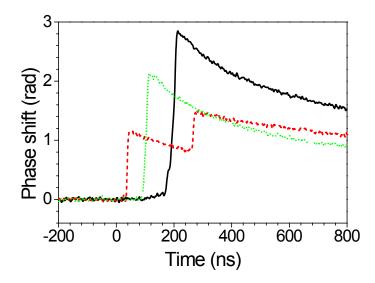

| 4.1.4 Optical characterisation in the snapback regime (the parasitic BJT transistor is active)                                                                                                                                                                             | 64  |

| 4.1.5 Discussion                                                                                                                                                                                                                                                           | 71  |

| 4.1.6 Failure analysis                                                                                                                                                                                                                                                     | 75  |

| 4.1.7 Summary                                                                                                                                                                                                                                                              | 81  |

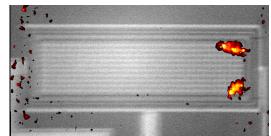

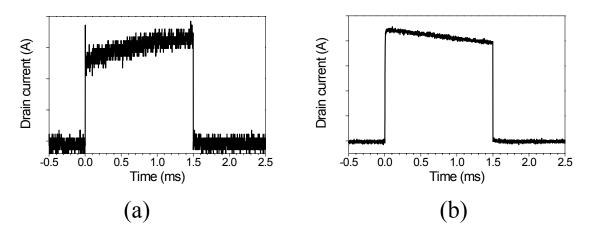

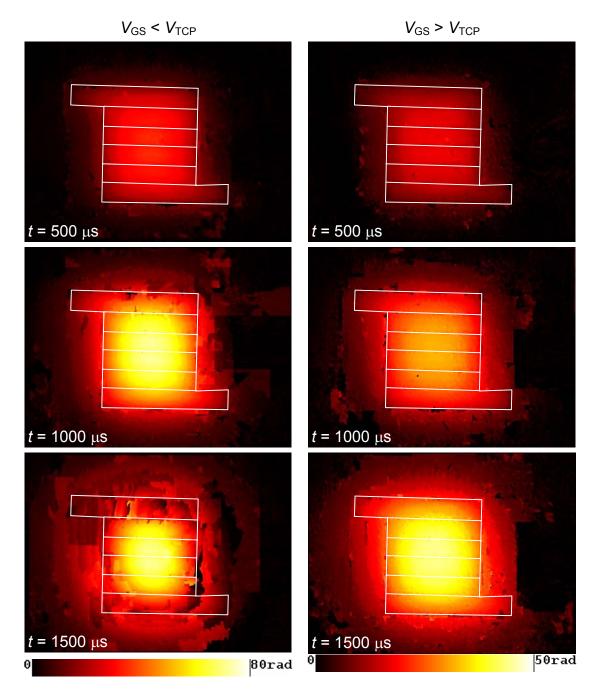

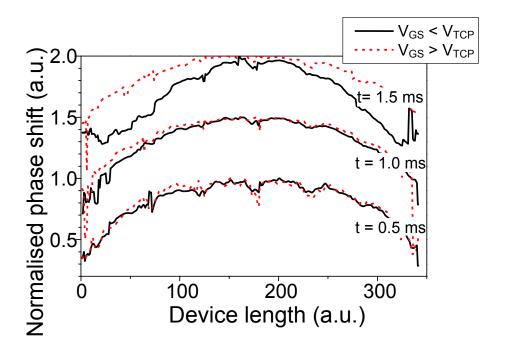

| 4.2 Investigation of the DMOS devices in the thermal SOA region                                                                                                                                                                                                            | 82  |

| 4.2.1 Experimental results                                                                                                                                                                                                                                                 | 82  |

| 4.2.2 Extraction of the heat-dissipating sources                                                                                                                                                                                                                           | 85  |

| 4.2.3 Extraction of temperature from the phase shift                                                                                                                                                                                                                       | 89  |

| 4.2.4 Summary                                                                                                                                                                                                                                                              | 92  |

| Summary                                                                                                                                                                                                                                                                    | 93  |

| Appendix A                                                                                                                                                                                                                                                                 | 95  |

| Bibliography                                                                                                                                                                                                                                                               | 98  |

| List of Symbols                                                                                                                                                                                                                                                            | 105 |

| List of Acronyms                                                                                                                                                                                                                                                           | 107 |

| List of Publications                                                                                                                                                                                                                                                       | 108 |

| Acknowledgement                                                                                                                                                                                                                                                            | 110 |

| Biography                                                                                                                                                                                                                                                                  | 111 |

# Chapter 1 Introduction

## 1.1 Motivation

During the history of integrated circuit (IC) technology, the primary attention was mostly placed on advance in the signal processing and data storage capabilities of logic circuits. Besides this branch of electronic "brains", which is nowadays dominated by CMOS technology, a branch of semiconductor devices dedicated to a control of energy was developing too. These power devices were initially realised as discrete components. When a need to improve their performance, functionality, versatility and reliability arose, they were integrated with logic circuitry and power ICs appeared. The power ICs were first implemented using bipolar technologies, until a new power IC class based on the MOS technology emerged in the mideighties [Andr86]. It was named *Smart Power Technology* (SPT).

Smart power technology ICs serve as an interface between the control logic and a load [Bali91]. They integrate into one chip power devices for regulation of the output power flow, analogue circuitry necessary to drive and protect the power devices, and logic circuitry for communication with a control unit. These functions are implemented using mixed bipolar (analogue), CMOS (logic) and DMOS (power) process. Smart power technology is therefore often addressed as *BCD technology*. SPT devices nowadays penetrate into all areas, where discrete power devices have been used, and they are available for wide range of voltage and current ratings [Bali91]. These devices can be found e.g. in video, telecommunication, multimedia or power supply applications, as well as in the automotive electronics.

Whatever is expected from a smart power IC, in the first place it should be reliable [Mura97]. In addition to an elementary functionality of a device under regular operating conditions, smart power ICs must also withstand potential electrical, thermal or mechanical stress, because they often operate in a severe environment. For example devices installed in the engine compartment of a car can be exposed to temperatures from -40°C up to 175°C

and vibrations up to 50g [Berg02]. Designers have to take into account also variety of electrical stresses, which threaten smart power devices during their lifetime [Casi04].

One of the major electrical threats, which a device has to face, is the electrostatic discharge (ESD) [Amer95]. Single high-current short-duration pulse occurring for instance when a charged person touches a pin of an integrated circuit can cause its fatal degradation. This becomes even more critical with the downscaling of characteristic sizes of microelectronic devices, which are more vulnerable to over-voltage and over-current events. It is therefore inevitable to protect ICs against such events. Protection is usually realised by means of special class of devices dedicated to this purpose. In case of power devices the latest trend is to design them as self-protecting, which is solution that saves space on the chip and consequently reduces the production costs.

Apart from the ESD, which in general constitutes hazard to any element of any IC, power elements of the smart power chips can be additionally encountered with situations, which leads to critical operation conditions: short circuit, unclamped inductive switching (UIS), or so-called load dump are few of them. These operating conditions cause excess power dissipation in the device, which should be capable to withstand it until the fault is recognised by control logic and the power supply is switched off.

Semiconductor companies are forced to evaluate robustness of their devices against the above-mentioned stresses. Each new technology generation brings new process steps, which also influence reliability of devices, and therefore testing has to be performed systematically. It is usually electrical and mostly intended for the determination of maximum allowable stress level a device can withstand (e.g. in case of the ESD it is the maximum applicable pre-charge voltage, typically few kV). However, in many cases it is advantageous to reveal internal behaviour of a device under critical operating conditions. This is useful for the understanding of device physics, it helps in the verification of device models, and afterwards shorten time and reduces costs, which is needed to optimise devices for required robustness.

This work presents the results of experimental investigation of internal behaviour of SPT devices studied by means of the Transient Interferometric Mapping (TIM) technique. This technique was presented as powerful tool for investigation of internal device operation under ESD-like operating conditions in the past [Furb00, Poga02c]. It represents a unique possibility of non-invasive and non-contacting mapping of thermal and free carrier dynamics in the semiconductor devices. The main focus of the thesis is placed on the study of ESD phenomenon (time scale in order of hundreds of ns), but the internal device behaviour is studied also in longer time scales (ms).

The thesis is divided into four chapters:

Chapter 1 provides an introduction into the ESD problem. Three standardised ESD models are briefly mentioned, concept of the ESD protection of ICs is introduced, and methods

for testing of the ESD robustness are explained. The reliability issues of power DMOS transistor is shortly introduced too, because a significant part of this thesis is devoted to this device.

Chapter 2 introduces the TIM technique. The principle of TIM is explained together with the physical meaning of measured quantity. The chapter additionally provides description of three TIM set-ups, which were used during the experiments. Technical parameters of these set-ups are given as well as their applicability for investigation of various phenomena. The chapter closes with a short description of two auxiliary optical techniques that were also used.

Chapter 3 provides detailed analysis of internal behaviour of SPT ESD protection devices under two types of ESD stress: HBM- and CDM-like. Electrical and optical experimental techniques were used to study the ESD robustness, homogeneity of the current flow, and locations of hot spots and failures in the devices. Behaviour of the devices under the HBMand CDM-like stress is compared and differences in the operation of the devices with varied layout are analysed. A 2-dimensional device simulation supports the experimental results.

Chapter 4 is dedicated to the power DMOS transistors and it is divided into two main parts: The first part deals with the investigation of smart power DMOS devices exposed to the ESD-like stress. Experimentally observed inhomogeneous current distribution is explained with a help of 2- and 3-dimensional device simulations. The second part of this chapter presents results of the experimental characterisation of large DMOS transistor in the ms time scale under short-circuit operating conditions. Applicability of the TIM technique for such kind of investigation is studied, and hints for the extraction of physical quantities from the measured one are provided.

## **1.2 Electrostatic discharge (ESD)**

#### 1.2.1 ESD models

When the need to systematically investigate the ESD phenomenon arose in the past, it was foremost necessary to describe different real-world conditions under which such events occur. This led to a specification of three ESD models, which are nowadays used for testing of ESD robustness of semiconductor devices.

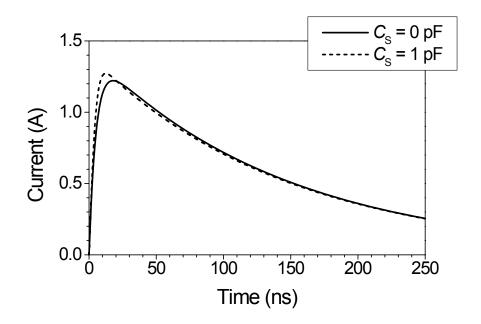

*Human body model* (HBM) describes the situation, when a contact of charged human body with a grounded device causes an electrostatic discharge. Typical HBM discharge waveform is shown in Fig. 1.1: the rise time of the discharge current pulse is about 10 ns,

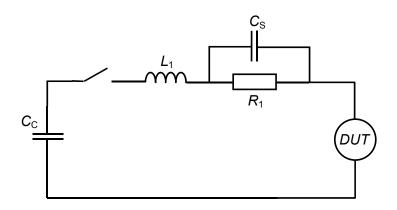

and the decay time is around 150 ns. The equivalent circuit of this model is shown in Fig. 1.2. It consists from 100 pF charged capacitor  $C_{\rm C}$ , which models the capacity of human body, and from 1.5 k $\Omega$  resistor ( $R_1$ ), which models the skin resistance. The parasitic inductance  $L_1$  determines the rise time of the pulse. Final waveform depends on the parasitic stray capacitance  $C_{\rm S}$  of the discharge resistor  $R_1$  and interconnects (cf. Fig. 1.1).

Fig. 1.1: An example of the HBM discharge waveform through 0  $\Omega$  load. The charging voltage is 2 kV. The shape of the waveform is influenced by the parasitic element  $C_s$ , cf. Fig. 1.2.

Fig. 1.2: Equivalent circuit for modelling of the HBM and MM discharge waveforms.  $C_{\rm C}$  is the charged capacitance; and  $R_1$  is the resistance of the discharge path. Elements  $L_1$  and  $C_{\rm s}$  are parasitic components, which influence the final waveform of the discharge current as it is shown in Fig. 1.1 and 1.3.

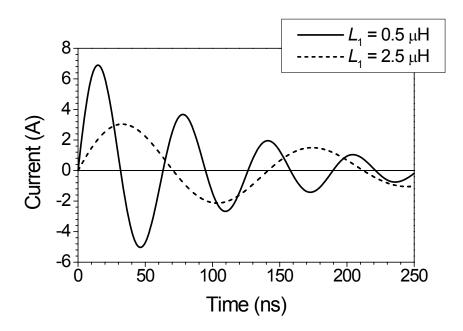

Fig. 1.3: An example of the MM discharge waveform through 0  $\Omega$  load. The charging voltage is 400 V. Shape of the waveform is influenced by the parasitic element  $L_1$ , cf. Fig. 1.2.

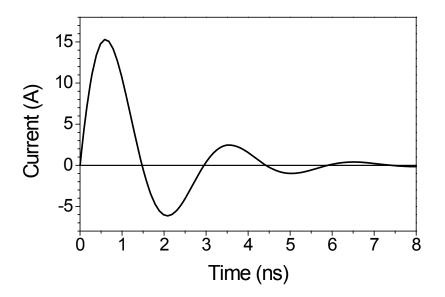

Fig. 1.4: An example of the CDM discharge waveform. The charging voltage is 1 kV.

*Machine model* (MM) describes discharges with a low-resistance path, such as may occur during mechanical handling of semiconductor devices. The equivalent circuit is a modification of the HBM circuit (Fig. 1.2), with the capacitor  $C_{\rm C}$  of value 200 pF and ideally zero discharging resistance  $R_1$  (in reality  $R_1 > 0$ ). The final waveform of the discharge current, which is shown in Fig. 1.3, again depends on the parasitic components.

*Charged device model* (CDM) becomes important with increasing fabrication automation. It describes discharge of a charged device to the ground. Device can be charged for instance during a transportation over conveyor belt, and discharged through the metallic arm of a robot touching it. Such ESD event leads to very short (< 10 ns) pulses with short rise time (< 1 ns) and extremely high currents (> 10 A). An example of the CDM discharge waveform is shown in Fig. 1.4.

The HBM and MM events cause excess heat dissipation, and therefore usually induce a thermal damage inside the semiconductor structure, mostly in the pn junctions. The CDM stress is too short to significantly increase temperature in the device. It usually causes the breakdown of gate oxide in an IC. The reason is that the self-inductance and the fast ramprate of this type of pulse induce a high voltage drop in the metal interconnects.

#### 1.2.2 ESD protection

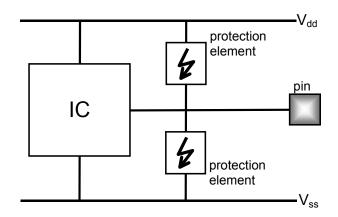

The demand to confront with the ESD phenomenon gave rise to a special class of devices dedicated purely to the ESD protection. They protect each pin of an IC as it is schematically shown in Fig. 1.5. Protection devices have two basic functions: to clamp the voltage at the input pin to a level below the gate oxide breakdown, and to limit the current to a level below the damage threshold of the junction being protected. Protection device should be effectively

Fig. 1.5: Principal scheme of the ESD protection of an IC.

and fast triggered, when an ESD event occurs. On the other hand, it should be "invisible" during normal operating conditions, i.e. it should not degrade the DC and AC characteristics of the protected IC.

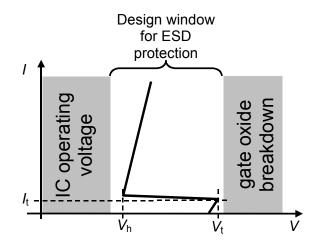

I-V characteristics of the protection element has to fit into the design window between the power supply voltage (lower limit) and the gate oxide breakdown voltage (upper limit), as it is shown in Fig. 1.6. Typically these devices have S-shaped I-V characteristics: they are activated at high voltage ( $V_t$  – trigger voltage), and once turned-on, they switch into low voltage regime ( $V_h$  – holding voltage). The latter limits the heat dissipation in the protection device and thus increases its current handling capability.

Fig. 1.6: Design window in the I-V plane of an IC, which is used by ESD protection element.

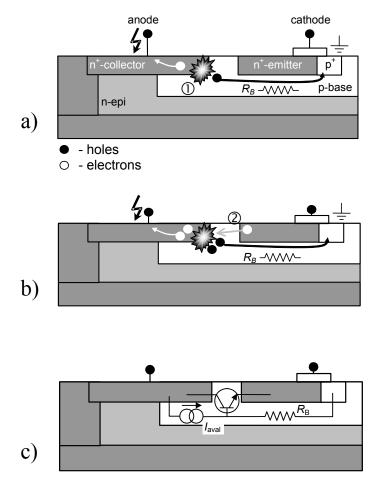

Operating principle of the ESD protection device with the *S*-shaped I-V characteristics can be explained on example of the npn structure, which internal behaviour is in detail investigated in Chapter 3. This device is realised as the lateral npn transistor with short-circuited base and emitter (Fig. 1.7(a)). When a positive voltage is applied to the anode,  $n^+$ -collector/p-base junction is reverse-biased. Eventually the breakdown voltage is reached. The impact ionisation starts, and electron-hole pairs are generated in the junction (O in Fig. 1.7(a)). The avalanche current is given by

$$I_{\text{aval}} = (M-1) \cdot I_{\text{in}},\tag{1.1}$$

where  $I_{in}$  is the current incident into the high electric field region; and M is the multiplication coefficient described by empirical formula

Fig. 1.7: Operating principle of the lateral npn ESD protection device: (a) breakdown; (b) turn-on of the BJT; (c) equivalent circuit of the device.

$$M = \frac{1}{1 - \left(\frac{V}{V_{\rm BD}}\right)^n},\tag{1.2}$$

where V is the voltage applied to the device;  $V_{BD}$  is the breakdown voltage; and n is the fitting parameter, which depends in general on the type of considered junction. At this moment  $I_{in}$  is only composed of the junction saturation current  $I_{C0}$ . The multiplication coefficient M is large, because  $I_{aval} = I_{ESD}$  (the ESD stress current).

The electrons generated by impact ionisation are attracted towards the n<sup>+</sup>-collector (anode), and generated holes flow through the p-base toward the p<sup>+</sup> cathode contact. Resistance of the p-base region  $R_B$  is non-zero, and the hole current  $I_h$  causes a voltage drop, which starts to forward-bias the p-base/n<sup>+</sup>-emitter junction:

$$V_{\rm BE} = I_{\rm h} \cdot R_{\rm B}. \tag{1.3}$$

If the hole current reaches certain level, the junction is opened, and the emitter starts to inject electrons into the base (@ in Fig. 1.7(b)). This is the moment, when the bipolar npn transistor is turned on. The electrons injected from the emitter and flowing to the collector contribute to the impact ionisation in the avalanching collector junction and  $I_{in}$  becomes

$$I_{\rm in} = I_{\rm C} \approx I_{\rm C0} \cdot \exp(V_{\rm BE}/V_{\rm T}), \qquad (1.4)$$

where  $I_{\rm C}$  is the bipolar collector current; and  $V_{\rm T} = kT/q$  is the thermal voltage. Therefore

$$I_{\text{aval}} = (M-1) \cdot I_{\text{C}}.$$

(1.5)

Thus, to sustain the same total ESD current, the multiplication coefficient M of the impact ionisation can be decreased. This leads to a sudden drop of the voltage at the device (from  $V_t$ to  $V_h$ , cf. Fig. 1.6), which is observed in the I-V characteristics. This effect is called *snapback*. After the snapback device operates in the low voltage, high current regime, with roughly constant differential resistance. The latter is mainly determined by the series resistance of involved device regions.

Fig. 1.7(c) shows a simple equivalent circuit of the ESD protection device [Amer96, Lim97]: current source  $I_{aval}$  represents the current generated in the avalanching n<sup>+</sup>-collector/p-base junction.

#### 1.2.3 ESD testing

Commercially available ESD testers, generally based on the equivalent circuits of the ESD models (cf. section 1.2.1), are usually employed for ESD testing. Besides them the Transmission Line Pulse (TLP) technique [Malo85] and the very-fast Transmission Line Pulse (vf-TLP) technique [Gies98] are often utilised in the HBM and CDM time domains, respectively. These two techniques provide rectangular pulse stressing with appropriate rise time and duration, and into some extent emulate the real life ESD stress. They are also used in the experimental investigations presented in this thesis.

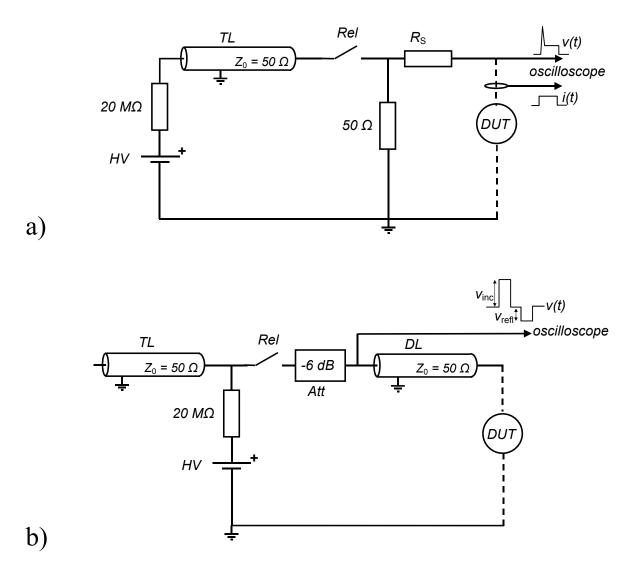

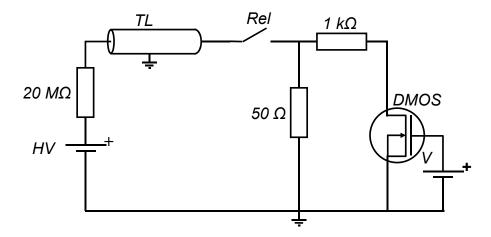

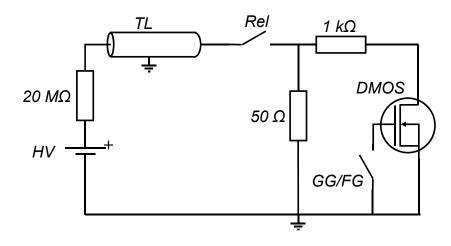

Fig. 1.8 shows the principal scheme of the TLP and vf-TLP set-ups. In both cases the output pulse is generated by discharge of a charged transmission line (*TL*). The length of the output pulse  $t_p$  is set by the length of the transmission line:  $t_p = 2l_{TL}/v$ , where  $l_{TL}$

is the length of the transmission line; and v is the speed of electromagnetic wave propagating in the *TL*. Typically 100 ns TLP pulses are used for the HBM-like testing and up to 10 ns vf-TLP pulses are used for the CDM-like testing.

The TLP operates in the constant current regime. This is achieved by appropriate choice of the series resistance  $R_S$  (Fig. 1.8(a)), which guarantees that voltage at the device under test

Fig. 1.8: Principal scheme of (a) the constant current transmission line pulser (TLP); and (b) the constant impedance very-fast TLP (vf-TLP): HV is the high-voltage source; TL is the transmission line; Rel is the relay switch;  $R_S$  is the voltage to current transformer; DUT is the device under test; v(t) and i(t) are the voltage and current probes, respectively; Att is the attenuator; and DL is the delay line.

(*DUT*) is much smaller than the voltage at  $R_{\rm S}$ . In such case the output current level can be calculated as

$$I_{\rm TLP} \approx \frac{1}{2} \frac{V_{\rm charge}}{R_{\rm S}}.$$

(1.6)

The 50  $\Omega$  resistor serves as matching for the transmission line to avoid the back reflections. Voltage and current probes are used to monitor respective quantities on the oscilloscope.

The current source TLP output pulse is distorted during the first few nanoseconds because of reflections from parasitics, which are introduced e.g. by current and voltage probes. This is the reason, why the constant current TLP is not suitable for investigation in the CDM time domain. The vf-TLP set-up intended for such type of investigation is therefore designed to be 50- $\Omega$  matched. It is based on the principle of time domain reflectometry. The stress pulse propagates towards the *DUT* where it is partially absorbed and partially reflected. The actual voltage and current at *DUT* can be calculated from the amplitudes of the incident and reflected pulses, which are separated in time by the delay line *DL* (Fig. 1.8(b)):

$$V_{\rm DUT} = a V_{\rm inc} + \frac{1}{a} V_{\rm refl}, \qquad (1.7a)$$

$$I_{\rm DUT} = \frac{aV_{\rm inc} - \frac{V_{\rm refl}}{a}}{Z_0},$$

(1.7b)

where  $V_{inc}$  and  $V_{refl}$  are incident and reflected pulses measured by the voltage probe, respectively; *a* is the attenuation of the delay line; and  $Z_0$  is the characteristic impedance of the system (50  $\Omega$ ). Accurate estimation of the delay line attenuation *a* is necessary for the precise determination of the  $V_{DUT}$  and  $I_{DUT}$ . The 6 dB attenuator (*Att*, Fig. 1.8(b)) is placed between *TL* and *DL* to suppress repeated stressing of the *DUT* due to multiple reflections.

...

Although the CDM testing cannot be directly substituted by the vf-TLP one [Gies98, Stad03], and there still exists a controversy, whether the results obtained by the TLP correlate with the HBM testing [Muss96, Bart00, Stad97, Note98], both TLP and vf-TLP enables investigation of devices under reproducible conditions. These techniques allow construction of the high current I-V characteristics, determination of failure thresholds and together with failure analysis techniques provide valuable information about the weak points of investigated device.

### **1.3 Smart power DMOS**

Double-diffused MOS (DMOS) transistor is the power MOSFET [Bali96a]. It is the most common power device used in low voltage (< 100 V) applications nowadays [Bali96b]. Power MOSFETs have replaced power bipolar transistors in the past, because they offer several advantages: higher switching speed, no DC driving current consumption, and thermally stable operation in a wide interval of drain currents are the most important ones [Mura96]. Consequently, the DMOS has been chosen as the power device for the Smart Power Technology ICs.

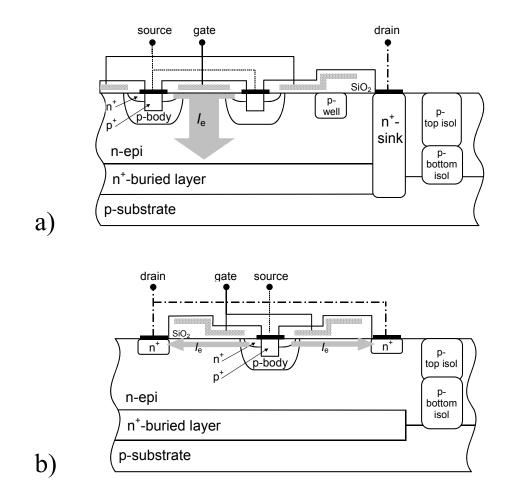

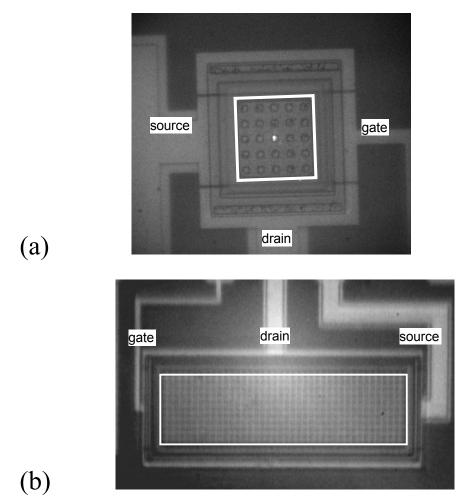

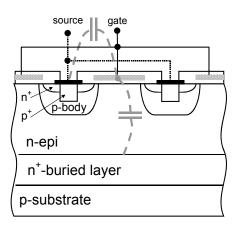

Fig. 1.9 shows the cross-sections of two basic n-channel DMOS devices designed within the SPT process: vertical DMOS (VDMOS, Fig. 1.9(a)) and lateral DMOS (LDMOS, Fig. 1.9(b)). It has to be mentioned at this place that the layout of an SPT IC is influenced by requirement to electrically isolate individual devices on the chip. This is inevitable to avoid any unwelcome crosstalk between different parts of the IC, e.g. from the power device (DMOS) to the control logic circuits (CMOS). Usual solution of the problem is junction isolation, which is also the case of devices studied in the present work. Another possibility is the silicon on insulator (SOI) process [Mura96]. The smart power technology process utilising junction isolation starts with a p-doped substrate, into which highly doped  $n^+$ -buried layer and  $p^+$ -bottom isolation are implanted. Afterwards a low doped n-epitaxial layer (n-epi) is grown, where a  $p^+$ -top isolation is implanted, and an n<sup>+</sup>-sinker contacting the buried layer is realised. Thereafter the DMOS block is processed: The p-body and  $n^+$ -source regions of the device are diffused to the n-epi self-aligned through the gate-polysilicon openings. The channel length results from the differential outdiffusion of the p- and n-dopants. This process is origin of the name "double-diffused". Note also that the channel length is independent of the lithography process accuracy. The p-body and  $n^+$ -source are short-circuited to establish a fixed potential of the p-body region during device operation. The main distinction between the VDMOS and LDMOS devices is in the current flow path. In the VDMOS the buried layer serves as drain and the electron current flows vertically through the epi layer (grey arrow in Fig. 1.9(a)). On the other hand in the LDMOS the drain is realised by shallow n<sup>+</sup>-region and current flows laterally along the silicon top surface (grey arrows in Fig. 1.9(b)).

The presented structures of the power DMOS transistor are the very basic ones, and there exist variety of improved concepts of the transistor, which uses RESURF principle or trenches. These are summarised e.g. in [Deni04a].

The most important characteristics of the DMOS transistor are voltage-blocking capability and on-resistance. When the device is off, i.e. the gate-to-source voltage is smaller

Fig. 1.9: Principal cross sections of SPT DMOS transistors: (a) vertical and (b) lateral. The displayed devices are n-channel ones. The electron current flow paths are also indicated.

than the threshold voltage ( $V_{\rm GS} < V_{\rm TH}$ ), the drain-to-source voltage  $V_{\rm DS}$  is supported by the reverse biased n-epi/p-body junction. To achieve high breakdown voltage, doping of the n-epi layer has to be low. However, resistance of this layer substantially influences the on-resistance of device, which is desired to be as small as possible. From such point of view it is beneficial to increase the n-epi doping. It is one of the main goals of the DMOS design to handle this trade-off between the breakdown voltage and on-resistance as well as to optimise the DMOS layout with respect to these parameters [Char96, Efla97, Mora97, Plik97, Kim01].

Another important characteristic of the DMOS is so-called *Safe Operating Area* (SOA). This term defines an interval of the drain current  $I_{DS}$  and drain-to-source voltage  $V_{DS}$ , where the device can operate without suffering damage [Howe02]. As an ultimate operating limit of the DMOS is usually taken the turn-on of the parasitic bipolar transistor inherent in any MOSFET device [Yilm89]. This transistor is formed by the source (emitter)/body (base)/drain (collector) structure. It is turned on, when a sufficient

voltage develops across the body/source (= base/emitter) junction. The junction is forward biased due to a current flow through the body region. This current can be supplied by impact ionisation, thermal generation, or it is the displacement current in case a voltage pulse with high rise-time is applied to the drain (so-called dV/dt-triggering [Bali96a]).

Depending on the mechanism, which dominantly controls the device operation, one can distinguish between *electrical* SOA and *thermal* SOA:

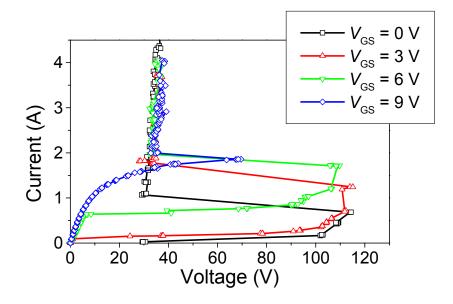

ESD pulse runs DMOS transistor into the avalanche breakdown and activity of the parasitic BJT is controlled by the impact ionisation. DMOS device sensitivity to the ESD is therefore determined by its electrical SOA. The triggering of the parasitic BJT is in this case basically the same process as the one described for the npn ESD protection device in chapter 1.2.2. However, when the DMOS gate is biased,  $I_{DS}$  provides additional carriers into the avalanching region and Eq. (1.5) in general extends into a form

$$I_{\text{aval}} = (M - 1)(I_{\text{C}} + I_{\text{DS}}),$$

(1.8)

which could lead to the reduction of parasitic BJT triggering voltage  $V_t$ . Nevertheless, this effect takes place only if the  $I_{DS}$  path crosses the high electric field region [Merg00].

There are several approaches how to protect DMOS device against ESD:

- by external protection device, e.g. SCR parallel with the device [Duvv94];

- using Zener diodes clamp, which provides the gate bias to open the channel [Duvv97, Mene00];

- the device is intended to be self-protecting [Part02, Kawa02, Deni04b]. This approach requires knowledge of the physical effects, which governs behaviour of the device during an ESD event.

The turn-on of the parasitic BJT in the self-protected DMOS transistor leads to an electrical instability related to the existence of the negative differential resistance (NDR) region in the I-V characteristic. This instability can induce a strongly inhomogeneous current flow [Howe01, Stei03, Deni04b]. In case of the LDMOS devices, the snapback is often destructive [Bess02]. This originates from the triggering of the lateral npn structure accompanied by formation of the high electric field region at the Si/SiO<sub>2</sub> interface, where a thermal degradation takes place soon [Bess02]. On the other hand VDMOS have proved to be more robust against ESD, because in this case the high electric field region is localised in the bulk [Deni04b, Moen04].

The thermal SOA of DMOS transistors becomes more important and consequently gets more into the field of view of device designers in recent years, when the downscaling of the devices led to a growth of the power dissipation density. Significant rise of temperature

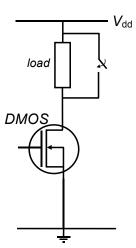

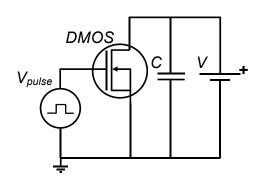

Fig. 1.10: Circuit representation of the DMOS transistor operation with short-circuited load.

in the device, which is caused by self-heating during high energy pulses, can alone induce a failure of the device. An example of such high energy stress is the short circuit operation, when the whole power supply voltage appears on the DMOS (Fig. 1.10). However, it is important to note that the thermal SOA is not inevitably linked with the turn-on of the parasitic BJT [Deni04a].

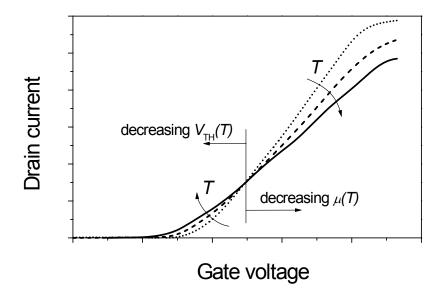

The DMOS thermal SOA is considerably affected by the operating point dependent power distribution [Breg99, Deni04c]. Fig. 1.11 demonstrates dependence of the DMOS transfer characteristic on temperature. While at higher gate voltages the drain current decreases with increasing temperature (temperature coefficient of  $I_{DS}$  is negative), at small gate voltages total drain current increases with increasing temperature (temperature coefficient of  $I_{DS}$  is negative). This behaviour is caused by two competing mechanisms, which affect the device operation at elevated temperatures [Doln92].

The first mechanism is a decrease of the free-carriers mobility with increasing temperature according to the formula [Doln92]

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{-2.5}.$$

(1.9)

This effect is dominant at high current regime and leads to a homogenisation of current flow in the device, thus making its operation thermally stable.

The second mechanism is a decrease of the threshold voltage  $V_{\text{TH}}$  with increasing temperature.  $V_{\text{TH}}$  of MOS transistor is given by:

$$V_{\rm TH} = \phi_{\rm ms} + 2\phi_{\rm f} + \frac{\sqrt{4\varepsilon q N_{\rm max} \phi_{\rm f}}}{C_{\rm ox}} - \frac{Q_{\rm ox}}{C_{\rm ox}}, \qquad (1.10)$$

where  $\phi_{MS}$  is the work function difference between metal and semiconductor;  $\phi_f$  is Fermi potential;  $\varepsilon$  is the semiconductor permitivity;  $N_{max}$  is maximum net doping concentration of the p-body region;  $C_{ox}$  is the gate oxide capacity; and  $Q_{ox}$  is the charge trapped in the gate oxide. The temperature dependence of Eq. (1.10) comes mostly from the temperature dependence of Fermi potential:

$$\phi_{\rm f} = \frac{kT}{q} \ln \left( \frac{N}{n_{\rm i}(T)} \right), \tag{1.11}$$

where k is Boltzman constant and  $n_i$  is the intrinsic concentration. The effect of the threshold voltage decrease with increasing temperature is dominant at small gate and high drain voltage regime, and it leads to a thermally unstable operation, which could limit the thermal SOA [Breg99, Cons99, Spirit02, Deni04c].

When the two effects mentioned above are compensated, the drain current of the DMOS is temperature independent. This point is called *temperature compensation point* (TCP).

In summary it is therefore of great interest to follow the dynamics of power dissipation distribution and temperature rise in the DMOS transistor in order to understand effects limiting its thermal SOA.

Fig. 1.11: Dependence of the DMOS transfer characteristics on the temperature.

# Chapter 2 Experimental Technique

## 2.1 Transient interferometric mapping technique

#### 2.1.1 Operating principle

The transient interferometric mapping (TIM) technique is based on a probing of localised variation of the refractive index n due to a temperature change [Bert90, Stur92] and/or a change in the free-carrier concentration [Sore87, Schr78]. The refractive index changes are probed by a laser beam and they are detected as a phase shift using an interferometer.

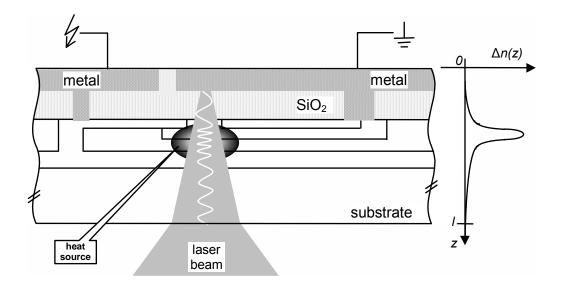

In the interferometer the laser beam is split into reference and probe branches. The probe beam, which propagates in the probe branch, enters the investigated device from the backside, and it is reflected by top metal (Fig. 2.1). Its phase profile is modified due to a spatial and time variation of the refractive index  $\Delta n(x,y,z,t)$  caused by electrical stress. The reflected probe beam interferes with the reference beam, which propagates in the reference branch and which is reflected by the reference mirror. Optical detector detects the resulting interference signal. Any phase shift introduced into the probe beam is hence transferred into an intensity change of the detector signal.

The operating principle of the TIM technique requires the probing laser beam not to be absorbed in the sample. Wavelength of the laser source used for investigation of silicon devices is therefore chosen to be around 1.3  $\mu$ m, which is beyond absorption edge of the silicon. This choice is also determined by availability of laser sources.

The measured phase shift  $\Delta \varphi$  is given by [Seli97]

$$\Delta \varphi(x, y, t) = 2 \cdot \frac{2\pi}{\lambda} \int_{0}^{t} \Delta n(x, y, z, t) dz , \qquad (2.1)$$

Fig. 2.1: Operating principle of the transient interferometric mapping technique: self-heating in the investigated structure gives rise to a local variation of the refractive index in the hot area (see the  $\Delta n(z)$  distribution along the probe beam path on the right hand side of the figure). This causes a phase modulation of the probing laser beam.

where  $\lambda$  is the free-space wavelength of the laser beam; *l* is the thickness of semiconductor substrate; and  $\Delta n(x,y,z,t) = n(x,y,z,t) \cdot n_0(x,y,z,t)$  is the local change of refractive index from its initial value  $n_0(x,y,z,t)$  when *DUT* in not stressed, to a new value n(x,y,z,t) when *DUT* is under electrical stress.

The total refractive index change  $\Delta n(x,y,z,t)$  can be in the first approximation divided into thermal ( $\Delta n_{\text{th}}$ ) and free carrier ( $\Delta n_{\text{fc}}$ ) contributions:

$$\Delta n(x, y, z, t) = \Delta n_{\rm th}(x, y, z, t) + \Delta n_{\rm fc}(x, y, z, t).$$

(2.2)

Thermally induced change of refractive index can be expressed using the thermo-optical coefficient dn/dT, which is positive and for silicon in the first approach temperature independent:

$$\Delta n_{\rm th}(x, y, z, t) = \frac{dn}{dT} \Delta T(x, y, z, t)$$

(2.3)

The value of dn/dT for silicon is approximately  $1.9 \times 10^{-4}$  K<sup>-1</sup> for 1.3 µm wavelength [MCau94].

Free-carrier induced refractive index change is negative for increasing concentration, and it can be expressed as the sum of electron  $(\Delta n_{\rm fc,e})$  and hole  $(\Delta n_{\rm fc,h})$  contributions

$$\Delta n_{\rm fc}(x, y, z, t) = \Delta n_{\rm fc,e}(x, y, z, t) + \Delta n_{\rm fc,h}(x, y, z, t) =$$

$$= k_{\rm e} \Big[ N_{\rm e}^{\alpha}(x, y, z, t) - N_{\rm e0}^{\alpha}(x, y, z, t) \Big] + k_{\rm h} \Big[ N_{\rm h}^{\beta}(x, y, z, t) - N_{\rm h0}^{\beta}(x, y, z, t) \Big]$$

(2.4)

where  $N_{\rm e}(x,y,z,t)$  and  $N_{\rm h}(x,y,z,t)$  are the electron and hole concentrations during electrical stress, and  $N_{\rm e0}(x,y,z,t)$ ,  $N_{\rm h0}(x,y,z,t)$  are the corresponding quantities in the steady state conditions. The parameters  $k_{\rm e}$ ,  $k_{\rm h}$ ,  $\alpha$  and  $\beta$  are coefficients obtained from the fitting of experimental data [Sore87].

#### 2.1.2 Extraction of physical quantities from the phase shift

From the Eqs. (2.1) and (2.2) follows that the total phase shift can be calculated as

$$\Delta\varphi(x,y,t) = \Delta\varphi_{\rm th}(x,y,t) + \Delta\varphi_{\rm fc}(x,y,t), \qquad (2.5)$$

where  $\Delta \varphi_{\text{th}}(x,y,t)$  and  $\Delta \varphi_{\text{fc}}(x,y,t)$  are the thermal and free carrier components of the total phase shift, respectively. The latter one can be sometimes neglected, especially when high power is dissipated in the investigated device or in case of longer time scales. If also temperature independent thermo-optical coefficient dn/dT and volume specific heat  $c_v$  is assumed, the phase shift  $\Delta \varphi$  is found to be directly proportional to the 2-dimensional energy density  $E_{2D}$  stored inside the semiconductor [Poga02a], which can be written in a form:

$$E_{\rm 2D}(x,y,t) = \frac{\lambda c_v}{4\pi} \frac{1}{\frac{dn}{dT}} \Delta \varphi(x,y,t) \approx 0.88 \cdot \Delta \varphi(x,y,t) \text{ [nJ.}\mu\text{m}^{-2}\text{]}.$$

(2.6)

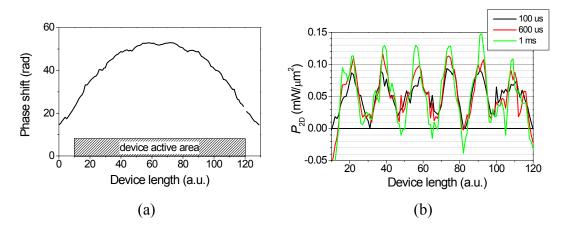

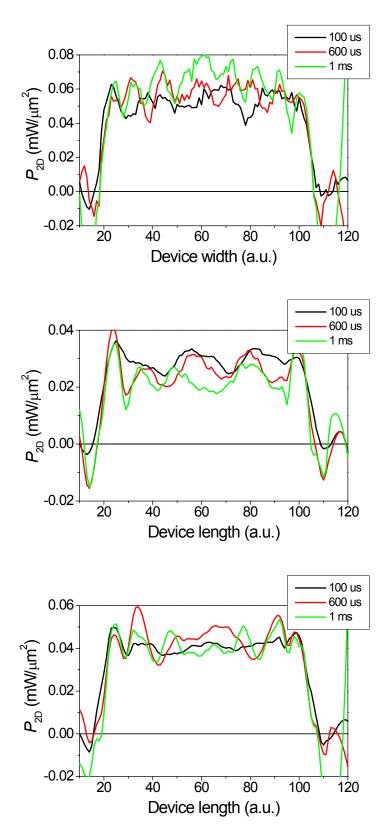

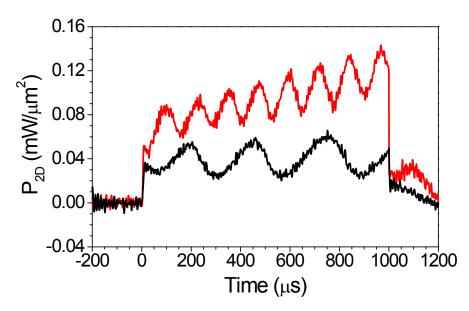

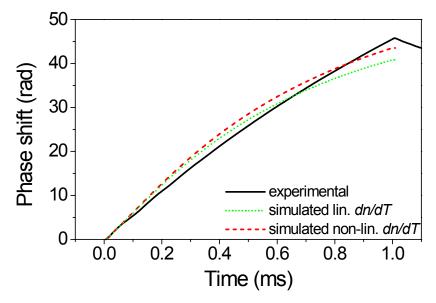

The temperature induced phase shift is a memory quantity, i.e. it reflects the complete history of power dissipation in a device, not the instantaneous one. Hence, all experimental results have to be carefully analysed to uncover any possible dynamic changes in the heat dissipation. It is therefore advantageous to extract the instantaneous 2-dimensional power dissipation density  $P_{2D}$  from the phase shift [Poga02b]:

$$P_{\rm 2D}(x,y,t) = \frac{\lambda}{4\pi \frac{dn}{dT}} \left\{ c_v \frac{\partial \Delta \varphi(x,y,t)}{\partial t} - \kappa \left[ \frac{\partial^2 \Delta \varphi(x,y,t)}{\partial x^2} + \frac{\partial^2 \Delta \varphi(x,y,t)}{\partial y^2} \right] \right\} + j_{\rm th,z}(x,y,0,t), \quad (2.7)$$

where  $\kappa$  is the temperature independent heat conductivity, and  $j_{\text{th},z}(x,y,0,t)$  is the normal component of the heat flow density vector at the device top surface. The latter represents the thermal power transferred from silicon to top device layers and it can be in some cases neglected.

#### 2.1.3 Experimental set-ups for Transient Interferometric Mapping

Following part provides a brief description of three set-ups, which were used for transient interferometric mapping within the frame of this work.

#### 2.1.3.1 Dual beam Michelson interferometric set-up

Dual-beam Michelson interferometric set-up [Dube03] provides information about the time evolution of the phase shift at two places on a *DUT*.

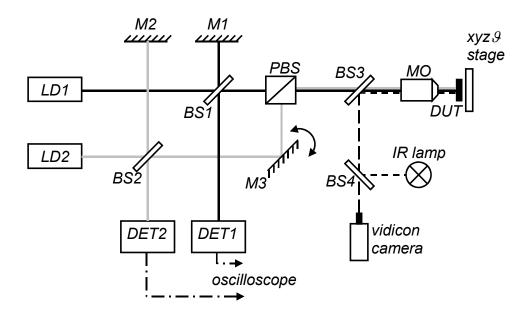

Fig. 2.2 shows the set-up schema. It is a combination of two independent Michelson interferometers. Two DFB laser diodes (*LD1*, *LD2*) generate linearly polarised light beams of 1.3  $\mu$ m wavelength. The laser beams are split to the reference and probe beams by two beamsplitters (*BS1* and *BS2*). The probe beams are focused onto different locations of the *DUT* by a microscope objective (*MO*). The laser beam positions on the *DUT* can be visualised using an IR *vidicon camera* and the distance between them can be changed by rotation of the mirror *M3*. Minimum laser spot diameter is about 2  $\mu$ m, which determines maximum space resolution. Reference mirrors *M1* and *M2* mounted on piezo-controlled *x*-stages allow precise adjustment of the reference branches lengths for maximum sensitivity. Interference signals from respective interferometers are detected by two InGaAs photo-detectors (*DET1*, *DET2*) with 1 GHz bandwidth. The detectors are chosen as a compromise between the large bandwidth and acceptable signal-to-noise ratio. Time resolution of the set-up is 0.4 ns. Output signal from the detectors is measured by a fast digital oscilloscope.

Fig. 2.2: Schematic diagram of the dual-beam Michelson interferometric set-up: LD1 and LD2 are the laser diodes; M1 and M2 are the reference mirrors; BS1 - BS4 are the beam splitters; DET1 and DET2 are the optical detectors; PBS is the polarising beam splitter; M3 is the mirror for adjustment of laser beam separation on the DUT; and MO is the microscope objective.

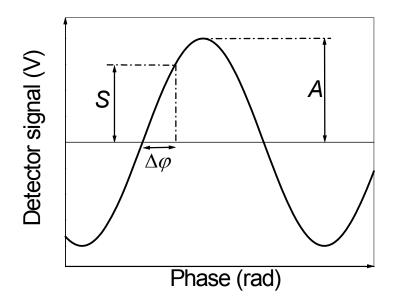

When an electrical stress is applied to the *DUT* and a refractive index change occurs at the position probed by the laser beam, a sinusoidal signal s(t) is measured. It can be generally expressed as

$$s(t) = B(t) \sin[\Delta \varphi(t) + \varphi_0], \qquad (2.8)$$

where B(t) is the amplitude of the sinusoidal signal;  $\Delta \varphi$  is the phase shift due to electrical stress; and  $\varphi_0$  is set by the reference mirror. No DC component is present in the measured signal, because AC output of the detector is used. The phase shift is not large in most cases ( $\Delta \varphi < \pi/4$ ), therefore the working point of the interferometer is usually adjusted to a "half-fringe" ( $\varphi_0 = 0$ ), where the sensitivity to the optical path changes is the highest. The absolute phase shift can be then calculated as

$$\Delta \varphi = \arcsin\left(\frac{S}{A}\right) \approx \frac{S}{A},\tag{2.9}$$

where the meaning of the symbols is clear from Fig. 2.3. To improve the signal to noise ratio, averaging over several pulses is used, if the signal is reproducible.

Fig. 2.3: Detector signal vs. phase shift dependence in the dual-beam Michelson interferometric set-up.

Because of good time resolution, the set-up is applied for investigations of very fast transients, e.g. for investigation of trigger delays in ESD protection devices under vf-TLP stress [Bych03]. The employment of two laser beams also enables simultaneous investigation of activity at two different places on a device.

#### 2.1.3.2 Scanning heterodyne interferometric set-up

Scanning heterodyne interferometric set-up [Furb98] provides information about the time evolution of phase shift at certain position alike the previous set-up, but the present one additionally allows automatic scanning for investigation of the phase shift distribution along x and/or y direction.

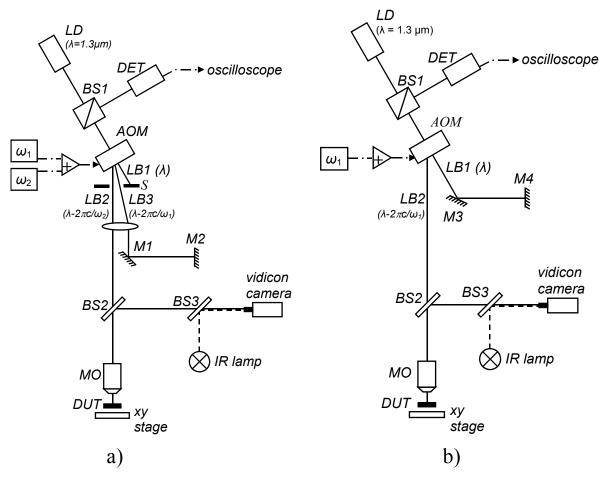

Fig. 2.4 shows two utilised configurations of the set-up: so-called "slow" (Fig. 2.4(a)) and "fast" (Fig. 2.4(b)). They differ in the time resolution and signal-to-noise ratio parameters (cf. Table 2.1). Laser beam of 1.3  $\mu$ m wavelength is generated by a DFB laser diode (*LD*). It is split into the probe and reference beams by an acoustic optic modulator (*AOM*), which is driven by one ("fast" configuration) or two ("slow" configuration) frequency generators ( $\omega_1$ ,  $\omega_2$ ).

Fig. 2.4: Schematic diagram of the scanning heterodyne interferometric set-up used for TIM: (a) "slow" configuration; and (b) "fast" configuration: *LD* is the laser diode; *DET* is the photodetector; *BS1* – *BS3* are the beam splitters; *AOM* is the acoustic optic modulator;  $\omega_1$  and  $\omega_2$  are the frequency generators; *LB1* – *LB3* are the refracted laser beams; *S* is the slit; *M1* – *M4* are the mirrors; *MO* is the microscope objective and *DUT* is the device under test.

Besides splitting, the AOM also shifts the frequency of refracted beam(s). The reflected probe and reference beams interfere in the photo-detector (*DET*). The detector output signal, which is measured by an oscilloscope, is the heterodyne beat signal, and can be expressed as

$$s(t) = s_{\rm r}(t) + s_{\rm p}(t) + s_{\rm d}(t) + 2\sqrt{s_{\rm r}(t)s_{\rm p}(t)} \cdot \cos(2\Delta\omega t + \Delta\varphi(t)), \qquad (2.10)$$

where  $s_r(t)$ ,  $s_p(t)$  and  $s_d(t)$  are the time dependent amplitudes of the reference beam, probe beam and possible signal disturbances, respectively;  $2\Delta\omega$  is the beating frequency; and  $\Delta\varphi(t)$ is the phase shift due to electrical stress. The beating frequency is given by the difference in frequencies of the reference and probe beam:

- for "slow" configuration:  $2\Delta\omega = 2(\omega_1 \omega_2)$ ,

- for "fast" configuration:  $2\Delta\omega = 2\omega_1$ ,

where  $\omega_1$  and  $\omega_2$  are the frequencies of the signals that drive the *AOM*. The beating frequency is higher in case of the "fast" configuration, and consequently a faster photo-detector is used. This brings the advantage of better time resolution, however this configuration suffers worse signal-to-noise ratio. Important parameters of both variations of the set-up are summarised in Table 2.1:

|                    | SET-UP CONFIGURATION |                    |  |

|--------------------|----------------------|--------------------|--|

|                    | "slow" (Fig. 2.4a)   | "fast" (Fig. 2.4b) |  |

| beating frequency  | 6 MHz                | 137 MHz            |  |

| detector bandwidth | 28 MHz               | 198 MHz            |  |

| time resolution    | 15 ns                | 3 ns               |  |

| space resolution   | 1.5 μm               | 1.5 μm             |  |

| S/N –ratio         | ~ 60                 | ~ 14               |  |

Table 2.1: Technical parameters of the two variations of the scanning heterodyne interferometric set-up

When long pulses (in  $\mu s$  – ms time scale) are applied to the *DUT*, the "slow" configuration of set-up is used, and the detector signal is first mixed with a local oscillator to mix down the beating signal frequency. Only then is the mixer output signal measured by the oscilloscope:

$$s(t) = s_0 \cos[(2\Delta\omega - \omega_{LO})t + \Delta\varphi + \varphi_{LO}], \qquad (2.11)$$

where  $s_0$  is the amplitude of the mixer output signal; and  $\omega_{LO}$  and  $\varphi_{LO}$  are the frequency and phase of local oscillator signal, respectively. The  $\varphi_{LO}$  is typically chosen to be zero.

Measurement with the scanning heterodyne set-up is fully computer controlled. The sample is mounted on a stepping motor controlled *xy*-stage of 0.1  $\mu$ m precision. Several stress pulses per scan position are usually applied to improve the signal-to-noise ratio. The phase shift is extracted from the heterodyne signal by home made software, which uses Fast-Fourier Transformation method [Litz03].

This set-up is of general-purpose. It can be used for investigation of temperature and free-carrier dynamics in the devices [Blah03a], and also allows to follow different device activity modes in case of trigger instabilities [Poga01a, Poga03a]. However, it suffers the disadvantage of necessity of multiple stressing, which constitutes the threat of gradual

degradation of the investigated device. The set-up is not applicable for investigation of destructive phenomena.

#### 2.1.3.3 2-dimensional holographic set-up

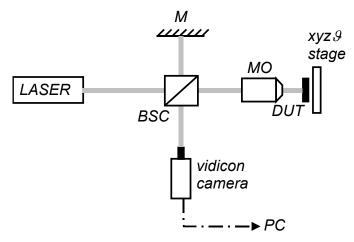

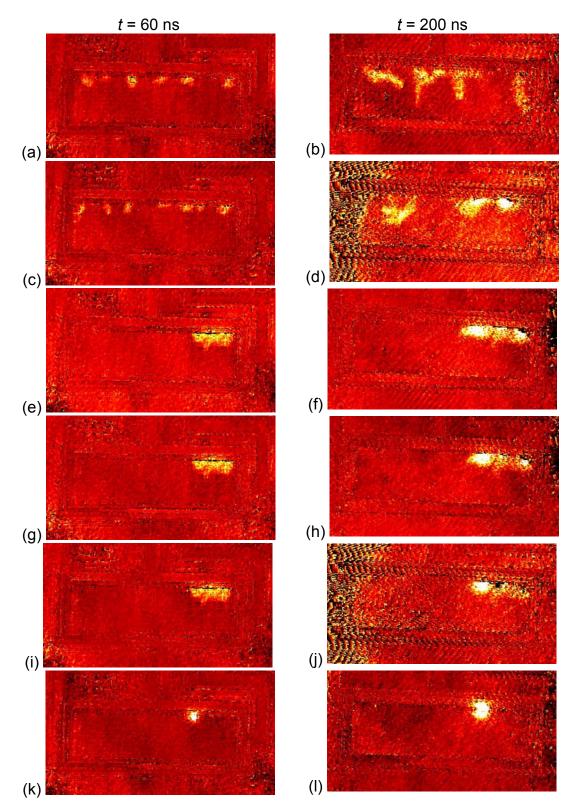

The 2-dimensional holographic set-up [Poga02c] provides information about 2-dimensional phase shift distribution in one or two time instants during a single stress pulse.

Fig. 2.5: Schematic diagram of the 2-dimensional holographic set-up: *M* is the reference mirror; *BSC* is the beam-splitting cube; *MO* is the microscope objective; and *DUT* is the device under test.

The principal set-up schema is shown in Fig. 2.5. An optical parametric oscillator (*OPO*) pumped by a Q-switched YAG:Nd laser is used as the pulsed light source (*Laser*). The wavelength of the laser beam can be adjusted in a wide range of VIS and NIR spectrum (410 – 2000  $\mu$ m), but usually 1.25  $\mu$ m is used, because the light of this wavelength is not absorbed in the silicon even at high temperatures, and maximum output energy of the laser pulse is reached at this wavelength. The laser beam is split into the probe and reference beams in the beam splitting cube (*BSC*). The probe beam is collimated by the microscope objective (*MO*) in such way that it illuminates the whole *DUT*. The beam diameter can be adjusted in the range of 100  $\mu$ m – 5 mm, which defines the field of view. Interference of the reference and probe beams transforms the phase profile into intensity changes, which have the form of interference fringes. These are visualised using an IR *vidicon camera* and saved in a computer for further processing. Generally the recorded fringe pattern *I*(*x*,*y*) can be expressed as

$$I(x,y) = A(x,y) + B(x,y) \cdot \cos[k \, r + \Phi(x,y)]$$

(2.12),

where A(x,y) is the background signal; B(x,y) is the amplitude of the fringes;  $\Phi(x,y)$  is the total phase shift profile; **k** is the wave vector of the laser beam; and **r** is the spatial vector.  $\Phi(x,y)$ carries not only information about the phase shift induced by electrical stress, but also information about the phase shift induced by device topology. The latter is eliminated during the phase shift extraction procedure, which is based on the Fast Fourier Transformation method [Dube04a].

Timing is critical for the optimal operation of the laser source used in this set-up. It is therefore fully computer controlled<sup>1</sup>. Stress pulse is synchronised with the laser flash, and user can specify the time instant within the stress pulse, when the image is taken (laser flashes). The time resolution of the imaging is determined by the laser pulse duration, which is 5 ns. Recent improvement of the set-up, employing the second laser and camera, enables to record two fringe images taken in two different time instants during a single stress pulse [Dube04b].

Thanks to the ability of the set-up to record the phase shift profile in the whole device active region during a single stress pulse, it is optimally suited for investigation of non-repeatable events, such as the pulse-to-pulse instabilities [Deni03] or destructive events [Poga03a]. The set-up extension by the second laser flash makes it also suitable for extraction of the 2D power dissipation density  $P_{2D}$  [Dube04b].

### 2.2 Sources of electrical stress

During the transient interferometric mapping of devices studied under ESD-like stress conditions, a home-made TLP or vf-TLP pulsers were used. The parameters of these two pulsers are listed in Table 2.2. In addition to them, a commercial pulse generator DEI SV-4000 was used for electrical stressing with the 2-dimensional holographic set-up. The reason for that is that the instrument can be electronically controlled and it allows exact timing. This is not possible with the TLP and vf-TLP pulsers, because their relay switches have a high jitter. However, the rise time of 20 ns and minimal pulse length of 180 ns of the SV-4000 pulser does not allow direct comparison with the 100 ns TLP. On the other hand, this pulse generator allows study of the rise time effects when compared with the 150 ns TLP with 1 ns rise time [Litz01].

The above mentioned pulsers were also used for measurements of the high current I-V characteristics. This measurement is fully computer controlled. Voltage at the device and current

<sup>&</sup>lt;sup>1</sup> The control routines for automatic measurement sequence were programmed within the framework of this thesis.

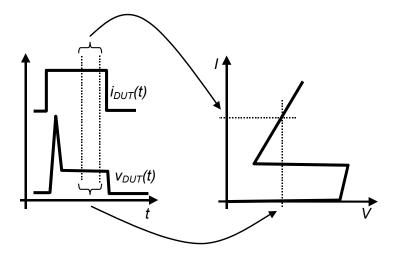

through the device are visualised on a fast digital oscilloscope and saved in a computer. Points of the I-V characteristics are obtained by averaging of the voltage and current values over appropriately chosen time interval within the stress pulse (Fig. 2.6). After each stress level the leakage current is measured, which gives information about the leakage current evolution with the stress current level and enables to determine failure threshold.

|                | TLP            | vf-TLP | DEI SV-4000     |       |

|----------------|----------------|--------|-----------------|-------|

| Pulse duration | 100 ns, 300 ns | 10 ns  | 180 ns – 250 ns |       |

| Rise time      | 1 ns           | 0.5 ns | 20 ns           |       |

| Rs             | 1 kΩ           | -      | 1 kΩ            | 500 Ω |

| Output (max.)  | 4 A            | 8 kV   | 4 A             | 8 A   |

Table 2.2: Parameters of the pulse generators used for electrical stressing during the transient interferometric mapping.

Fig. 2.6: Extraction of the high current I-V characteristics using the TLP or vf-TLP technique.

## 2.3 Auxiliary optical characterisation techniques

#### 2.3.1 Optical beam induced current (OBIC)

Optical beam induced current (OBIC) technique is widely used in the failure analysis, where it helps to identify the exact position of a damage in semiconductor devices [Beau02, Beau03]. Nevertheless, it can be similarly used for identification of high electric field regions [Poga02d], for which sake it was also employed in this work.

The scanning heterodyne set-up is adopted for the OBIC measurements. The same DFB laser diode is used as a source of light, and the laser beam is focused on a *DUT* from the backside. The device is reverse-biased. Any optically generated carriers are separated by electrical field, and cause a change of the measured current. This can be afterwards related to the illuminated position. Sensitivity of the technique can be increased, when the device is biased close to the breakdown voltage, where the impact ionisation increases the measured current.

#### 2.3.2 Emission microscopy

This technique involves recording of the electroluminiscence resulting from the transformation of electrical energy into light [Debo94]. In this work it is mainly used in the failure analysis (localisation of damages) [Russ99, Teh97]. It is sensitive to junction and dielectric related failures. It can be also used for identification of high electric fields or investigation of homogeneity of current flow in the studied devices [Blah02].

Emission microscopy can be performed in any of the TIM set-ups presented in this chapter. DUT is reverse biased and current through the device results in the electroluminiscence. This is observed using IR vidicon camera with spectral sensitivity of 400 nm – 1600 nm. The region, where the electroluminiscence takes place, localises the damage.

# Chapter 3

# BCD ESD protection devices under TLP and vf-TLP stress

This chapter presents results of the experimental investigation of low voltage BCD ESD protection devices, which are intended for protection of power supply pins and low voltage I/O pins of Smart Power Technology ICs. These devices are built in the 0.8  $\mu$ m BCD4 technology of STMicroelectronics.

Single finger devices were tested in the HBM time domain, and proved a very high ESD robustness [Blah02]. Furthermore few layout variations, which included structural and dimensional changes, were investigated. Additional investigations were performed in the CDM time domain using the vf-TLP [Blah04].

### 3.1 Devices

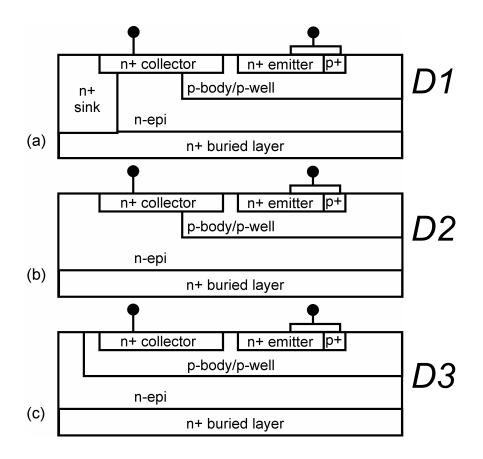

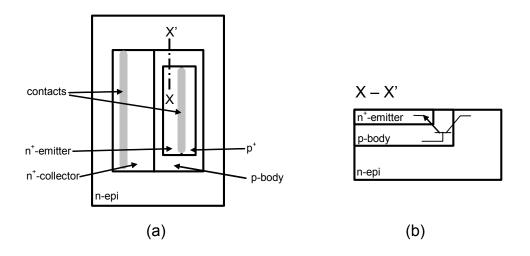

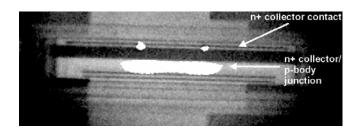

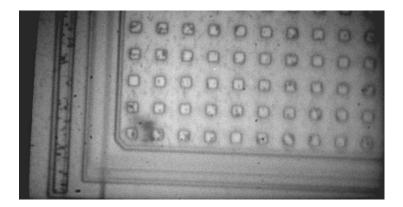

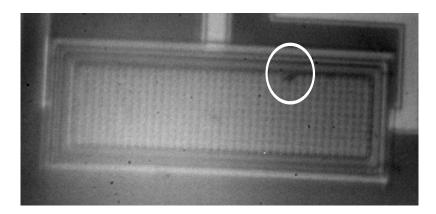

Fig. 3.1 shows simplified cross-sections of three structural variations of the tested devices. These are basically npn bipolar transistors with short-circuited base and emitter. All devices are fabricated on a p-substrate with the n<sup>+</sup>-buried layer implantation. Then the n-epi layer is grown where the p-body/p-well is diffused. Two shallow n<sup>+</sup> regions create collector and emitter. The first type of the device (referred as device *D1*) has an n<sup>+</sup>-sinker, which connects the buried layer with the n<sup>+</sup>-collector (Fig. 3.1(a)). Devices with this layout have widths 50  $\mu$ m, 100  $\mu$ m, 170  $\mu$ m and 300  $\mu$ m. Next kind of the investigated device is without sinker (Fig. 3.1(b), referred as device *D2*). The last device type is also without sinker, and in addition the collector region is isolated from the n-epi layer by an extension of the p-body region (Fig. 3.1(c), referred

Fig. 3.1: Principal cross sections of the investigated devices: (a) with sinker -D1; (b) without sinker -D2; and (c) with isolated collector -D3.

as device D3). The width of the two latter types of the devices is 170  $\mu$ m. During the experiments, positive polarity stress was applied to the collector, and the emitter/base contact was kept grounded.

Operating principle of the devices has been explained in the Section 1.2.2.

## 3.2 Characterisation under DC operating conditions

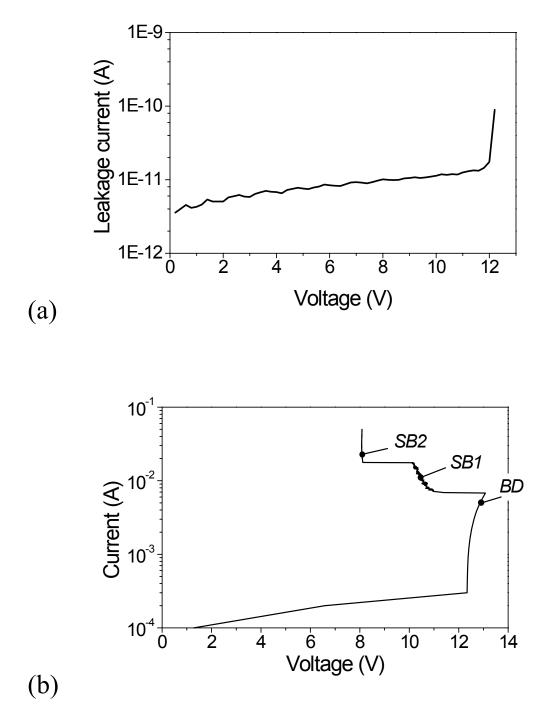

Figure 3.2(a) shows the DC I-V characteristics of the device DI, measured by a semiconductor parameter analyser operating in the voltage-source mode. Leakage current (the n<sup>+</sup>-collector/p-body junction reverse current) of the device is in order of few pA. The breakdown voltage is about 12 V. Fig. 3.2(b) shows the DC I-V characteristics measured in the current source mode. In this case the characteristics exhibit double-snapback behaviour.

Fig. 3.2: DC I-V characteristics of the device D1 ( $w = 170 \mu m$ ) measured (a) in the voltage-source mode; and (b) in the current-source mode.

The first snap-back is reached at about 7 mA, and the voltage on the device drops down from about 13 V to about 10 V. When the current level increases further (above 18 mA), the second snapback is observed, and the voltage drops down to 8 V.

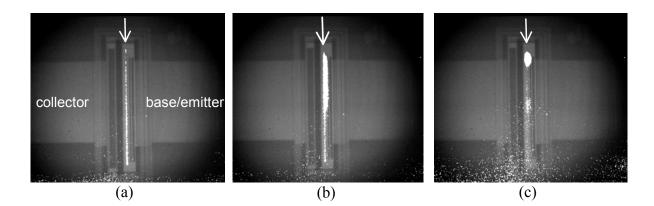

Behaviour of the device in various operating points marked in Fig. 3.2(b) (*BD*, *SB1* and *SB2*) was studied by DC emission microscopy in the constant current mode. Fig. 3.3 shows the emission microscopy images, which are aligned with the device backside infrared image. When the device operates in the breakdown (point *BD* in Fig. 3.2(b)), the light is emitted from the place marked by an arrow (Fig. 3.3(a)). The latter indicates position of the lateral edge of the collector junction. This implies that the impact ionisation is dominant in the lateral part of the n<sup>+</sup>-collector/p-body junction and not in the vertical one. This is consistent with a high electric field expected at this place due to high curvature of the n<sup>+</sup>-collector region there. Uniform emission along the whole width of the device also shows that the current flows quite

Fig. 3.3: DC emission microscopy images of the device D1 ( $w = 170 \mu$ m) taken at various working points marked in Fig. 3.2(b): (a) *BD*; (b) *SB1*; and (c) *SB2*. The arrow marks the lateral edge of the collector junction.

homogeneously in this regime. Transition to the first snapback (working point *SB1* in Fig. 3.2(b)) leads to a widening of the emitting area toward the  $n^+$ -emitter, indicating the triggering of the bipolar transistor (Fig. 3.3(b)). The emission also indicates that the transistor is turned on only in a part of the device. Finally, the second snapback in the I-V characteristics (point *SB2* in Fig. 3.2(b)) is accompanied with a collapse of the light emitting region into one device corner (Fig. 3.3(c)), which is caused by the self-heating.

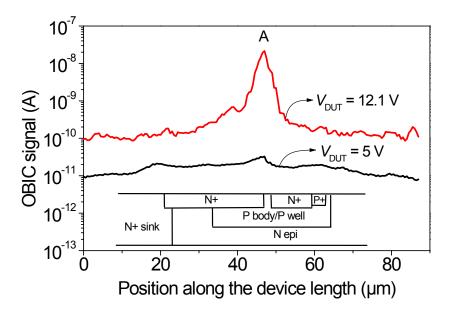

In order to identify high electric field regions, an OBIC scan along the device length was performed at voltages below the breakdown (V = 5 V) and in the breakdown (V = 12.1 V).

Fig. 3.4: OBIC signal distribution along the length of the device D1 (w = 170  $\mu$ m) biased to V = 5 V and V = 12.1 V

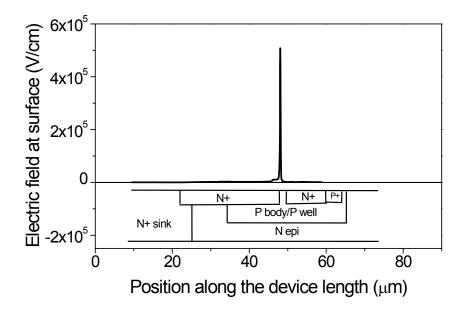

Fig. 3.5: Simulated surface electric field distribution along the length of the device *D1*. (Courtesy of L. Zullino)

Fig. 3.4 shows the OBIC signal as a function of the position along the device length. The signal exhibits a peak at the lateral collector/body junction ("A" in Fig. 3.4), indicating the highest electric field in this point. No other pronounced high electric-field regions are found. This result agrees with the EMMI observations in the breakdown operating point (Fig. 3.3(a)) and also with the simulated surface electric field distribution, which is shown in Fig. 3.5. Note that the OBIC signal in the breakdown (V = 12.1 V) is more than two orders of magnitude higher than at V = 5 V. Origin of the OBIC signal under this below band-gap light excitation (wavelength of the laser is  $\lambda = 1.3 \mu m$ ) is attributed to the photo-carrier generation processes related with the energy tails in the highly doped n<sup>+</sup>-collector region and/or with the intrinsic states at the Si/SiO<sub>2</sub> interface. The amplified OBIC signal in the breakdown originates from the avalanche multiplication of the photo-generated carriers in the region with a high electric field.

## 3.3 Characterisation under pulsed (ESD-like) operating conditions

## 3.3.1 Electrical characterisation

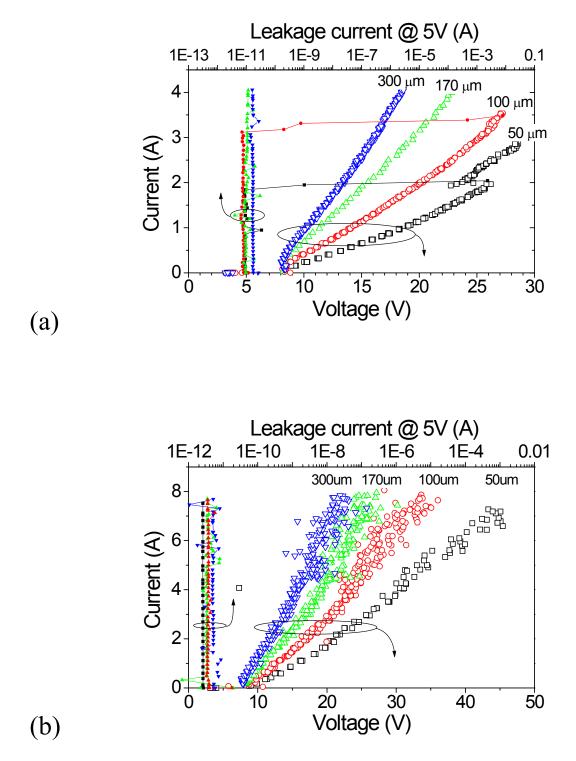

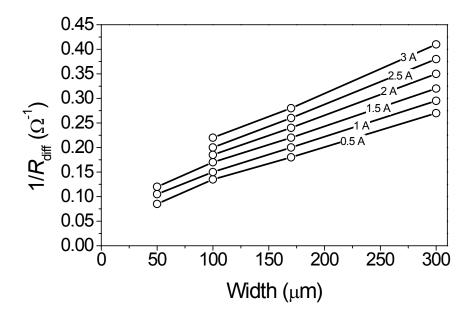

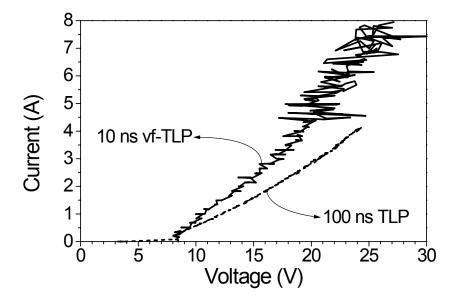

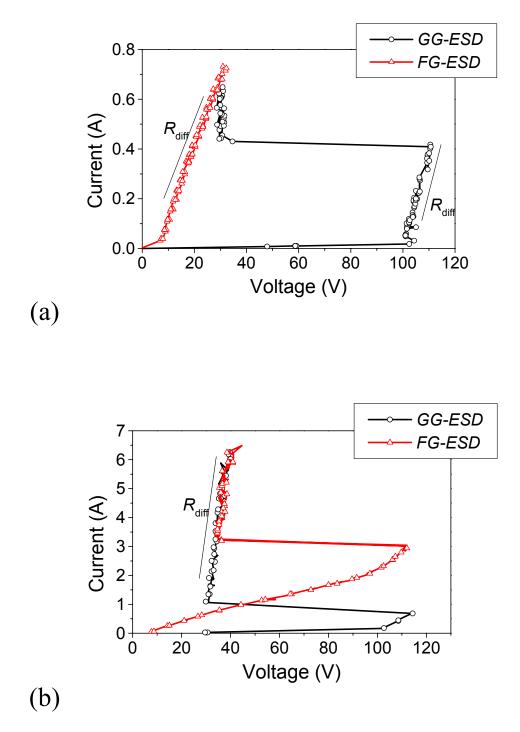

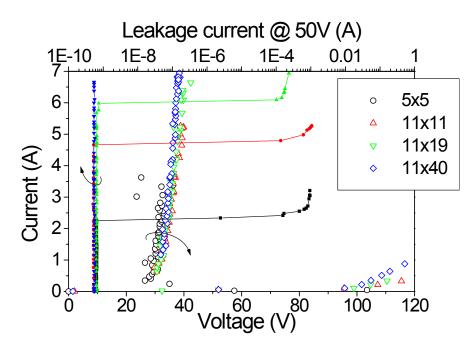

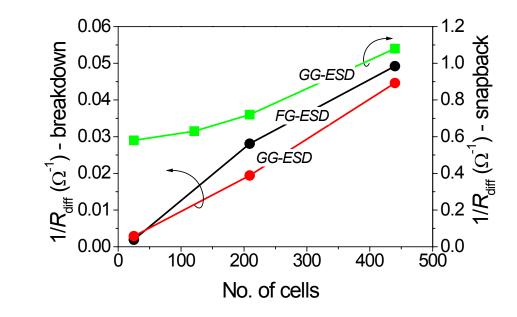

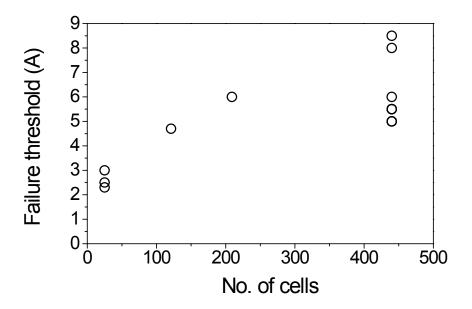

Figs. 3.6(a) and (b) show the high current I-V characteristics of the devices *D1* of different widths measured using the 100 ns TLP and 10 ns vf-TLP, respectively. The holding voltage is about 8 V for both stress types, which corresponds to the second snapback labelled as *SB2* in Fig. 3.2(b). Since the turn-on of the npn transistor, the I-Vs exhibit a slightly super-linear behaviour, which means that the differential resistance  $R_{diff}$  of the devices decreases with increasing stress current level. This is probably caused by the conductivity modulation in the p-body region, and this effect is discussed in more details in the section 3.3.2.1. The main contribution to the  $R_{diff}$  is attributed to the resistance of collector and emitter regions. When the  $1/R_{diff}$  is extracted from the TLP I-Vs and plotted as a function of the device width (Fig. 3.7), nearly linear dependence is found. The scaling suggests that the current flow is homogeneous in the devices under the TLP operating conditions.

Figs. 3.6(a) and (b) also exhibit the leakage current evolution with the stress current level. Sudden increase of the leakage current  $I_{\text{leak}}$  to the *mA* region indicates a failure of the device. This is observed for the devices with 50 µm and 100 µm widths stressed by the 100 ns TLP (Fig. 3.6(a)). The current levels at which it occurs are about 1.8 A and 3.2 A,

Fig. 3.6: High current I-V characteristics of the devices *D1* of various widths measured using (a) 100 ns TLP; and (b) 10 ns vf-TLP.

Fig. 3.7: The  $1/R_{\text{diff}}$  extracted from the 100 ns TLP I-V characteristics of the devices *D1* (Fig. 3.6(a)) as a function of the device width. The stress current level is a parameter.

Fig. 3.8: Comparison of the high current I-V characteristics of the device *D1* of width 170 µm measured using the 100 ns TLP and 10 ns vf-TLP.

Fig. 3.9: High current I-V characteristics of the devices D1, D2 and D3 ( $w = 170 \mu m$ ) measured using (a) 100 ns TLP; and (b) 10 ns vf-TLP.

respectively. For the devices with  $w \ge 170 \ \mu m$  the TLP failure threshold is beyond 4 A. On the other hand, all devices can withstand 7 A of the 10 ns vf-TLP stress, because no increase of the leakage current is observed until then (Fig. 3.6(b)).

If the TLP and vf-TLP I-Vs of the device D1 are compared, a difference can be found: the  $R_{\text{diff}}$  is higher for the TLP case (Fig. 3.8). This can be related to the self-heating effect. At the end of the longer TLP pulse the device is hotter, and consequently its total resistance is higher.

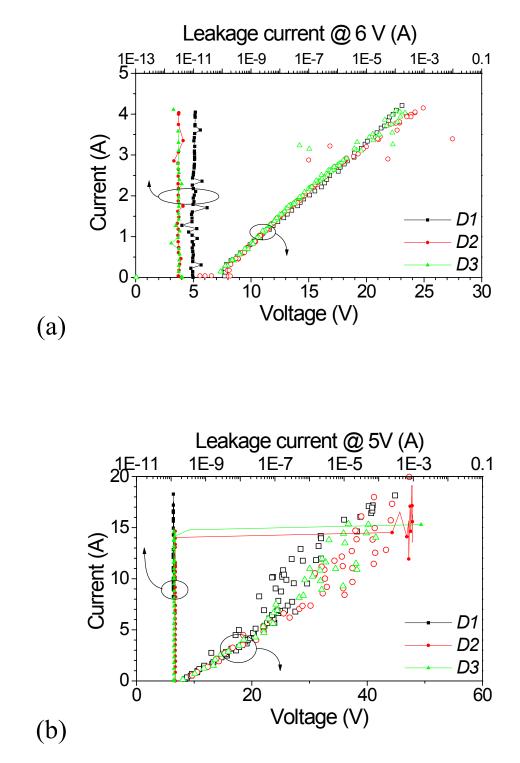

The subsequent electrical characterisation was concentrated on the influence of the device layout on the high current I-V characteristics. Figs. 3.9(a) and (b) compare the high current I-V characteristics of the devices D1, D2 and D3 of the same width (170 µm) measured using the 100 ns TLP and 10 ns vf-TLP, respectively. The  $R_{diff}$  obtained from the 100 ns TLP measurements is the same for all three types of devices (Fig. 3.9(a)). The same is valid for the vf-TLP measurements, at least for  $I_{stress} < 7$  A (Fig. 3.9(b)). At higher currents ( $I_{stress} > 7$  A) the data are rather scattered, and it is difficult to draw any conclusion. The scattering comes mostly from the sparking resistance of the switching TLP relay and from a digitising error of the oscilloscope. All devices can sustain 4 A TLP stress, which is the set-up limit (Fig. 3.9(a)). Moreover, device D1 does not degrade up to the vf-TLP stress level of 18 A (Fig. 3.9(b)), which is again the set-up limit. On the other hand, devices D2 and D3 fail at the vf-TLP current level of approximately 14 A. This means that although there is no remarkable difference in the I-V characteristics, the devices without sinker are less robust.

Summary of the failure thresholds obtained during the electrical characterisation is given in Table 3.1.

|    | TLP   |       |       |       | vf-TLP |       |        |       |

|----|-------|-------|-------|-------|--------|-------|--------|-------|

|    | 50    | 100   | 170   | 300   | 50     | 100   | 170    | 300   |

| D1 | 1.8 A | 3.2 A | > 4 A | > 4 A | > 7 A  | > 7 A | > 18 A | > 7 A |

| D2 | -     | -     | > 4 A | -     | -      | -     | 14 A   | -     |

| D3 | -     | -     | > 4 A | -     | -      | -     | 14 A   | -     |

Table 3.1: Failure thresholds of the investigated devices.

## 3.3.2 Optical characterisation

Optical characterisation employing the heterodyne scanning set-up and the 2-beam Michelson interferometric set-up was performed to investigate the internal behaviour of the devices by localising the heat dissipation sources and the places with an excess free-carrier concentration.

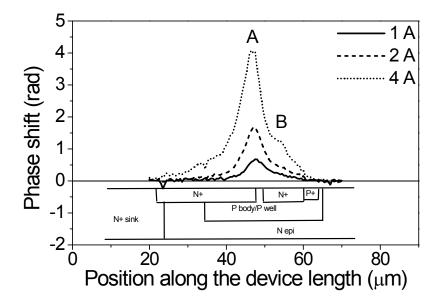

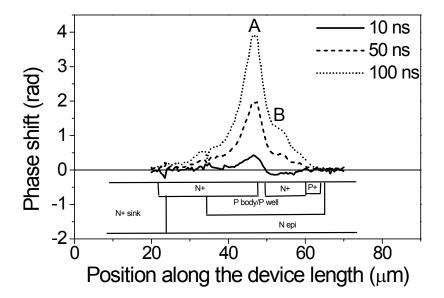

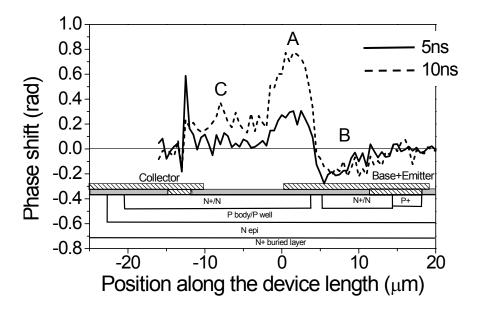

#### 3.3.2.1 Device D1

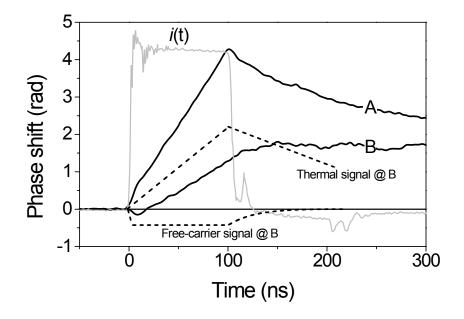

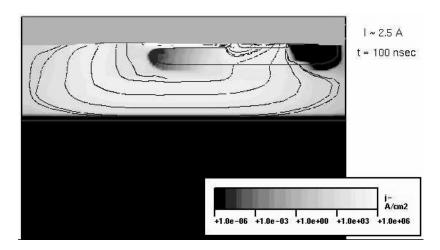

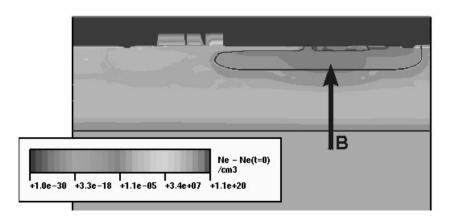

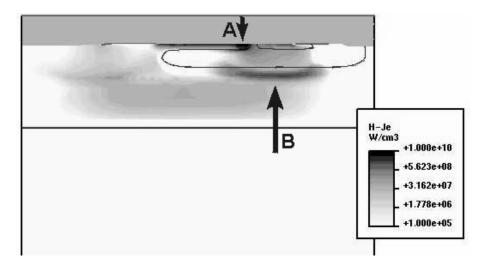

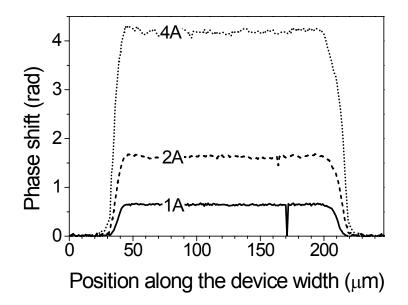

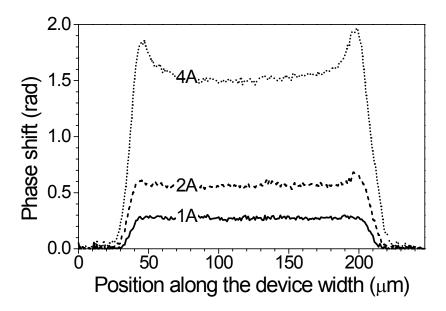

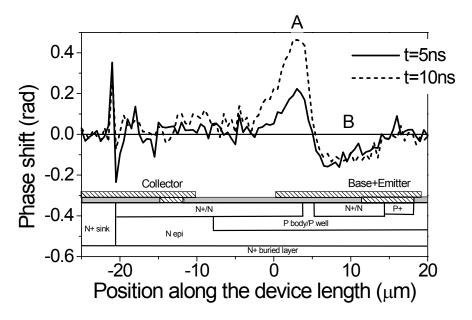

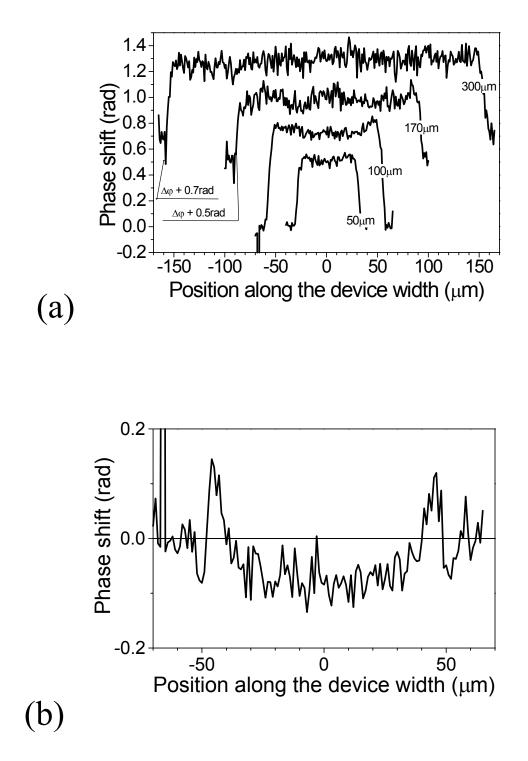

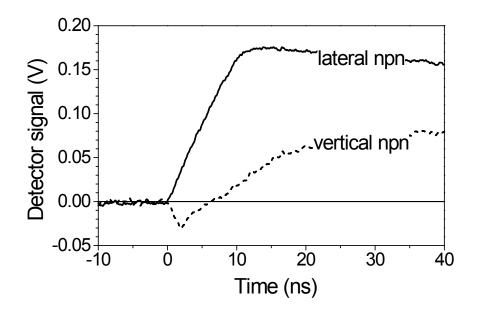

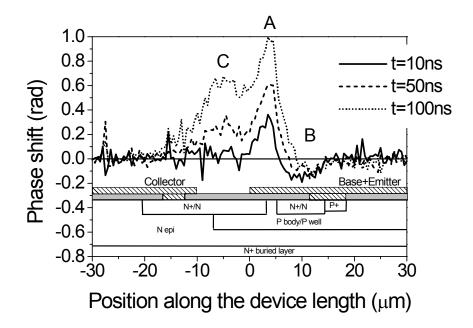

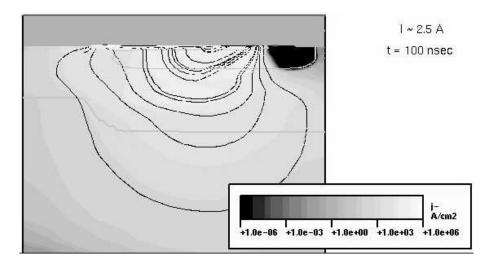

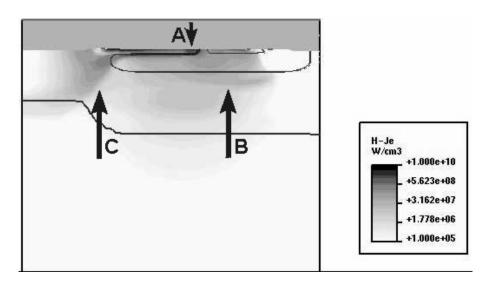

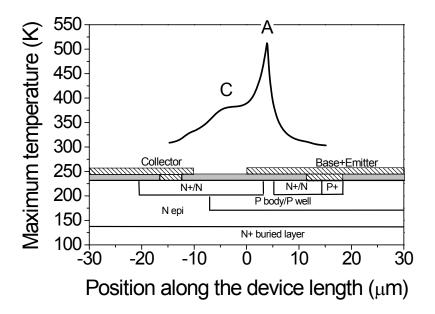

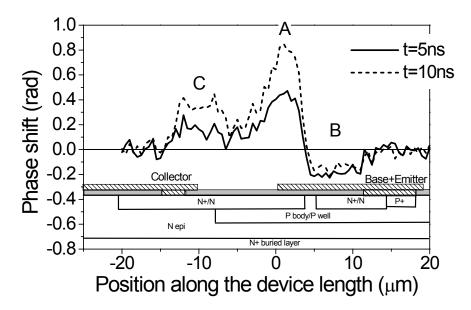

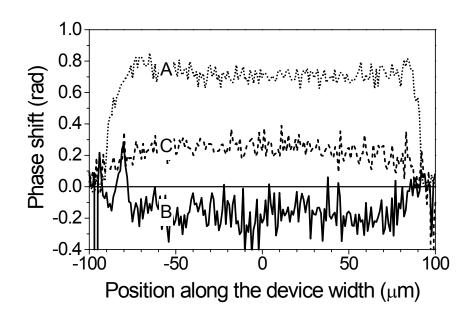

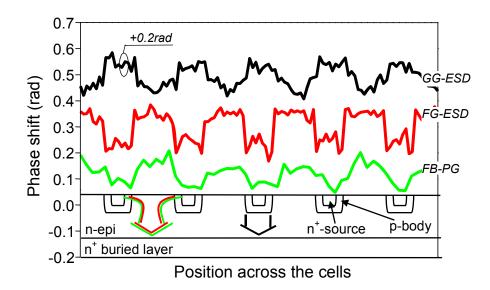

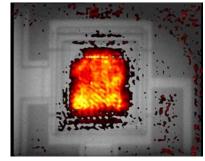

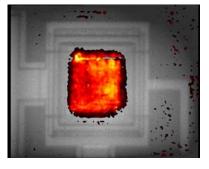

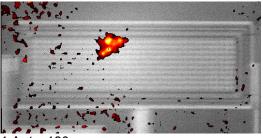

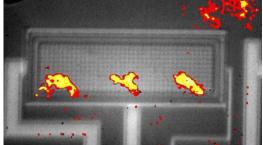

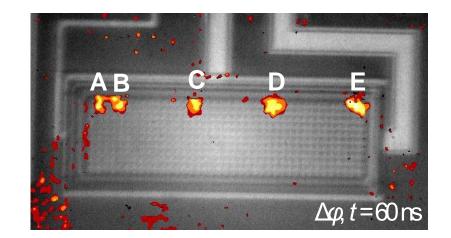

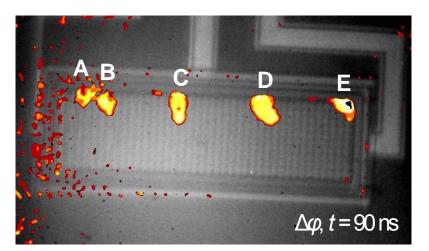

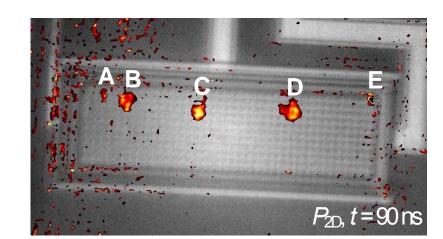

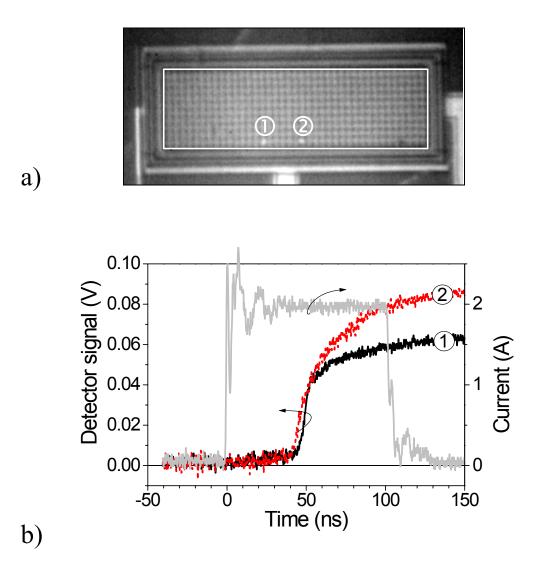

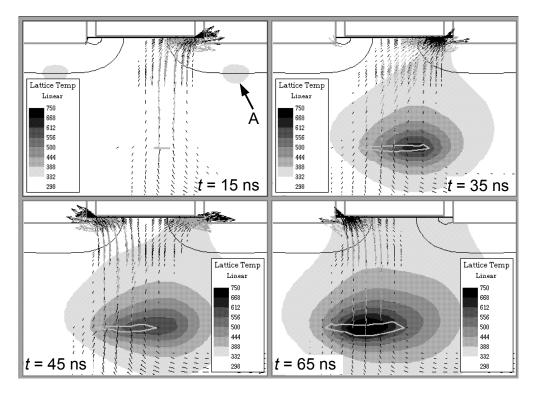

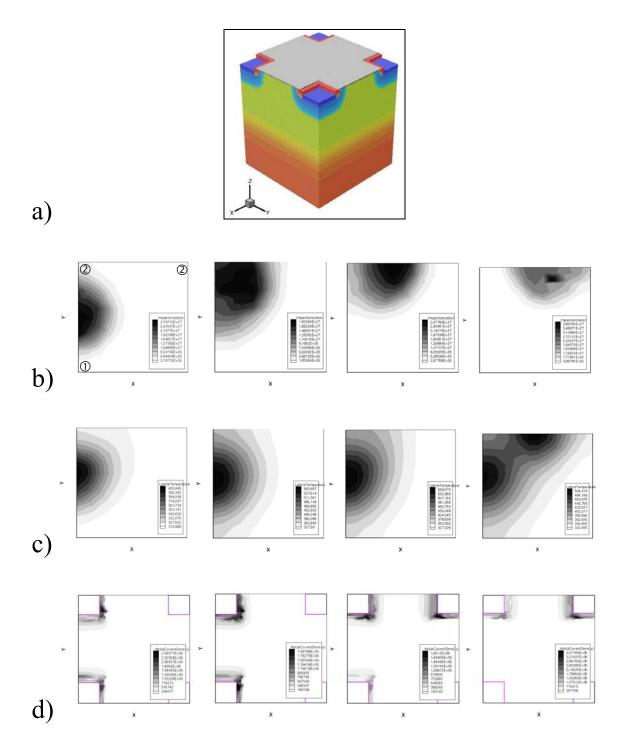

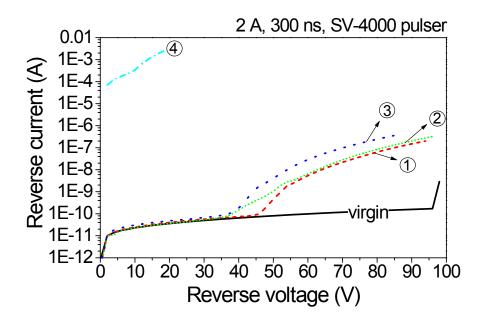

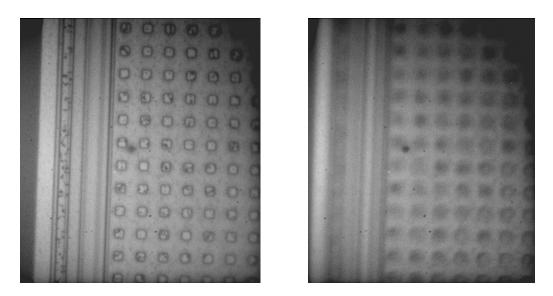

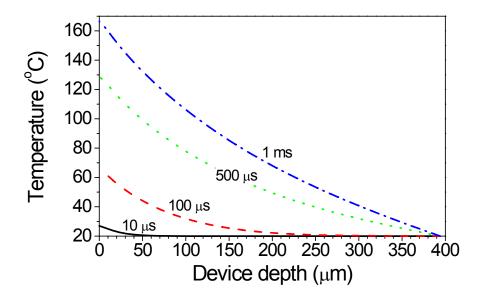

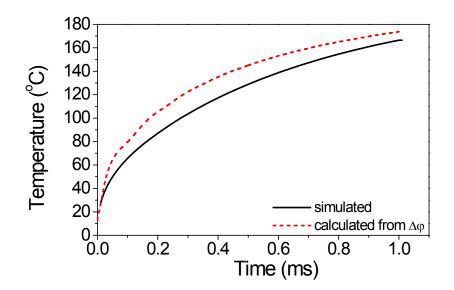

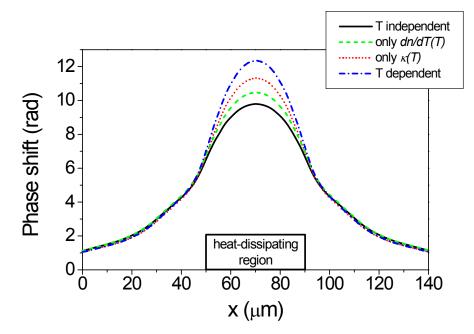

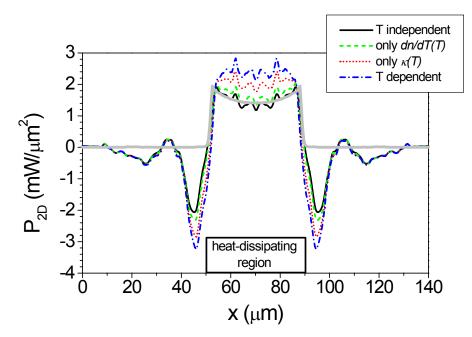

Fig. 3.10 shows the phase shift distributions along the length of the device DI of 170 µm width at the end of the 100 ns TLP stress pulses of different current levels: 1 A, 2 A, and 4 A. Dominant phase shift peak is found at the lateral n<sup>+</sup>-collector/p-body junction (see "A" in Fig. 3.10). This is the same place, where the maximum electric field was found (cf. Fig. 3.5). Accordingly one can deduce that this peak arises from the heat dissipation caused by the impact ionisation in the junction (cf. Fig. 3.3). With increasing stress current the amplitude of the phase shift signal increases at this place, as more and more power is dissipated. Besides the dominant