# DISSERTATION

# Optimization for Enhanced Thermal Technology CAD Purposes

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

STEFAN HOLZER

Matrikelnummer 9525914 geboren am 18. Januar 1976 in Wien

Wien, im Juni 2007

### Abstract

N THE PRESENT PHASE of development, microelectronics has reached a state in which, because of the diminutive size of structures, quantum mechanical effects on the one hand side, and thermal and mechanical effects on the other hand side, gain increasing significance. As a result of the ever-shrinking size of the semiconductor devices, more and more components per given chip area can be integrated for the purpose of handling highly complex tasks more efficiently. This high integration density of semiconductor components entails new challenges for their design, operation, and reliability.

While — on the average — over a period of eighteen months the density of integration of components per chip doubles, over the same span of time the resulting power-loss density keeps growing exponentially — and, concurrently, resulting a dramatic increase in the thermal load on the components. Consequently, it becomes essential to provide considerably better cooling for these high-performance semiconductor devices than for traditional components of the same type.

In order to deal with these effects, a deepened insight into thermal effects and developments is required, while in addition, these effects and their consequences should be rigorously considered by an effective simulation software tool already during the development phase. This way, by the use of suitable optimizing strategies, the components involved can be optimally designed to meet specific operating conditions. As a result, effectively combining the simulation of electrical and thermal effects will be a task of ever increasing importance. Furthermore, for components of such diminutive size, it will become essential to also include mechanical aspects into relevant investigations and research, since particularly these effects are of considerable relevance for reliability.

Since both thermal and mechanical loads have significant bearing on the electrical properties as well as on the reliability of semiconductor components, it becomes a must to optimize them for their intended specific use. An absolute requirement for this is determining material properties with utmost precision, so that characteristics of critical components can be optimized for their specific purpose.

Furthermore, this dissertation is to demonstrate how — by means of simple transient electrical measurements and sophisticated optimizing strategies — important electrical and thermal material parameters can be identified without taking recourse to costly and time-consuming caloric measuring procedures. Subsequently, material parameters thus identified find use in complex compound structures in order to provide the even more precise results that are required for describing the transient temperature developments, and thus being able to calculate the resulting mechanical loads.

# Kurzfassung

IE MIKROELEKTRONIK hat mittlerweile einen Stand erreicht, in dem aufgrund der Strukturgröße quanatenmechanische Effekte auf der einen Seite und thermische und mechanische Effekte auf der anderen Seite, immer mehr an Bedeutung gewinnen. Aufgrund der immer kleiner werdenden Halbleiterbauelemente können immer mehr Bauelemente pro Flächeneinheit auf dem Halbleiterchip intergriert werden, um hoch komplexe Aufgaben noch effizienter bewältigen zu können. Die hohe Intergrationsdichte der Halbleiterbauelemente birgt aber auch neue Herausforderungen in sich, für das Design, den Betrieb und die Zuverlässigkeit dieser Bauelemente.

Während sich die Integrationsdichte der Bauelemente pro Chip in achtzehn Monate im Durchschnitt verdoppelt, wächst die auftretende Leistungsdichte exponentiell im selben Zeitintervall und damit auch die thermische Belastung der Bauteile. Darum ist es notwendig, diese hochperformanten Halbleiterbauelemente noch stärker als bisher zu kühlen.

Um diesen Effekten vorbeugen zu können ist es notwendig, die thermischen Effekte einerseits besser zu verstehen und andererseits diese Effekte und deren Auswirkungen durch Simulation schon in der Entwicklungsphase aufzuzeigen. Dadurch ist es möglich mittels Optimierungsverfahren die Bauteile für bestimmte Betriebsbedingungen optimal zu entwickeln. Eine Kopplung der Simulation von elektrischen und thermischen Effekten gewinnt daher zunehmend an Bedeutung. Für sehr kleine Strukturgrößen der Bauelemente ist es von außerordentlicher Wichtigkeit, mechanische Aspekte in den Untersuchungen mitzuberücksichtigen, da diese Effekte erheblichen Einfluß auf die Zuverlässigkeit haben.

Thermische und mechanische Belastungen haben erheblichen Einfluß sowohl auf die elektrischen Eigenschaften als auch auf die Zuverlässigkeit der Halbleiterbauelemente. Daher ist es unumgänglich, die Halbleiterbauelemente für ihren Einsatz zu optimieren. Dafür müssen die Materialeigenschaften auf das genaueste bestimmt werden, um eine optimumale Bauteilcharakteristik zu erreichen.

Diese Arbeit zeigt wie anhand einfacher transienten elektrischen Messungen und ausgeklügelten Optimierungemethoden wichtige elektrische und thermische Materialparameter identifiziert werden können ohne teure und zeitintensive chalorische Meßmethoden anwenden zu müssen. Im Anschluß daran werden die identifizierten Materialparameter in komplizierteren Verbindungsstrukturen Anwendung finden um genauere Resultate zu liefern. Diese Daten sind erforderlich um die transiente Temperaturentwicklung zu beschreiben und um damit die mechanischen Belastungen berechnen und im Vorfeld abschätzen zu können.

# Acknowledgments

WANT to express my gratitude to my supervisors TIBOR GRASSER, ERASMUS LANGER, and SIEGFRIED SELBERHERR, who gave me the possibility to enroll my PhD program at the Institute for Microelectronics. Moreover, I have to say big thanks to Siegfried for teaching me how to teach and supervise my students and some of my colleagues through several national and international projects. Special thanks go HERMANN SCHICHL, who was always available at short call providing me with the appropriate help and valuable discussions regarding optimization issues.

I am indebted to my collegues CHRISTIAN HOLLAUER, ALIREZA SHEIKHOLESAMI, and GREGOR MELLER and their excellent knowledge of mechanics and thermodynamics which brought me a sympathy to the mechanics and thermodynamics side of microelectronics.

Furthermore, I want to thank STEPHAN WAGNER and WILFRIED WESSNER for their valuable contributions and discussions on compilers, solvers, and meshes over a relaxing beer after work.

Special thanks go to MARKUS KARNER, ANDREAS GEHRING, and OSKAR BAUMGARTNER, the very helpful and understanding room mates. They always had good ideas for lunch and showed much imagination in interpreting some of my written works.

To my colleagues ROBERT ENTNER, STEPHAN-ENZO UNGERSBÖCK, and MARTIN WAGNER, I want to say thanks for their valuable contributions and discussions, even concerning private matters. In addition to our research work, we had great times doing sports together. Moreover, I was allowed to learn a lot from PAUL JÜRGEN WAGNER. He excels in discussions on topics related to electrodynamics, mathematics, and IATEX. I am also indebted to RAINER MINIXHOFER and HELMUT PUCHNER for their valuable discussions on challenging and emerging technology and device issues from an industrial point of view.

Je remercie tous ceux qui m'ont aidé avec les corrections linguistiques de ce thèse et par leur soutien personnel. Mais particulièrement, je voudrais exprimer mes meilleurs sentiments de reconnaissance envers URSULA & THOMAS HEUMESSER, ELEONORA LUISA, PENELOPE & KARL-ERWIN LICHTENECKER, et biensûr ma professeur d'anglais et français SISSI SCHIEMEL.

Ju guter Lett möchte ich meiner Familie und meinen Freunden dafür danken, daß sie mich in diesem schwierigen Lebensabschnitt tatkräftig und unermüdlich unterstützt und mir stell so viel Verständnis entgegen gebracht haben.

En poussant le cri triomphal je remercie tous: "TÖÖÖÖRRRRÖÖÖÖ" .

# Contents

| 1        | Intr | oduction                                                                                                               |

|----------|------|------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Challenges Discussed in this Thesis                                                                                    |

|          | 1.2  | The ITRS and MOORE's Law                                                                                               |

|          | 1.3  | Electrical and Physical Properties                                                                                     |

|          | 1.4  | Thermal Properties and Power Density                                                                                   |

|          | 1.5  | Challenges                                                                                                             |

| <b>2</b> | The  | rmal Effects in Semiconductor Devices 11                                                                               |

|          | 2.1  | Temperature                                                                                                            |

|          | 2.2  | Heating Phenomena 15                                                                                                   |

|          |      | 2.2.1 Heat Flux                                                                                                        |

|          |      | 2.2.2 Onsager's Theorem                                                                                                |

|          |      | 2.2.3 Electro-Magnetic Power Density                                                                                   |

|          |      | 2.2.4 Global versus Local Heating                                                                                      |

|          |      | 2.2.5 Heat Sinks and Sources                                                                                           |

|          |      | 2.2.6 Electro-Thermal Coupling                                                                                         |

|          |      | 2.2.7 Volume Expansion $\ldots \ldots 30$ |

|          |      | 2.2.8 Mechanical Subsystem                                                                                             |

|          |      | 2.2.9 Micromechanics in TCAD                                                                                           |

|          |      | 2.2.10 Electro-Mechanical Coupling 34                                                                                  |

|          | 2.3  | Material Properties                                                                                                    |

|          |      | 2.3.1 Interconnect Materials                                                                                           |

|          |      | 2.3.2 Polycrystalline Materials                                                                                        |

|          | 2.4  | Material Deposition                                                                                                    |

|          |      | 2.4.1 Chemical Vapor Deposition                                                                                        |

|          |      | 2.4.2 Deposition of $SiO_2$                                                                                            |

|          |      | 2.4.3 Deposition of Cu – Damascene Processes                                                                           |

| 3        | The | ermal Models                                                                                                                        | <b>5</b> 8 |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 3.1 | Electrical Conductivity                                                                                                             | 58         |

|          | 3.2 | Electrical Permittivity                                                                                                             | 61         |

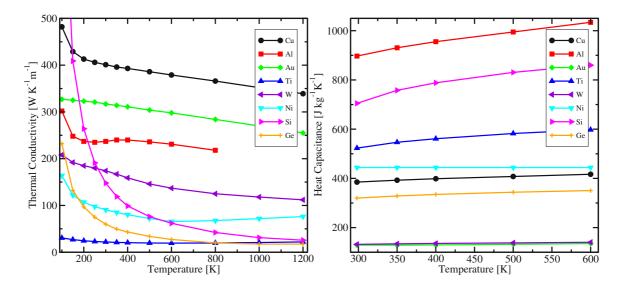

|          | 3.3 | Thermal Conductivity                                                                                                                | 63         |

|          | 3.4 | Heat Capacitance                                                                                                                    | 65         |

|          | 3.5 | Volume Expansion                                                                                                                    | 65         |

|          | 3.6 | Mechanical Stress                                                                                                                   | 66         |

|          | 3.7 | Interconnect Reliability                                                                                                            | 67         |

|          |     | 3.7.1 Electro-Migration                                                                                                             | 68         |

|          |     | 3.7.2 Mean Time To Failure                                                                                                          | 73         |

| 4        | Opt | imization for Technology CAD                                                                                                        | 74         |

|          | 4.1 | Basic Issues on Optimization                                                                                                        | 78         |

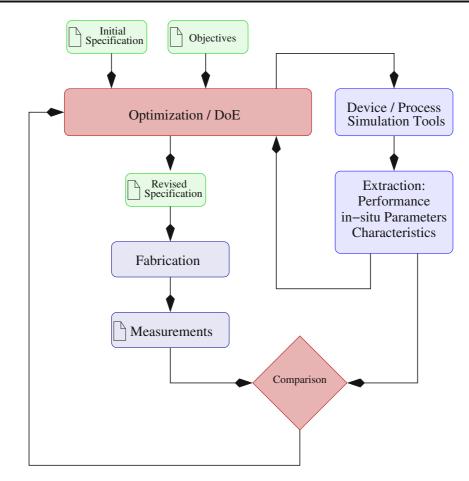

|          |     | 4.1.1 Optimization Loop                                                                                                             | 80         |

|          |     | 4.1.2 Industrial Requirements                                                                                                       | 82         |

|          | 4.2 | Optimization Strategies                                                                                                             | 83         |

|          |     | 4.2.1 Coordinate Search Algorithm                                                                                                   | 83         |

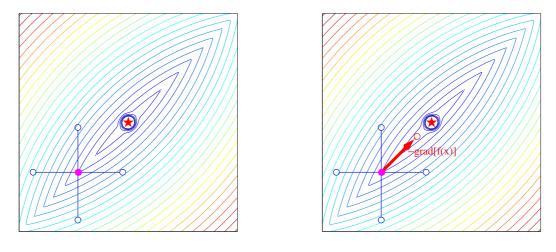

|          |     | 4.2.2 Gradient-based Optimization                                                                                                   | 83         |

|          |     | 4.2.3 DIRECT Search Optimization                                                                                                    | 86         |

|          |     | 4.2.4 Genetic Optimization                                                                                                          | 86         |

|          |     | 4.2.5 Evolutionary Optimization                                                                                                     | 87         |

|          |     | 4.2.6 Simulated Annealing Approach                                                                                                  | 89         |

|          | 4.3 | State-of-the-art in Optimization                                                                                                    | 89         |

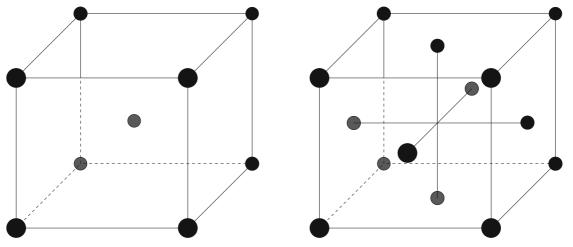

|          |     | 4.3.1 Design of Experiments                                                                                                         | 92         |

|          | 4.4 | Challenges in Optimization                                                                                                          | 93         |

|          |     | 4.4.1 Constraints                                                                                                                   | 94         |

|          |     | 4.4.2 Selection of Optimization Strategies and Score Functions                                                                      | 94         |

|          |     | 4.4.3 Convergence                                                                                                                   | 95         |

|          |     | 4.4.4 Reasonable Results versus Numerical Optimum                                                                                   | 96         |

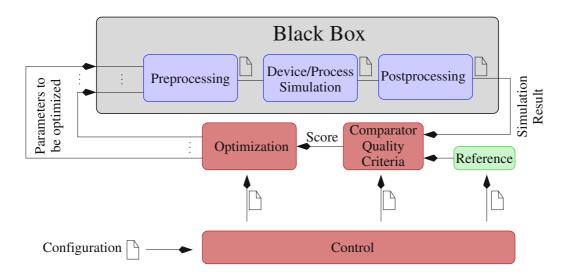

|          | 4.5 | Optimization Framework SIESTA                                                                                                       | 96         |

|          |     | 4.5.1 Parallelization Strategy                                                                                                      | 98         |

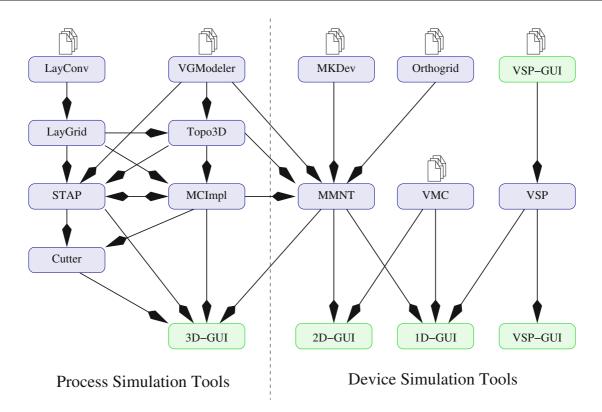

|          |     | 4.5.2 Simulation Tools                                                                                                              | 99         |

| <b>5</b> | App | plications 1                                                                                                                        | 04         |

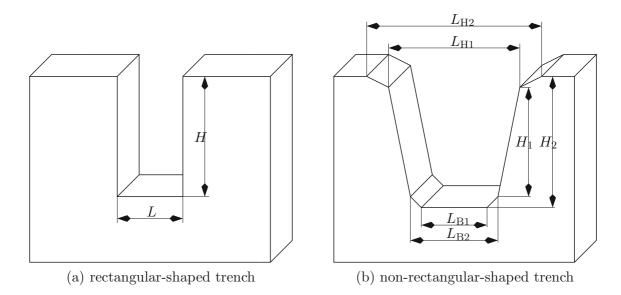

|          | 5.1 | Calibration of Trenches                                                                                                             | 04         |

|          |     | 5.1.1 Treatment of Moving Boundaries                                                                                                | .04        |

|          |     | 5.1.2 Quality Criteria $\ldots \ldots 1$ | 05         |

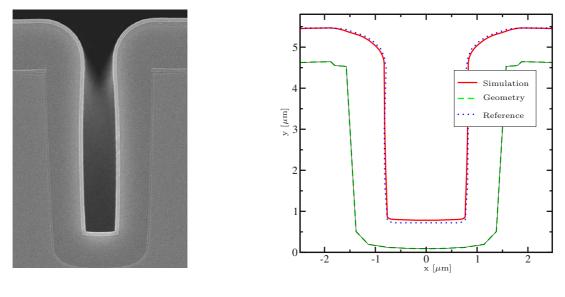

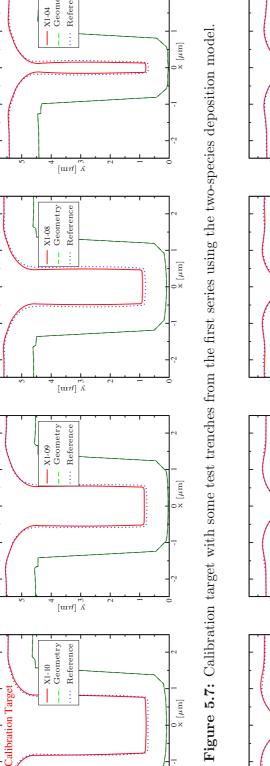

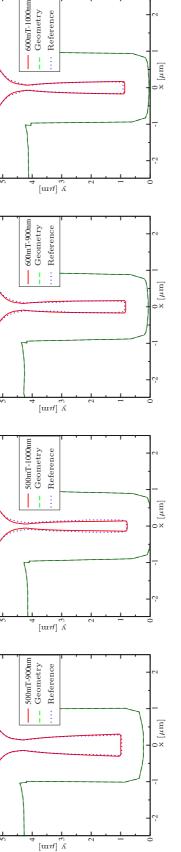

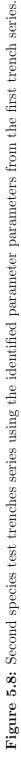

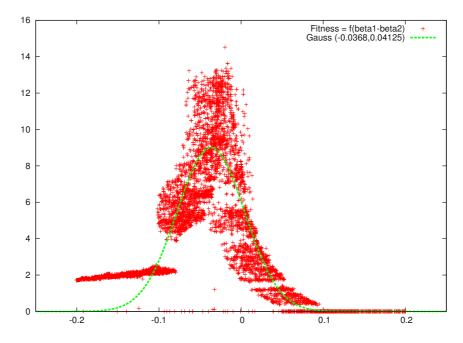

|              |                                                                                                       | 5.1.3                                                                                    | TEOS Deposition                                                          | 105                                                         |

|--------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------|

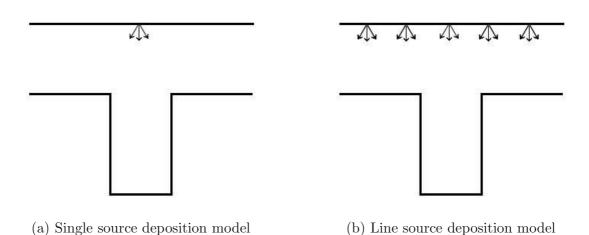

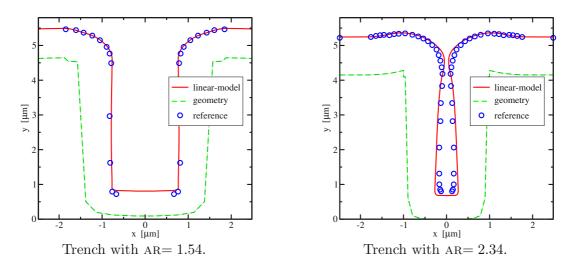

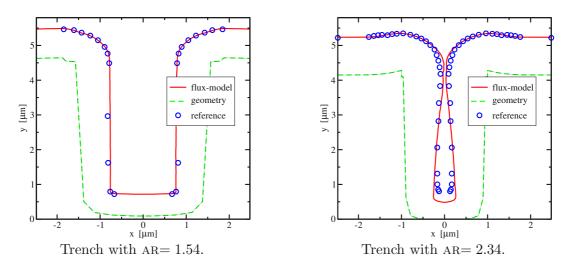

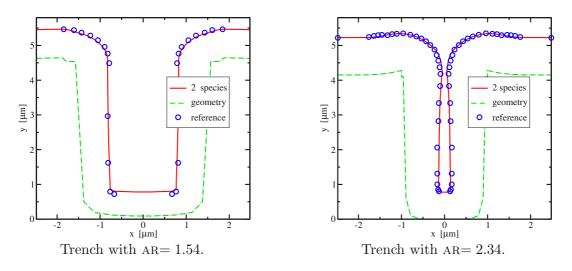

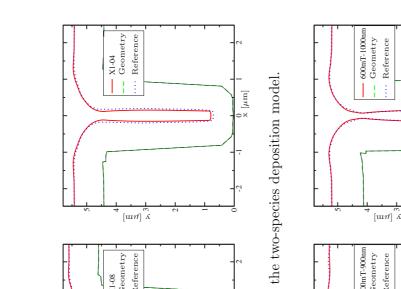

|              |                                                                                                       | 5.1.4                                                                                    | Deposition Models                                                        | 107                                                         |

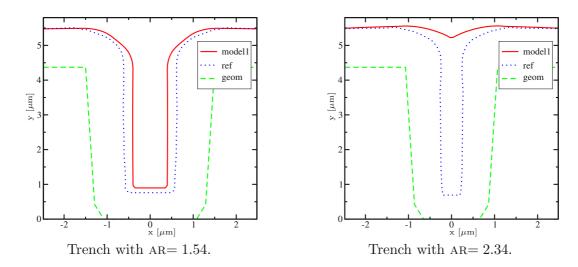

|              |                                                                                                       | 5.1.5                                                                                    | Model Calibration                                                        | 110                                                         |

|              | 5.2                                                                                                   | Param                                                                                    | eter Extraction of a Fusing Structure                                    | 113                                                         |

|              |                                                                                                       | 5.2.1                                                                                    | Fusing Structure                                                         | 113                                                         |

|              |                                                                                                       | 5.2.2                                                                                    | Simulation and Parameter Extraction                                      | 115                                                         |

|              |                                                                                                       | 5.2.3                                                                                    | Results                                                                  | 115                                                         |

|              | 5.3                                                                                                   | Applie                                                                                   | d Optimized Parameters                                                   | 119                                                         |

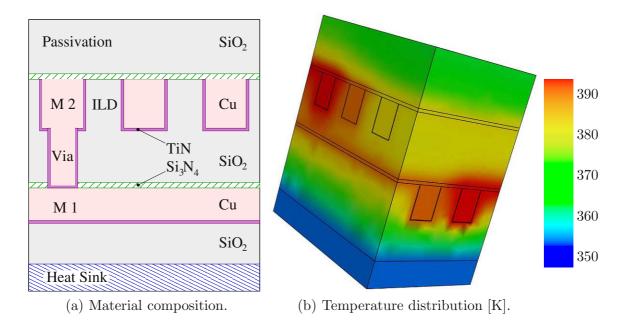

|              |                                                                                                       | 5.3.1                                                                                    | Thermal Analysis of a Multi-Layered Interconnect Structure               | 119                                                         |

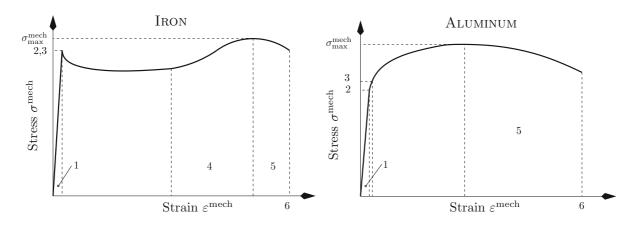

|              |                                                                                                       | 5.3.2                                                                                    | Interconnect Structure Subjected to Mechanical Stress                    | 122                                                         |

| 6            | Con                                                                                                   | nclusion                                                                                 | ıs                                                                       | 124                                                         |

|              | 6.1                                                                                                   | Tempe                                                                                    | erature as a Limiting Factor                                             | 124                                                         |

|              | 6.2                                                                                                   | Multip                                                                                   | le (Thermal) Redundancy                                                  | 125                                                         |

|              | 6.3                                                                                                   | New N                                                                                    | faterials and New Devices Structures                                     | 125                                                         |

|              | 6.4                                                                                                   | Outloo                                                                                   | ok                                                                       | 126                                                         |

|              |                                                                                                       |                                                                                          |                                                                          |                                                             |

| $\mathbf{A}$ | Mat                                                                                                   | themat                                                                                   | ical Notes                                                               | 127                                                         |

| A            | Mat<br>A.1                                                                                            |                                                                                          | ical Notes                                                               | 1 <b>27</b><br>127                                          |

| A            |                                                                                                       | Conve                                                                                    |                                                                          |                                                             |

| A            | A.1                                                                                                   | Conver<br>Voigt                                                                          | xity of Sets and Domains                                                 | 127                                                         |

| Α            | A.1<br>A.2                                                                                            | Conver<br>Voigt                                                                          | xity of Sets and Domains                                                 | 127<br>128                                                  |

| A            | A.1<br>A.2                                                                                            | Conver<br>Voigt I<br>Norms                                                               | xity of Sets and Domains                                                 | 127<br>128<br>129                                           |

| A            | A.1<br>A.2<br>A.3                                                                                     | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2                                             | xity of Sets and Domains                                                 | 127<br>128<br>129<br>129                                    |

|              | A.1<br>A.2<br>A.3                                                                                     | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2<br>Aspect                                   | xity of Sets and Domains                                                 | 127<br>128<br>129<br>129<br>129                             |

| A<br>B       | A.1<br>A.2<br>A.3<br>A.4                                                                              | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2<br>Aspect                                   | xity of Sets and Domains                                                 | 127<br>128<br>129<br>129<br>129<br>130                      |

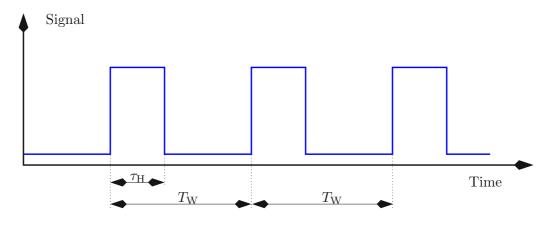

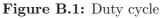

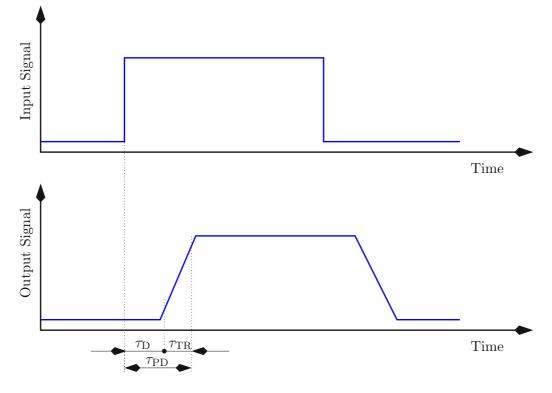

|              | <ul><li>A.1</li><li>A.2</li><li>A.3</li><li>A.4</li><li>Tim</li></ul>                                 | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2<br>Aspect<br><b>hing</b><br>Duty (          | xity of Sets and Domains                                                 | 127<br>128<br>129<br>129<br>129<br>130<br><b>131</b>        |

| в            | <ul> <li>A.1</li> <li>A.2</li> <li>A.3</li> <li>A.4</li> <li>Tim</li> <li>B.1</li> <li>B.2</li> </ul> | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2<br>Aspect<br><b>hing</b><br>Duty (          | xity of Sets and Domains   Notation   Definition   Special Norms   Ratio | 127<br>128<br>129<br>129<br>130<br><b>131</b><br>131        |

| B            | A.1<br>A.2<br>A.3<br>A.4<br><b>Tim</b><br>B.1<br>B.2<br><b>bliog</b>                                  | Conver<br>Voigt I<br>Norms<br>A.3.1<br>A.3.2<br>Aspect<br><b>hing</b><br>Duty C<br>Delay | xity of Sets and Domains                                                 | 127<br>128<br>129<br>129<br>130<br><b>131</b><br>131<br>132 |

# List of Physical Constants

| Symbol           | Description                                                                                                                                | Relative Uncertainty       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| c <sub>0</sub>   | Vacuum speed of light<br>$c_0 = 299792458 \mathrm{m  s^{-1}}$                                                                              | per definitionem [1]       |

| $\mu_0$          | Vacuum permeability constant<br>$\mu_0 = 4\pi \times 10^{-7} \mathrm{H  m^{-1}} = 12.56637 \times 10^{-7} \mathrm{H  m^{-1}}$              | per definitionem [1]       |

| $\varepsilon_0$  | Vacuum permittivity constant<br>$\varepsilon_0 = \frac{1}{\mu_0 c_0^2} = 8.854187817 \times 10^{-12} \mathrm{F m^{-1}}$                    | per definitionem [1]       |

| h                | PLANCK's constant<br>$h = 6.6260693 \times 10^{-34} \text{ Js}$                                                                            | $1.7 \times 10^{-7} \ [1]$ |

| $k_{\mathrm{B}}$ | BOLTZMANN's constant<br>$k_{\rm B} = 1.3806503 \times 10^{-23}  {\rm J/K}$                                                                 | $1.8 \times 10^{-6} \ [1]$ |

| $N_L$            | LOSCHMIDT's number or AVOGADRO's constant $N_L = 6.0221415 \times 10^{23} \text{ mol}^{-1}$                                                | $1.7 \times 10^{-7} \ [1]$ |

| q                | Elementary charge of an electron $q = 1.60217653 \times 10^{-19} C$                                                                        | $8.5 \times 10^{-8} \ [1]$ |

| R                | Universal gas constant<br>$R = N_L k_B = 8.314472  J  K^{-1}  mol^{-1}$                                                                    | $1.7 \times 10^{-6} \ [1]$ |

| $\sigma_{ m SB}$ | STEFAN-BOLTZMANN's constant<br>$\sigma_{\rm SB} = \frac{2\pi^5 k_{\rm B}^4}{15h^3 c_0} = 5.6704 \times 10^{-8} \mathrm{W  m^{-2}  K^{-4}}$ | $7.0 	imes 10^{-6}$ [1]    |

|                  |                                                                                                                                            |                            |

# Notations

| x                       | <br>Scalar-valued quantity                                  |

|-------------------------|-------------------------------------------------------------|

| x                       | <br>Vector-valued quantity                                  |

| $\tilde{x}$             | <br>Tensor-valued quantity                                  |

| $<\!\!x\!\!>$           | <br>Mean value of the quantity $x$                          |

| $f_1 \circ f_2$         | <br>Nested Function: equivalent to $f_1(f_2)$               |

| $(\cdot)^{\mathcal{T}}$ | <br>Transposition of a vector or matix                      |

| $\partial_t$            | <br>Time derivative operator: $\frac{\partial}{\partial t}$ |

| $\nabla$                | <br>Nabla operator                                          |

| $\nabla(\cdot)$         | <br>Gradient of $(\cdot)$                                   |

| $ abla \cdot (\cdot)$   | <br>Divergence of $(\cdot)$                                 |

| $\nabla \times (\cdot)$ | <br>Curl (or Rotation) of $(\cdot)$                         |

| $\Delta(\cdot)$         | <br>LAPLACEan operator: $\nabla \cdot \nabla(\cdot)$        |

| $\wedge$                | <br>Logical conjunction                                     |

| $\implies$              | <br>Logical implication                                     |

# List of Acronyms

| ALD                     | <br>Atomic layer deposition                                |

|-------------------------|------------------------------------------------------------|

| CAD                     | <br>Computer aided design                                  |

| CNT                     | <br>Carbo-Nanotube                                         |

| Corba                   | <br>Common Object Request Broker Architecture              |

| CPU                     | <br>Central processing unit                                |

| CVD                     | <br>Chemical vapour deposition                             |

| CoO                     | <br>Cost of ownership                                      |

| DD                      | <br>Drift Diffusion                                        |

| DNA                     | <br>Deoxyribonucleic acid                                  |

| ELK                     | <br>Extreme low- $\kappa$                                  |

| Elsa                    | <br>Enhanced Level-Set Applications                        |

| EOT                     | <br>Effective oxide thickness                              |

| FET                     | <br>Field effect transistor                                |

| Gb                      | <br>Gigabit                                                |

| GB                      | <br>Gigabyte                                               |

| GHz                     | <br>Gigahertz                                              |

| GUI                     | <br>Graphical user interface                               |

| ILD                     | <br>Interlayer dielectric                                  |

| IPD                     | <br>Inputdeck language                                     |

| IT                      | <br>Information Technoloy                                  |

| ITRS                    | <br>International Technology Roadmap for Semiconductors    |

| LPCVD                   | <br>Low pressure chemical vapour deposition                |

| MC                      | <br>Monte Carlo                                            |

| MTTF                    | <br>Mean time to failure                                   |

| MILP                    | <br>Mixed integer linear programming                       |

| n-Si                    | <br>n-doped Silicon                                        |

| NFS                     | <br>Network file system                                    |

| NTC                     | <br>Negative temperature coefficient                       |

| OSG                     | <br>Organo-silcate glass                                   |

| p-Si                    | <br>p-doped Silicon                                        |

| poly                    | <br>polycrystalline                                        |

| $\operatorname{polySi}$ | <br>polycrystalline Silicon                                |

| PTC                     | <br>Positive temperature coefficient                       |

| PTFE                    | <br>Polytetrafluoroethylene                                |

| PZT                     | <br>Lead Zirkonium Titanate $Pb(Ti, Zr)O_3$                |

| RE                      | <br>Rare earth elements, member of the lanthanoide group   |

|                         | ${La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu}$ |

| RTD                     | <br>Resonant tunneling diode                               |

|                         |                                                            |

### CONTENTS

| SeiLib | <br>Simulation Environment Interaction Library                       |

|--------|----------------------------------------------------------------------|

| SEM    | <br>Scanning electron microscopy                                     |

| Siesta | <br>Simulation Environment for Semiconductor Technology Analysis     |

| TCAD   | <br>Technology computer aided design                                 |

| TEM    | <br>Transmission electron microscopy                                 |

| TEOS   | <br>Tetra-ethoxy-silane, Tetra-ethyl-ortho-silicate: $Si(C_2H_5O)_4$ |

| VLSI   | <br>Very large scale integration                                     |

| WSS    | <br>Wafer-State-Server: File format for distributed quantities       |

| XML    | <br>Extensible markup language                                       |

# List of Chemical Symbols

| Ac                     | <br>Actinium    | Gd                  | <br>Gadolium     | Ро                     | <br>Polonium            |

|------------------------|-----------------|---------------------|------------------|------------------------|-------------------------|

| Ag                     | <br>Silver      | Н                   | <br>Hydrogenium  | $\Pr$                  | <br>Praseodymium        |

| Al                     | <br>Aluminum    | He                  | <br>Helium       | $\operatorname{Pt}$    | <br>Platinum            |

| Am                     | <br>Americum    | Hf                  | <br>Hafnium      | Pu                     | <br>Plutonium           |

| Ar                     | <br>Argon       | Hg                  | <br>Mercury      | Ra                     | <br>Radium              |

| As                     | <br>Arsenic     | Ho                  | <br>Holmium      | Rb                     | <br>Rubidium            |

| At                     | <br>Astatine    | In                  | <br>Indium       | RE                     | <br>Rare earth elements |

| Au                     | <br>Gold        | Ir                  | <br>Iridium      | Re                     | <br>Rhenium             |

| В                      | <br>Bor         | J                   | <br>Iodine       | $\mathbf{R}\mathbf{h}$ | <br>Rhodium             |

| Ba                     | <br>Barium      | Κ                   | <br>Pottassium   | Rn                     | <br>Radon               |

| Be                     | <br>Beryllium   | Kr                  | <br>Krypton      | Ru                     | <br>Ruthetium           |

| Bi                     | <br>Bismuth     | La                  | <br>Lanthanum    | $\mathbf{S}$           | <br>Sulphurous          |

| Bk                     | <br>Berkelium   | Li                  | <br>Lithium      | $\operatorname{Sb}$    | <br>Antimony            |

| $\operatorname{Br}$    | <br>Bromine     | $\operatorname{Lr}$ | <br>Lawrencium   | $\operatorname{Sc}$    | <br>Scandium            |

| $\mathbf{C}$           | <br>Carbon      | Lu                  | <br>Lutetium     | Se                     | <br>Selenium            |

| Ca                     | <br>Calcium     | Md                  | <br>Mendelevium  | Si                     | <br>Silicon             |

| $\operatorname{Cd}$    | <br>Cadmium     | Mo                  | <br>Molybdenum   | $\operatorname{Sm}$    | <br>Samarium            |

| Ce                     | <br>Cerium      | Mg                  | <br>Magnesium    | $\operatorname{Sn}$    | <br>Tin                 |

| $\mathbf{C}\mathbf{f}$ | <br>Californium | Mn                  | <br>Manganesium  | $\operatorname{Sr}$    | <br>Stronitium          |

| Cl                     | <br>Chlorine    | Mo                  | <br>Molybdenum   | Ta                     | <br>Tantalum            |

| Cm                     | <br>Curium      | Ν                   | <br>Nitrogenium  | Tb                     | <br>Terbium             |

| $\operatorname{Co}$    | <br>Cobalt      | Na                  | <br>Sodium       | $\mathrm{Tc}$          | <br>Technetium          |

| $\mathbf{Cs}$          | <br>Cesium      | Nb                  | <br>Niobium      | Te                     | <br>Tellurium           |

| Cu                     | <br>Copper      | Ne                  | <br>Neon         | $\mathrm{Th}$          | <br>Thorium             |

| Dy                     | <br>Dysprosium  | Nd                  | <br>Neodymium    | Ti                     | <br>Titanium            |

| $\operatorname{Er}$    | <br>Erbium      | Ni                  | <br>Nickel       | Tl                     | <br>Thallium            |

| Es                     | <br>Einsteinium | No                  | <br>Nobelium     | $\mathrm{Tm}$          | <br>Thulium             |

| $\mathbf{E}\mathbf{u}$ | <br>Europium    | Np                  | <br>Neptunium    | W                      | <br>Tungsten            |

| $\mathbf{F}$           | <br>Fluorine    | Ο                   | <br>Oxygen       | U                      | <br>Uranium             |

| Fe                     | <br>Iron        | Os                  | <br>Osmium       | Xe                     | <br>Xenium              |

| $\operatorname{Fm}$    | <br>Fermium     | Р                   | <br>Phosphorus   | Υ                      | <br>Yttrium             |

| $\mathbf{Fr}$          | <br>Francium    | Pa                  | <br>Protactinium | Yb                     | <br>Ytterbium           |

| Ga                     | <br>Gallium     | $\mathbf{Pb}$       | <br>Lead         | Zn                     | <br>Zinc                |

| Ge                     | <br>Germanium   | Pd                  | <br>Palladium    | $\operatorname{Zr}$    | <br>Zirconium           |

|                        |                 |                     |                  |                        |                         |

### Chapter 1

## Introduction

N THE EARLY 1970s, at the beginning of the age of microelectronics, the integration density was approximately two transistors per square millimeter [2]. This density is very low compared to integration densities of today's microelectronic devices [2, 3]. With the continuous miniaturization of semiconductor devices and a nearly constant power dissipation per transistor, the power densities on microelectronic chips have increased in much the same way as the devices have shrunk. Therefore, thermal issues have become more and more important for the design of state-of-the-art devices determined by the maximum thermal

budget for the device fabrication process and for the device operation.

The thermal budget can be influenced by the choice of the materials and chemical reactions that are used to form the microelectronic device structure. The increase of temperature causes changes in chemical reactions and growth rates as well as an increase of the electrical resistance and also broadening of doping profiles. Obviously, finding the appropriate temperature is crucial for all parts in device fabrication and device operation. Therefore it is important to investigate and predict the influence of the temperature to determine the process window for fabrication and the operation window to run the device.

The main goal of today's and future microelectronic designs is to determine the produced heat and heat flow in the device as well as to estimate the temperature and its impact on the device characteristics and its consequences for surrounding materials. In addition to the thermal requirements for fabrication and operation, the occurring self-heating can be critical if the heat flow through the device from the heat source to the heat sink cannot be controlled appropriately. This phenomenon can often be observed in devices with very high power densities.

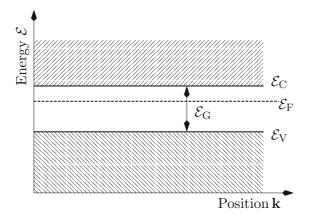

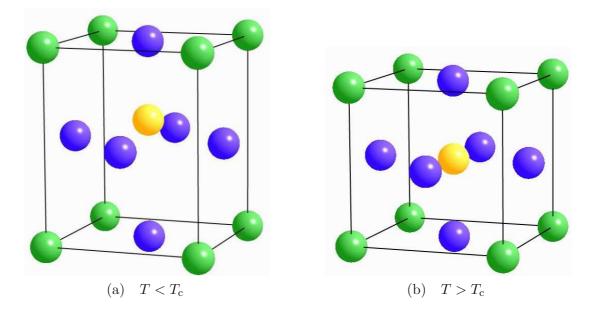

Hence, thermal effects are becoming the dominant factor which determine the maximum performance of integrated circuits due to limited heat transport to the heat sink. The temperature dependence has been neglected for a long time, but today for certain characteristic parameters of microelectronic devices and technologies, these formerly neglected of self-heating effects in the simplified models have to be adapted. Hence, these parameters are becoming functions of temperature and their maximum heat transport capabilities. For example the maximum clock frequency is mostly determined by the temperature increase induced by the increased switching currents and the enhancement of integration density, which produce a higher power dissipation. Hence, the surrounding devices are also heated by this additional power density. Due to the temperature increase, also the volume expansions of the materials have to be considered which result in changes of the crystal structure and therefore also in the band structure of the semiconductor material. This effect can increase or decrease the carrier mobility depending on the direction of the mechanical stress. Thus, the complexity and the maximum integration density of integrated circuits is limited by electrical, thermal, and mechanical constraints of material properties.

To achieve the present and future goals proposed by the International Technology Roadmap for Semiconductors (ITRS) [3], faster devices have to be created which need less chip area and less power to operate. Therefore, imminent thermal effects [4,5] have to be considered carefully in order to keep right on track. Since the physics behind these effects is very complex and is only rudimentary implemented, more rigorous physics-based models have to be applied which increase the computational effort tremendously. Rigorous investigations of problems which are of industrial interest are therefore limited by the finite resources both in time and CPU power.

However, despite of these limitations, the time-to-market has to be reduced in order to position new microelectronic products at an early stage for an advantageous market share. Therefore, experiments have to be carried out either with measurements or simulations to achieve the required quality criteria. The faster the developments can be achieved and verified, the faster the market entry and therefore, the higher the earnings are for the first development stage. Hence, rapid results can be obtained with a combination of simulations and experiments, where the simulations give an overview on the intrinsic material parameters and quantity distributions, while the measurements ensure that the overall functionality remains with in the specifications. Measurements of material parameters of real devices cost a lot of money and time because it takes the whole time of a complete fabrication process before the measurements can be performed. With simulation tools, the same experiments can be performed within a very small fraction of the time a new device fabrication process would take. Moreover, the simulation results can be calibrated in order to perfectionize the prediction from the simulation. Again, these new and better results can be used to develop better simulation models which have to be calibrated as well for each new technology. The main benefit from this procedure is that once the simulation has been calibrated to the technology, the prediction gained from the simulation results supports the engineers during the design and the fabrication process. Therefore, physics-based models have to be developed, that allow the calculation of sufficiently accurate simulation results within reasonable time for the evaluation. For such purposes, but especially for thermal problems, new approaches or enhancements of existing models are needed in order to detect hot spots due to heat accumulation, heat conduction paths, and heat fluxes as well as other phenomena that coincide with the increase of the temperature. In order to obtain accurate simulation results within reasonable time, improved numerical methods are required as well.

### 1.1 Challenges Discussed in this Thesis

This chapter presents the motivation of this thesis and points out the resulting benefits for semiconductor devices, their enhancements, and their applications.

In Chapter 2, the impact of thermal effects on important parameters of fabrication processes and operation conditions of microelectronic devices is discussed. Moreover, this chapter shows how coupling of different simulation regimes is possible and consequently provides a better insight into today's critical thermal issues for semiconductor devices.

Chapter 4 gives an introduction to available optimization techniques that can be used within a certain range of applications for industrial requirements. Furthermore, important industrial requirements for optimization in general are presented as well as an approach which allows to apply an inverse modeling technique for parameter extraction and identification purposes in an efficient way. Examples are presented in Chapter 5 which show the wide range of applications for optimizations and for the optimization environment SIESTA (Simulation Environment for Semiconductor Technology Analysis). In order to improve device characteristics as well as to reduce thermally induced parasitic phenomena, some special sub-problems are discussed that are crucial for certain device fabrication processes.

To conclude this thesis, Chapter 6 discusses future trends in microelectronics with a focus on exploiting thermally induced phenomena and presents alternatives for the semiconductor devices and materials in the micro and nano regime.

### 1.2 The ITRS and MOORE's Law

Since the beginning of the microelectronics age, the increase in sophistication of semiconductor devices seems to grow exponentially. This behavior was described by  $MOORE^1$  [6] in 1965 and remains valid until today [7]. The transistor integration densities as well as the complexity of microelectronic devices have increased in the same speed. On average, they have doubled every eighteen months [3,8–11]. This observation has become known as MOORE's law.

It seems that despite some fluctuations of the average speed of the enhancements, the growth rate remains exponential and keeps constant for microprocessors and memory and seems to remain valid for future devices [7]. At present, the upcoming challenges are the absolute physical constraints of the atomic material structure [3] in terms of the electrical behavior and mechanical properties due to the high stress gradients in thin film materials which appear during fabrication and may be enhanced during device operation.

The enhancement of integration and the shrinking of the device feature size leads to smaller and more sophisticated devices. Thus, more devices can be integrated within the same area as before, leading to a higher package density. At a certain package density, however, new effects become important, e.g. self-heating of the semiconductor devices and the interconnect lines [11, 12]. To overcome these problems, the device engineers have to develop smart device arrangements and new technologies for fabrication to reduce parasitic (thermal) effects or to exploit them by using these effects for compensation purposes.

In 1959, the first integrated circuit was presented by KILBY [13, 14] which was followed by the first microprocessor on a single chip, the 4004 from INTEL in 1971 [2]. This processor series was improved and continued by the 8008 in 1974 and other processors. In 1978, the 8086 [2] was announced and newer and more powerful processors have followed.

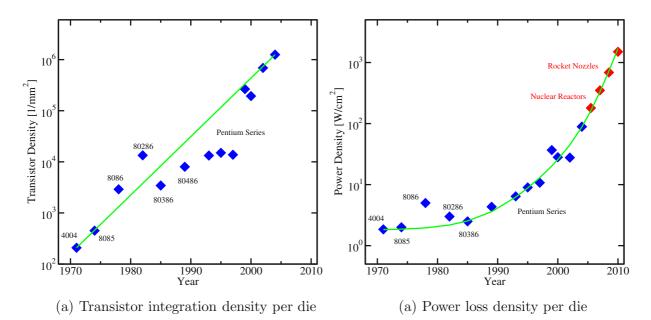

The outlook of MOORE on the future of semiconductors has motivated and forced design and research centers to fulfill the predictions of MOORE. A viewgraph of the achieved enhancements for microprocessors is outlined in Figure 1.1. The current version of the International Technology Roadmap for Semiconductors (ITRS) summarizes the requirements which are mandatory for the future enhancements to obtain the predicted sophistication of semiconductor devices.

Figure 1.1 shows the achievements for microprocessors over the last decades since 1972 [2]. In Figure 1.1a a logarithmic plot shows the transistor density of selected microprocessors versus the year of their announcements. Obviously, the transistor density on die shows an exponential growth. It doubles every 18 months. Figure 1.1b depicts the corresponding power loss densities on these selected microprocessor chips. As it is clearly depicted in Figure 1.1b, the power loss density increases exponentially even on the logarithmic scale. Extrapolated by the current growth

<sup>&</sup>lt;sup>1</sup>Gordon Earl Moore (born January 3, 1929)

Figure 1.1: The chronological evolution of selected microprocessors in terms of transistor integration density per die (a) and the observed power loss density per die (b).

rates and assuming that the past trends in development will continue, we would soon reach power loss densities of nuclear power plants or rocket nozzles in a few years.

With the fast development of the early semiconductor technology in terms of purity of the materials, the integration density, and the complexity of the device structures, new processor types have become possible, e.g. the 80286, 80386, 80486, and today Core2Duo and Core2Quad. In 1975, MOORE's forecast of the electrical operation conditions as well as the package density of the processors from the 1980s were assumed to be highly futuristic and not realizable in terms of former device fabrication processes [8]. However, this vision has come true and the processors were realized in spite of general disbelief and are being constantly improved.

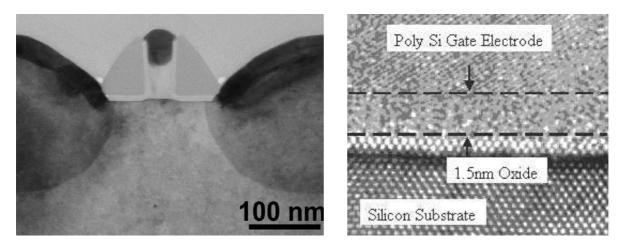

Today, a similar development of the enhancement process can be observed. According to the future predictions of the current ITRS [3], device structures have been proposed which reach or have already gone beyond of the absolute physical constraints for classical devices. For instance, the thicknesses of gate oxides have been successfully reduced to approximately three to four atomic layers of  $SiO_2$  [15, 16] (cf. Figure 1.2), which raises questions about the efficiency due to high leakage currents through these thin layers [17] and long-life reliability [18]. However, for switching transistors used in digital logic devices, the provided functionality is sufficient for reliable operation. This point of view is completely different from ten to twenty years ago, but changing the view point has enabled engineers to find new solutions within these new constraints. From our current understanding, shrinking this type of devices by one more step would result in oxide thicknesses of two atomic layers and the energy barriers in this structure would be far too small for a proper transistor operation. As an alternative to these limits, new materials with a higher dielectric constant are introduced which provide the same capacitance as  $SiO_2$  but with a larger gate dielectric thickness. In order to compare the effective thickness of the gate dielectric, the physical thickness of the gate dielectrics is mapped to the thickness of a  $SiO_2$  layer with the same electrical properties. This thickness is called the effective oxide thickness (EOT).

(a) Structure of a 35 nm MOS transistor

(b) Gate dielectric layer

Figure 1.2: Transmission electron microscopy (TEM) picture of a typical 35 nm MOS transistor [15] (a) and a typical gate dielectric layer structures [16] (b) with a thickness of 1.5 nm.

This example shows the capabilities of how new technologies can exploit certain material properties to enhance the transistor performance and to reduce the area per transistor on a die. In addition, this simple example has shown that the future will bring new paradigms for building and operating electronic devices.

### **1.3** Electrical and Physical Properties

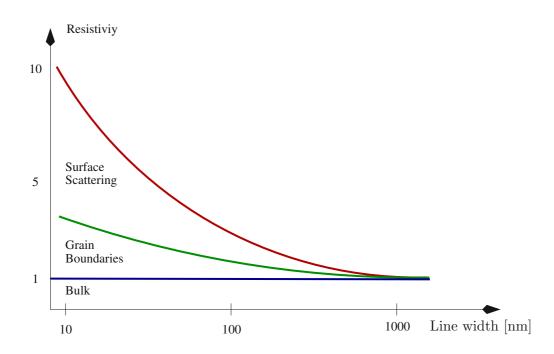

With the same speed as integration density of semiconductor devices increases, the requirements of material properties have to be adjusted accordingly which also implies improvements of fabrication technology in terms of purity of the material sources as well as the uniform applications on reactor-scale. Hence, the fluctuation of the electrical and thermal conductivity and of the permittivity has been dramatically reduced to obtain devices with uniform characteristics and with improved reliability. Many enhancements have been proposed by former editions of the ITRS [10] and most of them have been achieved in advance. Only a few forecasted technologies are missing. Most of the missing parts are related to too high power densities or too high current densities [3]. This lack of achievements leads to more research activities and the rapid development of new types of devices and has pushed the effort to find alternative materials for device interconnect structures [19, 20], dielectrics [21, 22], and for the semiconductor device parts of microelectronic devices [15, 23].

To overcome these types of problems, the current technique is to use other materials which have a better performance than  $SiO_2$ . The requirements for alternatives are to provide a higher dielectric constant, under the constraint that the life-time and the leakage current meet the specifications of the design.

By the introduction of materials with smaller lattice constants, the number of atomic layers slightly increases, but the possible enhancement is less than approximately 20% due to their similar lattice constants compared to that of  $SiO_2$  [24, 25]. To achieve better results for down-scaling, it is necessary to introduce materials which perform better at large thicknesses than

$SiO_2$  but behave similar to  $SiO_2$  in terms of insulation and interface behavior. To choose the appropriate materials for a proper operation of a FET, the value of the control capacitance between the gate and the channel must not fall under a certain threshold value for the capacitance.

The control gate capacitance  $C_{\text{GB}}$  can be roughly estimated by using the formula of a capacitor for parallel plates

$$C_{\rm GB} = \varepsilon_0 \varepsilon_{\rm r} \frac{A}{d}, \qquad (1.1)$$

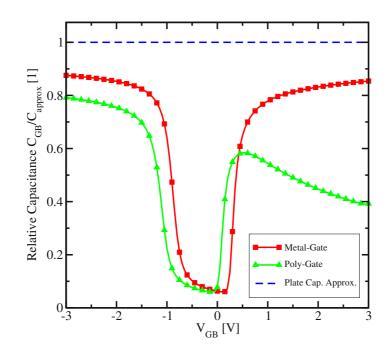

where  $\varepsilon_0$  is the dielectric constant for the matter-free space,  $\varepsilon_r$  the material-specific dielectric constant, A the effective area of the gate electrode, and d the average distance between the gate contact and the channel of the FET. For real devices, the capacitance of the control device is a function of the work function of the gate contact material, the channel doping, and the applied voltage as presented in Figure 1.3. However, to improve the prediction of the electrical behavior of state-of-the-art devices the range of validity has to be considered in advance. For this particular example of a MOS capacitance, a more accurate approach is required to obtain rigorous models for the depletion zones in the gate material for polySi and the voltage dependence of the MOS capacitance structure.

In order to increase the value of the gate capacitance, the area A and the dielectric constant  $\varepsilon_{\rm r}$  have to be increased or the distance of the gate dielectric layer has to be decreased. Due to technology and cost-efficient reasons, the area has to be kept constant. The thickness of the gate dielectric layer cannot be reduced any more due to the hard limit of the lattice constants. The only remaining variable part in (1.1) is the material-specific relative dielectric constant  $\varepsilon_{\rm r}$ . If there exist materials which behave like SiO<sub>2</sub> but have a higher  $\varepsilon_{\rm r}$ , the thickness of the gate dielectric can be increased while the overall gate capacitance remains constant or increases.

Figure 1.3: Capacitance-voltage characteristic of a typical MOS transistor with a gate dielectric thickness of 1.2 nm.

By using materials with lower dielectric constants than  $SiO_2$  the capacitance from (1.1) can be reduced as well. This can be applied for dielectric layers in between of interconnect lines to reduce for instance the cross-talk of these lines due to the reduced dielectrics which are currently widely used in VLSI devices.

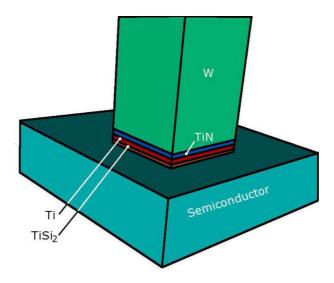

Another considerable performance improvement for VLSI devices was the replacement of Al by Cu for the reduction of the specific line resistivity for high speed applications. This material change has brought many improvements, e.g. less power consumption due to the reduced resistivity of the interconnect lines, but also a lot of new challenges for the device fabrication processes. Hence, due to the higher diffusivity of Cu, new barrier layers had to be introduced [26]. Moreover, for special applications, where the performance of Si-based materials is not sufficiently enough, new materials have been investigated in order to improve the overall performance and in addition also the reliability of these devices.

Some these special applications are memory cells, which require high dielectric constants in order to provide capacitances at very high package densities, so  $SiO_2$  has been partially replaced by Ta compounds [27] or by Perovskite materials<sup>2</sup> [29] for capacitor materials.

All these measures require a considerable effort in terms of development, time, and money. Hence, the industrial manufactures try to exploit the available technology node as long as possible to save money. This sometimes leads to quite unconventional, but very effective results in device designs [30], to new improvements in process technology [31] and material science [32].

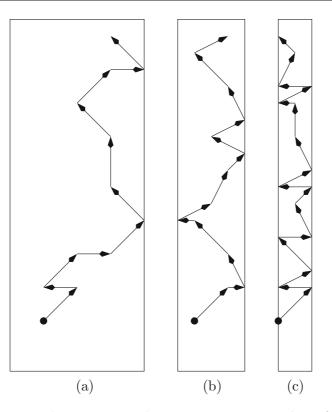

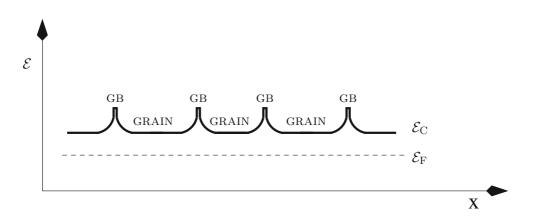

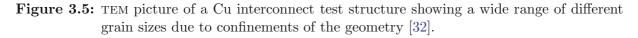

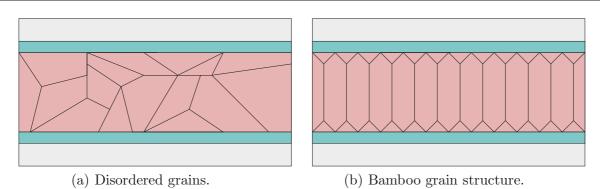

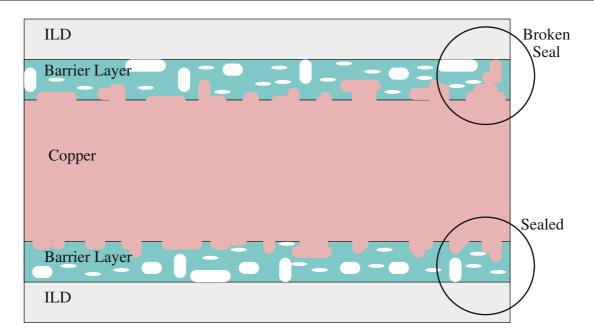

The use of alternative materials has posed new challenges, which have to be identified and considered as well. For instance, the substitution of Al by Cu has increased the conductivity and decreased bulk electromigration and therefore the long-life reliability, but due to technology reasons, parasitic side effects occur at the Cu interfaces [33]. First, Cu easily diffuses into Si and SiO<sub>2</sub> [26, 34, 35]. Therefore, a new barrier layer has to be introduced into the device structure. Moreover, the adhesion between Cu and the barrier layer is quite weak, which causes a high disorder of the crystal lattice structure at the side walls of the metal lines. Hence, high-speed diffusion paths have been established and the desired enhancement of the long-life reliability is not as high as estimated at the introduction of this technology [36].

### **1.4** Thermal Properties and Power Density

The decreasing feature sizes and the increasing integration densities go hand in hand with the increase of power dissipation per unit area. Since the output specifications of electrical circuit designs are kept within the same range of magnitude for backward compatibility, the local power density increases more than exponentially as the device sizes shrink (cf. Figure 1.1 and ITRS [11]).

In the early stages of the microelectronic age, the performance was mainly determined by the achievable electrical properties. Today's microelectronic devices are determined also by thermal issues. The heat produced on the chip has to be transported to the heat sink at the surface of the chip. Since modern chip designs consist of multiple metalization layers, there is the Si substrate on the bottom which is normally thermally connected to a heat sink but at the top side there are only thermally insulating layers which include also the ceramic or plastic package on top of the chip. Hence, the heat is transported through the metal layers because their thermal conductivity is much higher than the thermal conductivity of the insulation layer on the lower side. Due to the heat transport through the metal layers, the metal lines heat up. This leads to

<sup>&</sup>lt;sup>2</sup>The members of the Perovskite group are oxides which follow the general chemical formula  $AXO_3$ , where A is substituted by {Ce, Ca, Na, Sr, Pb, RE} and the X site can be occupied by {Ti, Nb, Fe} [28].

a global warming of the chip which means in the worst case that a single hot spot at one side could determine the temperature of the whole chip, if the heat transport is unfavorably arranged or designed.

To overcome this particular type of design problem, stationary and transient thermal effects have to be included foremost into the device and process simulation models [37–39]. Since the major goal of TCAD applications in the industrial design flow is to obtain sufficiently accurate simulation results in reasonable time, simulation models have to cover the most dominant effects. Many of these effects have been described earlier in a fundamental way. If the physical models are still not accurate enough or are computationally too expensive, parameterized compact models have to be introduced and calibrated to obtain sufficiently accurate results in reasonable time.

The ideal thermal requirements for today's microelectronic devices can be briefly summarized as follows. First, the thermal conductivity of dielectrics or their heat capacitance should be adjustable by choosing different materials which are compatible with other involved metals in terms of fabrication and material interactions. The optimum for the designer engineers would be to choose the materials for interconnects and contacts according to their needs, for instance in terms of electrical or thermal conductivity or according to the material interaction properties. However, since the materials within a certain technology node cannot be arbitrarily chosen, the design engineers have to decide on the best materials according to several technology-dependent constraints, e.g. the thermal budget for the fabrication process, the electrical and thermal load capacity, and other limits which occur at device fabrication processes or during device operation.

Once the materials are chosen, the device can be finally designed. However, after process and device simulations, the results proof whether the designs of the device structures and its chosen materials yield the desired performance and characteristics. Without simulation, the procedure of producing a test wafer to measure the characteristics takes several weeks instead of few minutes or hours. At this stage of development, thermal effects like self-heating, heat conduction, or heat accumulation are commonly neglected or have mostly not been considered correctly using standard design tools. Hence, without electro-thermal simulation or early measures of test devices, unintentional problems might occur within the prototype phase.

### 1.5 Challenges

Due to the high power loss densities in the interconnect structures, the materials for these structures are required to have a high electrical conductivity to provide a good electrical connection between two or more contacts. The heat transfer of the connected contacts has to be reduced or enhanced according to design requirements of the particular device. This requested feature is only possible by changing the material or the material composition in the case of binary or ternary materials. Since the exchange of materials often requires several additional process steps, such design decisions have to be considered carefully due to additional cost. Hence, the achievable optimum device characteristics are often not realizable in terms of given economical constraints. Therefore, other solutions have to be found to implement them in the fabrication process. The first step for the implementation is the determination of the electrical and thermal behavior for non-optimal device structures. Together with given constraints of fabrication and the design requirements, the best solution can be obtained using adaptive optimization strategies provided from state-of-the-art optimization frameworks [40–44].

For changing electrical or economical requirements, a similar optimization procedure can be applied. Because some of those requirements demand alternative materials, various numbers of new materials have been introduced and are gaining more and more importance for future applications. However, their application is very expensive and can be expressed as the "Cost of Ownership" (CoO), which includes the costs for fabrication and for additional precautions like the maximum allowed electrical or thermal burden.

Moreover, many new constraints appear if new materials are considered for optimization. For instance the use of Cu interconnect lines demands additional barrier layers to avoid the diffusion of Cu into the surrounding dielectrics [26]. Therefore, the application of alternative materials like Perovskites [28,29,45] or other high- $\kappa$  materials [22,27,45] or low- $\kappa$  materials [21,46] is very limited with respect to the benefits per costs ratio.

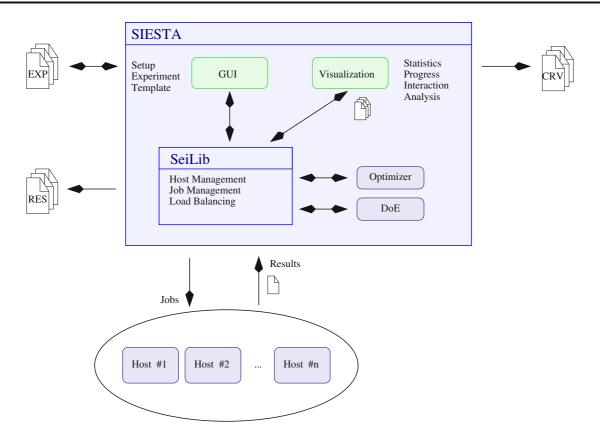

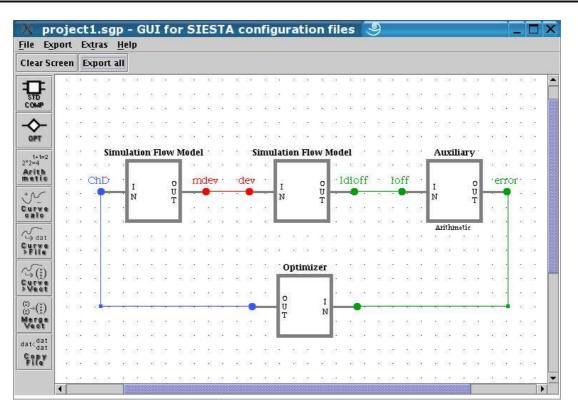

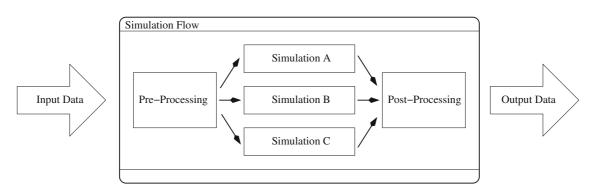

#### Approaches

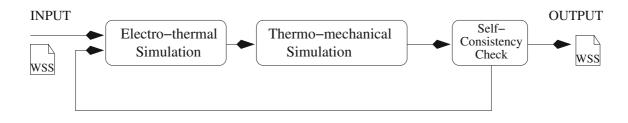

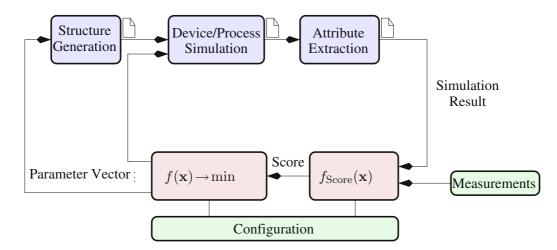

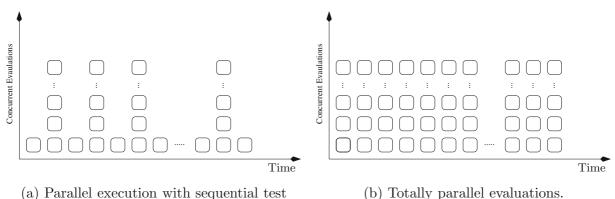

Materials in small device structures underly certain parameter fluctuations as much as bulk materials, but due to the small dimensions of the material regions, the impact of the fluctuations is much higher as compared to bulk material. Hence, fluctuations have to be considered from the beginning of the design. Even if an optimal device has been designed, the characteristic after its fabrication might be completely different. In order to minimize these discrepancies, certain technology-specific constraints have to be introduced which have to be considered within the optimization frameworks to improve the characteristics. To perform the optimization tasks the state-of-the-art simulation and optimization framework Simulation Environment for Semiconductor Technology Analysis (SIESTA) [44] is used and refined in this thesis which provides an open interface that allows to easily add new software tools. SIESTA can be used with several optimization strategies for specific optimization tasks. The optimizer varies and proposes values for the unknown or uncertain parameters. The framework sends the parameters from the optimizer in an appropriate format to the simulators. The simulator may be arranged in a simulation tool flow where the output of one simulator is submitted as the input to another simulation tool. At the end of the simulation flow, the quality of the final simulation result is determined by an objective function which returns a score value which is a quantified representation of the quality of the simulation result. The following presents typical applications in which optimization is used.

Parameter extraction can be used to identify model parameters which are not accurately known [47]. The required input data for this task includes the simulation software with the appropriate models, as well as measurements or reference data to which the simulation result can be compared, and a score function (or objective function) that determines the quality of the simulation result. This extraction mechanism uses the inverse modeling technique [48–50], which is often performed to characterize novel device structures and new materials as well as material compositions in order to develop compact models at a specified scope.

*Calibration* is a special case of the parameter extraction [49]. The range of the uncertain parameters can be further constrained which enables in general faster convergence to complete the calibration task. The main difference between parameter extraction and calibration is that calibration needs a much higher accuracy because the initial guess is normally very close to the optimum, but should be further improved, if for instance a sample has to be calibrated to a certain set of measurements to minimize the model error. Due to the higher quality demands, the determination of the quality of the simulation result is a very critical issue for calibration. These quality criteria (objective or score functions) have to be specified by the user for each particular problem class and tuned for each individual problem. This function can include comparisons of absolute and relative values to calculate a significant metric to determine the quality of the simulation result with respect to reference data.

General optimization is the most general approach and can be used for arbitrary purposes. The optimization is performed until a certain quality criterion has been reached. There exists a wide range of applications for the optimization related to TCAD or electronic devices [51, 52]. More general electronic design purposes have been discussed in [53, 54], and specific optimizers and application for other regimes for instance in economics have been discussed in [55, 56].

With a rigorous implementation of the major aspects occurring in a particular setup problem the optimization framework is able to minimize or maximize certain figures of merit within userdefined specifications. Hence, many trade-offs can be optimized together to obtain a reasonable solutions for the specified problem.

### Chapter 2

# Thermal Effects in Semiconductor Devices

"Alles Vergängliche ist nur ein Gleichnis."

$Johann Wolfgang \ von \ Goethe^1$

ANY CHALLENGES faced in modern semiconductor devices are related to heating phenomena. Since shrinking the device feature size causes higher power loss densities and therefore higher and faster temperature evolution inside the device structure, many additional problems occur due to material-related constraints because the produced heat cannot be transported to the heat sink fast enough. Hence the surrounding device structure heats up and the global microelectronic chip heats up globally.

Since the absolute temperature is not zero, matter is in steady motion at least in terms of BROWN's<sup>2</sup> molecular movements. Therefore, the most probable consequence is that the number of possible states of a closed system, e.g the quantum states, is increasing until a temporary state of thermal equilibrium has been reached. Hence, also the entropy which represents the information about the reachable states in a system is not decreasing spontaneously. This fundamental theorem of thermodynamics and its derivations challenge today's electronic devices including the decrease of the device feature size on the wafer while the ITRS request that the operational current density remains the same. Correspondingly, the power loss density increases quadratically with the reduction of the feature size. Two possible alternatives to overcome these problems are to reduce the supply voltage or the use of alternative materials which produce and inherit less parasitic effects. To describe the general behavior of the electro-magnetic system, fundamental electro-magnetic field equations are given by MAXWELL<sup>3</sup> [58–60] as

$$\nabla \times \mathbf{E} = -\partial_t \mathbf{B},\tag{2.1}$$

$$\nabla \times \mathbf{H} = \mathbf{J} + \partial_t \mathbf{D}, \qquad (2.2)$$

$$\nabla \cdot \mathbf{D} = \rho, \tag{2.3}$$

$$\nabla \cdot \mathbf{B} = 0, \tag{2.4}$$

<sup>&</sup>lt;sup>1</sup>Johann Wolfgang von Goethe (August 28, 1749 – March 22, 1832)

<sup>&</sup>quot;All transitory things are only symbols or reflections." [57]

$<sup>^{2}</sup>$ Robert Brown (December 21, 1773 – June 10, 1858)

<sup>&</sup>lt;sup>3</sup>James Clerk Maxwell (June 13, 1831 – November 5, 1879)

which are independent of the temperature and independent of the type of matter. The quantities **E** and **D** are the electric field and the displacement vector while **H** and **B** are the magnetic field and the magnetic flux density vector, respectively. **J** represents the current density and  $\rho$  the electric space charge density. Information about the material properties is included via the material equations for each region of matter by

$$\mathbf{D} = \tilde{\varepsilon} \cdot \mathbf{E},\tag{2.5}$$

$$\mathbf{J} = \tilde{\sigma} \cdot \mathbf{E},\tag{2.6}$$

$$\mathbf{B} = \tilde{\mu} \cdot \mathbf{H}.\tag{2.7}$$

With these equations, the field quantities and the flux quantities are coupled via the materialdependent parameters  $\tilde{\varepsilon}$ ,  $\tilde{\sigma}$ , and  $\tilde{\mu}$ . Here,  $\tilde{\varepsilon}$  denotes the permittivity tensor,  $\tilde{\sigma}$  the conductivity tensor, and  $\tilde{\mu}$  the permeability tensor. While the MAXWELL equations describe only field properties and field physics, the introduced material parameter tensors  $\tilde{\varepsilon}$ ,  $\tilde{\sigma}$ , and  $\tilde{\mu}$  reflect the material physics and describe the observed material-related phenomena within the involved materials. To complete the equations for the material parameters the heat conduction equation can be derived from FOURIER's<sup>4</sup> law [61]

$$\mathbf{q}_{\rm th} = -\tilde{\lambda} \cdot \nabla T, \qquad (2.8)$$

in which  $\mathbf{q}_{\text{th}}$  represents the local heat flux density. This quantity is proportional to the temperature gradient  $\nabla T$ , where the proportionality factor  $\tilde{\lambda}$  is the thermal conductivity tensor. In conjunction with (2.8), the energy conservation law can be expressed by

$$\nabla \cdot \left( \tilde{\lambda} \cdot \nabla T \right) = \rho_{\rm m} \, c_{\rm p} \, \partial_t T - H_{\rm th}. \tag{2.9}$$

Here,  $\rho_{\rm m}$  denotes the mass density,  $c_{\rm p}$  the specific heat,  $H_{\rm th}$  is the heat generation term, and T the local temperature.

The heat conduction equation (2.9) has some critical quantities: the heat generation  $H_{\rm th}$  term, the thermal conductivity  $\tilde{\lambda}$ , and the specific heat capacitance  $c_{\rm p}$ . The heat generation term  $H_{\rm th}$ is mostly represented by JOULE's<sup>5</sup> power loss (cf. Section 2.2.3). For the thermal conductivity  $\tilde{\lambda}$ and the specific heat capacitance  $c_{\rm p}$  several tables of material parameters exist, which have also different ranges of validity (cf. Section 2.2.1).

In order to describe the behavior of semiconductor devices more specifically, the necessary equations can be derived from MAXWELL's equations [62]. Equation (2.3) and (2.2) are used to derive the continuity equation between the charge carrier current for space charge

$$\nabla \cdot \mathbf{J} + \partial_t \rho = 0, \qquad (2.10)$$

where the space charge density  $\rho$  can be described by the different contributing charge carriers and the net doping

$$\rho = -q (n - p - C_{\text{net}}).$$

(2.11)

Here, q denotes the elementary charge and n, p, and C are the carrier densities for electrons and holes and the net doping density, respectively. The net doping itself can be split into acceptor and donor doping concentrations to account for different dopant species. With a carrier generation

<sup>&</sup>lt;sup>4</sup>Jean Baptiste Joseph Fourier (March 21, 1768 – May 16, 1830)

<sup>&</sup>lt;sup>5</sup>James Prescott Joule (December 24, 1818 – October 11, 1889)

rate G, equation (2.10) can be finally separated into equations for current densities for electrons and holes  $\mathbf{J}_n$  and  $\mathbf{J}_p$ , respectively:

$$\nabla \cdot \mathbf{J}_n = +q \,\partial_t n + q \,G,\tag{2.12}$$

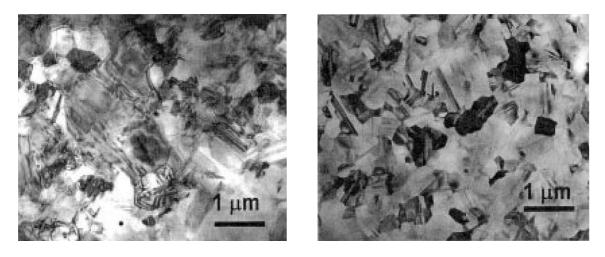

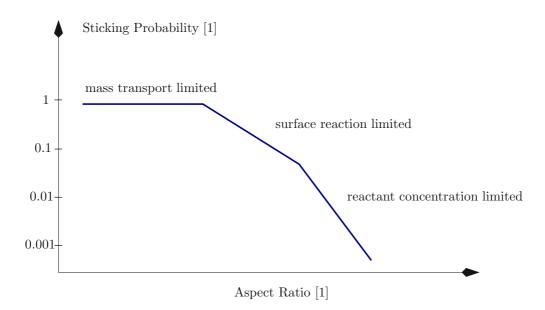

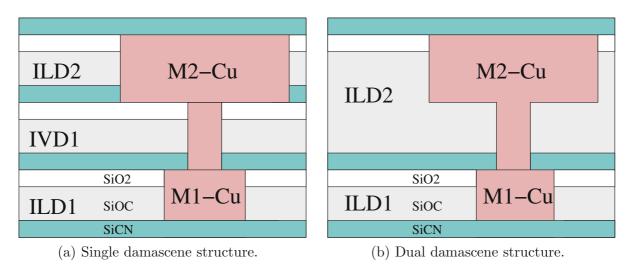

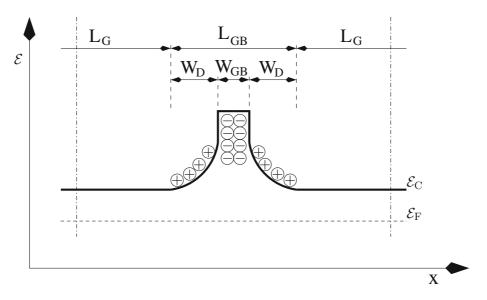

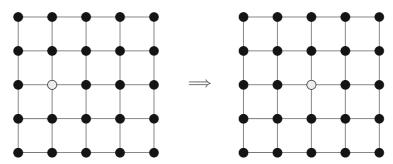

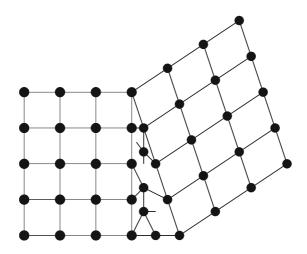

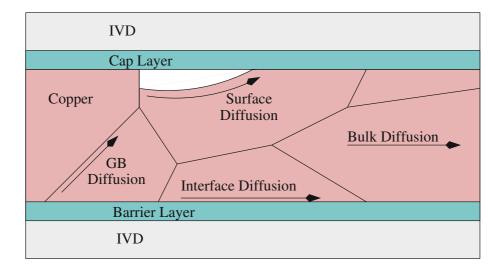

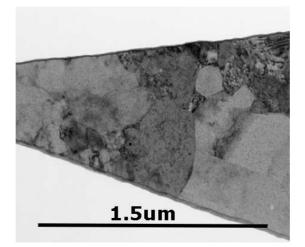

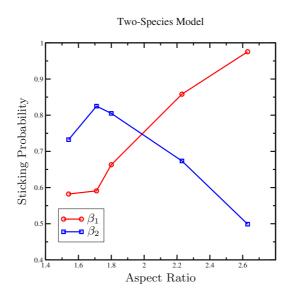

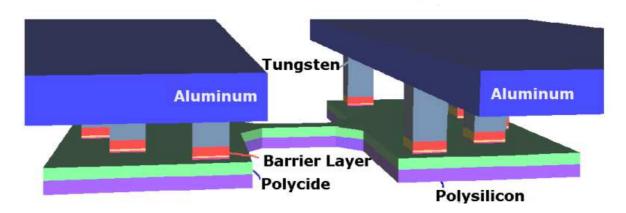

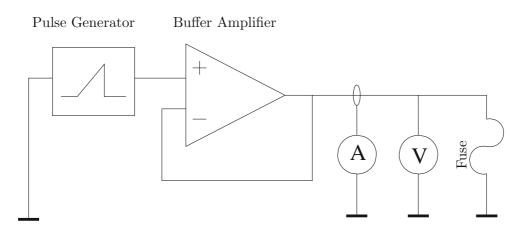

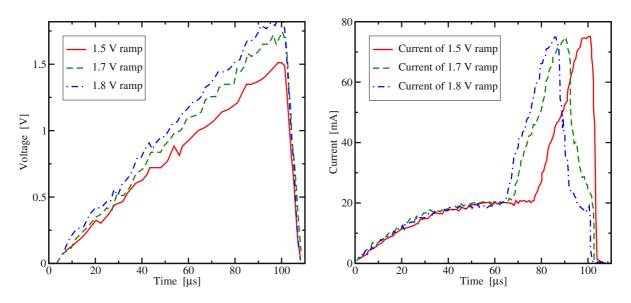

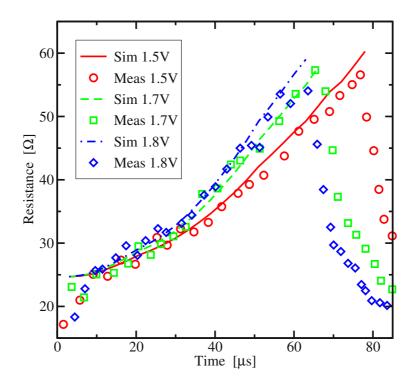

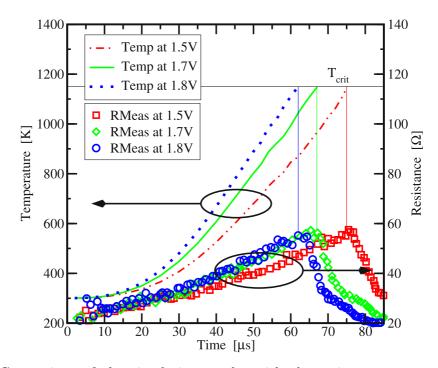

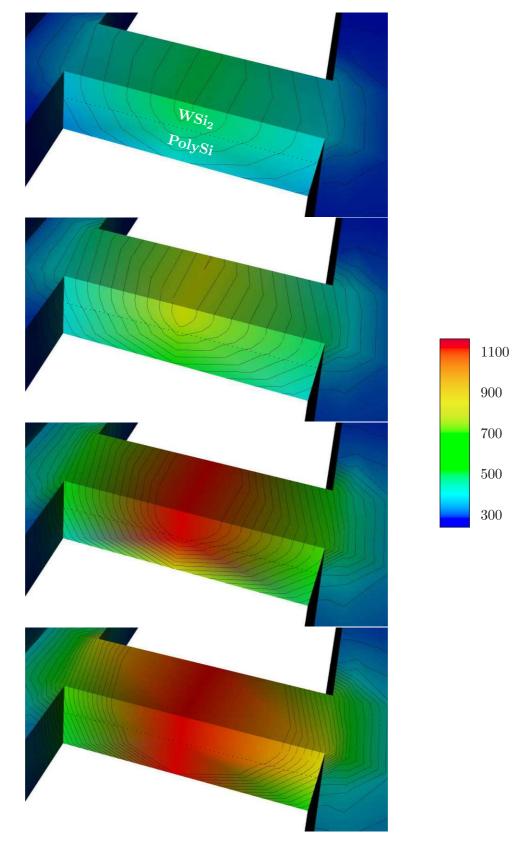

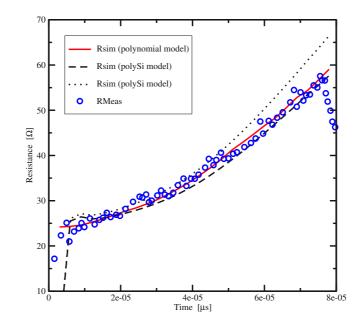

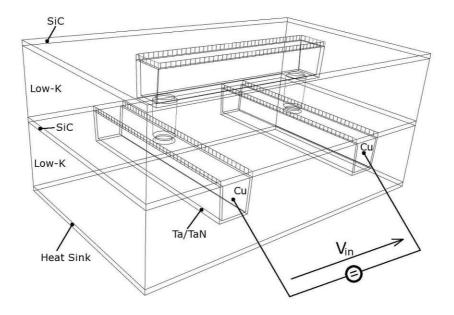

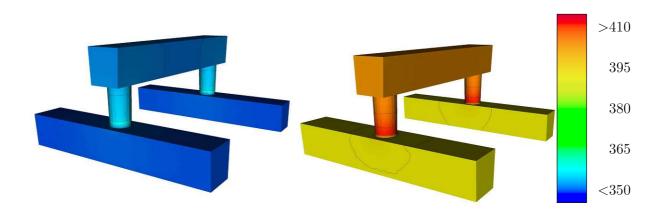

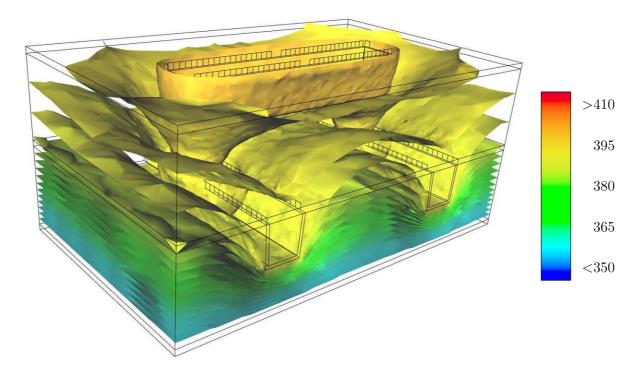

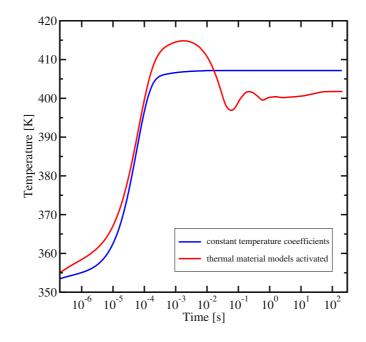

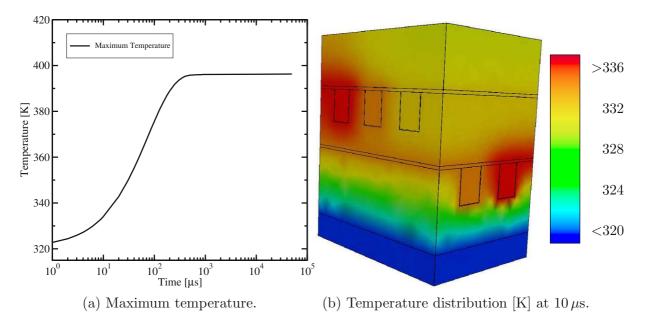

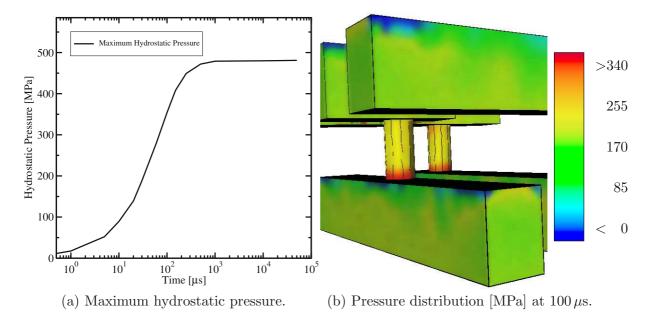

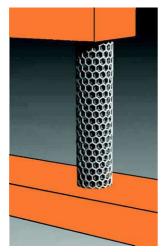

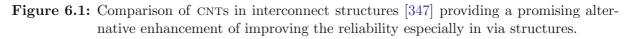

$$\nabla \cdot \mathbf{J}_p = -q \,\partial_t p - q \,G,\tag{2.13}$$