## DISSERTATION

# Integrated Microwave Power Amplifiers

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

ao. Univ. Prof. Dr. Arpad L. Scholtz

E389

Institut für Nachrichtentechnik und Hochfrequenztechnik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

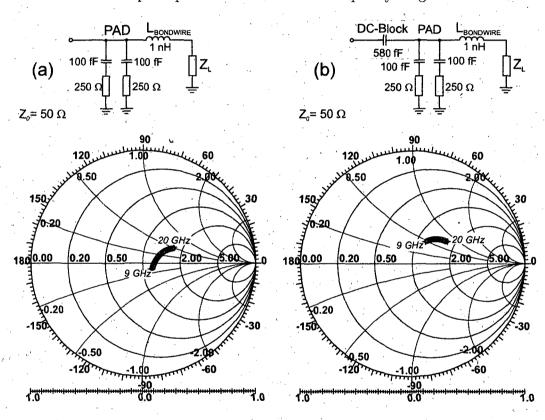

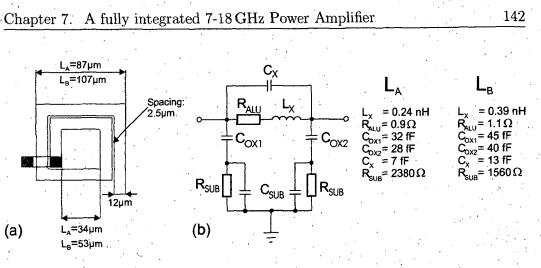

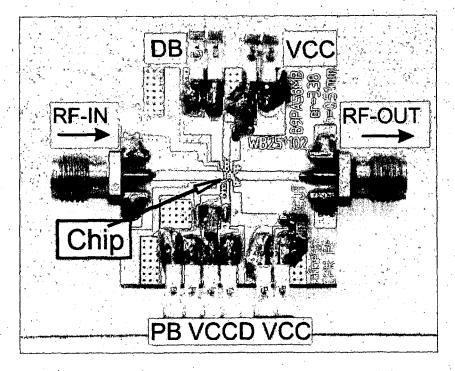

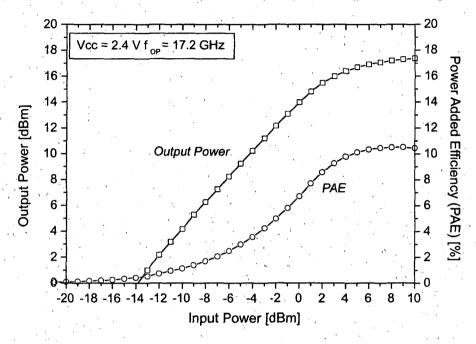

Dipl.-Ing. Winfried Bakalski

von

Matrikelnummer 9527233

Metzstr.26 D-86316 Friedberg

Friedberg, im November 2003

Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at). The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### Abstract

New wireless communication systems like wireless local area networks (wireless LAN, WLAN), satellite communications, wireless point to multipoint radio links, etc. lead to increasing efforts in the development of high-speed semiconductor technologies and RF circuits for these applications. Due to the demand for low-cost solutions and miniaturization, technologies enabling the complete monolithic integration of major RF building blocks on single semiconductor chips are strongly preferred. One of the key RF building blocks is the power amplifier (PA). Due to its position in front of the antenna, is has to fulfill several needs standing in contrary to each other: Low power consumption but high output power levels, or high transistor robustness and high speed efforts or high linearity and high efficiency. Another important task comes from the economic side: Expensive housing or matching networks are not wanted, but a high efficiency is required to face the market. A major limiting factor is the limited quality factor of on-chip passives. So some design techniques have to be considered to relax the limitations. All this, and accurate models for the transistors as well, are required to optimize the design.

The main results are:

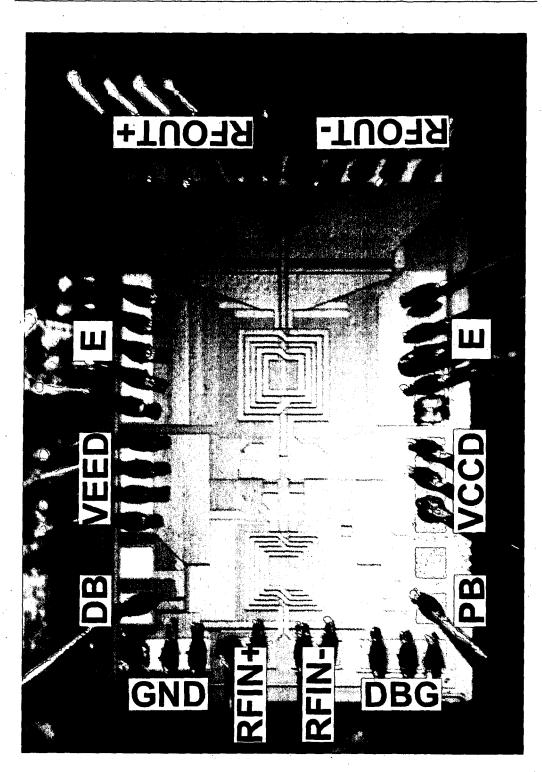

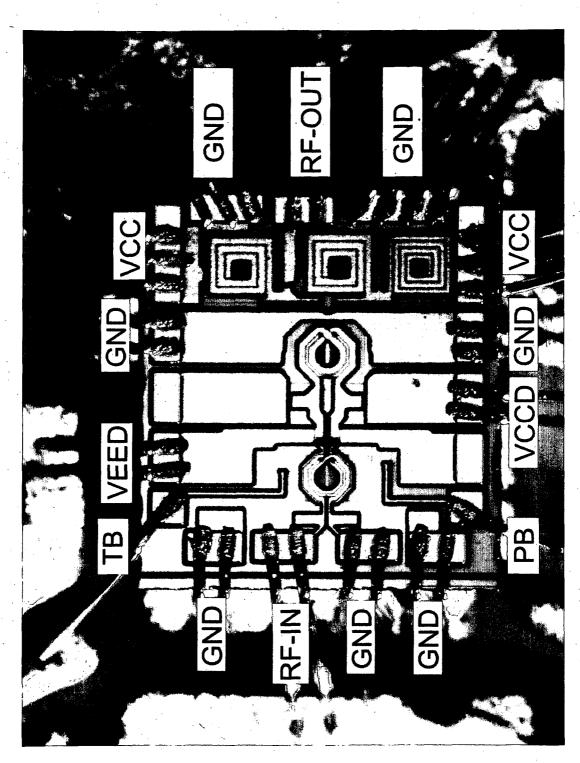

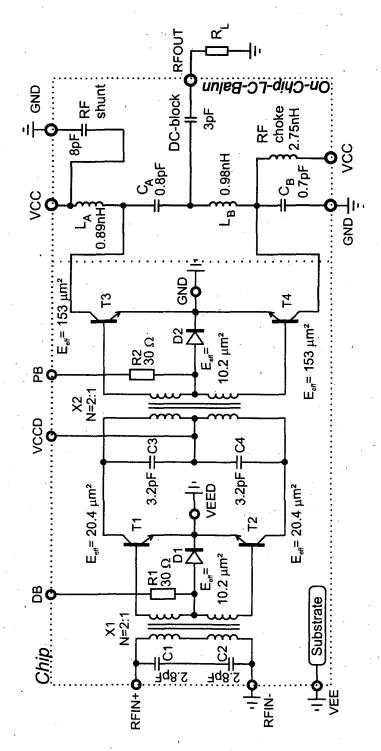

- A highly integrated 2.4 GHz ISM PA with a minimum of external components [Bakalski 02,e, Bakalski 02,d, Bakalski 02,a] is presented. It shows outstanding efficiency performance of over 50% at 2V of supply voltage [Bakalski 02,b].

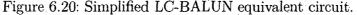

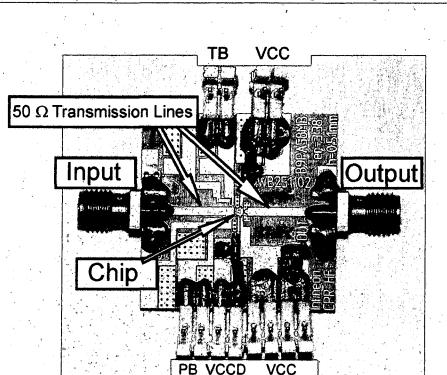

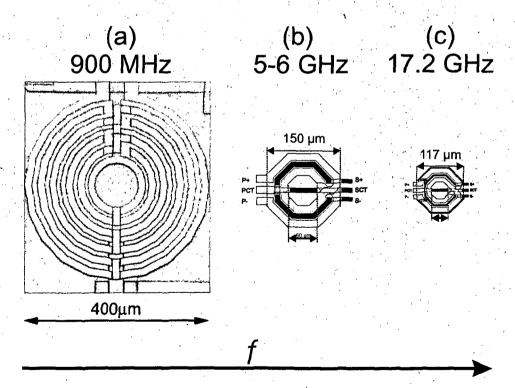

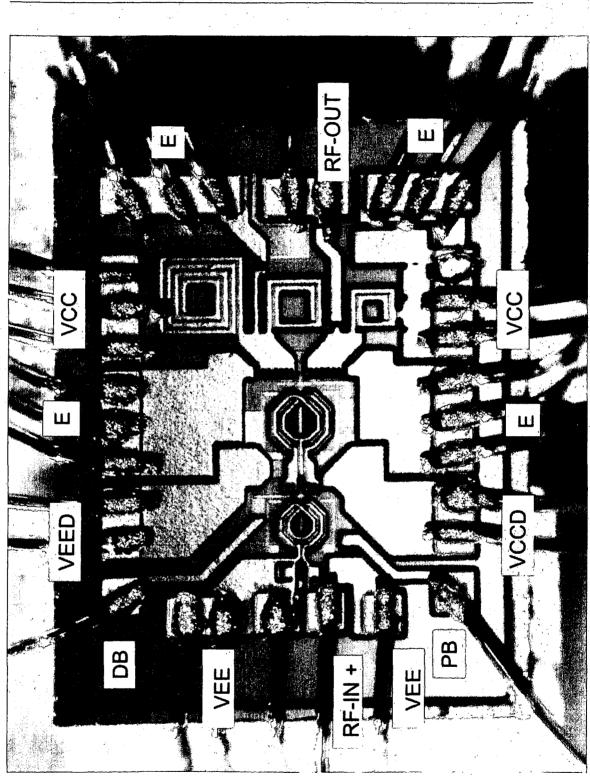

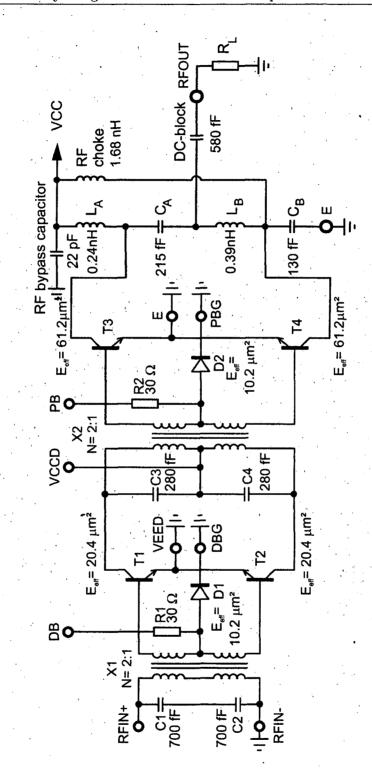

- The first fully-integrated wireless 5.3 GHz LAN PA in SiGe-bipolar technology is developed. It fulfills the needs on linearity and is free of any external matching components including DC-block capacitors [Bakalski 03,b, Bakalski 03,c]. Further it shows almost perfect input and output matching. It features efficiency levels comparable with solutions requiring expensive external networks or ceramics [Bakalski 03,a, Ilkov 03,b, Simbürger 01, Bakalski 02,c].

- The first fully integrated SiGe-bipolar PA working up to 18 GHz is reported. It features as well all matching components integrated on-chip [Bakalski 03,d]. It is an example for the technological limits as it rises up to an  $f_T/f_{op}$  of only about 4.2. It is further an example for the limits in the usage of on-chip transformers.

# Contents

## 1 Introduction

3

| 2   | ŔF    | power amplifier design                                                   | 5    |

|-----|-------|--------------------------------------------------------------------------|------|

|     | 2.1   | RF power amplifier characterization                                      | 5    |

| . , |       | 2.1.1 The power transfer characteristic                                  | 5    |

|     |       | 2.1.2 The frequency response                                             | 7    |

|     | •     | 2.1.3 The third order intercept point (IP3)                              | 8    |

|     |       | 2.1.4 The Error Vector Magnitude (EVM) characterization                  | 12   |

|     |       | 2.1.5 The Power Complementary Cumulative                                 |      |

|     | · ·   | Distribution Function (CCDF)                                             | 16   |

|     |       | 2.1.6 Noise Power Ratio (NPR)                                            | 19   |

|     |       | 2.1.7 Adjacent Channel Power Ratio (ACPR)                                | 19   |

|     |       | 2.1.8 PA ruggedness: Operation into mismatch loads                       |      |

|     | 2.2   | RF power amplifiers topologies                                           |      |

|     |       | 2.2.1 Single-Ended PAs                                                   | 22   |

| · e |       | 2.2.2 Push-Pull PAs                                                      | 24   |

|     | •     | 2.2.3 Balanced PAs                                                       |      |

| •   | 2.3   | Power amplifier classes                                                  | 28   |

|     |       | 2.3.1 Class-A power amplifier                                            | 28   |

|     | , i e | 2.3.2 Class-B and AB power amplifier $\ldots$ $\ldots$ $\ldots$ $\ldots$ |      |

|     |       | 2.3.3 Class-C power amplifier                                            |      |

|     |       | 2.3.4 Class-D power amplifier                                            |      |

|     |       | 2.3.5 Class-E power amplifier                                            |      |

|     |       | 2.3.6 Class-F power amplifier                                            |      |

|     |       | 2.3.7 Class-G/H/S power amplifier                                        | 38   |

| 3   | SiG   | e bipolar transistors                                                    | 41   |

|     | 3.1   | Introduction                                                             | 41   |

|     | 3.2   | Self-aligned Silicon Bipolar Junction Transistors (BJT) and Silicon      |      |

|     |       | Germanium Heterojunction Bipolar Transistors (HBT)                       | 42   |

|     | 3.3   | Compact transistor models                                                | 47 : |

|     | 3.4   | Process technology characteristics                                       |      |

|     | 3.5   | Breakdown effects in bipolar transistors                                 |      |

|     | 3.6   | Breakdown modeling                                                       | 56   |

iii

## List of Abbreviations

| AC             | Alternating Current                                             |

|----------------|-----------------------------------------------------------------|

| ADC            | Analog Digital Converter                                        |

| AF             | Audio Frequency                                                 |

| ACLR           | Adjacent Channel Leakage Ratio                                  |

| ACPR           | Adjacent Channel Power Ratio                                    |

| B6HF           | Infineon silicon bipolar technology with $f_T = 25 \text{ GHz}$ |

| B7HF           | Infineon SiGe bipolar technology with $f_T = 72 \mathrm{GHz}$   |

| BALUN          | BALanced to UNbalanced                                          |

| BICMOS         | Bipolar Complementary Metal Oxide Semiconductor                 |

| BJT            | Bipolar Junction Transistor                                     |

| $\mathbf{C}$   | Capacitance in [F]                                              |

| $\mathrm{CDF}$ | Cumulative Distribution Function                                |

| CCDF           | Complementary Cumulative Distribution Function                  |

| CMOS           | Complementary Metal Oxide Semiconductor                         |

| CSMA/CD        | Carrier Sense Multiple Access with Collision Detection          |

| CW             | Constant Wave (= constant frequency)                            |

| DÁC            | Digital Analog Converter                                        |

| DBPSK          | Differential Binary Phase Shift Keying                          |

| DC             | Direct Current                                                  |

| DQPSK          | Differential Quadrature Phase Shift Keying                      |

| DECT           | Digital Enhanced Cordless Telecommunications                    |

| DSSS           | Direct Sequence Spread Sprectrum                                |

| $\epsilon_r$   | Relative permittivity                                           |

| ESD            | Electrostatic Sensitive Device                                  |

| EVM            | Error Vector Magnitude                                          |

| $f$ , $\cdot$  | Frequency [Hz]                                                  |

| F              | Capacitance in [F]                                              |

| $f_{max}$      | Maximum oscillation frequency in [Hz]                           |

| $f_{Op}$       | Operating frequency in [Hz]                                     |

| $f_T$          | Transit frequency in [Hz]                                       |

| FET            | Field Effect Transistor                                         |

| FHSS           | Frequency Hopping Spread Sprectrum                              |

| GaAs           | Gallium Arsenide                                                |

| GaN            | Gallium Nitride                                                 |

| GSM            | Global System for Mobile Communication                          |

| Н              | Inductance in [H]                                               |

| HBT            | Heterojunction Bipolar Transistor                               |

| HICUM          | High-Current Model                                              |

| IC             | Integrated Circuit                                              |

| ISM            | Industrial Scientific Medical                                   |

iv

| IMD                  | InterModulation Distance                                       |

|----------------------|----------------------------------------------------------------|

| InP                  | Indium Phosphite                                               |

| IP3                  | Third order intermodulation point                              |

| L                    | Inductance in [H]                                              |

| $\overline{\lambda}$ | Wavelength in [m]                                              |

| LDMOS                | Laterally Diffused Metal Oxide Semiconductor                   |

| LNA                  | Low Noise Amplifier                                            |

| LOCOS                | LOCal Oxidation of Silicon                                     |

| LTCC                 | Low Temperature Cofired Ceramics                               |

| n                    | Turn ratio                                                     |

| N                    | Number of turns                                                |

| NPR                  | Noise Power Ratio                                              |

| $\mu$                | Permeability in [Vs/Am]                                        |

| MEXTRAM              | Most $Exquisite Transistor Model$                              |

| MIM                  | Metal Isolator Metal                                           |

| MOS                  | Metal Oxide Semiconductor                                      |

| OFDM                 | Orthogonal Frequency Division Multiplex                        |

| PA                   | Power Amplifier                                                |

| PAE                  | Power Added Efficiency                                         |

| PCB                  | Printed Circuit Board                                          |

| PHEMT                | Pseudomorphic High Eelectron Mobility Transistor               |

| PWM                  | Pulse Width Modulation                                         |

| QAM                  | Quadrature Amplitude Modulation                                |

| $\mathbf{RF}$        | Radio Frequency                                                |

| RMS                  | Root Mean Square                                               |

| ρ                    | Reflection coefficient                                         |

| SEG                  | Selective Epitaxial Growth                                     |

| SiGe                 | Silicon Germanium                                              |

| SGP'                 | SPICE Gummel Poon model                                        |

| SMA                  | $SubMiniatur A$ : Standard RF connector up to $18 \mathrm{GH}$ |

| SMD                  | Surface Mounted Device                                         |

| SPICE                | Simultion Program with Integrated Circuit Emphasis             |

| Tranceiver           | TRANS mitter and re $CEIVER$                                   |

| VBIC                 | Vertical Bipolar Inter-Company model                           |

| VSWR                 | Voltage Standing Wave Ratio                                    |

| WLAN                 | Wireless Local Area Network                                    |

| $\omega_{\perp}$     | angular frequency                                              |

| Z                    | complex impedance in $[\Omega]$                                |

|                      |                                                                |

## Chapter 1

## Introduction

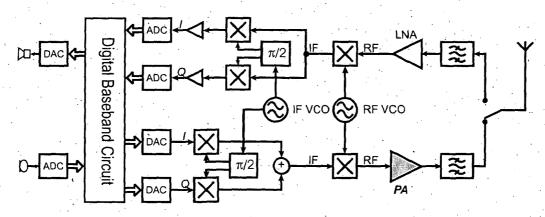

Every wireless communication system consists of different radio frequency (RF) and base band building blocks describing in sum a transceiver (*trans*mitter receiver). The RF building blocks are shown in fig. 1.1. The digital part containing the base band circuit of a modern communication system ends with its Analog/Digital converters. Due to the fact that the design of A/D converters is limited in speed, accuracy (e.g. quantization errors, noise..) [Schweinzer 96], a certain range in its resolution and the power consumption for fast converters, it is only possible to design "software radio" for a certain frequency range. Today, there only exist a small amount of real "software radios", such as shortwave receivers for frequencies up to 30 MHz [Cuno 03]. As today's mobile applications all can be found in the frequency range from 430 MHz to several GHz, it is obvious that there must be analog RF circuits outside the base band.

Figure 1.1: Block Diagram of a typical wireless digital communications tranceiver.

The power amplifier (PA) is one of the main building blocks of a radio frequency (RF) wireless communication system. Different to other amplifiers types, it has the focus on delivering high output power, as it usually has to drive the antenna.

#### Chapter 1. Introduction

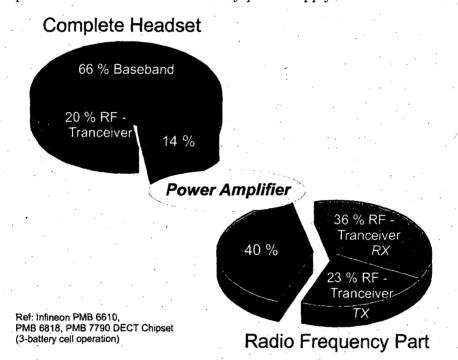

The PA can be found in front of the antenna switch. As well as other building blocks there are several aims in the design of the PA, caused by the needs for its applications. Besides the necessary output power level, which can be limited by technology as well as specifications and law reglementations, it usually has to meet linearity specifications and/or efficiency specifications. Due to the fact, that the PA together with processor are mainly responsible for the system power consumption it is quite obvious, that efficiency means battery life time. Figure 1.2 shows the power consumption statistics of a DECT wireless telephone headset chipset. In this example, three battery cell operation is estimated, as lower supply voltage causes the use of DC/DC converters lowering the efficiencies for certain building blocks such as the transceiver chip. It shows, that even for a wireless communication system like DECT with low output power levels, the PA requires about up to half of the whole RF circuitry power supply.

Figure 1.2: Power consumption statistics for a DECT headset chipset. (Infineon PMB 6610 tranceiver, PMB 6818 PA and PMB 7790 DECT Controller). The average power consumption values represent the normal operation mode with the PA being half time at low power and half time in high power mode.

As the PA is one of the main keys to reduce power consumption, it is necessary to improve the efficiency as much as possible. This includes also the use of efficient matching networks, switches and antennas [Krischke 95, Cripps 99, Gonzales 84, Vizmuller 95, Johnson 84, Bonek 00, Ilkov 03,b, Ilkov 03,a, Bakalski 02,e, Bakalski 02,d, Bakalski 02,a]. Another task is the linearity: New OFDM systems require highly linear PAs to guarantee the system performance. The more frequency carrier or

#### Chapter 1. Introduction

symbols [Agilent 02,a] are used, the tougher the linearity efforts become.

In the past years, a lot of design philosophies for power amplifiers have become feasible. Basically there exist three topologies and a lot of amplifier classes delivering a rough description of the used design. Chapter 2 gives an overview of PA characteriziation, the topologies and different classes used to categorize the design. However all these rely on the used semiconductor technology. An overview of the Si-based bipolar processes used for this thesis will be given in Chapter 3. Of course, the reason for the wide range of different technologies is not only for circuit design or technological reasons: The cheaper the building blocks can be produced, the easier a wireless system can be accepted by the market, as the products become affordable. The economic side cannot be neglected.

Currently, the market of PAs for mobile wireless applications is dominated mainly by GaAs or InP derivate technologies [Raab 03], the so-called III-V technologies<sup>1</sup>. It is a difficult task to compare the cost of different technologies per chip, as they depend on a lot of factors such as wafer size, mask resolution, amount of pieces to be produced and so on. Typically the cost of InP based chips is about 8 times higher than for standard Si-bipolar and GaAs based chips about 4 times higher. Typical III-V transistors are the HEMT (High Electron Mobility Transistor) and the HBT (Heterojunction Bipolar Transistor). III-V compound devices have typically lower packing densities and lower yields, increasing their per piece prices. The calculation for CMOS based circuits is much more difficult, as the circuits are more and more a mixture between baseband and RF circuits. While digital circuits can be scaled down very well by decreasing the structure size, this is not really possible for RF circuits, as components like inductors or capacitors cannot be scaled down, because of the fixed operating frequency. The main cost factor on very-large scaled CMOS processes today is the price for mask sets which are typically 10-15 times higher than in Si/SiGe-bipolar processes considering today's 120 nm CMOS processes. They become efficient only for very high production volumes. It has to be mentioned that the maximum yield and the different wafer sizes make a calculation difficult. For cheaper mass production usage there exist only a small amount of solutions on standard CMOS, Si or SiGe based power amplifiers [Aoki 01, Baltus 01, Parkhurst 98, Vathulya 01, Simbürger 00,a, Simbürger 01, Bakalski 02,c, Bakalski 02,b]. Especially [Vathulya 01] shows the basic problems in the design of CMOS PAs: The gate oxide breakdown and the hot carrier effect, which is a knock-out criterion for reliability issues. Other PA technologies featuring a high ruggedness such as LDMOS (Laterally Diffused MOS) are limited to lower microwave frequencies (typically 2 GHz) due to their direct grounding in its source eliminating bondwire inductances used to produce a negative feedback. Thus the gain at high frequencies is reduced [Raab 03].

Furthermore, it is also necessary to mention, that the highest possible integration is an important task to fulfill the market needs. Chips using a sec-

<sup>&</sup>lt;sup>1</sup>III-V: Description for the used elements of the chemical periodical system. The roman number tells the used material group. e.g. Ga = III, As = V, In = III, P = V

#### Chapter 1. Introduction

ond integrated circuit for negative bias voltages, such as in most GaAs MMIC PHEMT technology based amplifiers like [Raytheon 02], will not survive the next years, as packaging is an important cost factor as well as the used semiconductor technology. This implies that the full integration of all matching networks into the PCB [Weber 97, Simbürger 00,a, Simbürger 01, Bakalski 02,c, Bakalski 02,b], module [Yoshida 98, Bakalski 03,a, Ilkov 03,b, Ilkov 03,a] or even the die [Aoki 01, Bakalski 03,c, Bakalski 03,b, Bakalski 03,d] should be the next step in RF integration. An introduction on matching networks for the output and on-chip matching can be found in Chapter 4.

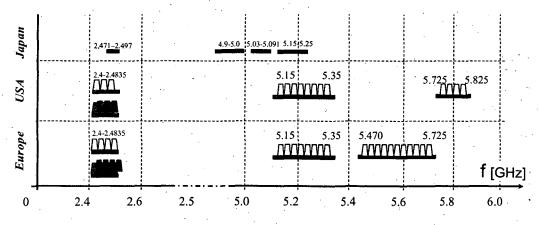

This work presents some issues in the successful integration of matching components as well as the implementation of power amplifier techniques on standard SiGe-based technologies. It starts up in Chapter 5 with a design for the 2.4 GHz ISM band [Bakalski 02,c, Bakalski 02,b], where wireless systems like Bluetooth and Wireless LAN or even wireless telephones are typical examples for its usage. In Chapter 6, a 5 GHz wireless LAN amplifier [Bakalski 03,c, Bakalski 03,b] is presented. As higher frequencies imply smaller wave lengths, the required chip area for matching networks decreases. Therefore it is an important task to include as much matching network onto the die if possible, as packaging becomes a difficult task at high frequencies. Finally Chapter 7 presents a 17.2 GHz PA or driver design for future wireless LAN applications [Bakalski 03,d]. It is also an example, in which range transformers as matching networks could be used.

## Chapter 2

## RF power amplifier design

## 2.1 RF power amplifier characterization

Power amplifiers have their usage on the most different applications. Therefore it is necessary to characterize them to fit the right design into the right system. The following sections should give a brief introduction in typical characterization methods.

#### 2.1.1 The power transfer characteristic

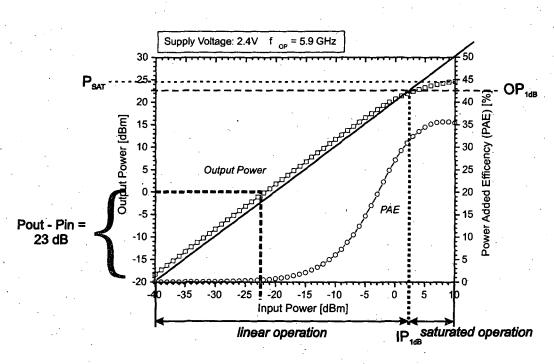

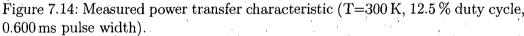

The power transfer characteristic curve represents the plot of the output power over the input power. A typical example for such a curve can be found in fig. 2.1.

This plot is one of the most often found in all application notes and datasheets. It is possible to get the information on small signal gain, the 1 dB compression point (P1dB) and the saturated output power  $(P_{SAT})$ . In some cases oscillation problems at the operation frequency are as well obtained (when the output power does not converge to 0 if no input power is supplied).

The small signal gain can be read out of the curve in the linear region (fig. 2.1). The linear region is found for an input power range beginning above the noise floor and ending up into the compression. In this area, the small signal gain is obtained by the difference between output power and input power:

$$G[dB] = P_{OUT,LIN}[dBm] - P_{IN,LIN}[dBm]$$

(2.1)

In addition, there exists also the saturated gain:

$$G_{SAT}[dB] = P_{OUT,SAT} [dBm] - P_{IN,SAT} [dBm]$$

(2.2)

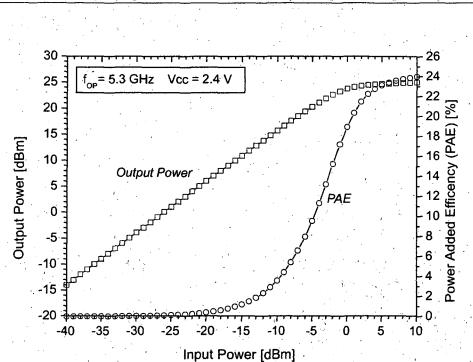

Figure 2.1: A typical PA power transfer characteristic plot [Bakalski 03,a].

Usually this definition is often used for systems operating with a saturated power amplifier (PA), such as GSM.

The point where the PA is driven into the compression is named the 1dB compression point: It describes, for which power level the small signal gain is reduced by 1dB. Concerning the output power it is the 1dB output compression point (OP1dB) and for the input power the 1dB input compression point (IP1dB):

$$OP1dB [dBm] = IP1dB [dBm] + G [dB] - 1 dB$$

(2.3)

Using the power transfer characteristic plot, the 1 dB compression point can be observed by adding a linear help line with the slope of 1 representing a small signal gain (G) lowered by 1 dB (offset of the help line): The cross of this line with the power transfer characteristic curve gives the 1 dB compression point (P1dB) (fig. 2.1). Finally, the saturated output power can be found as well: The absolute maximum output power level the PA is able to deliver. This information is usually necessary for the dimensioning of the PA output stage. Chapter 2.2 shows some issues on it based on the selected PA topology.

Figure 2.1 also shows the Power Added Efficiency (PAE) curve. This curve represents the overall efficiency of a PA. It is defined by the quotient of the output power divided by all input power the circuit is feeded with [Raab 03]:

$$PAE = \frac{P_{OUT}}{P_{DC} + P_{IN}}$$

(2.4)

where  $P_{DC}$  stands for the DC supply from the power supply,  $P_{IN}$  for the input power and  $P_{OUT}$  for the output power. In the case of high gain, the power added efficiency can also be simplified to

$$PAE \approx \frac{P_{OUT}}{P_{DC}}$$

(2.5)

which is the definition for the *DC-to-RF Efficiency* or often only called *Efficiency*. If the PA has a gain over 20 dB so that the RF input power can be neglected, the PAE is the same as the DC-to-RF efficiency. It has theoretical limits, and each amplifier class implies the maximum efficiency for the case that all components being assumed to work ideal. The amplifier classes are described in section 2.3.

Another term often found in PA circuits is the collector efficiency CE for circuits using bipolar junction transistors (BJT) and the drain efficiency DE for field effect transistors (FET). It is defined by the output power divided by the power supply of the transistor without bias-currents:

$$CE = \frac{P_{OUT}}{P_{DC,Transistor}} = \frac{P_{OUT}}{V_{CC} \cdot I_C}$$

(2.6)

for BJTs with  $I_C$  representing the collector current and  $V_{CC}$  for the supply voltage.

$$DE = \frac{P_{OUT}}{P_{DC Transistar}} = \frac{P_{OUT}}{V_{DD} I_D}$$

(2.7)

for FETs with  $I_D$  representing the drain current and  $V_{DD}$  for the supply voltage. Furthermore there exist efficiency definitions considering the average efficiency, as PAs are often used for a certain range of different input power levels. The average efficiency is defined by

$$\eta_{AVG} = \frac{P_{OUT,AVG}}{P_{IN,AVG}} \tag{2.8}$$

The average power levels are usually determined by probability functions based on the used modulation scheme.

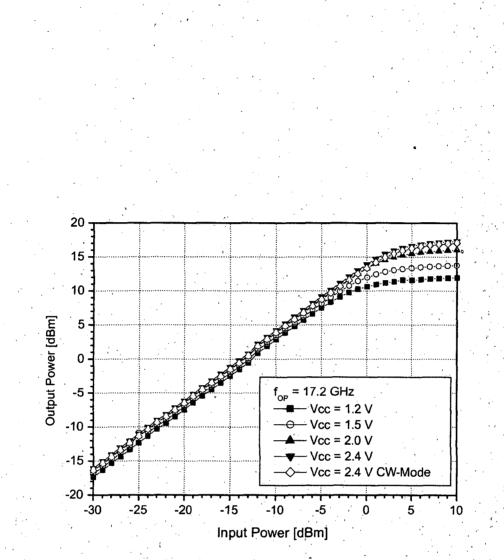

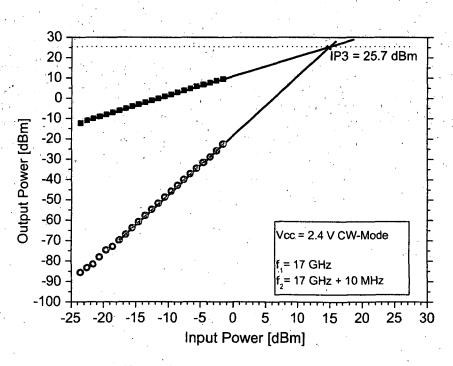

#### 2.1.2 The frequency response

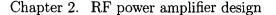

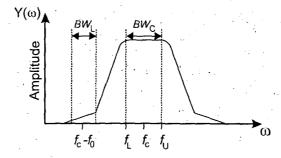

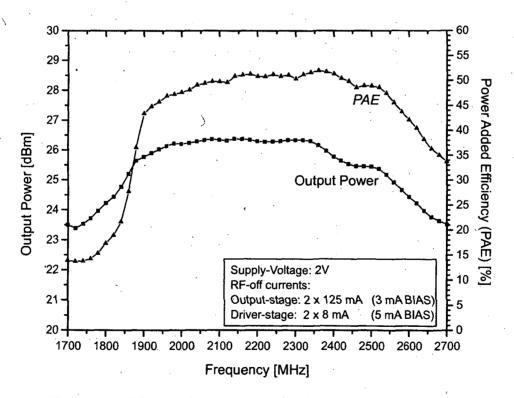

Every RF PA has a certain operating frequency range, for which it is designed. Depending on the used matching and the center operation frequency the bandwidth can vary quite much. Figure 2.2 shows a typical frequency response plot for a narrow-band PA [Simbürger 01].

In this example the 3 dB bandwidth can be read out quite simple: Just examine the frequency where the output power is going down about 3 dB (the half output

Figure 2.2: A typical PA frequency response plot.

power). The resulting frequency range gives the 3dB bandwidth. Usually the range of operation depends on the application: For linear multicarrier systems the output power deviation has to be much smaller to satisfy conditions like Error Vector Magnitude (EVM) (described in 2.1.4 or [Agilent 02,b]). Hereby the usable bandwidth is narrowed much more, so that the bandwidth is for example a 1dB-bandwidth.

#### 2.1.3 The third order intercept point (IP3)

Linear PAs gain more and more importance, as new communications systems like Wireless LAN require a high linearity to ensure proper operation. The most popular linearity measurement is the intermodulation measurement on third order interception (IP3). It gives the output power level (OIP3), when the third order intermodulation product reaches the fundamental frequency output power level (fig. 2.5). This level usually cannot be reached, as the amplifier saturates much earlier. It is observed by considering a nonlinear amplifier, or in the simplest case, a nonlinear transistor: The nonlinear transistor curve or PA curve can be formally written as

$$I_C = A_1 U_{BE} + A_2 U_{BE}^2 + A_3 U_{BE}^3 + \dots$$

(2.9)

with  $I_C$  for the Collector current of a bipolar transistor and  $U_{BE}$  for the input voltage between Base and Emitter.

Applying two signals with a different frequency <sup>1</sup> on the input of the PA,

$$U_{BE} = U_1 \cos(\omega_1 t) + U_2 \cos(\omega_2 t)$$

(2.10)

with  $\omega_1 - \omega_2 \ll \omega_1, \omega_2$ , the output current of the transistor is

$$I_{C} = A_{1}[U_{1}\cos(\omega_{1}t) + U_{2}\cos(\omega_{2}t)] + A_{2}[U_{1}^{2}\cos^{2}(\omega_{1}t) + U_{2}^{2}\cos^{2}(\omega_{2}t)^{2} + 2U_{1}U_{2}\cos(\omega_{1}t)U_{2}\cos(\omega_{2}t)] + A_{3}[U_{1}^{3}\cos^{3}(\omega_{1}t) + U_{2}^{3}\cos^{3}(\omega_{2}t) + 3U_{1}^{2}U_{2}\cos^{2}(\omega_{1}t)\cos(\omega_{2}t) + 3U_{1}U_{2}^{2}\cos(\omega_{1}t)\cos^{2}(\omega_{2}t)] + 3U_{1}U_{2}^{2}\cos(\omega_{1}t)\cos^{2}(\omega_{2}t)] + C_{2}^{3}\cos^{2}(\omega_{2}t) + C_{2}^{3}\cos^{2}(\omega_{2$$

Using the additional theorems [Bartsch 99] on eqn. 2.11, the spectral parts of the output signal are easy to obtain with the dependence on linear, quadratic, cubic and other parts:

$$I_C = 1$$

linear term:  $A_{1}[U_{1}\cos(\omega_{1}t) + U_{2}\cos(\omega_{2}t)] + \frac{1}{2}A_{2}[U_{1}^{2}(1 + \cos(2\omega_{1}t) + 2U_{1}U_{2}((\cos(\omega_{1} - \omega_{2})t + \cos(\omega_{1} + \omega_{2})t) + U_{2}^{2}(1 + \cos(2\omega_{2}t)] + \frac{1}{2}U_{2}^{2}(1 + \cos(2\omega_{2}t)] + \frac{1}{4}U_{2}^{3}((3\cos(\omega_{2}t) + \cos(3\omega_{2}t)) + \frac{1}{3}U_{1}^{2}U_{2}(\cos(\omega_{1}t) + \cos(3\omega_{1}t)) + \frac{1}{4}U_{2}^{3}((3\cos(\omega_{2}t) + \cos(3\omega_{2}t)) + \frac{1}{3}U_{1}^{2}U_{2}(\cos(\omega_{2}t) + \frac{1}{2}\cos(2\omega_{1} - \omega_{2})t + \frac{1}{2}\cos(2\omega_{2} - \omega_{1})t + \frac{1}{2}U_{2}^{2}(\cos(2\omega_{2} + \omega_{1})t)] + \frac{1}{2}U_{1}^{2}U_{2}(\cos(\omega_{1}t) + \frac{1}{2}\cos(2\omega_{2} - \omega_{1})t + \frac{1}{2}\cos(2\cos(2\omega_{2} + \omega_{1})t)] + \dots$ (2.12)

With this, the spectral parts that could be found in term 2.12 are:

| linear term    | $\omega_1,\omega_2$                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| quadratic term | DC, $\mid \omega_1 - \omega_2 \mid$ , $\mid \omega_1 + \omega_2 \mid$ , $2\omega_1$ , $2\omega_2$                                      |

| cubic term     | $\omega_1, \omega_2,  2\omega_1 - \omega_2 ,  \omega_1 - 2\omega_2 , 2\omega_1 + \omega_2, \omega_1 + 2\omega_2, 3\omega_1, 3\omega_2$ |

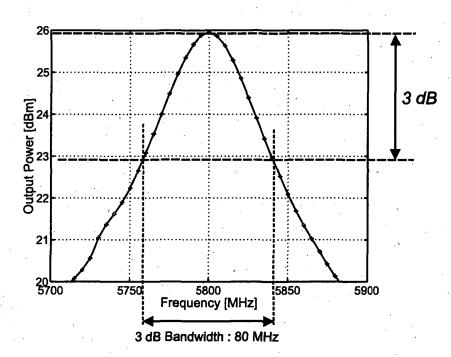

The resulting spectrum of an amplifier with a quadratic and cubic nonlinearity can be found in figure 2.3. The output power is plotted logarithmic [dBm], and some of the third order intermodulation products can be found in the operating frequency area causing errors in the output signal. The distance between the output power at the fundamental frequency and its unwanted intermodulation products is called the intermodulation distance IM3 for 3rd order and IM5 for 5th order intermodulation products.

(2.11)

<sup>&</sup>lt;sup>1</sup>usually the same amplitude to simplify the measurements

Figure 2.3: Output spectrum of a nonlinear PA: quadratic and cubic nonlinearity are shown.

There exists also another description for the intermodulation distance: The carrier to intermodulation ratio C/I. Hereby the C/I ratio describes the distance between carrier and all intermodulation products. Figure 2.4 shows a typical measurement setup for measuring the third order intermodulation point.

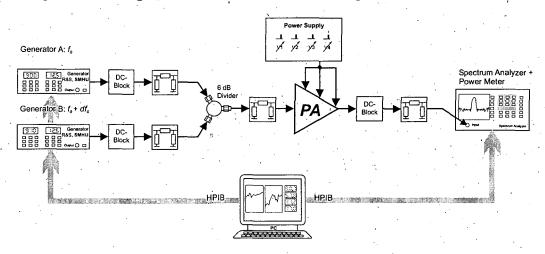

Figure 2.4: Two Tone measurement setup for the third order Intermodulation point.

In this setup two similar generators with a small frequency difference<sup>2</sup> are used for the IP3 measurement. To prevent any measurement errors, a lot of attenuators have to be used between the stages. This ensures that the generators and the device under test, the PA are loaded with  $50 \Omega$  loads everywhere. This is

$^{2}$ typically 10 MHz, depending on the spectrum analyzer accuracy and frequency resolution

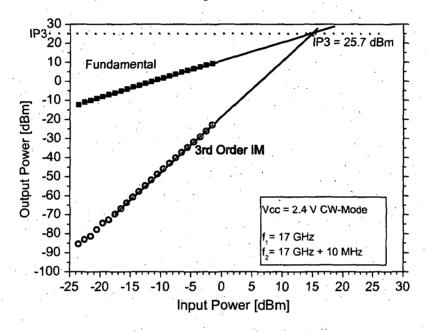

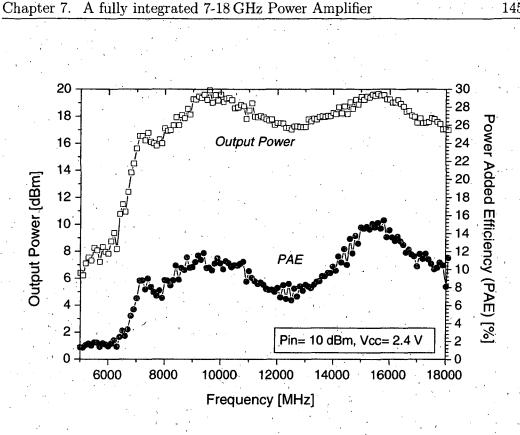

important, as mismatched generators itself and in combination with mismatched hybrids can cause additional intermodulation not caused by the PA. Especially at the input of the PA the signal has to be checked for such effects. Figure 2.5 shows a typical IP3 plot for a 17 GHz PA [Bakalski 03,d] using this setup. Due to the limited output power of the generators and the high attenuation, the saturated region of the PA is not reached by the fundamental frequency power transfer characteristic. The 3rd order intermodulation point IP3 is defined by the crossing of the fundamental frequency and the 3rd order intermodulation curve for the linear operated region (non-saturated). It is important to mention, that the 3rd order intermodulation *must* have a slope of 3.

Figure 2.5: IP3 measurement of a 17 GHz PA [Bakalski 03,d].

The cross of the fundamental transfer characteristic with the 3rd order intermodulation slope implies in fig. 2.5, that the output IP3 can be easily calculated by the measurement of only two power levels using a spectrum analyser:

$$IM3[dB] = P(f_2)[dBm] - P(2f_2 - \omega_1)[dBm]$$

(2.13)

$$OIP3[dBm] \approx P(f_2) [dBm] + \frac{1}{2} \cdot IM3 [dB]$$

(2.14)

Measuring just two power levels below the OP1dB compression point allows to estimate the OIP3. It has to mentioned that using eqn. 2.14 is only valid if the measured power levels fit exactly to the slopes of 1 and 3 respectively.

### 2.1.4 The Error Vector Magnitude (EVM) characterization

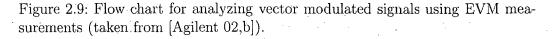

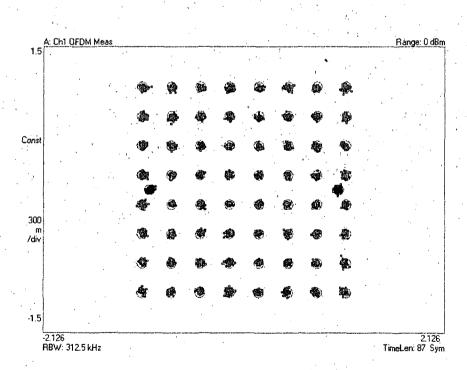

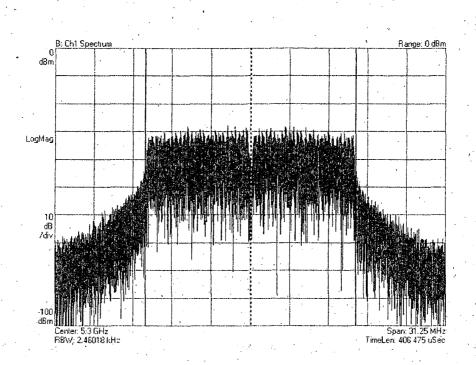

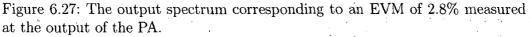

Digital communication systems use vector modulated modulation schemes. The digital bits are mapped to symbols in the constellation diagram [Hlawatsch 99]. Figure 2.6 shows a typical constellation diagram used for IEEE 802.11a wireless LAN systems.

|                | A: Ch1 OFDM Mea         | 38  | -      |   |    |     |       |      | 4 |       | R       | ange: -4 | 0 dBm          |

|----------------|-------------------------|-----|--------|---|----|-----|-------|------|---|-------|---------|----------|----------------|

| 1.5            |                         |     |        |   |    |     |       | • •. | , | · · · |         |          | 1V0            |

|                |                         |     | ۵.     | ۲ | ۲  | ۲   | ۲     |      | © | ۲     | а.<br>1 |          |                |

| -              |                         | · . | ۲      | ۲ |    | ۲   | ۲     | ۲    | ۲ | ۲     |         |          |                |

| nst            | •                       | •   | ۲      | ۲ |    |     | ۲     | ۲    | ۲ | ۲     |         | • .      |                |

|                |                         | •   | •      | ۲ | ۲  | ۲   | •     | ۲    | ۲ | ۲     |         |          |                |

|                | · · ·                   |     | •<br>• | ۲ | ۲  | ۲   |       | ۲    | ۲ |       |         |          | 2              |

| DO<br>m<br>fiv | -                       |     | ۲      | ۲ | •. | ۲   | ۲     | ۲    |   |       | · · ·   |          |                |

|                | •                       |     | ۵      | ٢ | ۲  | ۲   | ۲     | ۲    |   | ۲     |         | ·        |                |

|                |                         | ••  | ٢      | ۲ |    | . 🕢 | ۲     | ۲    | ۲ | 0     | <br>    |          |                |

| .5             |                         |     |        |   |    | ,   | ·. '. | .,   |   |       | j.      |          |                |

|                | 2.126<br>RBW: 312.5 kHz |     | · · ·  |   |    |     | -     |      | • |       | Time    | Len: 6   | 2.126<br>) Sym |

Figure 2.6: Measured 64-QAM constellation diagram. The signal was measured undistorted directly out of a generator capable to generate IEEE 802.11a test-signals (WLAN, 54Mbit/s, 64-QAM). The additional two symbols represent the tracking cursors required for the test set measurement to obtain the right amplitude and phase.

These data symbols consisting of several data bits have a certain position in this I/Q-plane represented by the carrier magnitude and the phase for a certain data clock transition. To ensure, that the signal is demodulated correctly, the exact magnitude and the exact phase at each clock transition have to be guaranteed within a certain error margin.

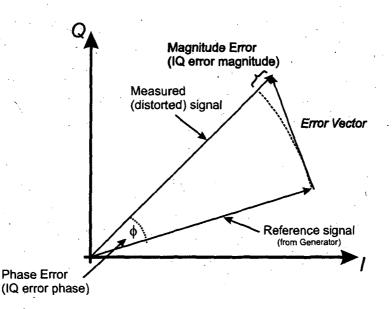

Figure 2.7 shows what happens, when a symbol of the I/Q-plane is shifted in its magnitude and phase. The EVM is measured for a certain modulation scheme and is defined by the scalar distance between two signal vector end points

Figure 2.7: Signal vector deviation of a distorting RF building block. The blue vector represents the resulting error vector.

[Agilent 02,b, 3GPP 03]. Usually EVM can be measured for peak and RMS errors. For applications needing a high linearity the RMS value is of higher interest, as the peak (saturated) operation is not used. The relative RMS vector error is defined by

RMS EVM =

$$\sqrt{\sum_{k \in K} |E(k)|^2 / \sum_{k \in K} |S(k)|^2}$$

(2.15)

with E(k) representing the error vector and S(k) the signal vector for each data clock transition k and K for the whole set of symbols.

The symbol vector error for a symbol k is defined by

EVM(k) =

$$\sqrt{\left(\frac{|E(k)|^2}{\sum_{k \in K} |S(k)|^2}\right)/N}$$

(2.16)

with N the total number of elements in the set K.

The EVM is usually given as percentage of the peak signal level error for the outermost symbols of the constellation diagram.

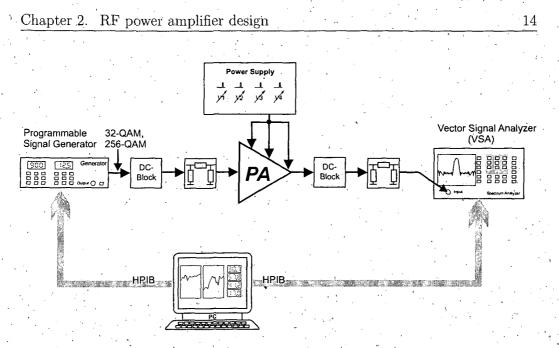

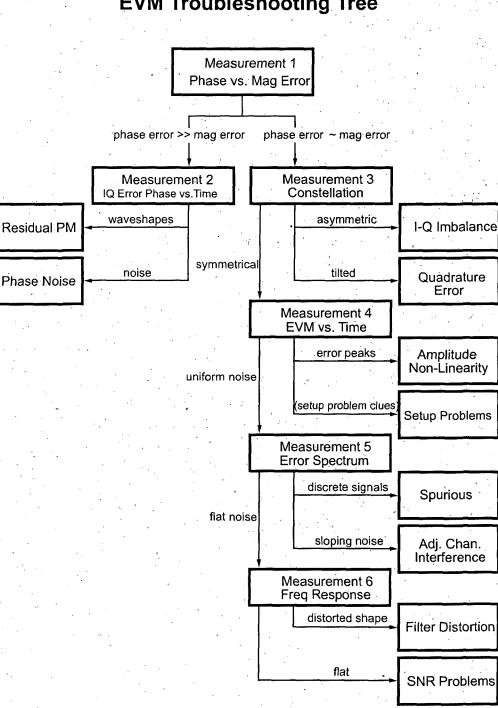

With a Vector Signal Analyzer (VSA), such vector modulation schemes can be measured. With the knowledge of the original signal, the error in the magnitude and the phase can be easily determined [Agilent 02,b]. The EVM measurement allows also further troubleshooting in RF circuits, an overview can be found in

Figure 2.8: Error Vector Magnitude (EVM) measurement setup using a Vector Signal Analyzer (VSA).

[Agilent 02,b] and in the flow chart 2.9. A typical measurement setup is shown in fig. 2.8.

For PAs, a certain level of distortion could be tolerated. A common maximum value for RMS EVM is 3% for wireless LAN applications which could usually be found in datasheets.

### 2.1.5 The Power Complementary Cumulative Distribution Function (CCDF)

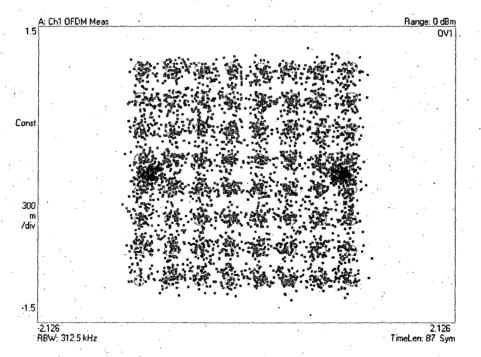

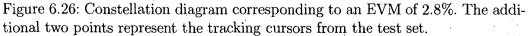

As new digital modulation formats (especially with WLAN and the so called 3G Systems) feature higher peak-to-average power ratios, the power distribution function is of importance not only for the calculation of average efficiencies but also for the design of PAs, as the operation in a saturated area leads to a deformation of the outgoing power distribution function. The look on output power distribution functions was not of interest as long as modulation schemes like analog FM with a fixed output power level or AM signals with a peak to unmodulated signal ratio of 6 dB (limited by modulation index) have been the typical applications. But for coded Orthogonal Frequency Division Multiplexing (OFDM) with a large amount of symbols there exist a large amount of different magnitudes and phase values for each symbol in the I/Q-plane. This causes a wide range of output power levels. As a result, the symbols in the I/Q plane will shift due to magnitude and/or phase errors. For example, applying the undistorted 64-QAM signal in fig. 2.6 to a PA [Bakalski 03,b] with an average power in the region of P1dB, the signal will look like fig. 2.10.

Figure 2.10: Measured 64-QAM constellation diagram of a PA working in the compression. The average power was selected to be -7 dBm at the PA presented in [Bakalski 03,b]. The additional two symbols represent the tracking cursors required for the test set measurement to obtain the right amplitude and phase.

The main idea of the power Complementary Cumulative Distribution Function

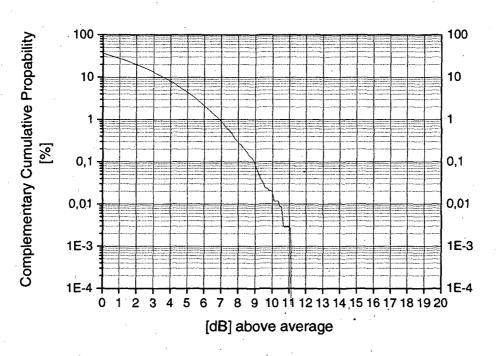

Figure 2.11: Measured undistorted IEEE 802.11a WLAN, 54 Mbit/s 64-QAM output signal CCDF curve.

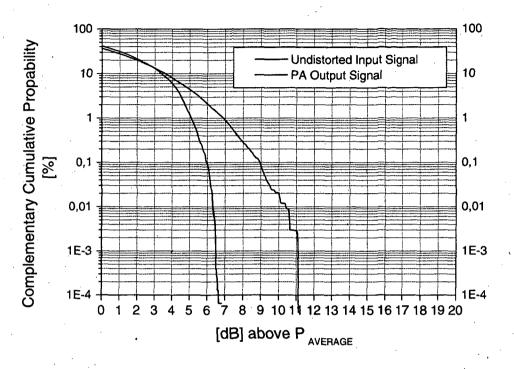

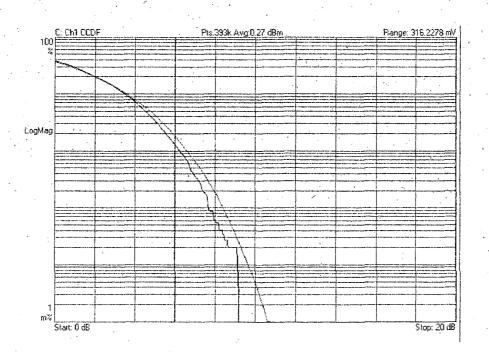

(CCDF) [Agilent 02,a] is to describe the probabilities of the power levels by the signal, and how the RF building block, like the PA but also other components like low noise amplifiers (LNA), mixers will deform the curve. A CCDF curve gives the information on the probability a signal has got for a certain power level. Figure 2.11 shows the CCDF of a IEEE 802.11a 64-QAM signal. The signal varies in its maximum output power by 11 dB, so that a typical back-off from the P1dB compression of 10 dB is used. Applying higher input power to a PA will shift the output peaks into the compression and thus lead to increased errors in the I/Q constellation plane. Figure 2.12 shows the CCDF for a PA [Bakalski 03,b] driven into strong compression.

The CCDF curve bases on the probability density function (PDF)  $p_x(\xi)$  given by the modulation scheme, hence by the probability of the symbols. The integration of the PDF gives the Cumulative Distribution Function (CDF) [Weinrichter 91]:

$$CDF(\xi) = \int_{-\infty}^{\xi} p_x(\alpha) d\alpha.$$

(2.17)

Inverting it, by subtracting the CDF from 1 (CCDF = 1 - CDF) gives the Com-

Figure 2.12: Measured undistorted input signal and a strongly compressed 64-QAM output signal CCDF curve. The PA was driven with an average input power of -4 dBm which is in the saturated area [Bakalski 03,b].

plementary Cumulative Distribution Function (CCDF):

$$CCDF(\xi) = 1 - \int_{-\infty}^{\xi} p_x(\alpha) d\alpha.$$

(2.18)

The difference between the CDF and CCDF curve is that the CCDF curve emphasizes peak power levels instead of minimum power levels in the CDF. The CCDF can be seen as an improvement on characterizations using the Crest Factor, as single peak levels are stressed much more. The Crest Factor itself is defined as the ratio of the peak voltage to RMS voltage level, but for the whole signal. Using only the crest factor would ignore single peak levels like parasitic effects, and the peak value measurement would strongly depend on the measurement time, and thus lead to problems in repeated measurements [Agilent 02,a].

#### 2.1.6 Noise Power Ratio (NPR)

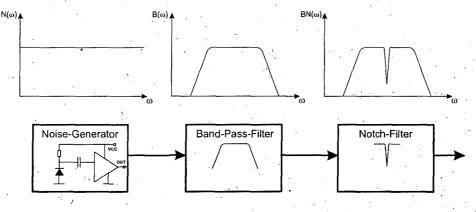

The Noise Power Ratio (NPR) is a less common linearity characterization method as it is now replaced more or less by CCDF or EVM characterization. Herby it is used to characterize the PA behavior used for multi-carrier signals (>10 carriers). Idea of this test procedure is to feed the PA with a white noise signal containing a notch in its spectrum. A nonlinear PA will cause the notch to disappear [Katz 03, Raab 03].

The white noise simulates many carriers of random amplitude and phase. A multicarrier system is therefore well-covered and it is easier to feed the device-undertest with a noise than with multiple well defined carriers that even do not interfere with each other. Usually the signal is generated with a noise-source <sup>3</sup> [Flecker 84] that is connected to a band-pass filter and a notch filter in series (fig. 2.13).

Figure 2.13: Generation of a test-noise for NPR analysis.

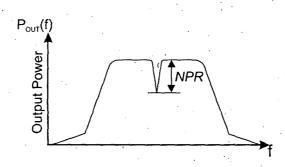

The notch depth can easily be measured by the use of a spectrum analyzer. Applying the signal to a PA with its intermodulation products will cause the notch to be filled up. The NPR is defined by ratio of the notch power to the average signal power (fig. 2.14):

$$NPR [dBc] = \frac{P_{OUT}(\omega_{Notch})}{P_{OUT,AVG}}$$

(2.19)

#### 2.1.7 Adjacent Channel Power Ratio (ACPR)

The Adjacent Channel Power Ratio (ACPR) is another very common linearity characterization. Especially in applications working with frequency multiplex, ACPR is often used. The ACPR is the ratio of the out of band power (of a specified range) to the RMS signal power. It characterizes the affection to adjacent

<sup>&</sup>lt;sup>3</sup>It is typically realised using an avalanche diode.

Figure 2.14: NPR measurement definition.

channels due to nonlinearity. Inverting the ACPR definition gives the Adjacent Channel Leakage Ratio (ACLR), which is not very common, but used in some  $R\&S^4$  measurement environments [Banerjee 02].

As introduced before, the ACPR can be defined by [Raab 03, Kenington 00]:

$$ACPR_{L} [dBc] = \frac{\int_{f_{c}-f_{0}}^{BW_{L}} |H(f)|^{2}S(f)df}{\int_{f_{L}}^{f_{c}-f_{0}} - \frac{BW_{L}}{2}}$$

(2.20)

with S(f) representing the power spectrum, H(f) a pulse-shaping filter (CDMA applications)  $f_c$  the center frequency, BW the bandwidth,  $f_0$  the offset, and  $f_L$  and  $f_U$  lower and upper band edge, respectively.

Figure 2.15:  $ACPR_L$  measurement definition.

Eqn. (2.20) specifies the lower sideband, but it is possible to specify the upper side band as well. Furthermore, sometimes the ACPR is defined for two different frequency offsets, and the outer band ACPR is often called Alternate Channel Power Ratio.

<sup>4</sup>R&S stands for Rohde&Schwarz, a measurement equipment manufacturer.

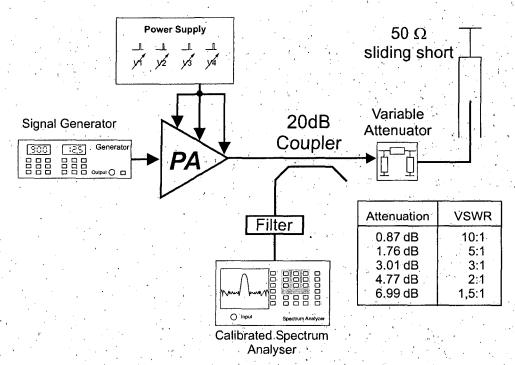

#### 2.1.8 PA ruggedness: Operation into mismatch loads

Mobile wireless communication systems such as GSM have the problem that the antenna finds itself in the most different conditions. Thus the offered load to the PA will not be in the optimum area as desired. In fact high VSWR peaks can occur, which may damage the PA. To test the ruggedness of the PA, fig. 2.16 shows a measurement setup for testing the PA with mismatched loads. The sliding short together with the attenuator provides a variable load to the PA, thereby emulating a mismatched antenna. Harmonics and spurii can be measured under different mismatch conditions using the spectrum analyser.

Figure 2.16: Test setup for the operation into mismatched loads.

### 2.2 RF power amplifiers topologies

RF power amplifiers have been constructed in three major topologies, each having different advantages and disadvantages [Shumaker 02, Walker 03]. However these rely mainly on the features of the used technology as well as the application the PA should be designed for.

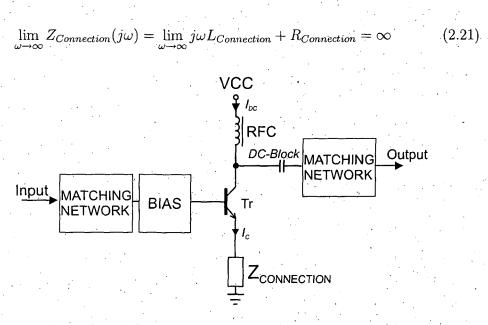

#### 2.2.1 Single-Ended PAs

The most simple and therefore most often found topology is the Single-ended power amplifier. Figure 2.17 shows the block diagram of such an amplifier.

Figure 2.17: A single-ended 1-stage power amplifier block diagram.

This amplifier topology is specified by the emitter or source (FET) connection to ground, while the input is feeding the base or the gate. Another configuration uses the base or gate contact connected to ground. Both have the operation with unbalanced in- and output signals in common. This shows the first major problem in all single-ended designs: The ground connection. Considering DC voltages and currents, the ground connection is only a problem of conductivity. With the typical Al-metalization in Si-based semiconductor technologies and the connection with bond wires, the DC resistance is typically in the range of some m $\Omega$ up to  $1-2\Omega$ . The real problem comes up considering RF signals: The longer the layout connection to ground, the higher the inductance of the connection will be. Additionally, bond wires behave like inductors with a high quality factor Q. In a typical RF chip package, the inductance from the outer connection pin to the emitter of the transistors is about 1-1.5 nH. Calculation formulas are presented in [March 91, Wadell 91]. For high frequencies, this problem becomes so dominant, that every amplifier gain will be reduced up to non-operation by the impedance of the emitter connection:

Figure 2.18: A single-ended 1-stage power amplifier with an emitter connection impedance.

It is easy to see, that the impedance  $Z_{Connection}$  will lead to reduced currents through the transistor and thus to reduced output power and gain (emitter degeneration).

However, there exist several possibilities to weaken the problem:

- The use of several bond-wires in parallel. This reduces the inductance, but only up to a certain level, as bond wires close to each other have mutual inductance. Calculations on bond-wires and coupling between bond-wires could be found in [March 91].

- The chip could be housed using flip-chip packaging technologies [Nicolics 97]. Hereby the die is soldered directly onto a PCB or ceramic carrier. However, the problem of heat dissipation could become relevant, as different thermal expansion coefficients may lead to reliability problems.

- Some semiconductor technologies feature a kind of VIA connection through the chip towards a ground plane. This is typically called a Sinker, and is usually available in III-V technologies. There exist two derivates: First, the real metalized VIA and the VIA using a highly doped substrate contact on a high conductive substrate. The second option suffers from a limited conductivity and thus matching components such as coils have a reduced Q-factor. It is easier to realise in Si-based technologies.

Figure 2.19: A push-pull type 1-stage PA block diagram.

The main advantage of single-ended designs is the easy in- and output matching [Gonzales 84]. Usually only a certain combination of an inductor and a capacitor is enough for a narrow-band matching network. The problems come up regarding the load impedance area and the bandwidth where transistors have to be matched. For example, single-ended GSM PAs need an output load impedance  $R_L$  of typically less than 1  $\Omega$ . In dependence of the package, between output transistor and the load exists a series inductance, hence the load presented to the transistor is:

$$Z_{Tr} = Z_{L,Bondwire} + R_L = j\omega L_{Bondwire} + R_L \tag{2.22}$$

It is obvious, that even low inductances will lead to high losses in the inductor. Furthermore, if we consider, that the bondwire inductance shifts due to manufacturing inaccuracies, the matching will have deviations in a certain range. As transistors are never unilateral, this shows up the next problem: The input matching. RF BJTs have a low input impedance <sup>5</sup>. If such an output transistor is fed by a small driver, the matching requires high Q-factors, to have an efficient design. It should be mentioned that most switched-mode amplifiers are based on single-ended topologies. Although they allow the highest possible efficiencies, it is not possible to implement them for highest frequencies (above 20 GHz), due to the limited switching speed of the transistors.

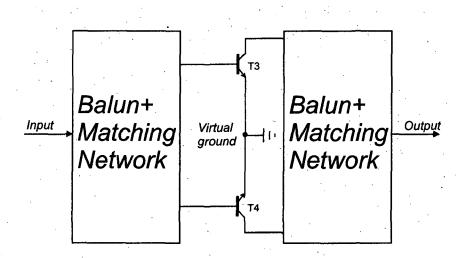

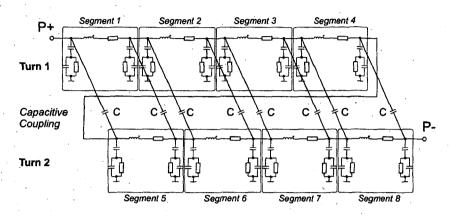

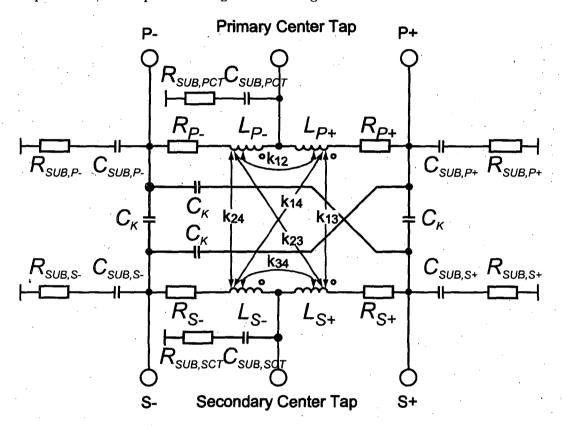

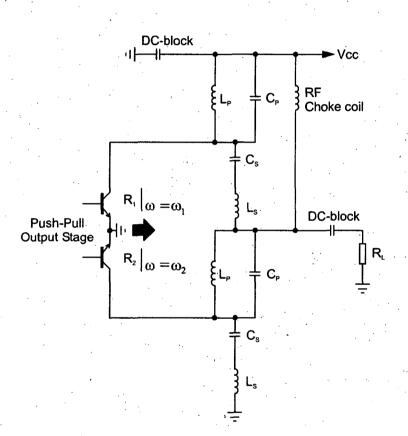

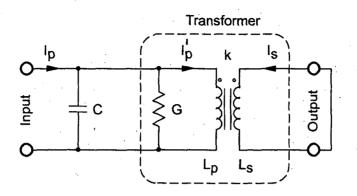

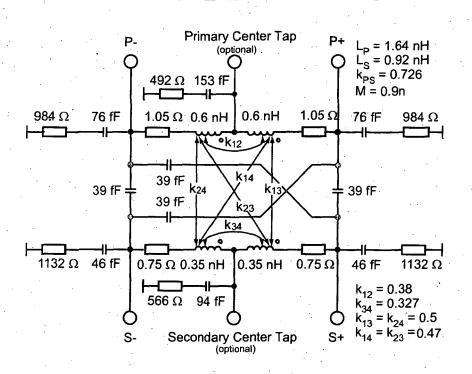

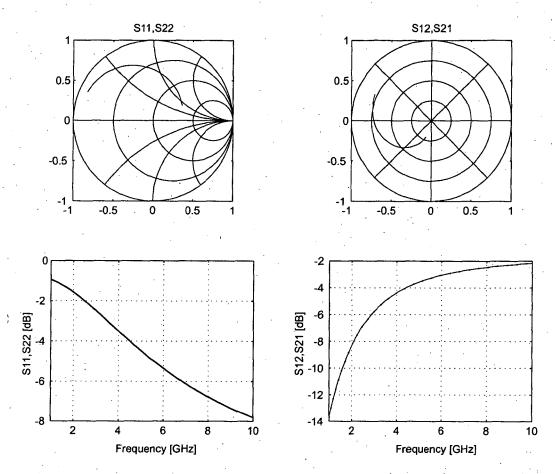

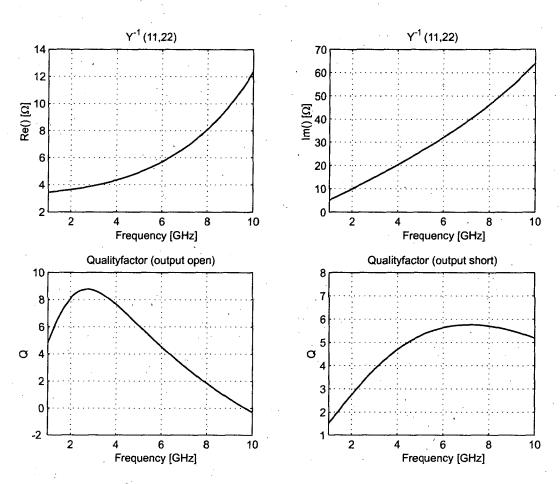

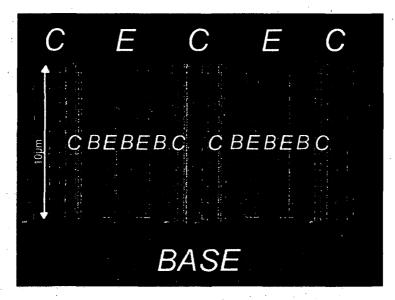

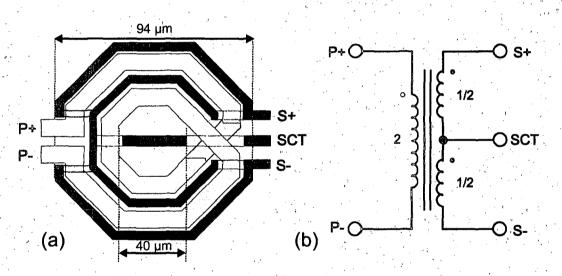

#### 2.2.2 Push-Pull PAs

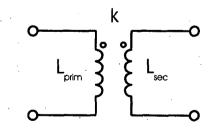

Using two single-ended PAs supplied by an input signal shifted by 180° brings up the so-called push-pull power amplifier. Figure 2.19 shows the block diagram of this topology. The 180° phase shift is typically generated by a so called BALUN

<sup>&</sup>lt;sup>5</sup>It depends on emitter area, output matching and operation point

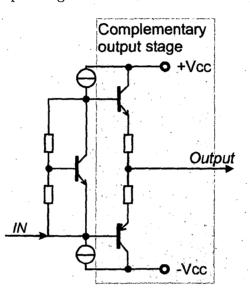

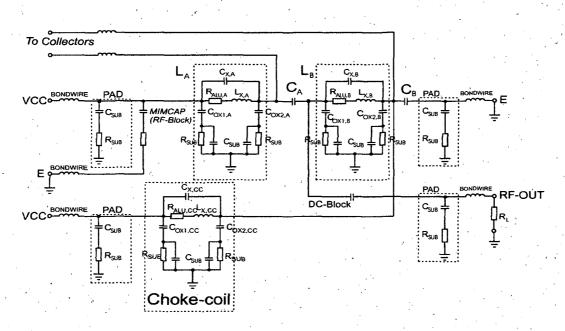

(*BAL*anced to *UN* balanced). There exist several methods of generating such signals, the LC-BALUN discussed in section 4.18 is one of them  $(\pm 90^{\circ})$  phase shift). While push-pull amplifiers for audio frequency (AF) applications today consist of a matched pair of npn and pnp transistors (or their equivalent FET types), this is usually not possible for RF amplifiers, due to the fact that the pnp transistors are much slower and operate with lower current densities. Figure 2.20 shows an AF complementary output stage.

Figure 2.20: An audio frequency (AF) PA output stage. It uses two complementary transistors: The npn for the positive, the pnp for the negative input signals.

Push-pull or also called differential amplifiers have several advantages compared to the single-ended solutions:

- Easy realisation of class-B or class-AB amplifiers, due to the fact that the circuit can be dimensioned in that way that each transistor is conductive for a current conducting angle of 180°.

- The circuit offers a virtual ground. Though, the ground connection is only required for the DC supply. For RF signals, the ground is exactly where both emitters connect to each other. Thus, the virtual ground of the input matching network can be used for the transistor biasing. No extra quarter wavelength transmission line or RF choke inductor is necessary.

- Transformer [Johnson 84] or Marchand [Marchand 44] based BALUNs have the feature that any DC potential can be applied without affecting the circuit at in- or output. Thus no DC blocks are required in this case.

- The load-line impedance for equal output power is four times higher than for single-ended designs. Thus losses in bond-wires are reduced. Further,

the necessary transistor areas are reduced as well, which improves linear design at higher efficiency and relaxes the need on high Q-factors for the interstage matching.

Of course push-pull PAs have one major disadvantage: They require a BALUN. The design of a low-loss, well-matched BALUN is not a simple task. Especially at the output side, a BALUN requires several efforts in one:

- The impedance of each input port of the differential input must be equal.

- The phase between the two ports of the differential input must be as near to 180° as possible.

- For high efficiencies it is also advantageous to match the second and third harmonic loads to the transistors [El-Hamamsy 94]. Especially for the second harmonic frequency a low impedance and for the third harmonic frequency a high-valued impedance is desired. Typically this task is best met by Marchand-BALUN [Marchand 44, Mongia 99] derivates.

- The BALUN losses should be as low as possible. For BALUNs constructed with lumped elements this requires high Q-factors.

Today, there exist a lot of very efficient BALUN proposals [Bakalski 02,a, Ilkov 03,b, Johnson 84, Mongia 99], fitting to a lot of applications. However their design suffer from higher complexity than that of single-ended matching networks.

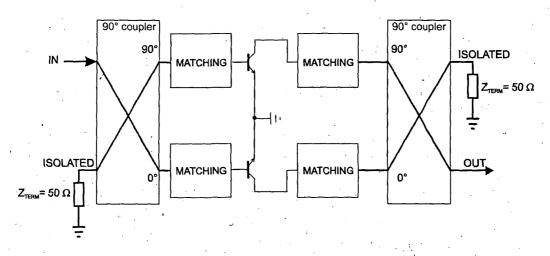

#### 2.2.3 Balanced PAs

The balanced PAs differ basically in their  $90^{\circ}$  phase shift between its parallel driven stages. It is important to mention, that usually the definition of "balanced" in RF circuits implies 180° of phase shift. Unlike to RF circuits for power amplifiers the nomenclature "Balanced Power Amplifier" exists for 90° phase shift between the stages [Shumaker 02]. For RF PAs, power combining is a very common method to increase output power, especially when a single stage won't fit the necessary specifications. Therefore not only Wilkinson power dividers [Wilkinson 60, Howe 74, Magerl 98] are used, also branch couplers like the Lange coupler [Lange 69] are in common for power combining. Especially for very high frequencies (>50 GHz), the combining with a 90° coupler makes sense, as the wavelength is very short, and can be integrated on-chip [Chang 03]. Furthermore such couplers typically offer a good input matching, as a 50  $\Omega$  load is used. This is necessary especially for very high frequencies, as the input matching needs to be as good as possible, as gain is low and matching with external components is very lossy and difficult. The use of a 50  $\Omega$  load implies a big disadvantage as well: This resistor is an additional part, and it will require die-size or an area on the

Figure 2.21: A balanced 1-stage power amplifier block diagram.

PCB. Further such loads have a certain power dissipation, worsening the thermal problems in the PA. The most important disadvantage from balanced PAs to push-pull typed amplifiers is the missing virtual ground. This causes similar problems with ground connections as known in single-ended designs. This implies that the resulting load impedances are two times lower than in push-pull designs, as it is in fact a single-ended design using a power divider. Furthermore, a class-B or class-AB operation is very difficult, as now both transistors are not used complementary anymore. Both, balanced and push-pull configuration, have the advantage, that intermodulation products are cancelled: For balanced the third order products, for push-pull the even products.

### 2.3 Power amplifier classes

PAs are categorized into classes dependent on the waveform of the voltages and currents observed at the transistors. The first major group are the class-A, B and AB. They are often described as the linear PA classes. The classes C, D, E, F, G, H and S are the so-called nonlinear amplifier classes. While a class-C PA uses the same topology as a class-A PA but with different biasing, the other classes have all in common that they use the transistor as a on/off switch. Most of them are based on proposals by Raab [Raab 75, Raab 78,b, Raab 78,a, Raab 77] and Sokal [Sokal 75, Sokal 77].

#### 2.3.1 Class-A power amplifier

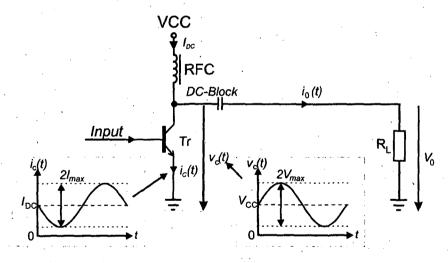

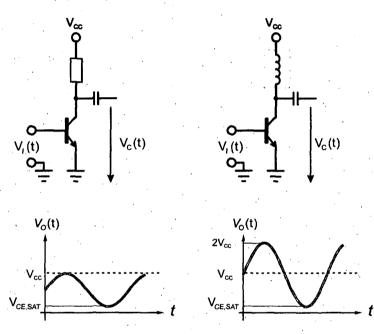

The most simple class is the class-A PA as it is quite similar to its small-signal amplifier counterpart. In this configuration the bias und thus the operating point is chosen in that way, as there is always a current flowing through the transistor. The transistor should therefore work in its linear area without any distortions. Typically it is realised in a single-ended configuration as discussed before. A typical schematic can be seen in fig. 2.22.

Figure 2.22: A class-A single-ended PA. The collector current  $i_c$  and the RF output voltage  $V_c$  are plotted with their ideal waveforms.

Neglecting the matching circuitry and its parasitics, the bias is assumed to be chosen that the operating point is in the mid of the linear region. With  $I_{C,quiet}$  describing the bias current, the collector current can be written as:

$$i_c(t) = I_{C,quiet} - I_{MAX}\cos(\omega t)$$

(2.23)

with  $I_{MAX}$  being the peak value of the collector current. While  $I_{C,quiet}$  flows via the RF choke coil RFC, the non-DC part passes the DC-Block capacitor causing an output voltage at the load impedance attached to the output:

$$v_0(t) = R_L \cdot I_{MAX} \cos(\omega t) = V_{MAX} \cos(\omega t)$$

(2.24)

Analogous to AF amplifiers using transformers, the peak output signal can reach up to  $V_{CC}$  instead of  $\frac{V_{CC}}{2}$  peak output voltages. This is due to energy stored in the RF choke coil (fig. 2.23) :

Figure 2.23: Improvement of the maximum output voltage with the use of an inductor instead of a resistor.

The maximum output power can therefore be as high as

$$P_L(t) = \frac{V_{MAX}^2}{2R_L} \le \frac{V_{CC}^2}{2R_L}$$

(2.25)

using the factor  $\frac{1}{\sqrt{2}}$  for the RMS voltage of a sinusoidal signal.

Considering the maximum efficiency of a class-A amplifier, additionally the power consumption has to be calculated:

$$P_{Supply} = V_{CC} \cdot I_{C,quiet} = \frac{V_{CC}^2}{R_L}$$

(2.26)

under the assumption, that the PA is biased to have the average output voltage  $V_{CC}$ .

The maximum overall efficiency is

$$\eta = \frac{P_L}{P_S} = \frac{V_{max}^2}{2V_{CC}^2} \le 0.5 \tag{2.27}$$

It is important to mention that the heat dissipation has to be considered, as class-A amplifier suffer from high quiescent currents beside the low theoretic efficiency maximum. This is an important point for PA designs with high peak to average power ratios (crest factors).

#### 2.3.2 Class-B and AB power amplifier

While the transistor in a class-A PA is always conducting, this is totally different for the other linear classes as well as for class-C. Hereby the conduction angle decides in which PA class the circuit is operated:

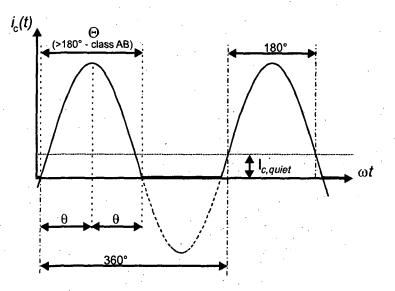

Figure 2.24: The conducting angle for a class AB amplifier

The conduction angle  $\Theta$  is the fraction of a full cycle where the transistor is operated to be conductive. Thus fig. 2.24 shows that a sinusoidal signal is cut off for negative currents, and thus the amplifier transistor must have a conduction angle  $\Theta$  of less then 360°, the conduction angle for class-A amplifiers. If  $\Theta$  is between 360° and 180° we have a class AB amplifier. For  $\Theta = 180$ ° it is a class-B design. Less than 180° of conducting angle is a class-nC amplifier. For calculations on efficiency and power there is also the half conduction angle  $\theta$  in common (fig. 2.24). It is used for calculations of output power an efficiencies.

The conducting angle also implies the information on the achievable output power and maximum efficiency. Expressing the collector current for  $i_c(t) > 0$  with Chapter 2. RF power amplifier design

$$\dot{u}_c(t) = I_{MAX} \cos(\omega t) - I_{c,quiet}$$

(2.28)

with the quiescent current  $I_{c,quiet} = I_{MAX} \cdot \cos\theta$  with  $-\theta < \omega t < \theta$  and  $\Theta = 2\theta$  gives:

$$i_c(t) = I_{MAX}(\cos(\omega t) - \cos\theta)$$

(2.29)

The calculation of the efficiency requires the knowledge of the DC component and the fundamental frequency component which both are determined by a Fourier series. Hence, the DC component is

$$I_{DC} = \frac{1}{2\pi} \int_{-\theta}^{\theta} \left[ I_{MAX}(\cos \omega t - \cos \theta) \right] d\omega t = \frac{1}{\pi} \int_{0}^{\theta} \left[ I_{MAX}(\cos \omega t - \cos \theta) \right] d\omega t =$$

$$= \frac{I_{MAX}}{\pi} [\sin \theta - \theta \cos \theta]$$

(2.30)

Using eqn. 2.30, the DC-power provided from the power supply is :

$$P_{DC} = V_{CC} \cdot I_{DC} = \frac{V_{CC}I_{MAX}}{\pi} (\sin \theta - \theta \cos \theta)$$

(2.31)

The fundamental frequency current is given by

$$i_1 = \frac{4}{2\pi} \int_0^\theta \left[ I_{MAX}(\cos \omega t - I_{c,quiet}) \cos \omega t \right] d\omega t = \frac{I_{MAX}}{2\pi} (2\theta - \sin 2\theta) \qquad (2.32)$$

Hence we get the maximum output power for the fundamental frequency by

$$P_{OUT,max} = \frac{i_1^2 \cdot R_L}{2} = \frac{u_{peak}}{\sqrt{2}} \cdot \frac{i_{peak}}{\sqrt{2}} = \frac{V_{CC}}{\sqrt{2}} \cdot \frac{i_{peak}}{\sqrt{2}} = \frac{V_{CC} \cdot I_{MAX}}{4\pi} (2\theta - \sin 2\theta) \quad (2.33)$$

Thus, the theoretical maximum efficiency is determined by

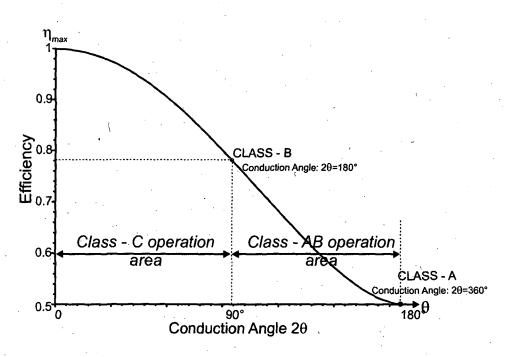

$$\eta_{max} = \frac{P_{OUT,max}}{P_{DC}} = \frac{2\theta - \sin 2\theta}{4(\sin \theta - \theta \cos \theta)}$$

(2.34)

Figure 2.25 shows the maximum efficiency vs. the conduction angle. It can be determined that the maximum efficiency for class AB PAs is between 50% and 78.5% (class-B). Hence the class A PA with a conduction angle of 360° is limited in its efficiency by 50% (eqn. 2.27). This represents a rather theoretical curve, as it implies an optimum loaded amplifier which has got its peak output voltage up to the supply voltage  $V_{CC}$ . Further the saturation voltage is simplified to 0V. If the output peak voltage is limited to  $V_{out,peak}$ , eqn. 2.33 can be written as

$$P_{OUT} = \frac{V_{out,peak} \cdot I_{MAX}}{4\pi} (2\theta - \sin 2\theta)$$

(2.35)

Chapter 2. RF power amplifier design

Figure 2.25: The maximum efficiency vs. the conduction angle.

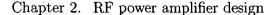

### 2.3.3 Class-C power amplifier

Class-C type PAs are rarely found today. Even as they offer higher efficiencies than class-B, they suffer from high distortions and thus high nonlinearities. The conduction angle  $\Theta$  for a class-C type PA is lower than 180°, being the reason for the nonlinear behavior. Figure 2.25 demonstrates that the efficiency rises up to 100%, but this implies extremely low conduction angles which must result in reduced output power levels. The degradation of output power with the reduction of the conduction angle can be found in [Rodgers 03] (fig. 2.26).

$$P_{0,max,norm} = \frac{P_{0,max}}{P_{0,norm}} = \frac{1}{\pi} \frac{(2\theta - \sin 2\theta)}{1 - \cos \theta}$$

(2.36)

Figure 2.26: The maximum normalized output power vs. the conduction angle.

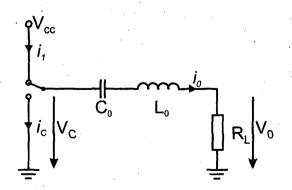

### 2.3.4 Class-D power amplifier

The class-D power amplifiers are switched-mode PAs. All these amplifiers see the transistor as a controlled switch (fig. 2.27). An ideal switch would behave as an ideal conductor for the 'on'-resistance and having an infinite resistance for the 'off'-resistance. Assuming that there is no loss, the output signal will be the power supply switched on and off, just depending on the rate of the input carrier signal. For this assumption the efficiency will be 100 %, as no losses due to finite switching time and internal parasitic resistances can occur.

Figure 2.27: Transistor used as a switch in a PA configuration.

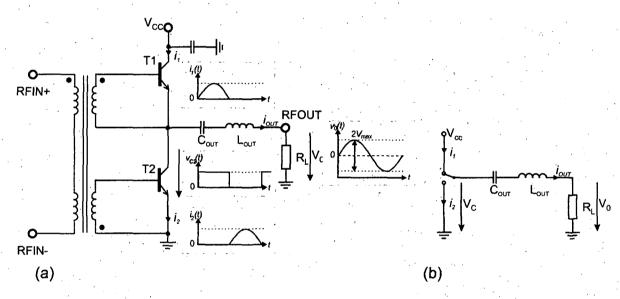

Class-D amplifiers typically base on a push-pull topology. Out of this there exist three types of class-D stages:

1. The complementary voltage switch PA

Figure 2.28 shows a simplified schematic of a class-D complementary voltage switch PA stage. This design uses a transformer to drive the transistors T1 and T2 with a phase difference of 180°. This concept known is a classic push-pull type configuration where T1 is turned on if T2 is turned off and vice versa. As a result, the capacitor is switched between the supply voltage  $V_{CC}$  and ground. The voltage found between emitter and collector of T2 has therefore a square waveform (fig. 2.28) with a 50% duty cycle.

Figure 2.28: a) Complementary voltage switch class-D PA (b) equivalent circuit

The emitter-collector voltage as sketched in (fig. 2.28) is:

$$V_{C2} = V_{CC} \left[ \frac{1}{2} + \frac{1}{2} \operatorname{sgn}(\omega t) \right]$$

(2.37)

with  $sgn(\omega t)$  as the signum function:

$$\operatorname{sgn}(\omega t) = \left\{ \begin{array}{cc} +1 & , & \sin(\omega t) > 0 \\ 0 & , & \sin(\omega t) = 0 \\ -1 & , & \sin(\omega t) < 0 \end{array} \right\}$$

(2.38)

Applying the Fourier analysis on the squarewave voltage gives:

$$\operatorname{sgn}(\omega t) = \frac{4}{\pi} \left\{ \sin(\omega t) + \frac{1}{3}\sin(3\omega t) + \frac{1}{5}\sin(5\omega t) + \cdots \right\}$$

(2.39)

and hence

$$V_{C2}(\omega t) = V_{CC} \left\{ \frac{1}{2} + \frac{2}{\pi} \sin(\omega t) + \frac{2}{3\pi} \sin(3\omega t) + \frac{2}{5\pi} \sin(5\omega t) + \cdots \right\} (2.40)$$

If the output network consisting of  $C_{OUT}$  and  $L_{OUT}$  is tuned to the fundamental frequency of the squarewave signal, we should see a sinusoidal current and voltage on the load  $Z_L$  as sketched in fig. 2.28:

$$_{out}(\omega t) = \frac{2V_{CC}\sin(\omega t)}{\pi R_L}$$

(2.41)

with the peak value

$$i_{out,peak} = \frac{2V_{CC}}{\pi R_L} \tag{2.42}$$

for the output current and

$$V_{MAX} = \frac{2V_{CC}}{\pi} \tag{2.43}$$

for the output voltage. Hence, the output power is calculated by

$$P_{out} = \frac{2V_{MAX}^2}{2R_L} = \frac{2V_{CC}^2}{\pi^2 \cdot R_L}$$

(2.44)

For the efficiency calculation, the DC consumption has to be calculated. The DC peak current is the same as in eqn. 2.41 due to the whole current flowing through T1 (or T2 half a cycle later). This implies that the power gathered from the power supply equals the RF power. Thus the theoretically efficiency is 1 (100%). However the efficiency will be reduced by finite switching speed and the non-ideal switching behavior (finite conductivity, and remaining resistance when switched off).

- RFIN+ RFIN+  $T_1$   $V_{cf0}$   $V_{cc}$   $V_{cc}$  $V_$

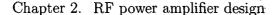

- 2. The transformer coupled voltage switching PA

Figure 2.29: Transformer coupled voltage switch class-D PA

The transformer coupled voltage switching amplifier has the same topology as a push-pull type amplifier. It is different to the complementary voltage switch PA as it needs a second transformer as a BALUN. Though it does not need the input transformer to feature inversely arranged windings. Its efficiency is theoretical 100%, the same as in the complementary voltage switch PA.

#### 3. The transformer coupled current switching PA

Referring the schematics 2.29 and 2.30, both amplifier types differ only in their power supply feeding, which is now done by a RF choke, and their output filter. The RF choke is hereby used to force the circuit to gather constant current from the power supply, which is switched by the transistors. In this configuration, the collector currents and voltages change, but the efficiency remains at the theoretical 100%. Using the amplifier as a current switch improves device speed behavior, as BJTs for example can be tuned to operate in their optimum working point and furthermore, the problem of avalanche breakdown due to high voltage switching is reduced.

Further topics on class D amplifiers can be found in [Albulet 01, El-Hamamsy 94].

Figure 2.30: Transformer coupled current switch class-D PA

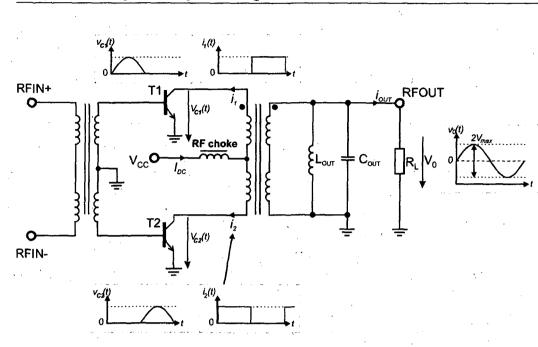

### 2.3.5 Class-E power amplifier

Chapter 2. RF power amplifier design

Class E power amplifiers are single-ended switch-mode configurations. Like in class D, the transistor is seen as an ideal switch. Figure 2.31 shows a simplified schematic and the equivalent circuit with a switch as an ideal transistor substitute.

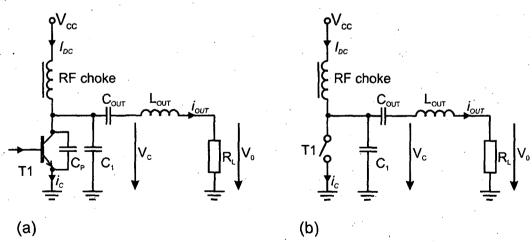

Figure 2.31: (a) Class E PA configuration (b) equivalent circuit

In this schematic  $C_P$  represents the transistors parasitic capacitance and thus a part of the passive load network sketched by  $C_1$ ,  $C_{OUT}$  and  $L_{OUT}$ . Class E

amplifiers have the theoretic maximum efficiency of 100%, but however rely on the same limitations as their class-D counterparts: Limited switching time, limitations in the Q-factor for the passive components (especially in lossy Si-substrates a big problem), and their saturation voltages.

### 2.3.6 Class-F power amplifier

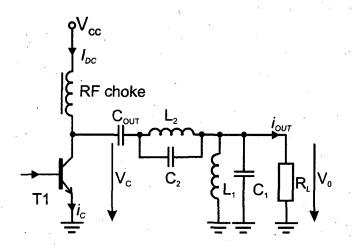

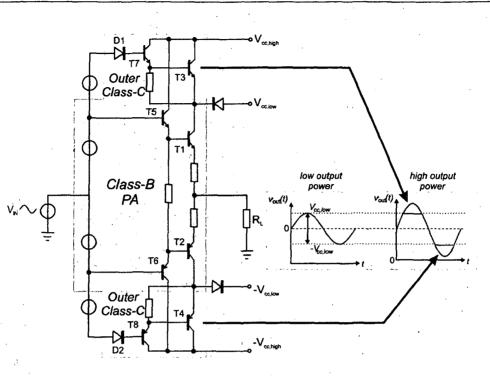

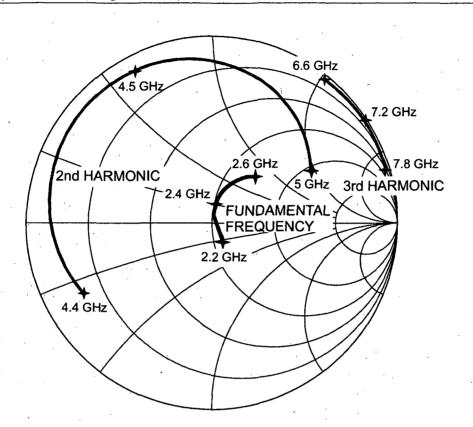

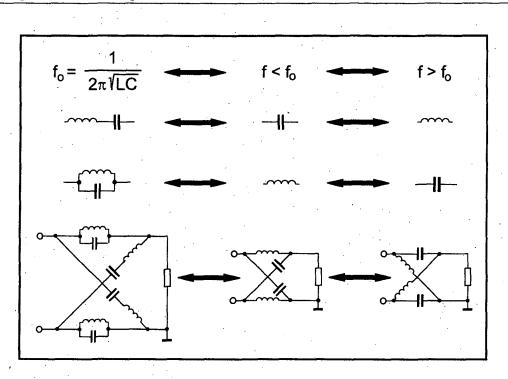

The class F power amplifiers are usually single-ended configurations but use a load network consisting of harmonic resonator circuits. Figure 2.32 shows an example for such a configuration. The voltage waveform consists of one or more odd harmonics to approximate a squarewave signal, while the current includes even harmonics to approximate a half sine wave signal. In inverse class F called designs this is vice versa. A class-F design equals class A for the number of harmonics set as 1. For  $\infty$  harmonics the efficiency converges to 100 % [Raab 03]. To get required harmonics the output is loaded with several C<sub>2</sub>/L<sub>2</sub> tanks and the transistor operated in saturated mode similar to class-C. It is important to mention, that class-F designs require the most complex output filters, whose component values must be correct for specific frequency points.

Figure 2.32: The Class F PA configuration.

### 2.3.7 Class-G/H/S power amplifier

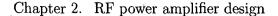

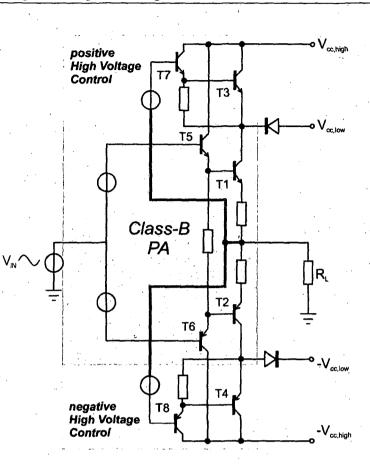

Class G and H amplifiers are further PA classes improving the class B efficiency especially with a focus on low input power signals. Today they can be found only in audio amplifiers and require several supply voltages and active devices. Figure 2.33 shows a class G audio power amplifier output stage for two supply voltages.

Figure 2.33: A Class G audio amplifier output stage.

The main idea in class G is to overcome the poor efficiency on low output power levels by designing an efficient class B or AB amplifier for small output power levels, so that the efficiency is high for the average power level. For the high output power levels an additional stage is stacked, operating in class-C mode. Hereby the low power amplifier transistors are cut off at their supply voltage and the stacked class-C transistor stage adds the necessary cut signals (fig. 2.33).

As a result, a class G amplifier has a higher average efficiency than a usual class B or AB amplifier. Furthermore the heat dissipation is also spread over two transistors. These designs are found mainly in audio applications due to the wide bandwidth necessary for the active components and the much slower pnp transistors.

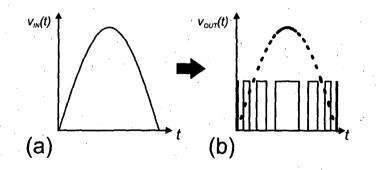

Class H is an extension to class G and modulates the higher power supply by the input or output signal (fig. 2.34). By this, the optimum supply voltage is tracked with the input signal to achieve better average efficiencies than in class G. Examples for class H PA could be found in [Higashiyama 95, Gottlieb 87] and a commercial example is the TDA 8574 line driver IC [Philips 98]. Another PA class is the class S. It includes all PA operating with pulse width modulation. Hereby the signal is brought to a rectangular waveform with variable duty-cycles in dependence of the input signal. Figure 2.35 sketches the possible waveform resulting of half a sinusoidal input signal. With such a configuration, an amplifier stage can be operated very efficient, but requires additional filtering, hence a low-pass at the output. The major disadvantage of such configurations is, that

Figure 2.34: A Class H audio amplifier output stage.

Figure 2.35: Pulse Width Modulation: Creation of a PWM waveform (b) out of an input sigal (a).

the transistors have to be much faster than in any before presented class as it must switch with a much higher switching frequency than the operating frequency to generate the accurate waveform with rectangular pulses and a low pass filter (comparable with 1-bit DACs using oversampling). This limits its RF ability, as the transistor speed is limited for every technology.

# Chapter 3

# SiGe bipolar transistors

## 3.1 Introduction

Today there exist several semiconductor technologies with the most different advantages and problems as well. A major group used for PA designs are the so called III-V-technologies. They include all InP, GaAs, and GaN technologies. III and V stand for the group in the chemical periodic system, respectively. As mentioned in the introduction, these technologies basically provide the best performance for PAs, wide band amplifiers and fast digital circuits, but suffer from high cost. The reason for the higher cost is originated in the smaller wafer sizes for III-Vtechnologies and the higher material cost implying higher wafer cost as well. The higher performance of III/V-technologies is based on the higher maximum carrier velocity, being up to 3 times higher than for Si.

The next major group are the silicon (Si) based semiconductor technologies. There exist the Si Bipolar Junction Transistor (BJT) and the SiGe Heterojunction Bipolar Transistor (HBT). Furthermore also Complementary Metal Oxide (CMOS) processes exits featuring complementary n- and p-FET transistors. Theoretically CMOS power amplifiers are feasible but suffer from reliability problems due to very low maximum supply voltage and hot carrier effects. Today no commercial CMOS-PAs are available. Further, there exist also mixed technologies called BiC-MOS processes. These combine the excellent high integration possibilities with the better RF performance of bipolar transistors. The next sections will give a brief discussion on the construction and the modeling of Si-BJTs and SiGe-HBTs used for the PAs in this thesis. A very good source on physics and modeling of bipolar transistors is found in [Reisch 03] and [Schrenk 78].

# 3.2 Self-aligned Silicon Bipolar Junction Transistors (BJT) and Silicon Germanium Heterojunction Bipolar Transistors (HBT)

The PA designs described in this thesis use SiGe bipolar HBTs. As this transistor type is mainly based on its Si bipolar BJT predecessor, this should give an introduction how such transistors are constructed and how the SiGe HBT differs from the Si BJT. In the past decades a lot of literature has been published describing the functional principles of bipolar transistors. The first publications originate from [Shockley 50], but more modern presentations can be found in [Ashburn 88] and other literature.

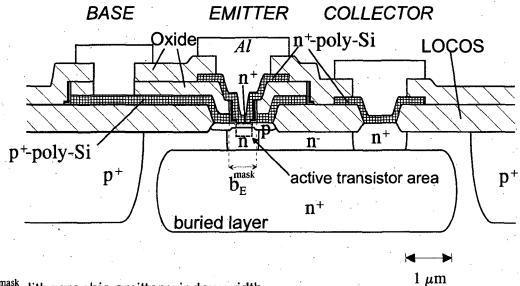

$\mathbf{b}_{\mathrm{E}}^{\mathrm{mask}}$ ... lithographic emitter window width

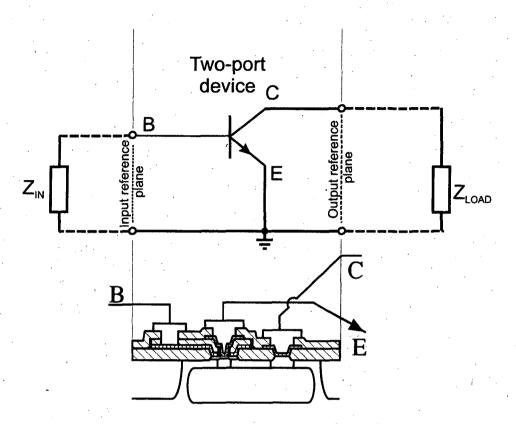

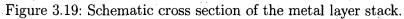

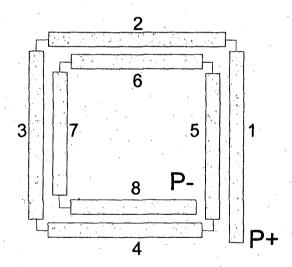

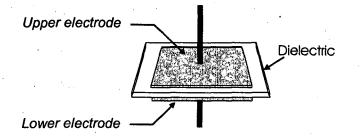

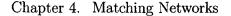

Figure 3.1: Schematic cross-section of an integrated npn Si bipolar transistor using polysilicon contacts and a self-aligned emitter-base-complex. The active transistor lies within the dashed region. The other area is used for contacting to the metalization and for the isolation from other components [Aufinger 01].

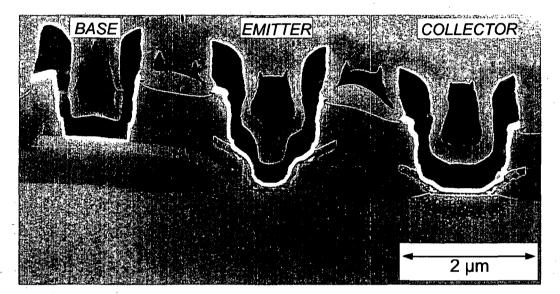

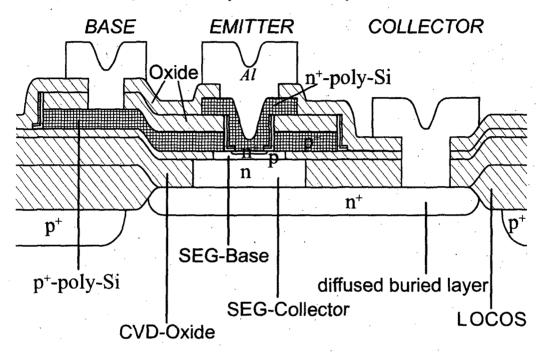

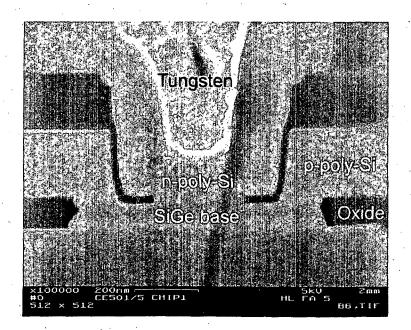

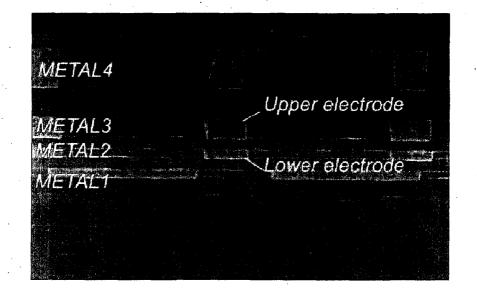

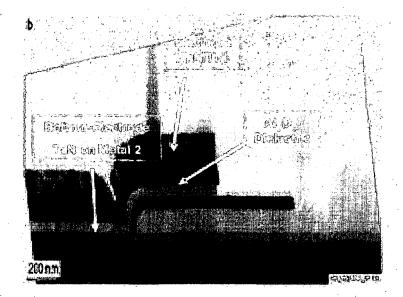

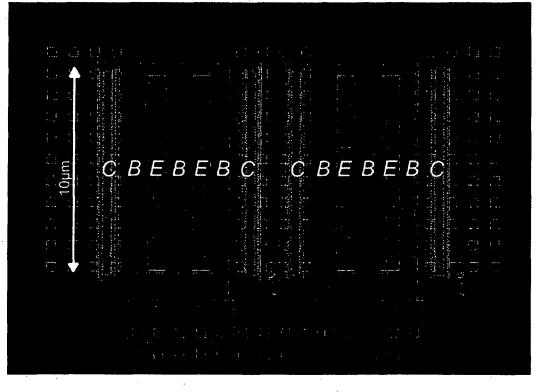

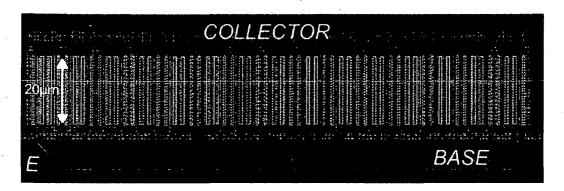

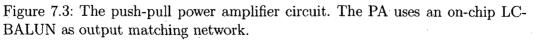

A schematic cross-section of an integrated npn BJT for RF applications is shown in fig. 3.1. The dashed lines outline the active area of the transistor with its three crystal regions, consisting of two n-doped domains for the emitter and the collector and the p-doped domain for the base. The connection to the outer metalized emitter contact is done using a highly n-doped polysilicon while the base is connected using highly p-doped polysilicon. The high doping is necessary to keep the contact resistances as low as possible. To isolate the polysilicon layers from each other a thin oxide-nitride double-layer is used. This so-called spacer is manufactured using anisotropic plasma etching and allows the construction of structures below the lithographic limits [Nakashiba 80, Ning 81]. This is known as the principle of self-alignment. The minimum mask width of the used lithography of the transistor in fig. 3.2 is  $b_E^{mask} = 0.6 \mu m$ . The width of the spacer is typically  $\sim 0.1-0.2 \mu m$ , so that the effective emitter width is typically  $b_{eff} = 0.3 \mu m$ . The relatively low n-doped collector is connected to the right side in fig. 3.1 via a layer with a good conductivity called the buried layer. Figure 3.2 shows a REM micrograph of the transistor.

Figure 3.2: Cross-section of an integrated bipolar transistor (REM photograph) [Klose 93].

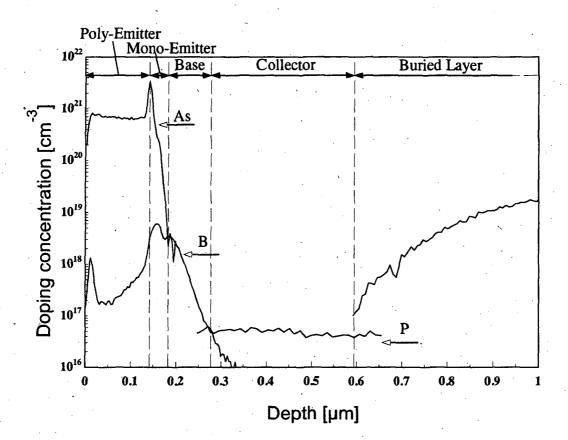

The transistor characteristics depend on the concentration of the doping materials, hence the doping profile. A typical doping profile from emitter to collector of the active transistor area in fig. 3.1, is shown in fig. 3.3 [Klose 93]. Donator materials are typically Arsenide (As) or Phosphor (P) for the emitter and collector and as acceptor material for the base usually Boron (B) is used.

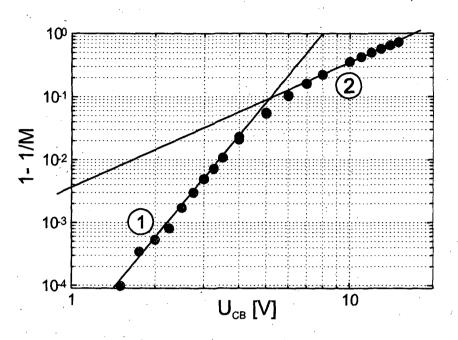

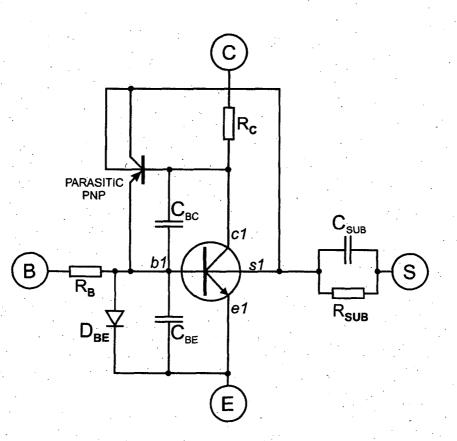

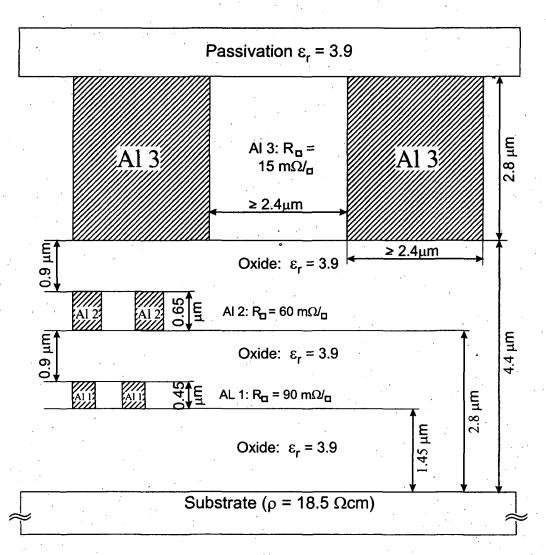

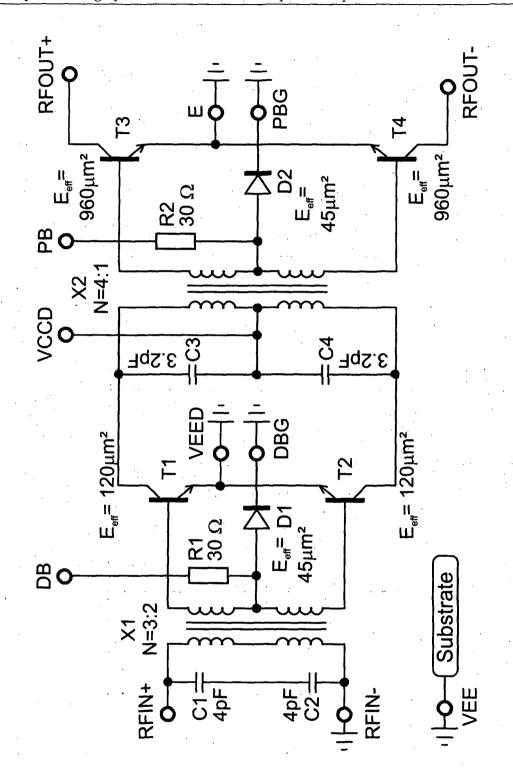

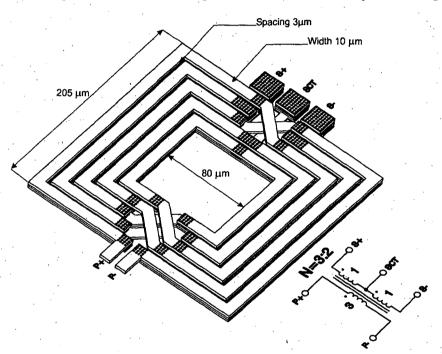

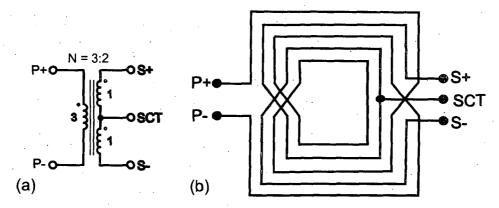

Important for the further development of Si bipolar technologies for high-speed applications is the lateral and vertical down-scaling: In the first sight, the lateral down-scaling increases the packing integration density, but – more important – it reduces the transistor parasitics, as parasitic capacitances and resistances are decreasing. Thus, higher transistor switching speeds can be obtained, as the charging and discharging times are reduced by the lower resistances and capacitances of the transistor. The vertical down-scaling yields to very small base layers helping to reduce the transit time in the transistor. All this requires improvements in the process technology, as presented for example in [Ruge 84]. [Böck 96,a, Böck 96,b] show that using lateral and vertical down-scaling the transit frequency  $f_T$  (described a section 3.4) can be doubled. Further improvements are obtained by