Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

TECHNISCHE UNIVERSITÄT WIEN

### DIPLOMARBEIT

### BURST MODE RECEIVER FOR PASSIVE OPTICAL NETWORKS

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Diplom-Ingenieurs

unter der Leitung von Prof. Horst Zimmermann und Kerstin Schneider Institut für Elektrische Meß- und Schaltungstechnik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

> Johann Glaser Mat. Nr. 9825761 Glasau 3 4191 Vorderweißenbach

Wien, im September 2004

### Abstract

A Burst Mode Receiver chip for Passive Optical Networks is presented. The chip is produced in a standard digital 120 nm CMOS process. High gain and high sensitivity are achieved. This diploma thesis describes basics of optical receivers and the circuit design. The development of the test chip is presented in thorough detail including schematics, simulation graphs and the layout. Two evaluation PCBs were designed and are described too. The measurement results are then presented and followed by a comparison to the simulation results and to other published works.

The incident light wavelength is  $\lambda = 1300 \text{ nm}$ . For this wavelength an external photodiode is necessary because (integrated) silicon photodiodes only receive  $\lambda < 1140 \text{ nm}$ . An external photodiode implies a high input capacity. This lowers the total bandwidth and increases the input referred current noise.

The receiver has a single supply with 1.5 V where the transimpedance amplifier alone only consumes 100 mW. The chip area of the TIA is  $18,840 \,\mu\text{m}^2$ . Control circuits (with large capacitors) add an area of  $36,120 \,\mu\text{m}^2$ . The total area is  $55,000 \,\mu\text{m}^2$ . The chip area itself is  $1.5 \,\text{mm}^2$  containing the pad frame and supply stabilizing capacitors.

The chip achieves a sensitivity of -27.6 dBm at 1.25 GBit/s for a BER =  $10^{-10}$ . At 2.5 GBit/s the sensitivity is -20.4 dBm at the same BER. The value was determined with a bad laser which emits at 2.5 GBit/s an eye not allowing for reliable measurements. The results at the highest bit rate are thus expected to be better when a higher-quality laser source is used.

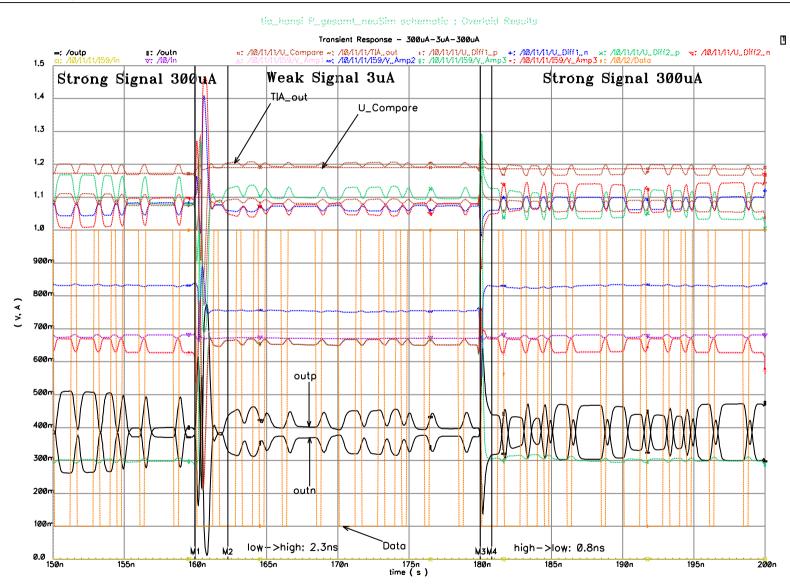

The chip utilizes a special circuit named "Prepare and Hold" for rapid changes of its gain. The gain can be switched within 800 ps from maximum to minimum and within 2.3 ns in the reverse direction. This values are better by a factor of 10 or more compared to any published works which, by the way, operate at only  $1.25 \,\mathrm{GBit/s}$ .

### Zusammenfassung

In dieser Diplomarbeit wird ein Burst Mode Empfänger Chip für Passive Optische Netze präsentiert. Der Chip wurde in einem digitalen Standard-120 nm-CMOS Prozess gefertigt. Hohe Verstärkung und hohe Empfindlichkeit wurden erreicht. In dieser Arbeit werden die Grundlagen und die Schaltungstechnik von optischen Empfängern beschrieben. Die Entwicklung des Test-Chips mit Schaltplänen, Simulationsergebnissen und den Layouts wird besonders genau ausgeführt. Zum Test des Chips wurden zwei Platinen entwickelt, die ebenfalls erklärt werden. Am Ende werden die Messergebnisse präsentiert und mit den Simulations-Ergebnissen und anderen publizierten Ergebnissen verglichen.

Die Wellenlänge des empfangenen Lichts beträgt  $\lambda=1300\,\mathrm{nm}$ . Dafür ist eine externe Photodiode notwendig, da (integrierte) Silizium-Photodioden nur für  $\lambda<1140\,\mathrm{nm}$  geeignet sind. Eine externe Photodiode bedeutet jedoch eine hohe Eingangsknotenkapazität wodurch die Bandbreite der Schaltung verringert und das Rauschen erhöht wird.

Der Empfänger wird mit 1,5 V versorgt wobei der Transimpedanzverstärker selbst eine Leistung von nur 100 mW benötigt. Die Chip-Fläche des TIAs alleine beträgt 18.840  $\mu$ m<sup>2</sup>. Die Steuerschaltung mit großen Kondensatoren erhöht die Fläche um 36.120  $\mu$ m<sup>2</sup> auf 55.000  $\mu$ m<sup>2</sup>. Die Fläche des gesamten Chips ist 1,5 mm<sup>2</sup> wobei die restliche Fläche vom Pad-Frame und den Kondensatoren zur Stabilisierung der Versorgung verbraucht wird.

Der Chip erreicht eine Empfindlichkeit von -27,6 dBm bei 1,25 GBit/s für ein BER =  $10^{-10}$ . Bei 2,5 GBit/s ist die Empfindlichkeit -20,4 dBm bei gleichem BER. Dieser Wert wurde mit einem schlechten Laser gemessen, der bei 2,5 GBit/s ein Auge abstrahlt, das keine zuverlässige Messung erlaubt. Die Messergebnisse sollten bei Verwendung eines passenden Lasers besser sein.

Am Chip wird eine spezielle Schaltung namens "Prepare and Hold" eingesetzt mit der eine sehr schnelle Änderung der Verstärkung erzielt wird. Die Verstärkung kann innerhalb von nur 800 ps vom höchsten auf den geringsten Wert und innerhalb von 2,3 ns in umgekehrter Richtung eingestellt werden. Diese Werte sind um mindestens einen Faktor 10 besser als in aktuell publizierten Arbeiten, die übrigens alle bei nur 1,25 GBit/s arbeiten.

### Acknowledgment

I want to thank Prof. Horst Zimmermann and Kerstin Schneider from the *Institut für elektrische Mess- und Schaltungstechnik* who supervised this diploma thesis. Kerstin advised me in the usage of the chip design software and the laboratory equipment. She gave me countless good hints and stimulated me to creative ideas.

Holger Arthaber (from the same institute) helped me to develop a DC suppression circuit for high frequency circuits. Günther Dorner from Infineon gave me many hints during the layout.

The following companies sent free samples of their products. Special thanks go to them: Maxim (http://www.maxim-ic.com/, voltage regulator and fast semiconductor switch), Fairchild Semiconductors (http://www.fairchildsemi.com/, logic ICs and LEDs), American Technical Ceramics (http://www.atceramics.com/, Ultra-Broadband Capacitors), Epcos (http://www.epcos.com/, Chip and Tantalum Capacitors) and Analog Devices (http://www.analog.com/, Frequency divider chip).

I want to thank my parents who enabled me to freely decide what to study and always supported me to reach my goals. The *University of Technology, Vienna* provided a good and fundamental education. The state of Austria supported me with the national scholarship. Together with stipends of other institutions I was financially independent and could pursue my study without an interruption.

Kudos go to the worldwide open source community which develops numerous highly professional tools. The tools I used most during my diploma thesis are: LATEX, BIBTEX, XFig, GNU Make, GVim, lots of other powerful GNU tools (sed, awk, octave, ...), Netpbm, Linux, GhostScript, GV and many others. Thanks go to their authors, maintainers, documentors, translators and all others who are involved to provide these programs.

Finally I want to thank Infineon http://www.infineon.com/ for making all this possible. Infineon produced the test chip and provided a friendly place to work.

## Contents

|   | Absti  | act                               |         | <br> | <br> |  |  |  | iii |

|---|--------|-----------------------------------|---------|------|------|--|--|--|-----|

|   | Ackn   | owledgment                        |         | <br> | <br> |  |  |  | V   |

|   | Cont   | ents                              |         | <br> | <br> |  |  |  | vii |

|   | List o | of Figures                        |         | <br> | <br> |  |  |  | ix  |

|   | List o | of Tables                         |         | <br> | <br> |  |  |  | xi  |

| 1 | Inti   | oduction                          |         |      |      |  |  |  | 1   |

|   | 1.1    | Overview                          |         | <br> | <br> |  |  |  | 2   |

|   | 1.2    | Outline                           |         | <br> | <br> |  |  |  | 4   |

|   | 1.3    | Specification                     |         | <br> | <br> |  |  |  | 4   |

|   |        | 1.3.1 Bit Duration and Bandwidt   | :h      | <br> | <br> |  |  |  | 6   |

|   |        | 1.3.2 Input Power and PD-Curren   | nt.     | <br> | <br> |  |  |  | 6   |

|   |        | 1.3.3 Bit Error Ratio and Noise ( | Current | <br> | <br> |  |  |  | 8   |

|   |        | 1.3.4 TIA specifications          |         | <br> | <br> |  |  |  | 9   |

| 2 | Op     | tical Receivers                   |         |      |      |  |  |  | 11  |

|   | 2.1    | Communication Techniques          |         | <br> | <br> |  |  |  | 12  |

|   |        | 2.1.1 Multiplex and Multiple Acc  | ess     | <br> | <br> |  |  |  | 12  |

|   | 2.2    | Fiber Communication               |         | <br> | <br> |  |  |  | 13  |

|   |        | 2.2.1 Laser                       |         | <br> | <br> |  |  |  | 13  |

|   |        | 2.2.2 Optical modulator           |         | <br> | <br> |  |  |  | 15  |

|   |        | 2.2.3 Fiber                       |         | <br> | <br> |  |  |  | 16  |

|   |        | 2.2.4 Photodiode                  |         | <br> | <br> |  |  |  | 18  |

|   |        | 2.2.5 Amplifier                   |         | <br> | <br> |  |  |  | 20  |

|   |        | 2.2.6 Slicer                      |         | <br> | <br> |  |  |  | 21  |

|   | 2.3    | Burst Mode                        |         | <br> | <br> |  |  |  | 21  |

### 3 Circuit Design

|   | 3.1        | Transis<br>3.1.1                                                                                                                                            | tors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25<br>26                                                                                     |

|---|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   | 3.2        | Amplifi                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>29                                                                                     |

|   | J.2        | 3.2.1                                                                                                                                                       | Transimpedance amplifier analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                                           |

|   |            | 3.2.1                                                                                                                                                       | CMOS Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                           |

|   |            | 3.2.3                                                                                                                                                       | Common source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                           |

|   |            | 3.2.4                                                                                                                                                       | Differential Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                                                                           |

|   |            | 3.2.5                                                                                                                                                       | Source Follower                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                           |

|   | 3.3        |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                                                                                           |

|   | 5.5        | 3.3.1                                                                                                                                                       | Resistor noise source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                           |

|   |            | 3.3.2                                                                                                                                                       | FET noise sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33                                                                                           |

|   |            | 3.3.3                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                                                                           |

|   |            | 3.3.4                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                           |

|   | 3.4        |                                                                                                                                                             | Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                           |

|   | 0          | 3.4.1                                                                                                                                                       | Process properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40                                                                                           |

|   |            | 3.4.2                                                                                                                                                       | Integrated Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                           |

|   |            | 3.4.3                                                                                                                                                       | Analog Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                                                                           |

|   |            |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 4 | Ser        | nicon                                                                                                                                                       | ductor Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                                           |

|   |            | _                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|   | 4.1        | Structu                                                                                                                                                     | ıre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46                                                                                           |

|   | 4.1        | Structu<br>4.1.1                                                                                                                                            | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>48                                                                                     |

|   | 4.1<br>4.2 | 4.1.1                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                            |

|   |            | 4.1.1                                                                                                                                                       | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                           |

|   |            | 4.1.1<br>Transin                                                                                                                                            | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50                                                                                     |

|   |            | 4.1.1<br>Transin<br>4.2.1                                                                                                                                   | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51                                                                               |

|   |            | 4.1.1<br>Transin<br>4.2.1<br>4.2.2                                                                                                                          | Specification    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .                                                                                                                                                                                                                                      | 48<br>50<br>51<br>51                                                                         |

|   |            | <ul><li>4.1.1</li><li>Transin</li><li>4.2.1</li><li>4.2.2</li><li>4.2.3</li></ul>                                                                           | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>51<br>52                                                                   |

|   |            | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                                               | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>51<br>52<br>54                                                             |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                                               | Specification       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       < | 48<br>50<br>51<br>51<br>52<br>54<br>58                                                       |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare                                                                                    | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>51<br>52<br>54<br>58<br>62                                                 |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1                                                                           | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62                                                 |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2                                                                  | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>51<br>52<br>54<br>58<br>62<br>62<br>63                                     |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3                                                         | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>51<br>52<br>54<br>58<br>62<br>62<br>63<br>64                               |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62<br>62<br>63<br>64<br>64                         |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6                              | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62<br>63<br>64<br>64<br>65                         |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6                              | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62<br>63<br>64<br>64<br>65<br>65                   |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compare                   | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>52<br>62<br>62<br>62<br>63<br>64<br>64<br>65<br>65<br>68       |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compare<br>4.4.1          | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62<br>63<br>64<br>64<br>65<br>65<br>68<br>69       |

|   | 4.2        | 4.1.1<br>Transin<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Prepare<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compare<br>4.4.1<br>4.4.2 | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48<br>50<br>51<br>52<br>54<br>58<br>62<br>62<br>63<br>64<br>64<br>65<br>65<br>68<br>69<br>70 |

|   | 4.5<br>4.6 | Supply                                   | 73<br>75<br>77<br>77 |

|---|------------|------------------------------------------|----------------------|

|   | 4.7        | 4.6.2SimulationSimulationToolsSimulation | 82                   |

| 5 | Pri        | nted Circuit Boards                      | 83                   |

|   | 5.1        | Requirements                             | 83                   |

|   |            | 5.1.1 Measurements                       | 83                   |

|   |            | 5.1.2 PCB Content                        | 84                   |

|   |            | 5.1.3 PCB base material                  | 84                   |

|   | 5.2        | Static PCB                               | 84                   |

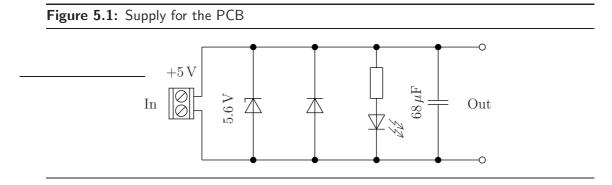

|   |            | 5.2.1 PCB Supply                         | 85                   |

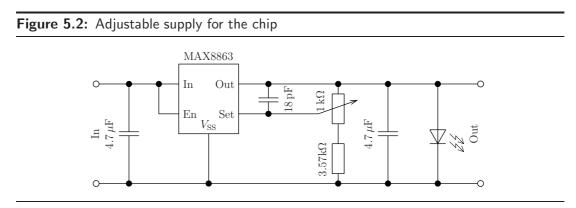

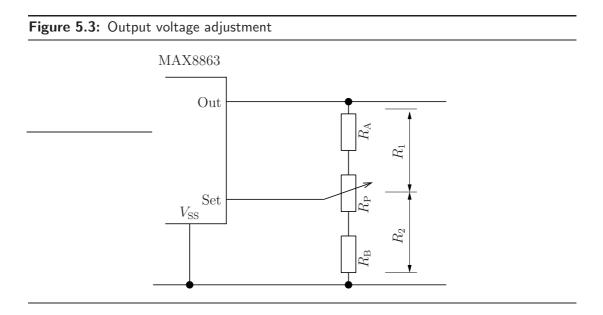

|   |            | 5.2.2 Chip Supply                        | 85                   |

|   |            | 5.2.3 Analog control voltages            | 87                   |

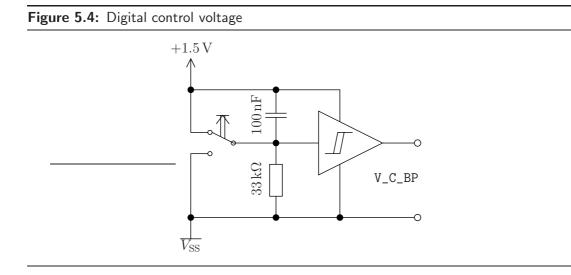

|   |            | 5.2.4 Digital control voltage            | 88                   |

|   |            | 5.2.5 Digital control signals            | 88                   |

|   |            | 5.2.6 Output                             | 88                   |

|   |            | 5.2.7 Chip and photodiode bonds          | 89                   |

|   | 5.3        | Burst PCB                                | 91                   |

|   |            | 5.3.1 Burst Clock                        | 91                   |

|   |            | 5.3.2 Cable lengths and Delay lines      | 91                   |

|   |            | 5.3.3 Control Voltages                   | 95                   |

|   |            | 5.3.4 Power Supply                       | 97                   |

|   |            | 5.3.5 Chip and photodiode bonds          | 98                   |

|   |            | 5.3.6 Layout of the Burst PCB            | 99                   |

|   | 5.4        | Tools                                    | 101                  |

| 6 | Me         | asurements 1                             | 03                   |

| Ū |            |                                          |                      |

|   | 6.1        |                                          | 103                  |

|   |            | 6.1.1 Static Measurements                | 104                  |

|   | 6.0        | 6.1.2 Burst Measurements                 | 105                  |

|   | 6.2        | Eye Diagrams                             | 106                  |

|   | 6.3        | Photons per bit                          | 112                  |

| 7 | Sur        | mmary 1                                  | 13                   |

|   | 7.1        | Specifications and Results               | 113                  |

|   |            | 7.1.1 Sensitivity                        | 114                  |

|   |            | 7.1.2 Switch the gain                    | 114                  |

|   | 7.2        | Comparison to Literature                 | 114                  |

|   | 7.3        | Possible Improvements                    | 115                  |

| 7.4 Conclusion    | 116 |

|-------------------|-----|

| A Abbreviations   | 117 |

| B List of Symbols | 119 |

| Bibliography      | 121 |

| Index             | 125 |

## List of Figures

| 1.1<br>1.2<br>1.3<br>1.4 | Schematic setup of a Passive Optical Network (PON)2Rough schematic of the optical receiver3Optical power and input current6Average input current for "0" s $I_0$ and "1" s $I_1$ 7 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2               | Time Division Multiplex13Overview of a typical optical transmission line14                                                                                                         |

| 2.2                      | Laser $P/I$ characteristic                                                                                                                                                         |

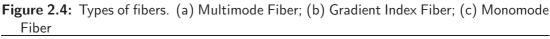

| 2.4                      | Types of Fibers         16                                                                                                                                                         |

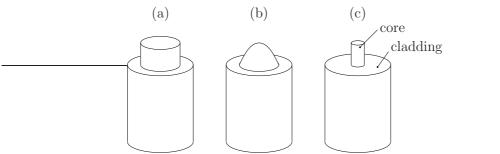

| 2.5                      | Electrical circuit with a photodiode                                                                                                                                               |

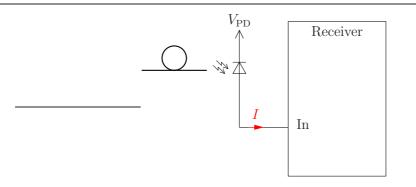

| 2.6                      | Structure of a PIN photodiode                                                                                                                                                      |

| 2.7                      | Opamp circuit as TIA                                                                                                                                                               |

| 2.8                      | Slicer in the eye diagram                                                                                                                                                          |

| 2.9                      | Schematic setup of a Passive Optical Network (PON)                                                                                                                                 |

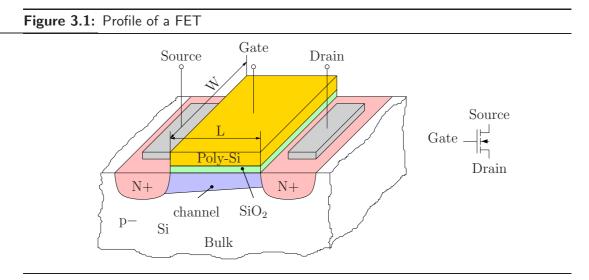

| 3.1                      | Profile of a FET                                                                                                                                                                   |

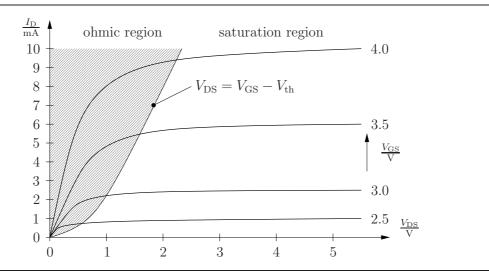

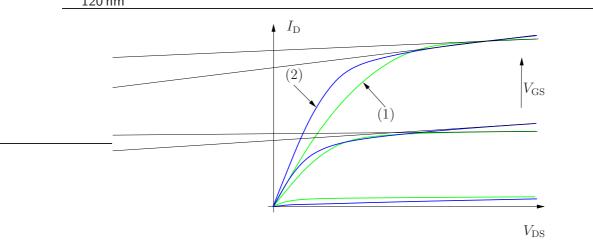

| 3.2                      | Output characteristic of an N-channel FET   27                                                                                                                                     |

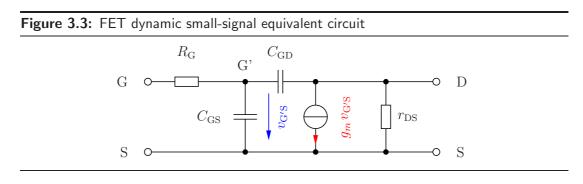

| 3.3                      | FET dynamic small-signal equivalent circuit   28                                                                                                                                   |

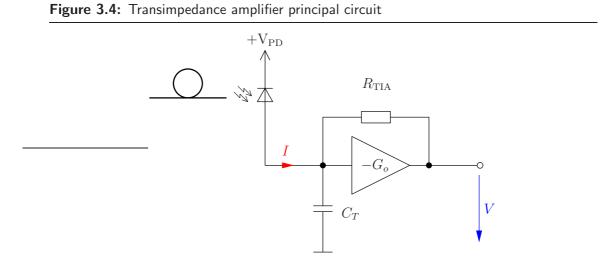

| 3.4                      | Transimpedance amplifier principal circuit                                                                                                                                         |

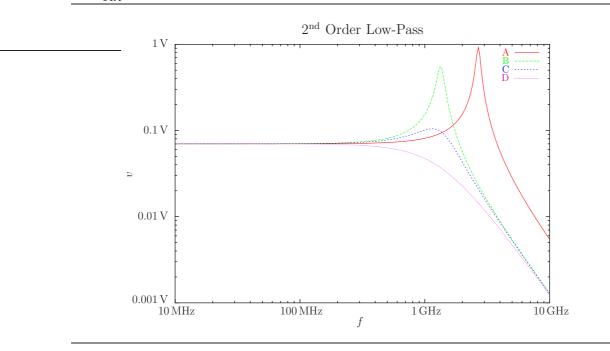

| 3.5                      | Frequency response of second order lowpass                                                                                                                                         |

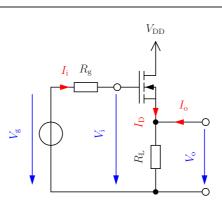

| 3.6                      | Example of a FET transimpedance amplifier                                                                                                                                          |

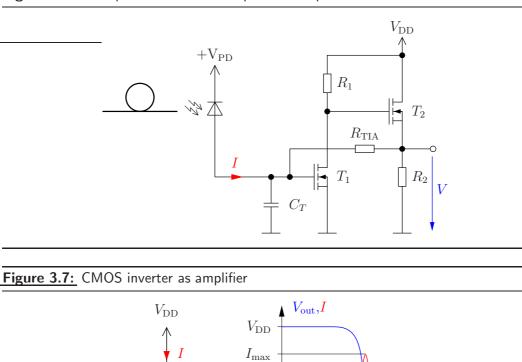

| 3.7                      | CMOS inverter as amplifier                                                                                                                                                         |

| 3.8                      | Common source circuit                                                                                                                                                              |

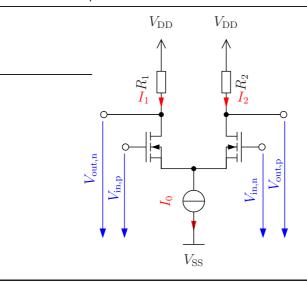

| 3.9                      | Differential amplifier                                                                                                                                                             |

| 3.10                     | Common drain circuit                                                                                                                                                               |

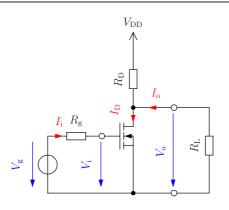

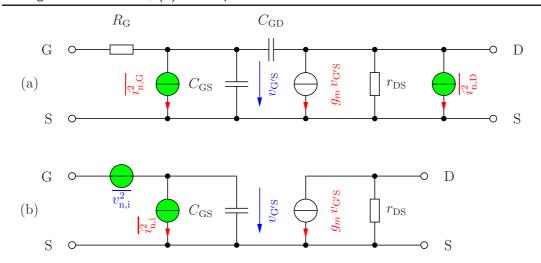

| 3.11                     | FET equivalent circuit with noise sources                                                                                                                                          |

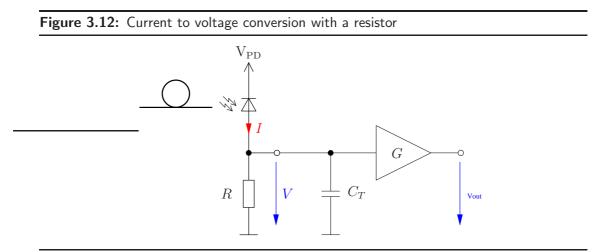

| 3.12                     | Current to voltage conversion with a resistor                                                                                                                                      |

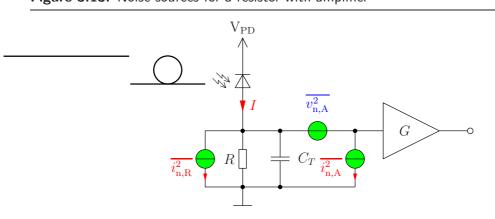

| 3.13                     | Noise sources for a resistor with amplifier                                                                                                                                        |

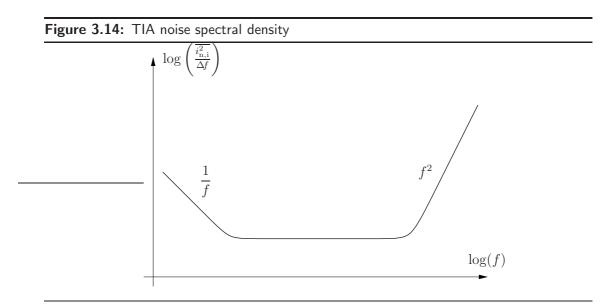

| 3.14                     | TIA noise spectral density                                                                                                                                                         |

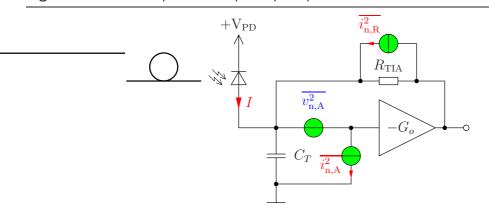

| 3.15 | Transimpedance amplifier principal circuit with noise sources |

|------|---------------------------------------------------------------|

| 3.16 | Early effect of two NMOS FETs                                 |

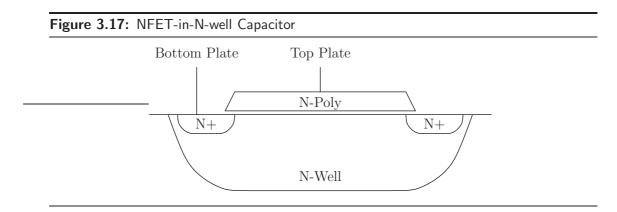

| 3.17 | NFET-in-N-well Capacitor                                      |

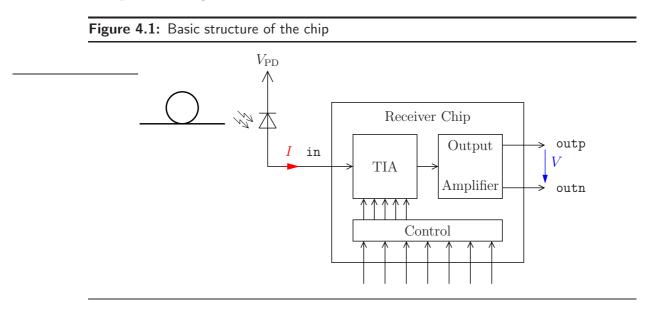

| 4.1  | Basic structure of the chip                                   |

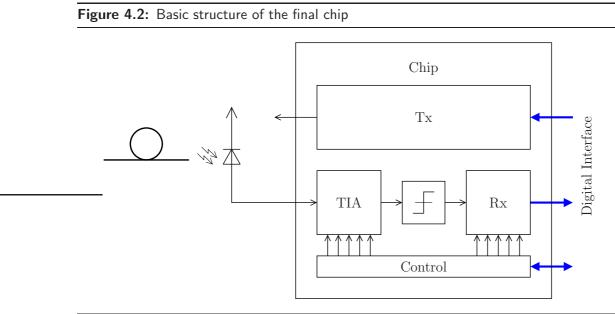

| 4.2  | Basic structure of the final chip                             |

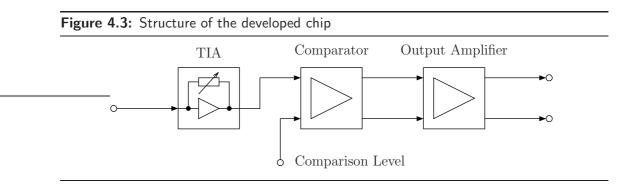

| 4.3  | Structure of the developed chip                               |

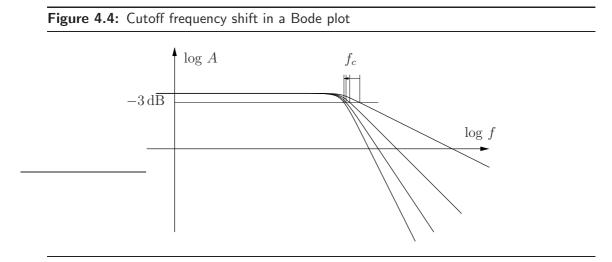

| 4.4  | Cutoff frequency shift in a Bode plot                         |

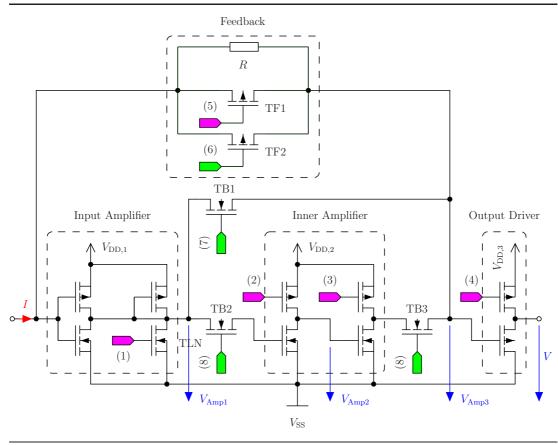

| 4.5  | Schematic of the developed TIA                                |

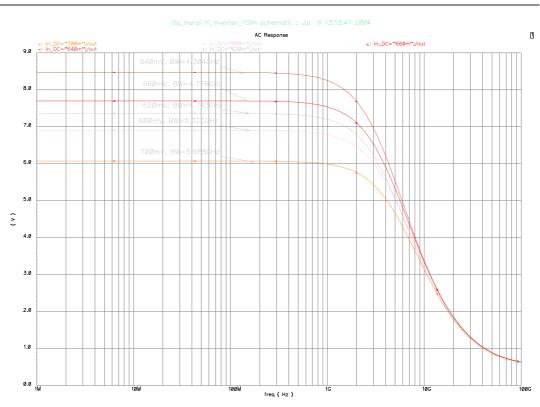

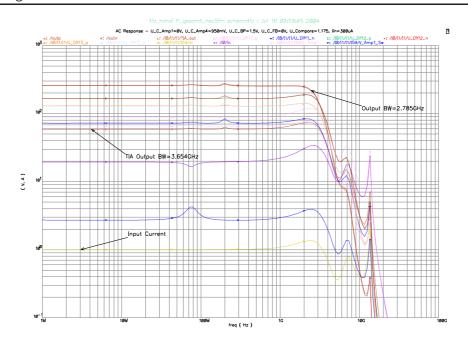

| 4.6  | AC response of the input amplifier                            |

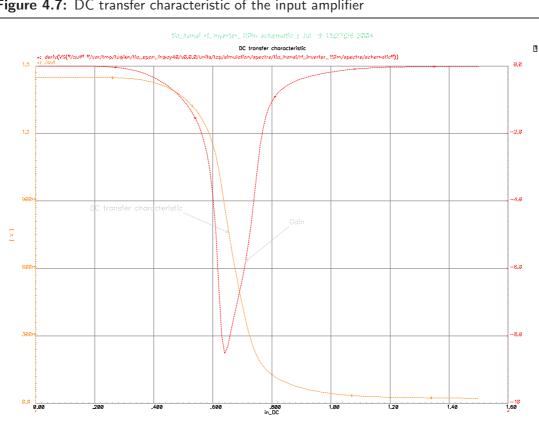

| 4.7  | DC transfer characteristic of the input amplifier             |

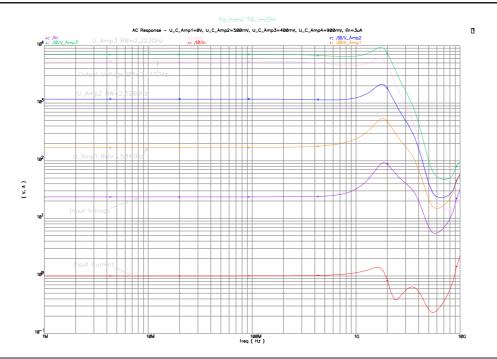

| 4.8  | AC transfer characteristic of the total TIA                   |

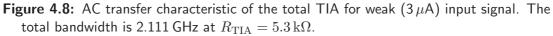

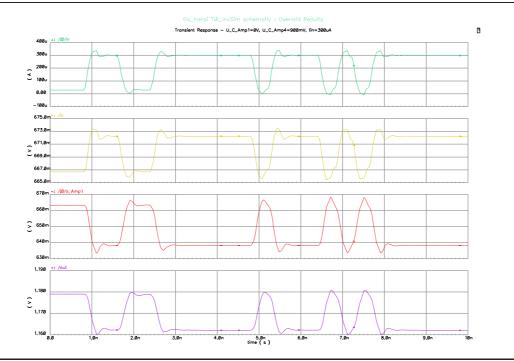

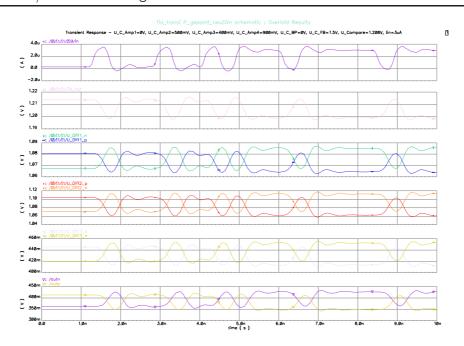

| 4.9  | Transient analysis of the total TIA                           |

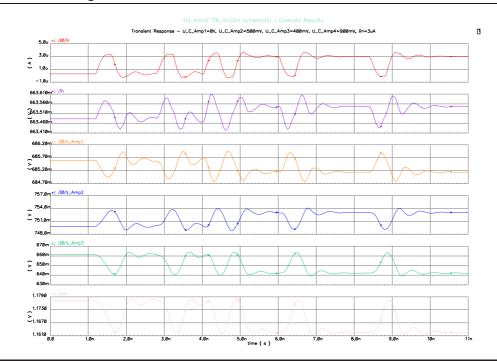

| 4.10 | AC transfer characteristic of the total TIA                   |

| 4.11 | Transient analysis of the total TIA                           |

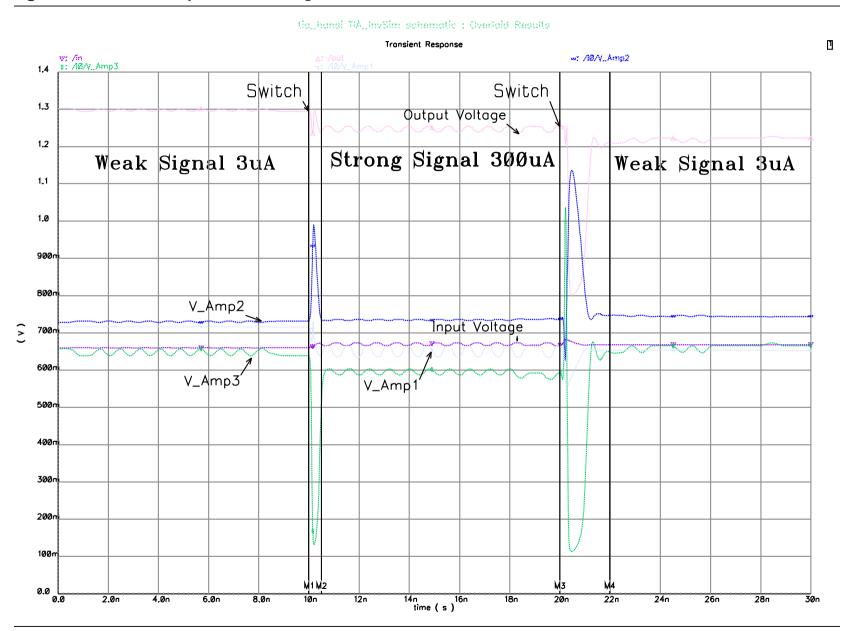

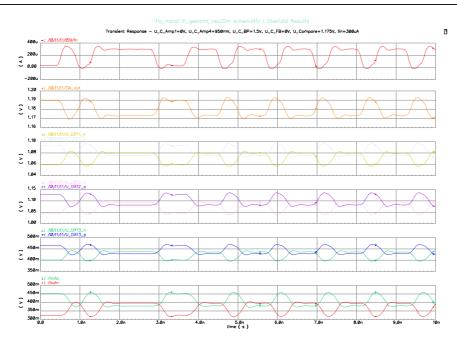

| 4.12 | Transient analysis with switch of gain                        |

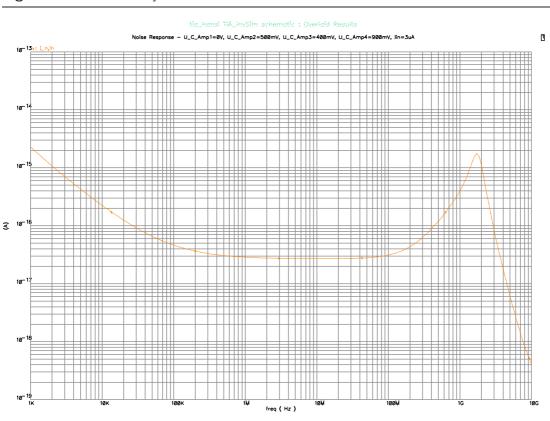

| 4.13 | Noise analysis of the total TIA                               |

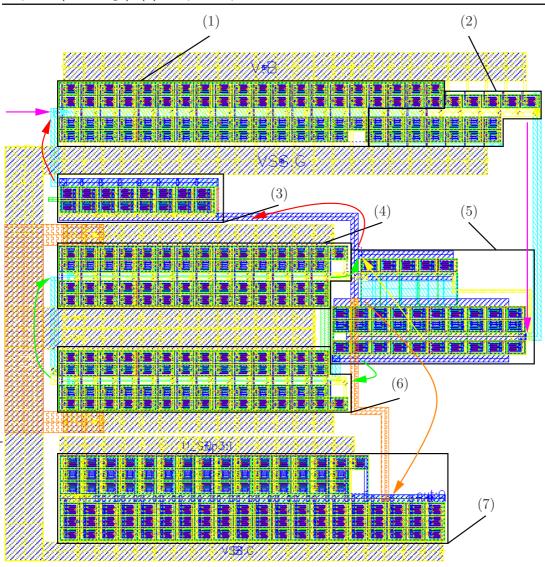

| 4.14 | Layout of the TIA                                             |

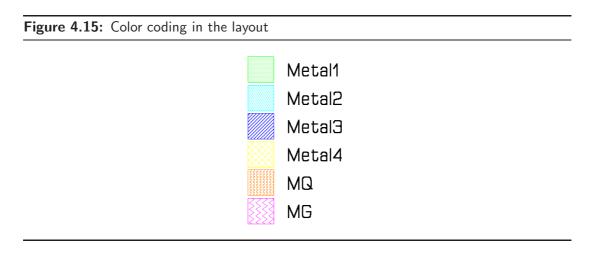

| 4.15 | Color coding in the layout                                    |

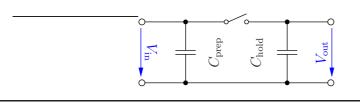

| 4.16 | Basic structure of the P&H circuit                            |

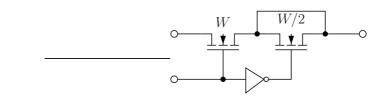

| 4.17 |                                                               |

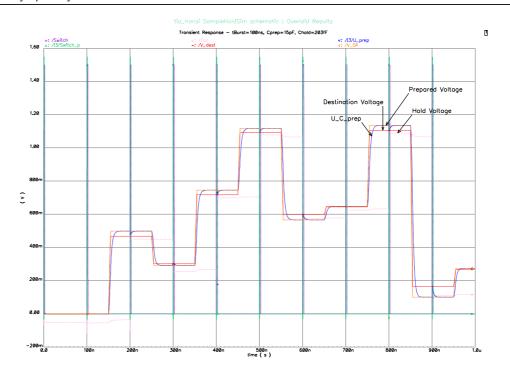

| 4.18 | Ten P&H cycles                                                |

|      | The transient process in the P&H                              |

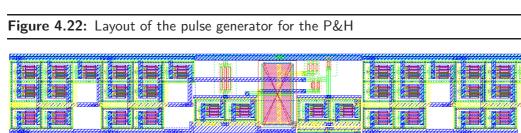

|      | Layout of the P&H circuit                                     |

|      | Schematic of the pulse generator                              |

|      | Layout of the pulse generator for the P&H                     |

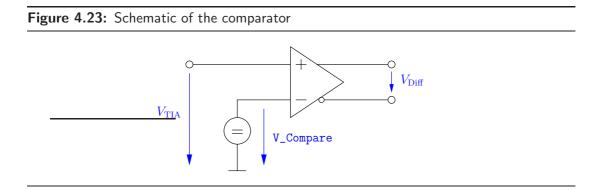

|      | Schematic of the comparator                                   |

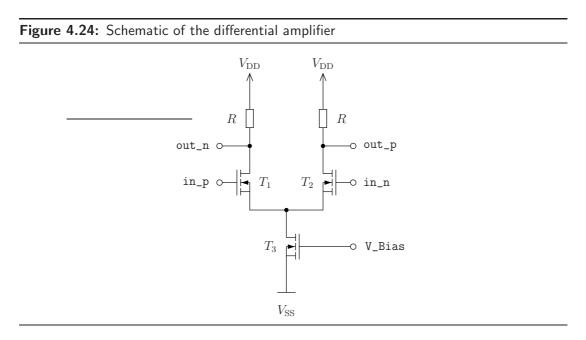

|      | Schematic of the differential amplifier                       |

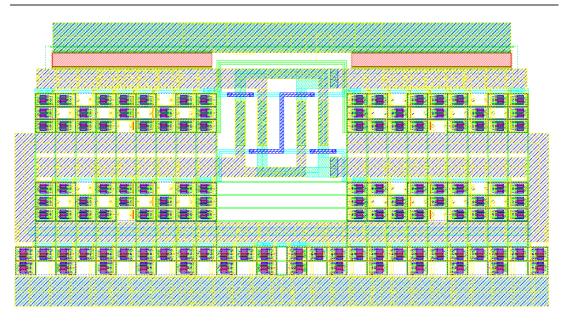

|      | Layout of the differential amplifier rf_Diff                  |

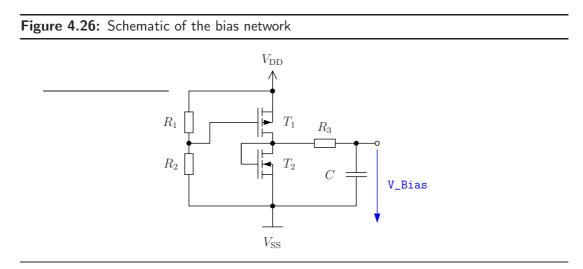

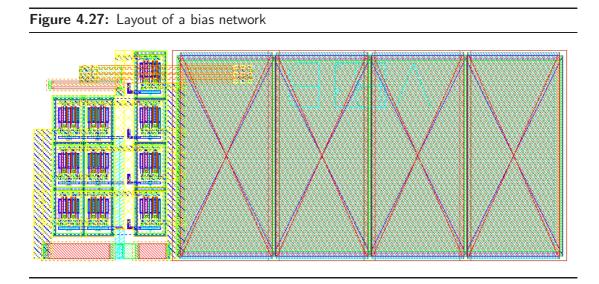

|      | Schematic of the bias network                                 |

|      | Layout of a bias network                                      |

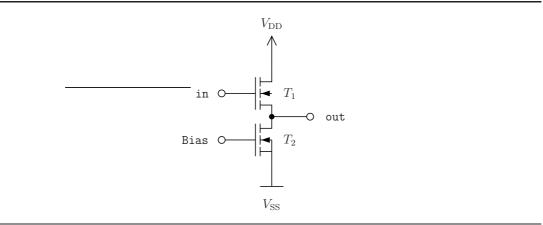

|      | Schematic of the NMOS source follower                         |

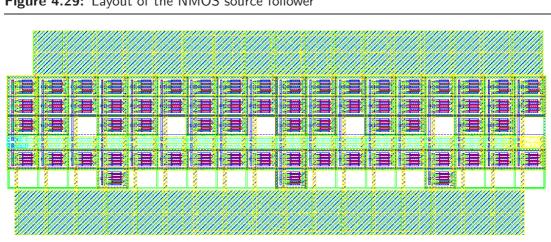

| 4.29 | Layout of the NMOS source follower                            |

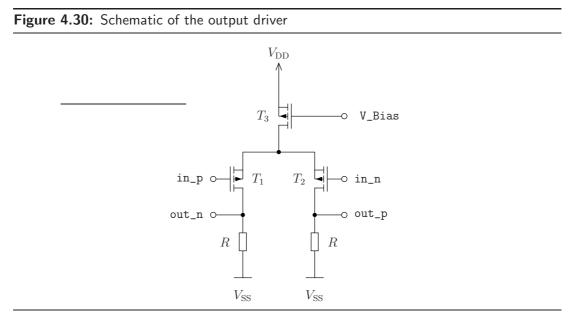

| 4.30 | Schematic of the output driver                                |

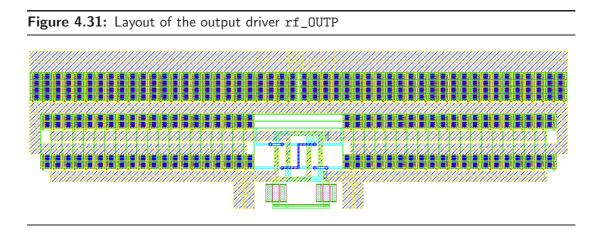

| 4.31 | Layout of the output driver rf_OUTP                           |

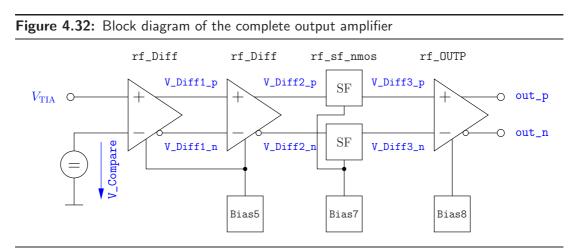

| 4.32 | Block diagram of the complete output amplifier                |

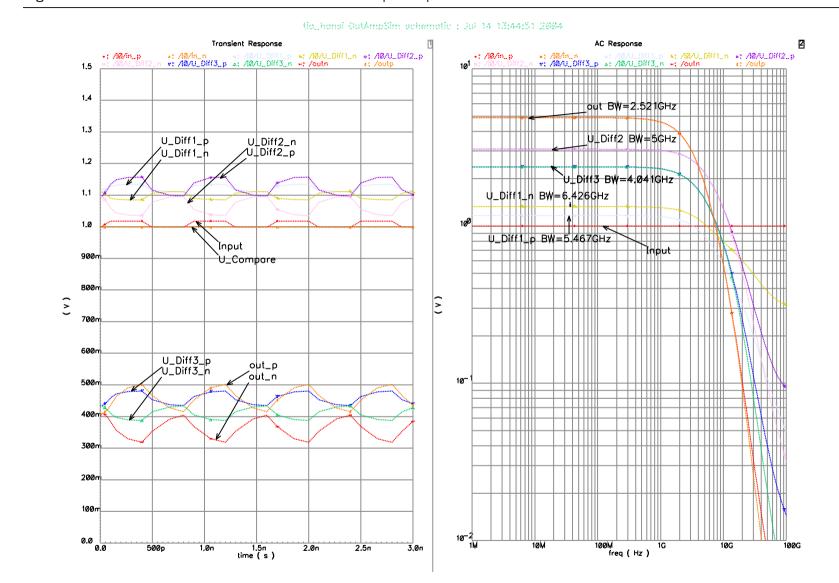

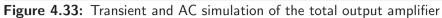

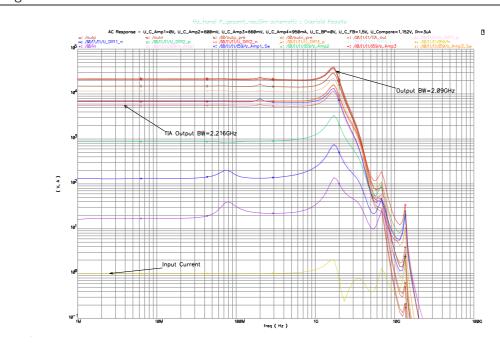

| 4.33 | Transient and AC simulation of the total output amplifier     |

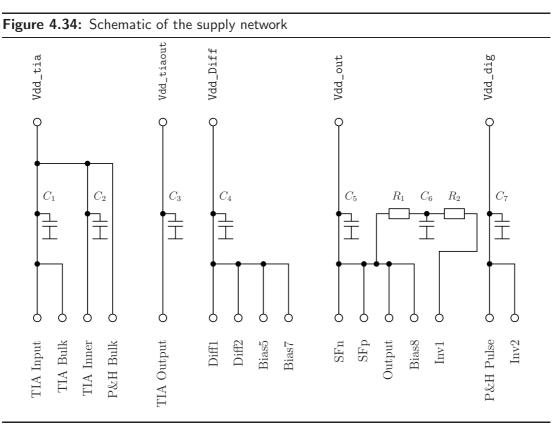

| 4.34 | Schematic of the supply network                               |

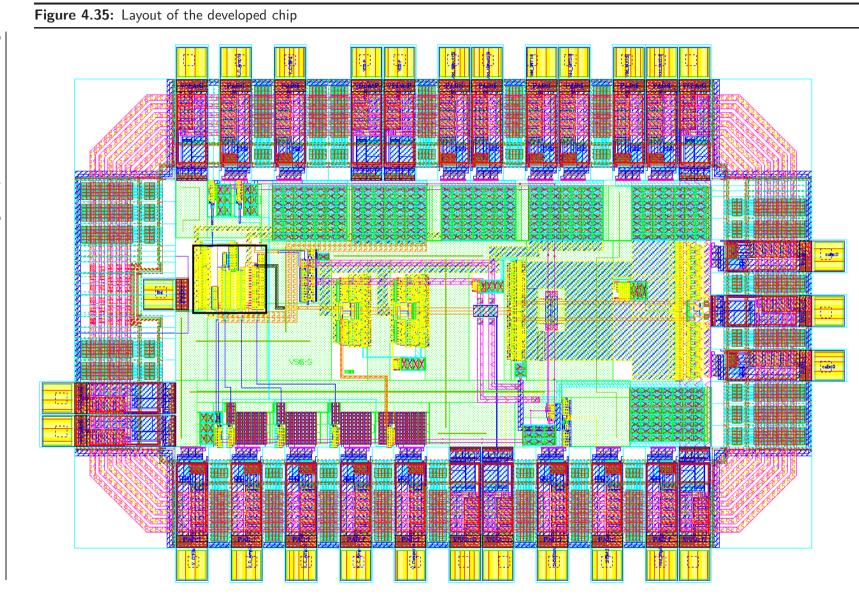

| 4.35 | Layout of the developed chip                                  |

|      |                                                               |

|      |                                                               |

|      |                                                               |

| 4.38 | AC transfer characteristic of the total developed chip        |

| 4.39 | Transient analysis of the total developed chip                |

| 4.40 | Chip transient analysis with switch of gain                                               | 1 |

|------|-------------------------------------------------------------------------------------------|---|

| 5.1  | Supply for the PCB                                                                        | 5 |

| 5.2  | Adjustable supply for the chip                                                            | 5 |

| 5.3  | Output voltage adjustment                                                                 | 6 |

| 5.4  | Digital control voltage                                                                   | 8 |

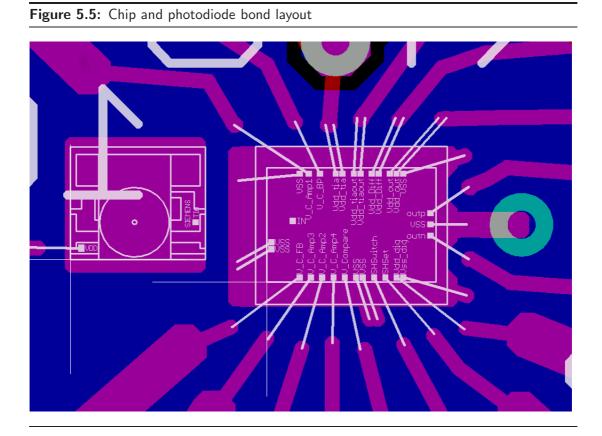

| 5.5  | Chip and photodiode bond layout                                                           | 9 |

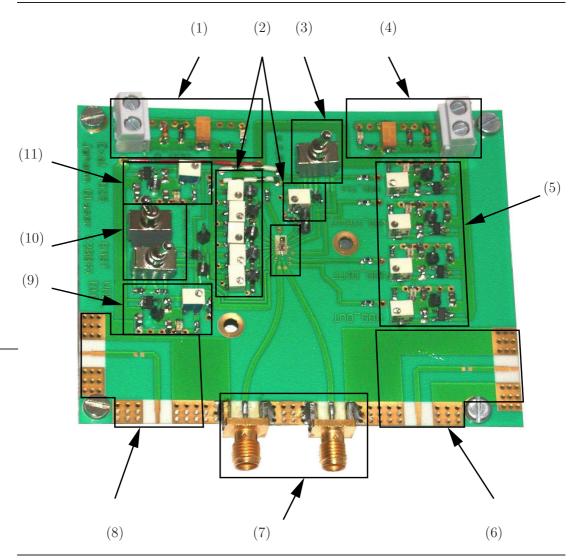

| 5.6  | Static PCB photograph                                                                     | 0 |

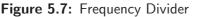

| 5.7  | Frequency Divider                                                                         | 2 |

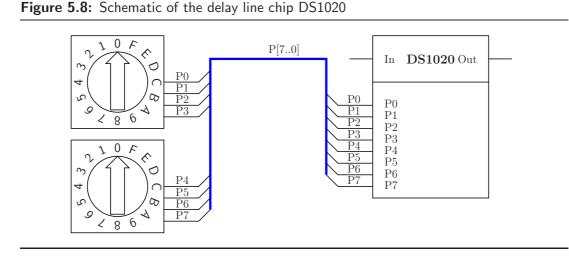

| 5.8  | Schematic of the delay line chip DS1020                                                   | 2 |

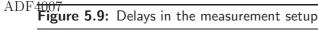

| 5.9  | Delays in the measurement setup                                                           | 3 |

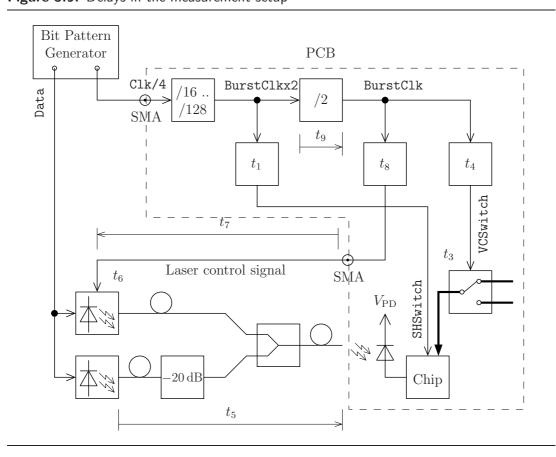

| 5.10 | Timing Diagram9                                                                           | 4 |

| 5.11 | Analog Control voltage switch                                                             | 6 |

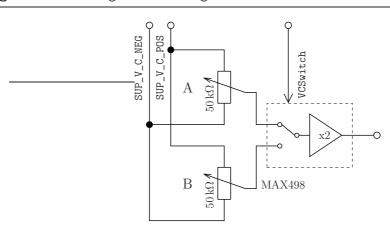

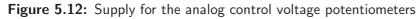

| 5.12 | Supply for the analog control voltage potentiometers 9                                    | 6 |

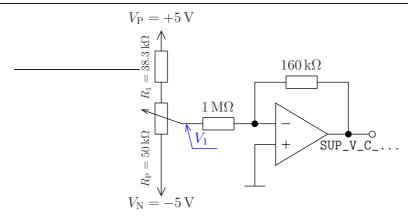

| 5.13 | Supply for the Burst PCB                                                                  | 7 |

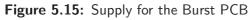

| 5.14 | Chip and photodiode bond layout                                                           | 8 |

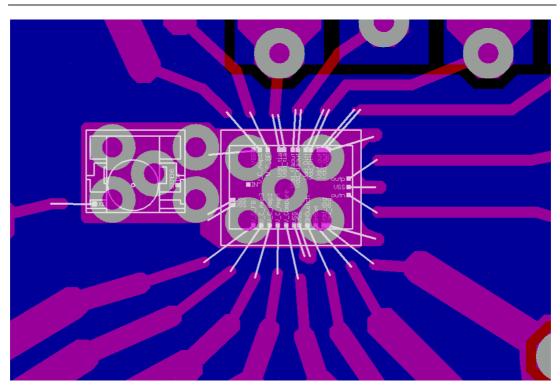

| 5.15 | Supply for the Burst PCB                                                                  | 9 |

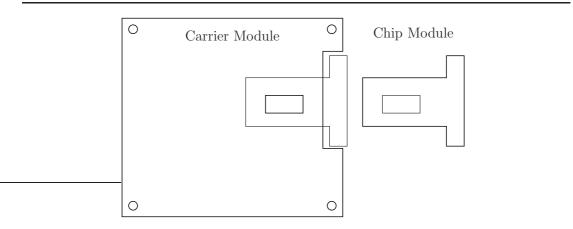

| 5.16 | Static PCB photograph                                                                     | 0 |

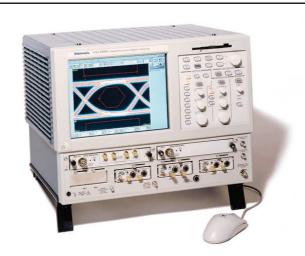

| 6.1  | Tektronix CSA8000 Communication Signal Analyzer                                           | 4 |

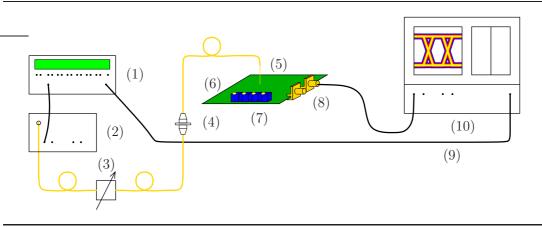

| 6.2  | Setup for the static measurement (eye diagram)                                            | 5 |

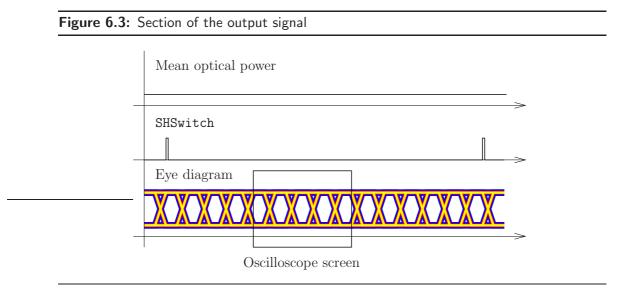

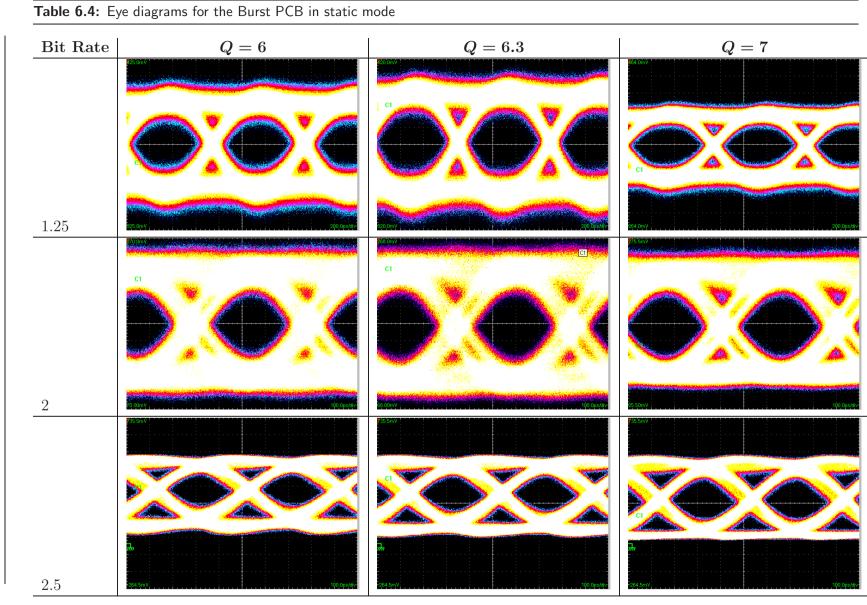

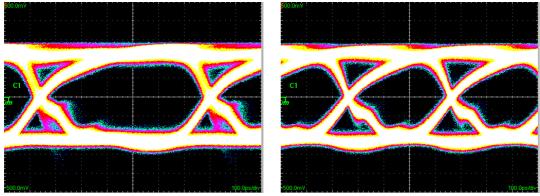

| 6.3  | Section of the output signal                                                              | 6 |

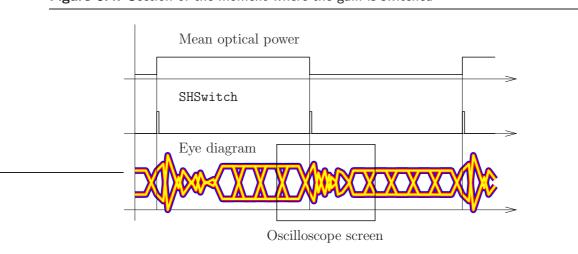

| 6.4  | Section of the moment where the gain is switched $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$ | 7 |

### List of Tables

| 1.1 | Specification of the chip                                                         |

|-----|-----------------------------------------------------------------------------------|

| 1.2 | Specification of the components around the chip                                   |

| 1.3 | Resulting additional specification of the chip                                    |

| 1.4 | Typical values for BER and $Q$                                                    |

| 2.1 | Types of fibers         17                                                        |

| 4.1 | Input power and current for typical values of $\overline{P}_{ m opt}$             |

| 4.2 | Control voltages as labeled in Fig. 4.5                                           |

| 4.3 | Areas of the layout of the TIA in Fig. 4.14                                       |

| 4.4 | Supply destination descriptions                                                   |

| 4.5 | Power consumption at the supply pads                                              |

| 5.1 | RO4003 $^{ m TM}$ high frequency circuit material properties $\ldots$ $\ldots$ 84 |

| 5.2 | Timing parameters                                                                 |

| 6.1 | Typical values for BER and $Q$                                                    |

| 6.2 | Corrected results                                                                 |

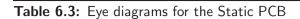

| 6.3 | Eye diagrams for the Static PCB                                                   |

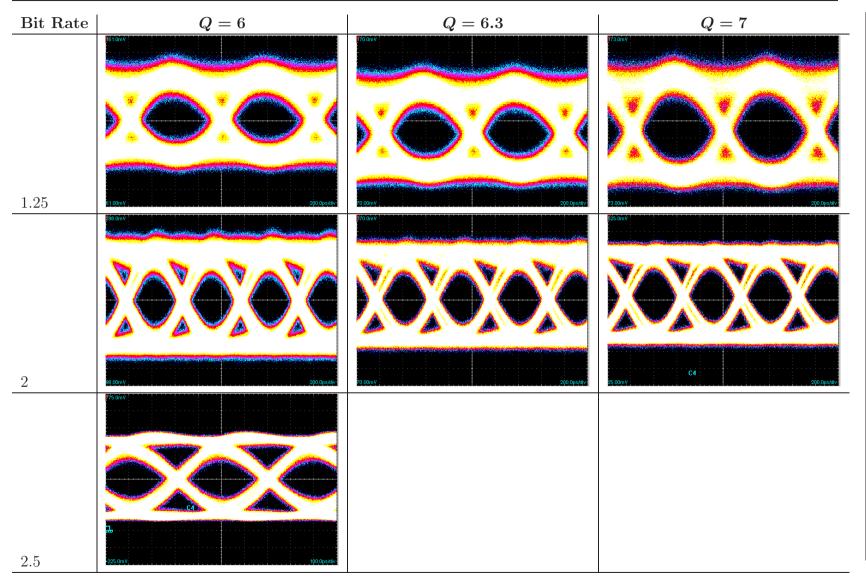

| 6.4 | Eye diagrams for the Burst PCB in static mode                                     |

| 7.1 | Comparison to other works                                                         |

# 1

### Introduction

**B** ROADBAND internet access is currently one of the fastest growing markets in telecommunication. Common technologies are "x Digital Subscriber Line (xDSL)" and cable TV. The most promising future technology is *Passive Optical Network (PON)*. The catch word "*Fiber To The x (FTTx)*" is used. Examples include

- Fiber To The Home (FTTH),

- Fiber To The Desk (FTTD),

- Fiber To The Office (FTTO),

- Fiber To The Curb (FTTC),

- Fiber To The Building (FTTB).

A fiber cable is directly available at the host.

### 1.1 Overview

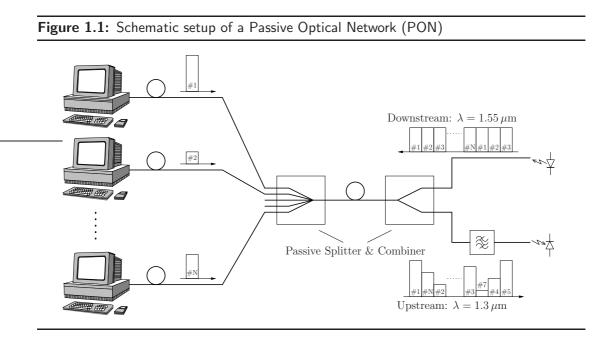

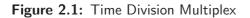

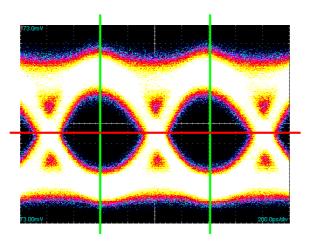

In PONs (see Fig. 1.1) there is a single fiber to every end station. Full duplex transmission is realized with different wavelengths for upstream ( $\lambda = 1.3 \,\mu$ m) and downstream ( $\lambda = 1.55 \,\mu$ m) communication. At the central station all fibers are joined with a *passive* star coupler. There is a single laser and a single *Photodiode* (*PD*). Data for the various end stations is sent and received in *Time Division* Multiplex (*TDM*). This means that the data packets are sent as bursts via the fiber. Every burst is dedicated to one end station. A single burst only contains a few bits (approx. 400, compare [Säc01]).

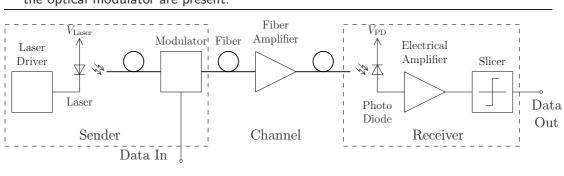

This diploma thesis deals with the development and test of a *Burst Mode Receiver* (BMR) chip for PONs (see Fig. 1.1). The various end stations may have different distance to the central office. This results in different optical power received in the central office because of the fiber attenuation. A BMR has to adapt its *gain* according to the incoming intensity. Higher level protocols provide the control signals to the optical receiver.

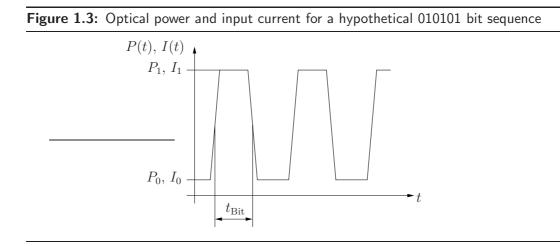

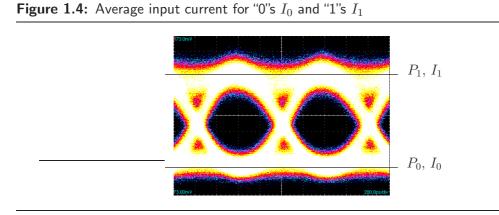

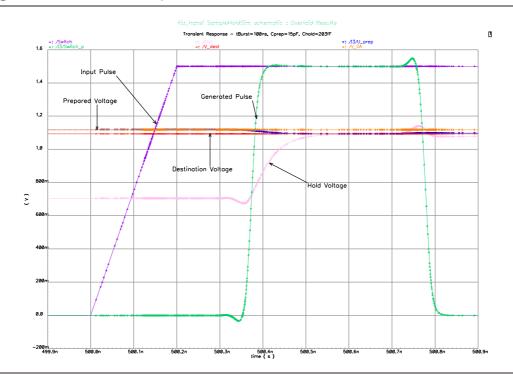

The intensity of incident light can vary by 20 dB which means 40 dB input current variation because the photodiode linearly converts the optical power to electrical current (see (1.3)). To avoid a loss of data transfer rate, the change of gain must be settled quickly. Only a few bits are allowed to be lost. In Fig. 4.12 the simulation result of this process is shown.

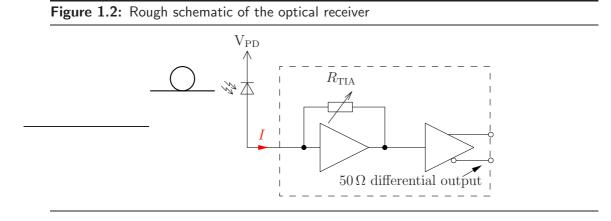

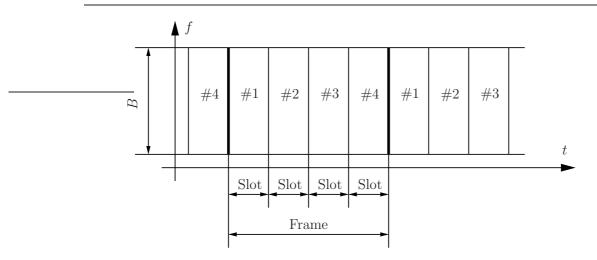

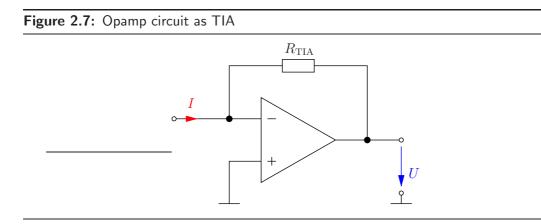

In Fig. 1.2 the principal structure of the optical receiver is depicted. The light is received by the PD. It converts the optical power to electrical current. This enters the BMR chip via a bond wire. The first stage is implemented as a so called

Trans-impedance Amplifier (TIA). This converts the current from the photodiode to a voltage. The TIA is followed by the  $50 \Omega$  output driver. It has a built-in conversion from the single ended signal to a differential signal.

For cost effective central office equipment, the BMR is included in the digital receiver chip. This combination of an analog amplifier and a digital receiver and control unit is called a *System on Chip (SoC)*.

Including an analog front end onto a mostly digital chip has several advantages. Apparently there is only one chip instead of two. This saves packaging cost and board space. The signal line from the analog amplifier to the digital decision device doesn't have to leave a chip package, go via the PCB board and enter another chip. This increases the bandwidth. Finally there is only one chip to produce which decreases costs additionally.

The disadvantage of this combinations is that the digital part will introduce substrate noise to the analog part. Both parts have to be isolated carefully.

An on-chip PD would even more increase the bandwidth and decrease the noise. Unfortunately silicon photodiodes are only able to detect light up to wavelengths  $\lambda < 1140 \text{ nm}$  (see [Lee01]). For the employed wavelength of  $\lambda = 1300 \text{ nm}$  an external PD is necessary. For more details refer to Sec. 2.2.4.

However, this diploma thesis is about the development of the analog part only. There is no digital part available. For *characterization and measurement* of the TIA, its output has to be fed into measurement equipment. For high frequencies these are only available as  $50 \Omega$  devices. Therefore a strong output amplifier is included at the test chip. This will not be necessary in the final product.