Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

TECHNISCHE UNIVERSITÄT WIEN VIENNA UNIVERSITY OF TECHNOLOGY

## DISSERTATION

# Solid State Power Amplifier for DAB in L-Band

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Markus L. Mayer Matrikelnummer: 9025322 Buchengasse 56/25 A-1100 Wien geb. 13. März 1969 in Schärding

Wien, im Dezember 2003

Mayer dearhus

1. Begutachter O.Univ.Prof. Dipl.-Ing. Dr. Gottfried Magerl 2. Begutachter Univ.Prof. Dr.-Ing.habil. Robert Weigel

## Kurzfassung

Digital Audio Broadcasting, DAB, ist die fundamentalste Weiterentwicklung in der Rundfunktechnologie seit der Einführung von UKW Stereo Rundfunk. Es ermöglicht dem Zuhörer einen kristallklaren Empfang, leicht zu bedienende Empfangsgeräte und ein deutlich umfangreicheres Angebot and Sendern und Services.

Volle Flächendeckung eines dicht bebauten Gebietes kann durch die Schattenbildung hoher Gebäude oder ähnlicher Hindernisse nur durch eine zusätzliche Versorgung abgedeckt werden. Für diesen Zweck werden "Gap-Filler" Sendeeinheiten benötigt die das Signal des Hauptsenders empfangen und verstärkt in die nicht versorgten Gebiete abstrahlen. Die Ausgangsleistung derartiger Sendeeinheiten beträgt typischerweise einige Watt.

Das DAB System verwendet Sendesignale mit hoher Amplitudendynamik die hochlineare Verstärker erfordern. Für den autonomen Betrieb von Gap-Filler Sendeeinheiten muss eine Maximierung des Wirkungsgrades angestrebt werden um eine Energieversorgung durch Solarenergie zu ermöglichen. Des Weiteren soll die Baugröße der Sendeeinheiten minimiert werden. Dünnfilmtechnologie ist für eine mittlere Stückzahl im Vergleich zu MMIC Technologie eine hervorragende und kosteneffiziente Möglichkeit der Miniaturisierung. Das verlustarme Keramiksubstrat erlaubt den Entwurf von passiven Bauteilen mit kontinuierlichem Wertespektrum, hoher Güte und hoher Fertigungsgenauigkeit.

Im Rahmen dieser Dissertation wurde ein halbleiterbasierender DAB-Leistungsverstärker in Dünnfilmtechnologie entwickelt um die konzeptionelle Machbarkeit einer gleichzeitigen Linearitäts- und Wirkungsgradoptimierung zu zeigen.

In den letzten 20 Jahren wurden von vielen Forschern Möglichkeiten zur Wirkungsgradsteigerung bei halbleiterbasierenden Mikrowellenleistungsverstärkern untersucht. Mit der Einführung von komplexen digitalen Modulationsverfahren mit hoher Amplitudendynamik (z.B. OFDM, CDMA, ...) verstärkte sich in den letzten 5-10 Jahren das Forschungsinteresse an hochlinearen Leistungsverstärkern. Dabei wurden die Quellen der Nichtlinearitäten untersucht und leistungsfähige Linearisierungstechniken von verschiedenen Forschern entwickelt. Die Linearitätsverbesserung einer Verstärkerschaltung wurde meistens durch eine Verbesserung der Halbleitertechnologie und sorgfältiger Arbeitspunktwahl erreicht, selten aber durch eine Optimierung der Verstärkerschaltung selbst.

Klasse F ist ein wohlbekanntes Konzept für den hocheffizienten Verstärkerentwurf. Dennoch gibt es nur wenige Untersuchungen am Linearitätsverhalten der harmonischen Klasse F Ausgangsterminierung und in keiner uns bekannten Publikation wurden die optimalen Phasenwinkel der harmonischen Terminierungen für optimale Linearität angegeben. In dieser Arbeit wurde, basierend auf nichtlinearen Simulationen, das Klasse F Verstärkerkonzept in Hinblick auf die Optimierung von Linearität und Wirkungsgrad erforscht. Um die Linearität weiter zu steigern, wurde eine harmonische Terminierung am Transistoreingang auf ihr Potential zur Verbesserung von Linearität und Wirkungsgrad untersucht. Eine Hybridkonfiguration wurde zur Erreichung der erforderliche Ausgangsleistung gewählt. Zur einfachen Charakterisierung und zur erhöhten Flexibilität wurde der Verstärker in einem modularen Konzept entwickelt.

Da es am Institut keine Erfahrung mit Dünnfilmtechnologie gab, wurde der Fertigungsprozess des gewählten Herstellers evaluiert um die Tauglichkeit der verwendeten Bauteilmodelle zu prüfen. Für multiharmonische Verstärkerterminierung werden passive Bauteile mit hoher Güte und Computermodelle mit hoher Genauigkeit benötigt. Da es in der verwendeten Simulationsumgebung kein ausreichend genaues Modell für Dünnfilmspiralinduktivitäten vorhanden war, wurde ein neues, skalierbares Spiralinduktivitätsmodell entwickelt das eine genaue Vorhersage inklusive aller parasitären Elemente und der geometrischen Parameter in einem weiten Induktivitätsbereich erlaubt. Dieses Modell ist ein fundamentales Tool für die Entwicklung von harmonischen Abschlüssen da es einen iterativen Spulenentwurfsprozess eliminiert. Im Weiteren wurden alle verwendeten passiven Bauteilserien charakterisiert und auch von diesen wurden skalierbare Modelle entwickelt. Um eine hohe Zuverlässigkeit der Transistoren zu gewährleisten wurde die Montagetechnik des ungehäusten Transistors untersucht und optimiert.

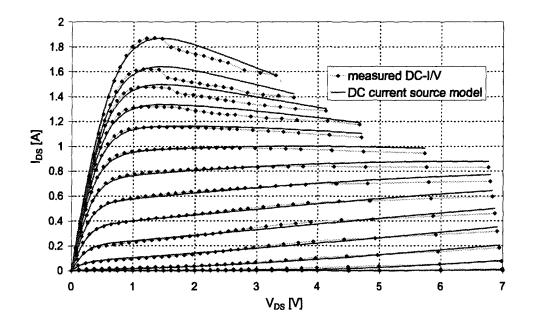

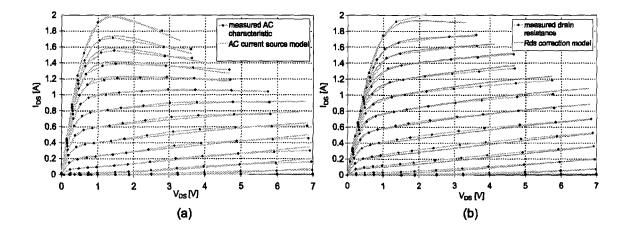

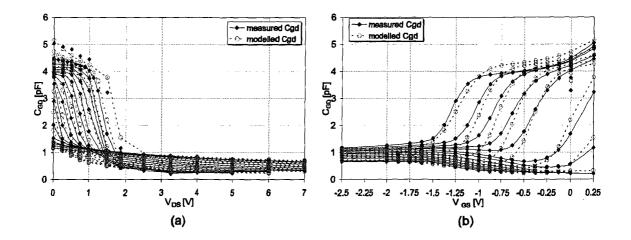

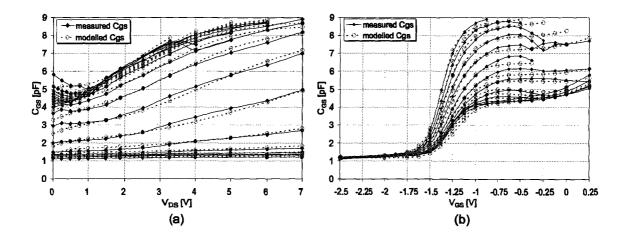

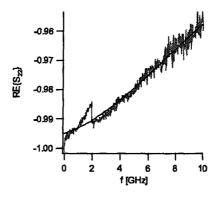

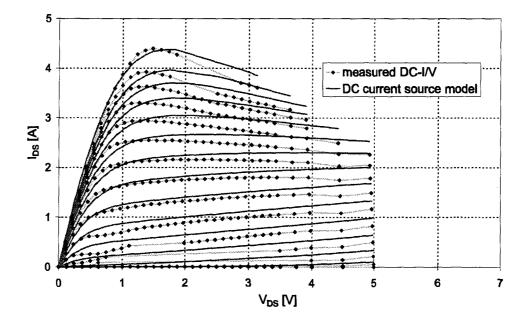

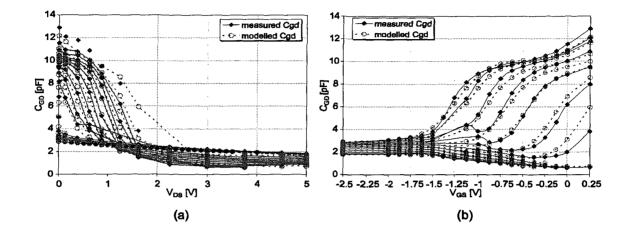

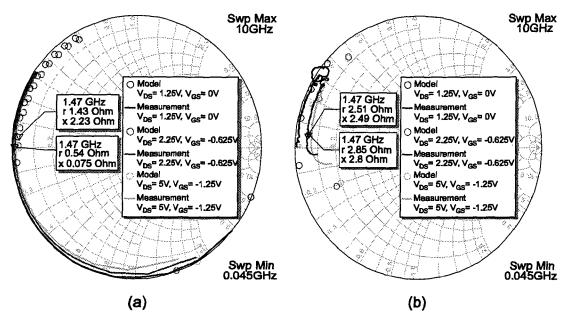

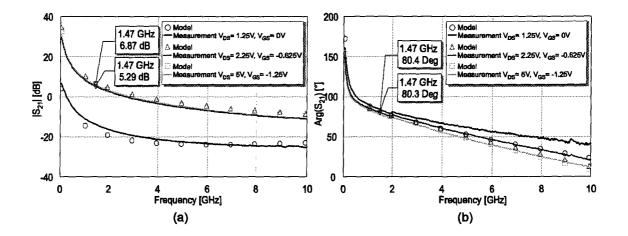

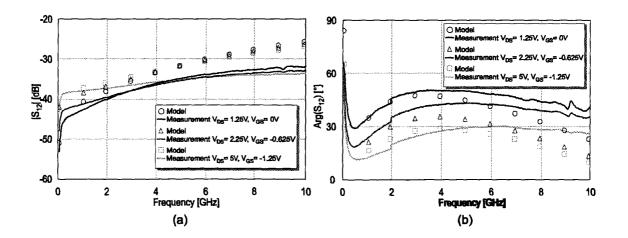

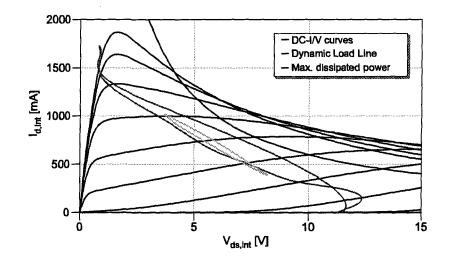

Für den Entwurf und die Optimierung von harmonisch gesteuerten Verstärkern sind verlässliche Großsignal-Computermodelle notwendig. Da für die verwendeten Transistoren kein derartiges Modell in der verwendeten Simulationsumgebung vorhanden war, wurde ein Computermodell basierend auf Gleichspannungsmessungen und einer Vielzahl von Kleinsignal-S-Parametermessungen, die bei unterschiedlichen Arbeitspunkten durchgeführt wurden, generiert. Messungen zeigen nicht nur im klassischen Klasse A Bereich eine gute Übereinstimmung mit den Simulationsergebnissen, sondern auch in Bereichen, die für hocheffiziente Applikationen wesentlich sind.

Simulationsergebnisse zeigten dass mit einem bis zur zweiten Oberwelle multiharmonisch abgeschlossenem realem Transistor der theoretisch maximal mögliche Klasse F Wirkungsgrad von 81.65 % beinahe erreicht werden kann. Diese wird im Wesentlichen nur durch den Kniespannungsfaktor  $\varkappa = \frac{V_{DD} - V_K}{V_{DD}}$  reduziert. Die Annahme, dass Linearität und Wirkungsgrad bei Klasse F Terminierung gleichzeitig maximiert werden, konnte durch nichtlineare Simulationsergebnisse bestätigt werden. Es stellte sich dabei heraus dass der Abschluss der ersten Oberwelle dabei die wesentlichste Rolle für die Optimierung von Linearität und Wirkungsgrad spielt. Linearität und Wirkungsgrad wurden durch einen geeigneten Abschluss der ersten Oberwelle am Transistoreingang zur Kompensation der Nichtlinearitäten zweiter Ordnung der Gate-Source Kapazität verbessert.

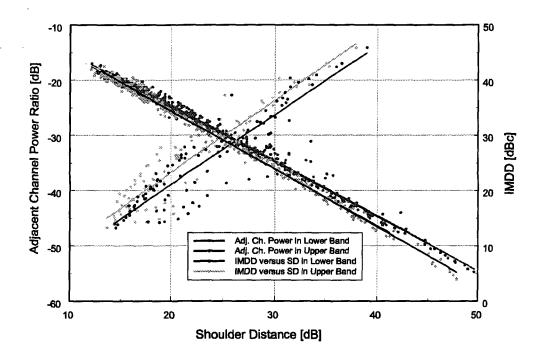

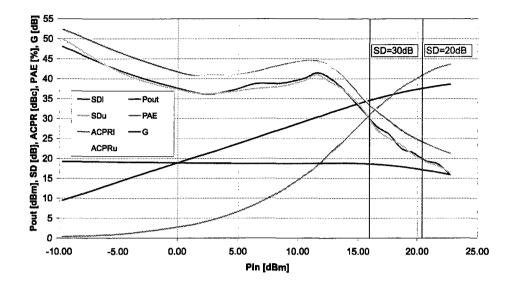

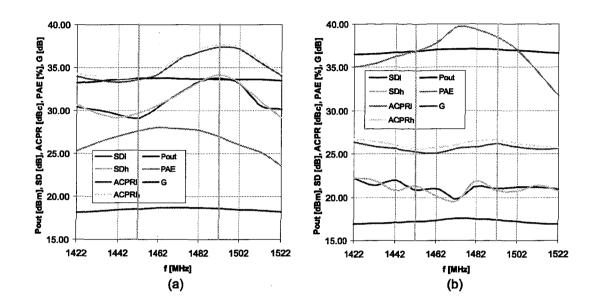

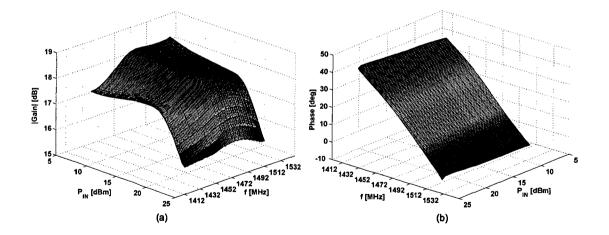

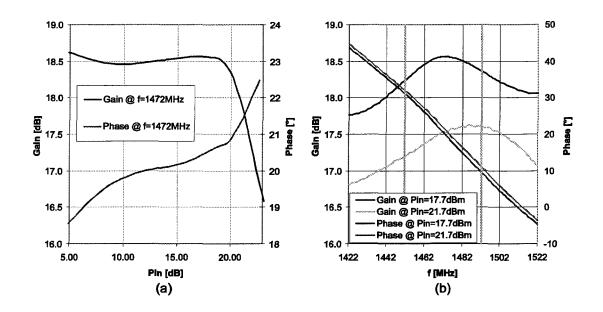

Das endgültige Verstärkermodul erfüllt die gestellten Anforderungen. Bei nominaler DAB Anspeisung liefert der Verstärker eine Ausgangsleistung von 37.3 dBm bei der geforderten Schulterdistanz von 20 dB mit einem Gesamtwirkungsgrad von 41 %. Bei reduzierter Eingangsleistung (back-off Betrieb) liefert das Modul eine Ausgangsleistung von 34.5 dBm bei der geforderten Schulterdistanz von 30 dB wobei ein Gesamtwirkungsgrad von 31 % erreicht wird. Im Vergleich zu kürzlich publizierten hocheffizienten und hochlinearen Leistungsverstärkern erreicht das Verstärkermodul durchschnittliche Wirkungsgradresultate, die hauptsächlich auf einen suboptimalen Entwurf des Ausgangskombinationsnetzwerks zurückzuführen sind. In Bezug auf Linearität aber bietet der neu entworfene Verstärker exzellente Ergebnisse.

## Abstract

Digital Audio Broadcasting, DAB, is the most fundamental advance in radio technology since the introduction of FM stereo radio. It gives listeners interference-free reception of high-quality sound, easy-to-use radios, and the potential for wider listening choice through many additional stations and services.

Full coverage of an area, in particular in big towns can only be achieved by retransmitting the DAB-signals into regions which are otherwise in the shadows of big buildings or similar obstacles. For this purpose fill-in or gap-filler transmitters are needed. The output power needed for such transmitters is usually in the range of several Watts.

The DAB system has to handle high dynamic range signals that can only be attained by the design of a low intermodulation distortion (IMD) amplifier. For stand-alone operation the efficiency of gap-filler transmitters have to be maximized to allow for solar powering. Furthermore, size has to be minimized for versatile use. Thin film technology is one miniaturization route which is for a medium number of units more cost effective than MMIC technology. Low-loss alumina substrate allows the design of passives with high quality factors and high manufacturing accuracy. Furthermore, the realization of components with a continuous spectrum of values is possible.

In this doctoral thesis a solid state power amplifier (SSPA) module fulfilling DAB requirements in thin film technology was developed showing conceptional feasibility for achieving simultaneously good linearity and good DC-power conversion rate.

The improvement of power added efficiency of microwave solid state power amplifiers has been investigated by many researcher in the last 20 years. With the introduction of complex digital modulation schemes with a non constant envelope (e.g. OFDM, CDMA, ...) interest in high linearity power amplifier design increased in the last 5-10 years. The sources for nonlinearities were investigated and effective linearisation techniques have been invented by several researchers. Improving linearity of the amplifier circuit was mostly done by an improvement in device technology and careful bias selection but rarely by an optimization of the amplifier circuit itself.

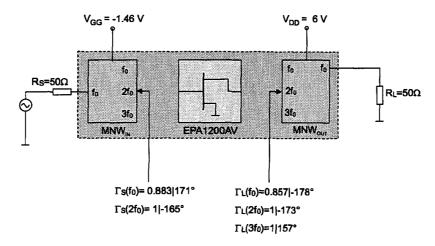

Class F mode of operation is well known for high efficiency. But investigations on linearity of class F termination have been reported rarely and the optimum termination angles of the harmonic loads in terms of linearity were not reported at all. In this thesis class F operation mode was investigated in terms of linearity and efficiency optimization based on nonlinear simulations. To improve linearity further, harmonic termination at the input was investigated on its capability to improve linearity and efficiency. To reach the required output power a balanced amplifier configuration was chosen since it offers many advantages, such as minimized input VSWR and increased stability. For easy characterization and flexibility the amplifier was designed in a modular way. As no experience with thin film technology was available at the institute the thin film process of the selected foundry was evaluated to ensure the validity of the used component models. For multiharmonic amplifier termination passive components with high quality factor are needed. Since no accurate model for spiral thin fim inductors was available in the simulation software used, a new spiral inductor model was developed being capable of predicting all parasitic elements and being scalable in a wide range of inductance values. This model is a fundamental tool in the design of harmonic terminations since it eliminates an iterative spiral inductor design process. All selected lumped components were characterized and scaleable models were made for those also. To ensure high reliability the bonding technique of the active devices was investigated and optimized.

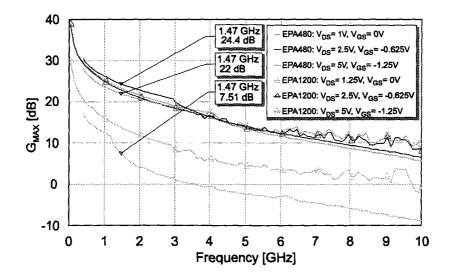

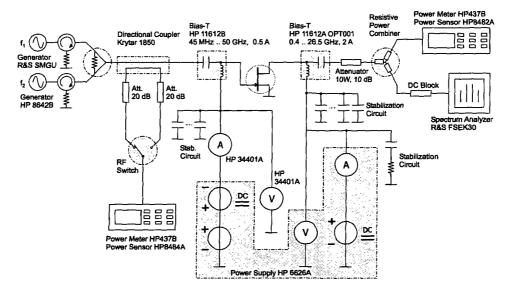

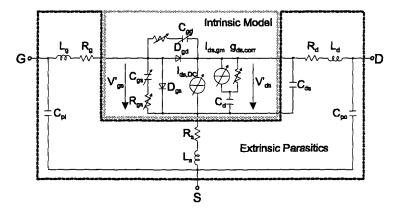

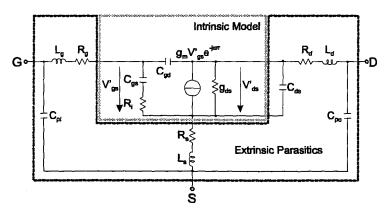

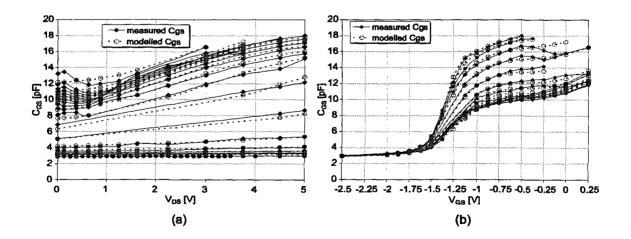

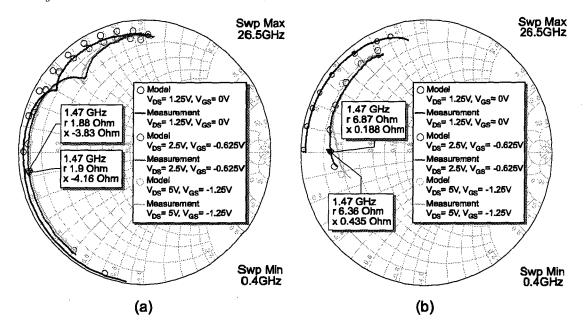

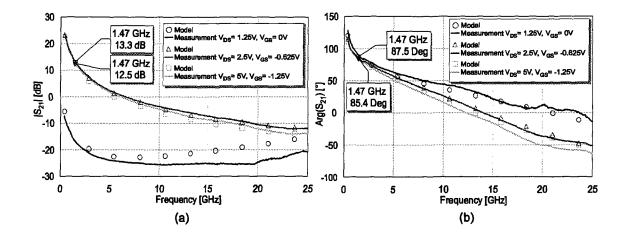

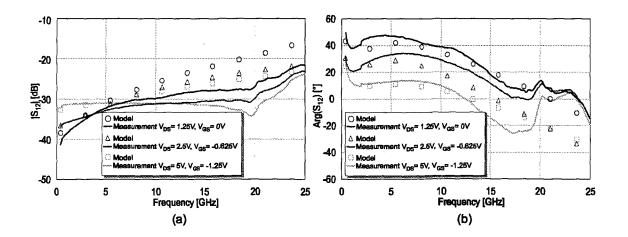

To design and optimize a harmonic controlled amplifier, reliable large-signal transistor models are necessary. As no such models were available in the used harmonic balance simulation software, computer models were generated from transistor DC and multiple bias small-signal scattering parameter measurements. The generated models agree well with measurements even at those regions which are crucial for high efficiency applications.

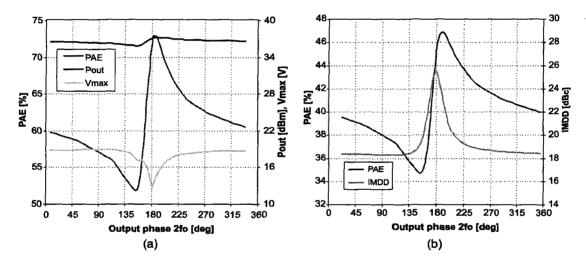

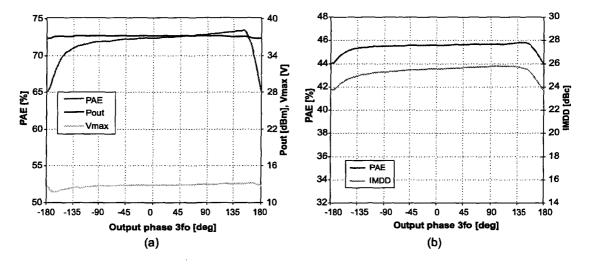

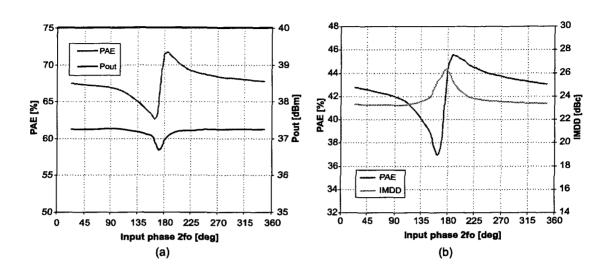

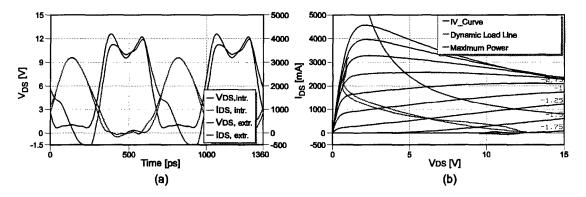

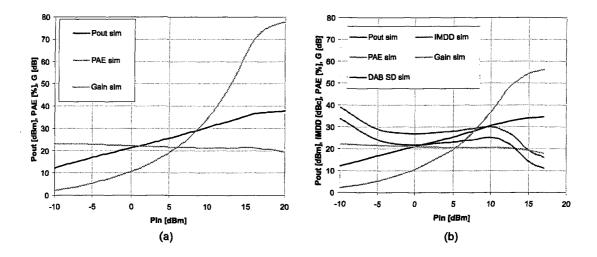

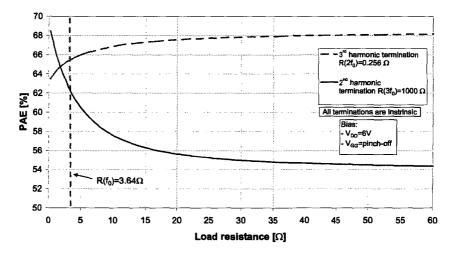

Simulation results of the 3<sup>rd</sup> order multiharmonic terminated transistor showed that with a non-ideal device the theoretical maximum of class F efficiency of 81.65 % is closely achievable only reduced by the knee voltage factor  $\varkappa = \frac{V_{DD} - V_K}{V_{DD}}$ . The assumption that linearity and efficiency are maximized simultaneously with class F termination was proven by non-linear circuit simulations. Termination of the 2<sup>nd</sup> harmonic at the output was found to be crucial for linearity and efficiency optimization. Linearity and efficiency were further improved by a 2<sup>nd</sup> harmonic termination concept at the device input to compensate for the 2<sup>nd</sup> order nonlinearities of the gate-source capacitance.

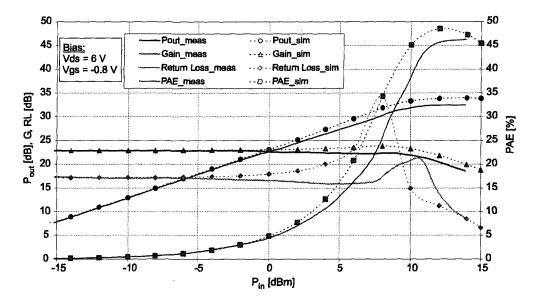

The final amplifier module fulfils the requirements for DAB operation. It delivers at nominal DAB drive an output power of 37.3 dBm with the requested shoulder distance of 20 dB and operating at a power added efficiency of 41 %. At reduced input power level (back-off condition) the module delivers at DAB excitation an output power of 34.5 dBm with the requested shoulder distance of 30 dB and providing a power added efficiency of 31 %. Compared to recent high efficiency and high linearity power amplifiers the developed amplifier module shows average results with respect to efficiency mainly due to suboptimal output combiner design. With respect to linearity, however, the newly developed power amplifier achieves excellent results.

## Acknowledgment

Many people supported me during the completion of this thesis with criticism, helpful assistance and references. This thesis would have never been possible without them.

First of all I would like to express my sincere gratitude to Gottfried Magerl for his patient guidance, encouragement and brilliant advice throughout this work. He was an excellent supervisor whose assistance and motivation were greatly appreciated.

Dieter Smely deserves special thanks for the work he did on device model development and on fitting the model parameters to my measurement results.

Further I would like to thank Holger Arthaber, Wolfgang Konrad, Gernot Hanreich, and Bernhard Ingruber for many fruitful discussions and their willingness and enthusiasm to share their thoughts and ideas.

The work presented was done within a research project which was performed in cooperation with Harris Communications, Rankweil, Austria and was supported by the European Space Agency, Noordwijk, The Netherlands, under the project No. 10779/94/NL/JV (CCN No.3). I would like to thank Felix A. Petz from the European Space Agency and Martin Pfurtscheller from Harris Communications for the good cooperation and their technical support.

# Contents

| 1 | Mo  | Motivation |                                                             |    |

|---|-----|------------|-------------------------------------------------------------|----|

| 2 | Dig | ital Au    | idio Broadcast                                              | 3  |

|   | 2.1 |            | DAB System Description                                      | 4  |

|   | 2.2 |            | s of the DAB System                                         | 5  |

| 3 | Am  | plifier    | Theory                                                      | 13 |

|   | 3.1 | Efficier   | ncy                                                         | 13 |

|   |     | 3.1.1      | Drain or Collector Efficiency                               | 13 |

|   |     | 3.1.2      | Power Added Efficiency                                      | 13 |

|   | 3.2 | Ampli      | tude Distortion                                             | 14 |

|   |     | 3.2.1      | Single-Tone Effects of 3 <sup>rd</sup> Order Nonlinearities | 15 |

|   |     | 3.2.2      | Two-Tone Effects of 3 <sup>rd</sup> Order Nonlinearities    | 15 |

|   |     | 3.2.3      | Higher Order Nonlinearities                                 | 16 |

|   |     | 3.2.4      | Large-Signal IMD Sweet Spots                                | 17 |

|   |     | 3.2.5      | Complex Distortion Measures                                 | 19 |

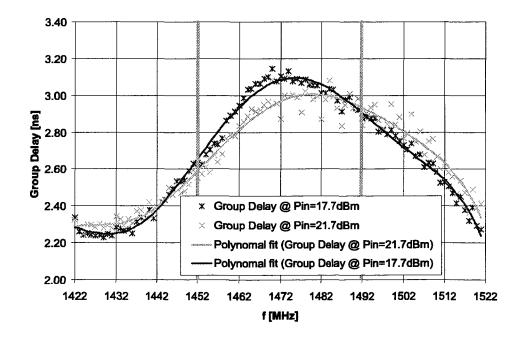

|   | 3.3 | Phase      | Distortion                                                  | 22 |

|   | 3.4 | Efficier   | nt Amplifier Concepts                                       | 26 |

|   |     | 3.4.1      | Class A, AB, B, C                                           | 26 |

|   |     | 3.4.2      | Harmonic Controlled Amplifiers – HCA                        | 31 |

|   |     | 3.4.3      | Doherty Amplifier                                           | 43 |

|   | 3.5 | Lineari    | ity Aspects                                                 | 45 |

|   |     | 3.5.1      | Feedback Techniques                                         | 45 |

|   |     | 3.5.2      | Injection/Termination Techniques                            | 46 |

|   | 3.6 | Power      | Combining Techniques                                        | 47 |

|   |     | 3.6.1      | Wilkinson Power Combiner                                    | 48 |

|   |     | 3.6.2      | Balanced Configuration                                      | 49 |

|   |     | 3.6.3      | Push-Pull Configuration                                     | 51 |

|   | 3.7 | Active     | Device Aspects                                              | 52 |

|   | 3.8 | Conclu     |                                                             | 55 |

|   | 0.0 | 3.8.1      | DAB Amplifier Realization Concept                           | 57 |

| 4 | Cha | racteri    | ization and Modeling                                        | 59 |

|   | 4.1 | Techno     | blogy                                                       | 59 |

|   |     | 4.1.1      | Evaluation of Thin Film Process                             | 59 |

|   |     | 4.1.2 Packaging                                  | 63  |

|---|-----|--------------------------------------------------|-----|

|   | 4.2 | TRL Calibration Technique                        |     |

|   | 4.3 | Passive Devices                                  |     |

|   | 1.0 | 4.3.1 Lumped Components                          |     |

|   |     | 4.3.2 Thin Film Components                       |     |

|   | 4.4 | Active Devices                                   |     |

|   |     | 4.4.1 Characterization Setup                     |     |

|   |     | 4.4.2 DC Characterization                        |     |

|   |     | 4.4.3 Small Signal RF Characterization           |     |

|   |     | 4.4.4 Two-Tone Characterization                  |     |

|   |     | 4.4.5 Modeling                                   |     |

|   |     | 4.4.6 Model Verification                         | 106 |

|   | 4.5 | Conclusion                                       | 115 |

| 5 | Pow | ver Amplifier Realization                        | 116 |

| J | 5.1 | Basic Considerations                             |     |

|   | 0.1 | 5.1.1 Linearity Aspects                          |     |

|   | 5.2 | Single Stage Class-F Amplifier                   |     |

|   | 0.2 | 5.2.1 Simulation Setup                           |     |

|   |     | 5.2.2 Class-F Termination                        |     |

|   |     | 5.2.3 2 <sup>nd</sup> Harmonic Input Termination |     |

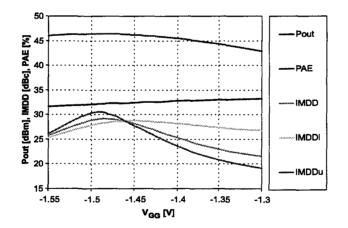

|   |     | 5.2.4 Bias Selection                             |     |

|   |     | 5.2.5 Simulation Results                         |     |

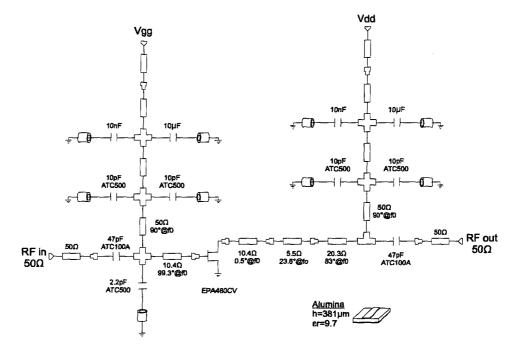

|   |     | 5.2.6 Implementation                             | 125 |

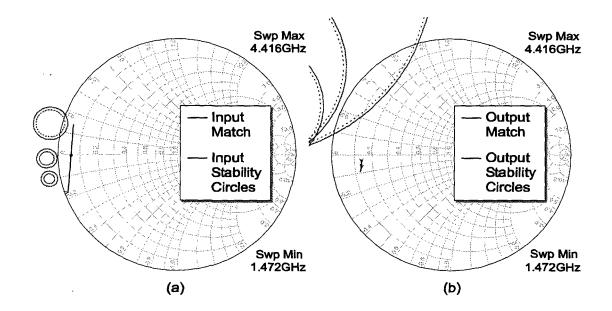

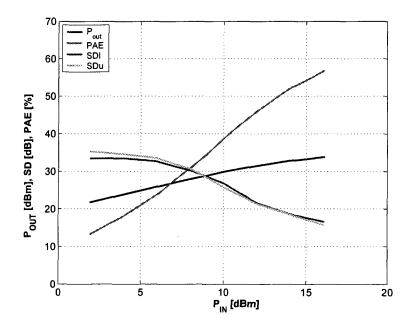

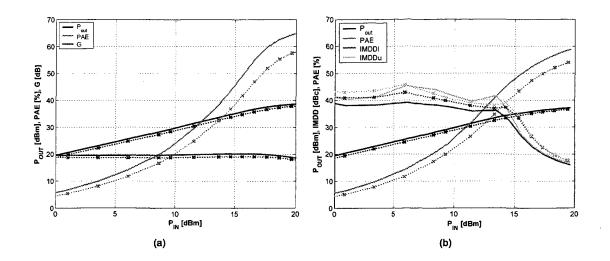

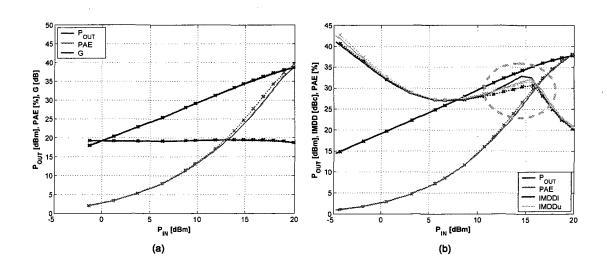

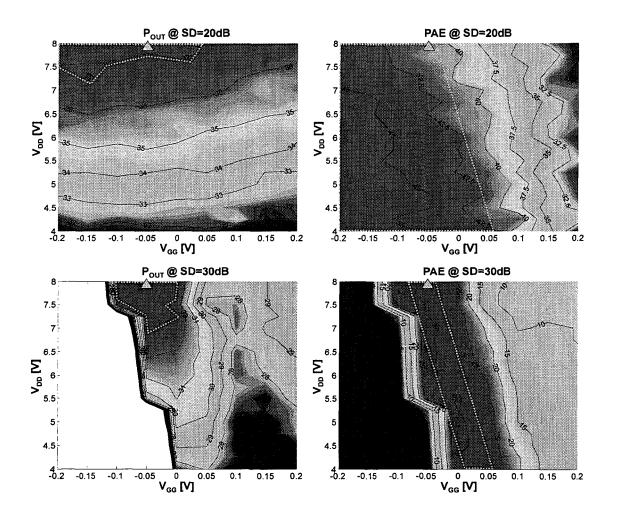

|   |     | 5.2.7 Measurement Results                        | 128 |

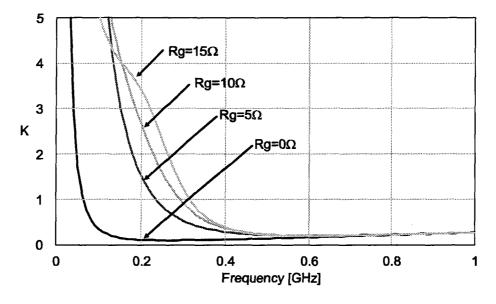

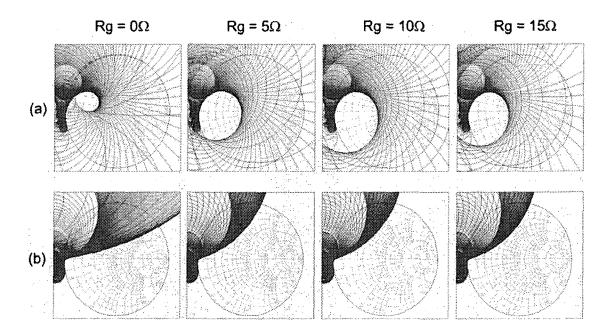

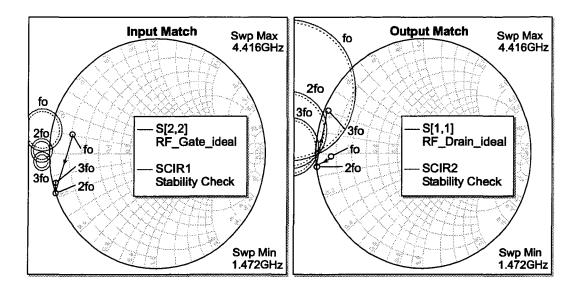

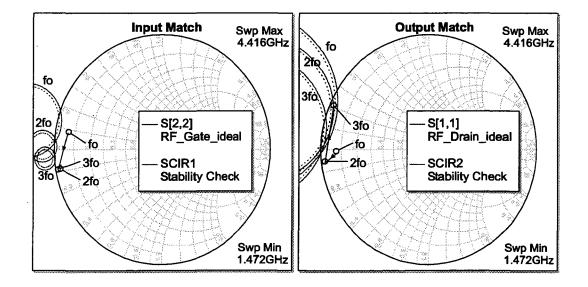

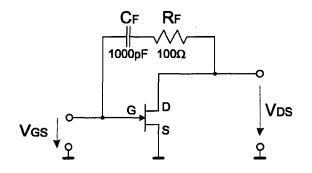

|   | 5.3 | Stability Issues                                 | 130 |

|   | 5.4 | Bias Networks                                    | 133 |

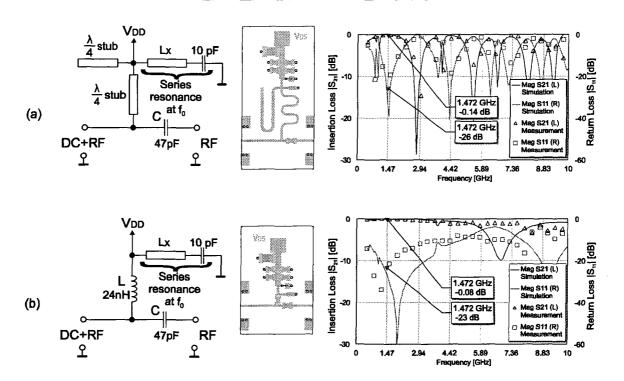

|   |     | 5.4.1 Drain Bias                                 | 133 |

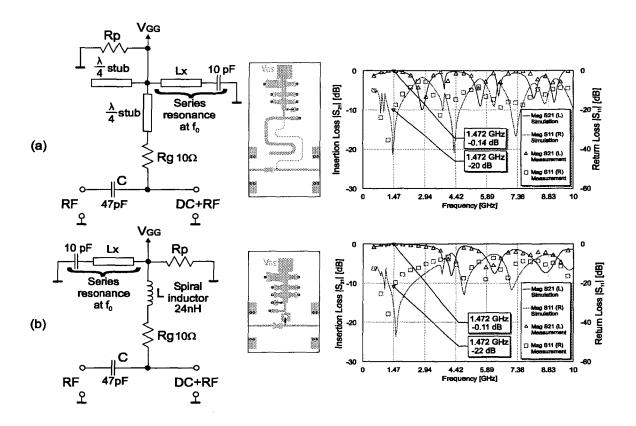

|   |     | 5.4.2 Gate Bias                                  | 134 |

|   | 5.5 | Quadrature Couplers                              | 135 |

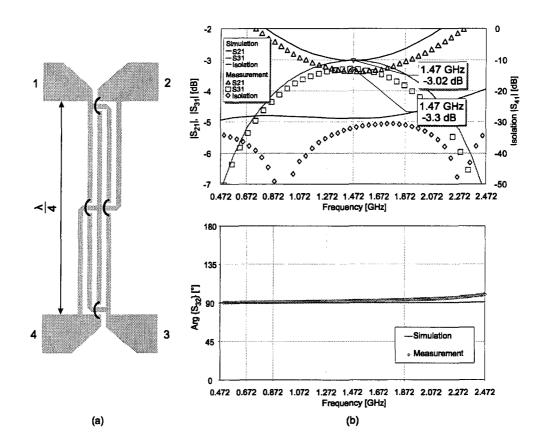

|   |     | 5.5.1 Lange Coupler                              |     |

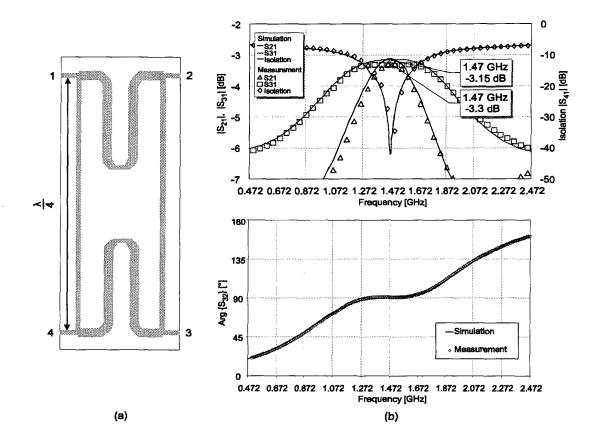

|   |     | 5.5.2 Branchline Coupler                         | 136 |

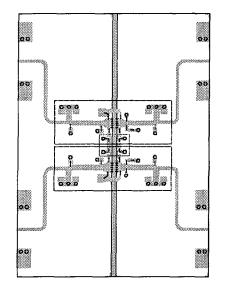

|   | 5.6 | Balanced Amplifier                               |     |

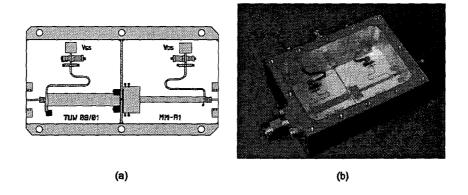

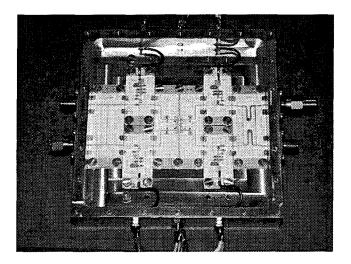

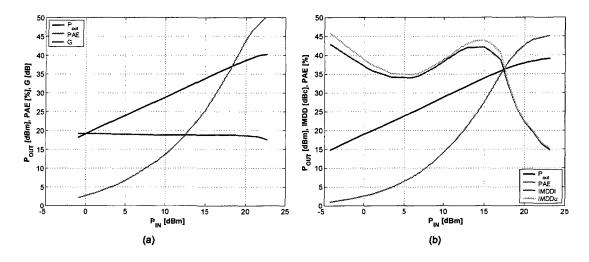

|   | 5.7 | Measurement Results                              | 143 |

| 6 | Con | nclusion                                         | 147 |

|   | 6.1 | Table of Compliance                              | 147 |

|   | 6.2 | Summary                                          |     |

|   | 6.3 | Outlook                                          |     |

|   | Bib | liography                                        | 152 |

|   |     |                                                  |     |

|   | Cur | riculum Vitae                                    | 160 |

|   |     |                                                  |     |

ii

# List of Figures

| 1.1  | Providing full radio coverage using a fill-in transmitter.                          | 1  |

|------|-------------------------------------------------------------------------------------|----|

| 2.1  | Multipath propagation.                                                              | 3  |

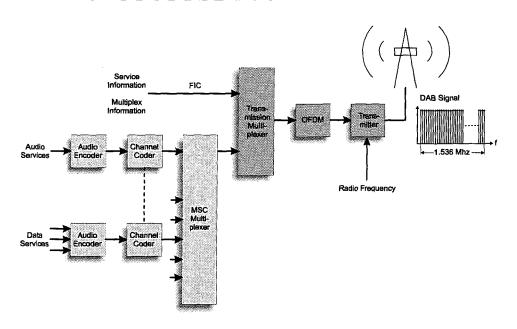

| 2.2  | Concept of DAB signal generation.                                                   | 5  |

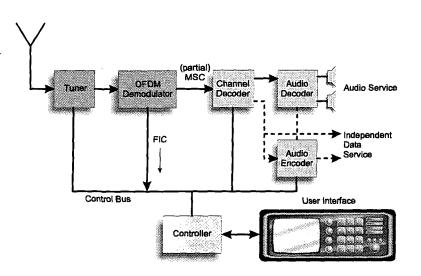

| 2.3  | Concept of DAB reception.                                                           | 6  |

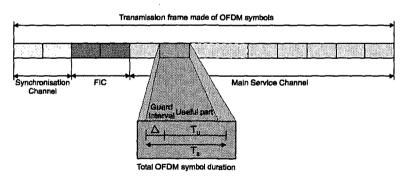

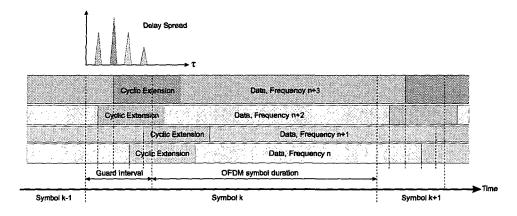

| 2.4  | Total OFDM symbol duration.                                                         | 8  |

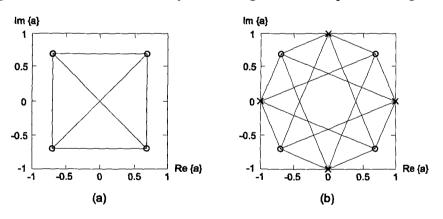

| 2.5  | Signal constellation of a DAB symbol.                                               | 9  |

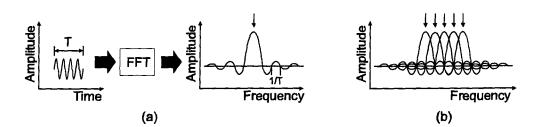

| 2.6  | FFT of modulated sub-carriers.                                                      | 10 |

| 2.7  | Orthogonal Frequency Division Multiplexing (OFDM)                                   | 10 |

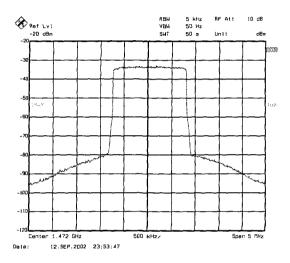

| 2.8  | Transmitter signal output spectrum (L-band)                                         | 11 |

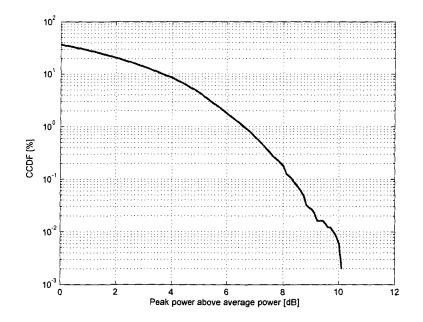

| 2.9  | CCDF of a DAB signal.                                                               | 12 |

|      |                                                                                     |    |

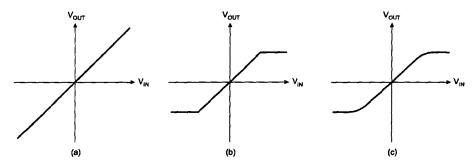

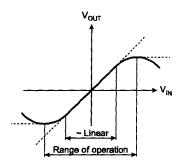

| 3.1  | Linear and nonlinear amplification                                                  | 14 |

| 3.2  | Transfer characteristic $3^{rd}$ order approximation                                | 15 |

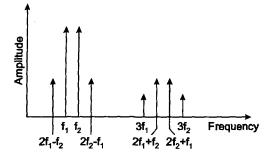

| 3.3  | Two-tone response of a 3 <sup>rd</sup> order nonlinear amplifier                    | 16 |

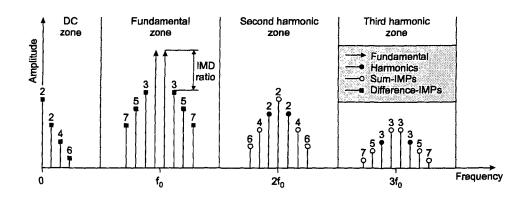

| 3.4  | Two-tone response of $7^{\text{th}}$ order nonlinear amplifier                      | 17 |

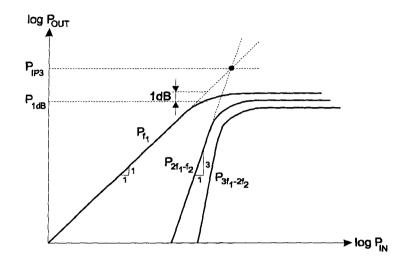

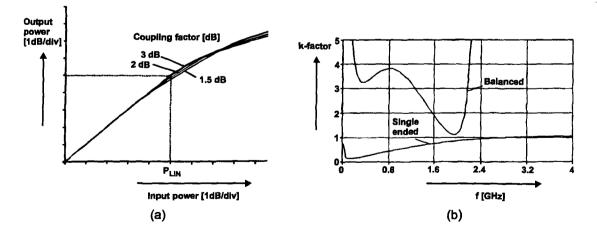

| 3.5  | 1dB compression point $P_{1dB}$ and 3 <sup>rd</sup> order intercept point $P_{IP3}$ | 18 |

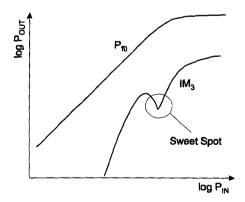

| 3.6  | Typical Class B two-tone performance showing a sweet spot in $IM_3$                 | 18 |

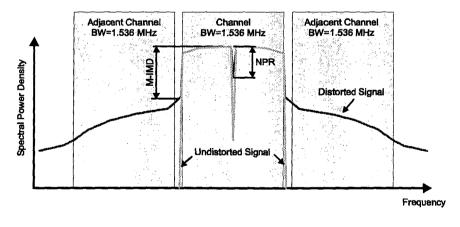

| 3.7  | Definition of ACPR, NPR, and M-IMD.                                                 | 19 |

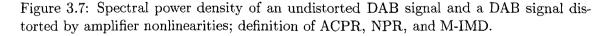

| 3.8  | Normalized relationship between the various nonlinearity measures for mul-          |    |

|      | titone signals.                                                                     | 21 |

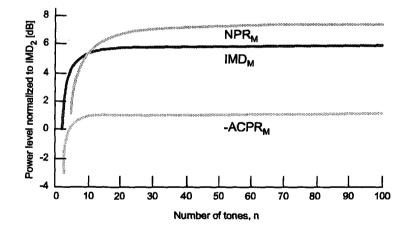

| 3.9  | Distortion of a GaAs power amplifier.                                               | 25 |

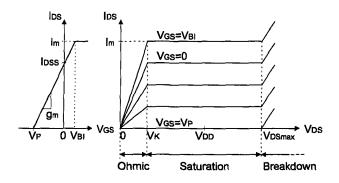

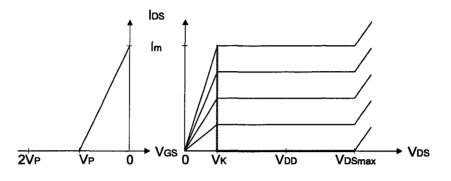

|      | Input and output characteristics of an idealized FET.                               | 27 |

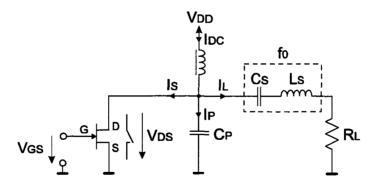

|      | Circuit diagram of a tuned loaded FET                                               | 27 |

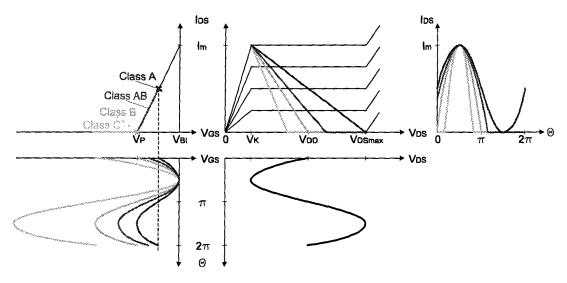

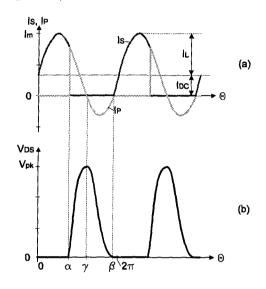

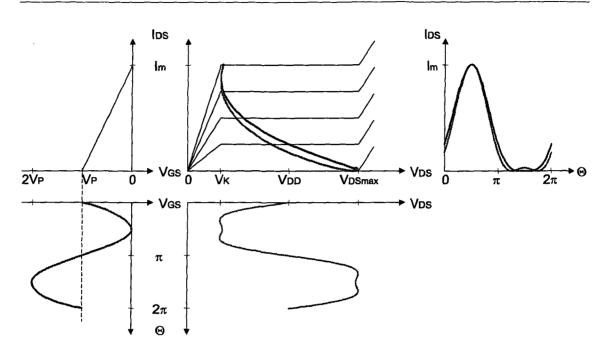

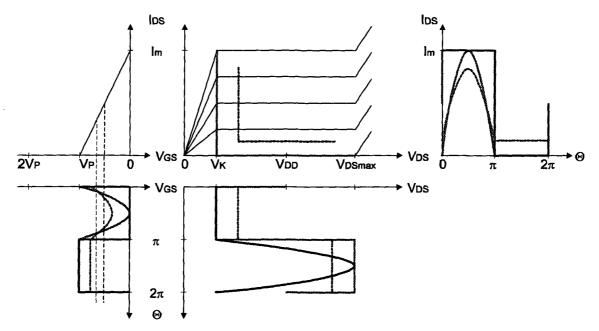

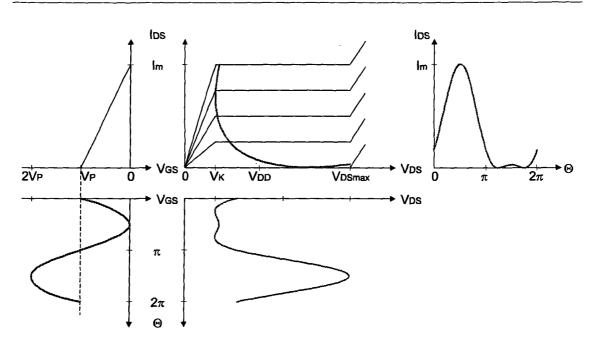

|      | Class A, AB, B, and C operation.                                                    | 28 |

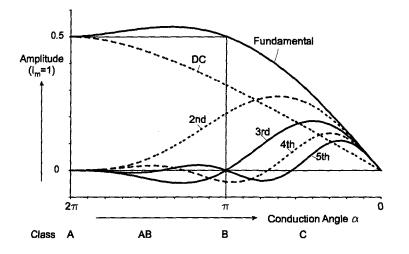

|      | Fourier analysis of reduced conduction angle mode                                   | 29 |

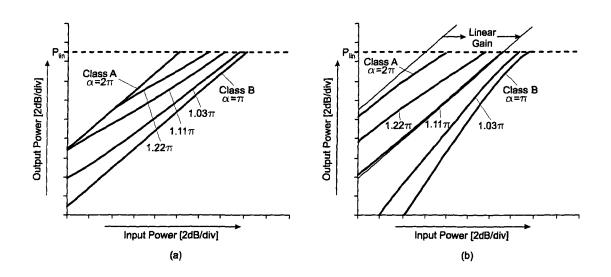

|      | Input-output power characteristics for class A to class B                           | 30 |

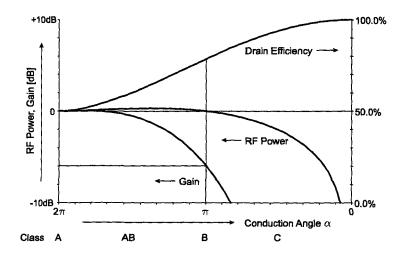

|      | RF power, gain, and drain efficiency versus conduction angle                        | 30 |

|      | Dynamic load line for maximum efficiency.                                           | 32 |

|      | Circuit diagram of a class E amplifier.                                             | 32 |

|      | Class E RF waveforms                                                                | 33 |

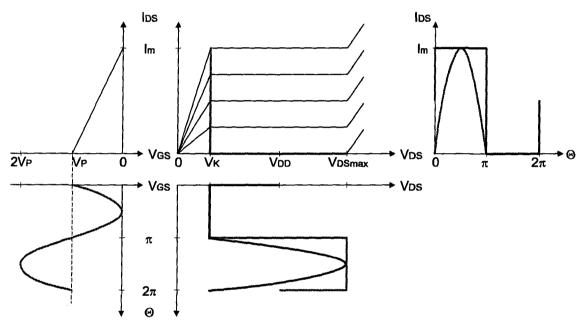

| 3.19 | Optimum dynamic load line and voltage and current waveforms for class ${\bf F}$     |    |

|      | operation                                                                           | 35 |

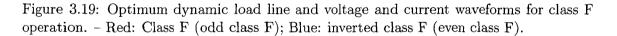

| 3.20 | Ideal circuit for class F operation                                                 | 36 |

iii

. •

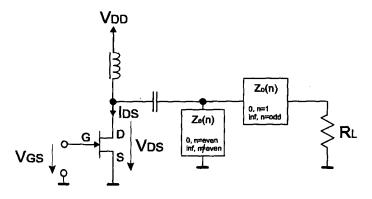

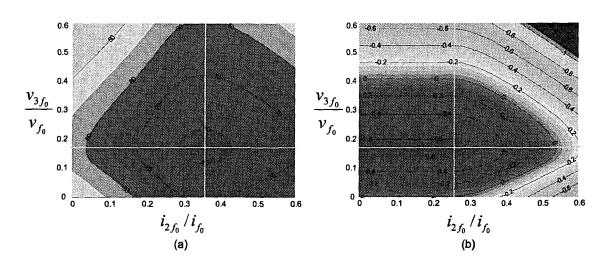

| 3.21                                                                                                                                                               | Dependency of efficiency and output power on normalized 3 <sup>rd</sup> harmonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 3.22                                                                                                                                                               | voltage and normalized 2 <sup>nd</sup> harmonic current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                                                               |

|                                                                                                                                                                    | imum efficiency and maximum output power, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                               |

| 3.23                                                                                                                                                               | Optimum DLL and voltage and current waveforms for half sinusoidally and rectangularly driven HCA, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40                                                                                                               |

| 3.24                                                                                                                                                               | Optimum dynamic load line and voltage and current waveforms for class G operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                               |

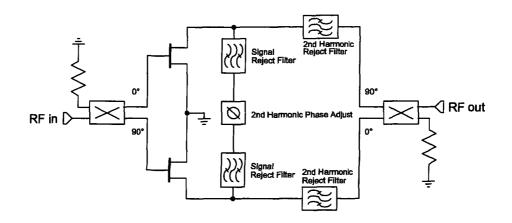

| 3.25                                                                                                                                                               | Fundamental conceptional structure of the harmonic reaction amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                                                                               |

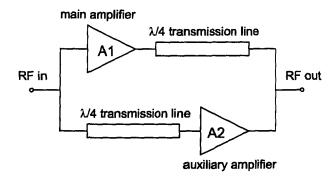

|                                                                                                                                                                    | Basic structure of a Doherty amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                                               |

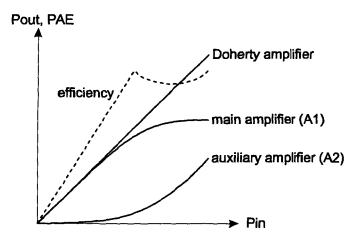

|                                                                                                                                                                    | Doherty amplifier – transfer function and power added efficiency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                                                                               |

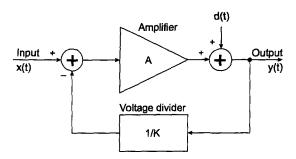

|                                                                                                                                                                    | Feedback applied around an amplifier with distortion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                                                                                                               |

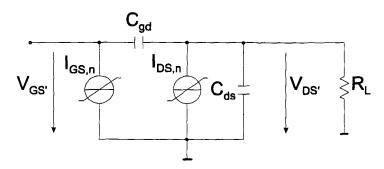

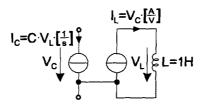

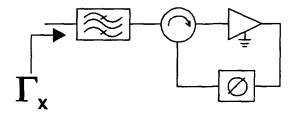

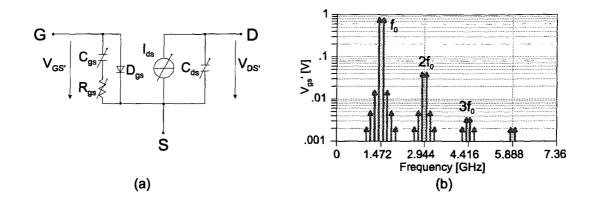

|                                                                                                                                                                    | Equivalent circuit for nonlinear analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46                                                                                                               |

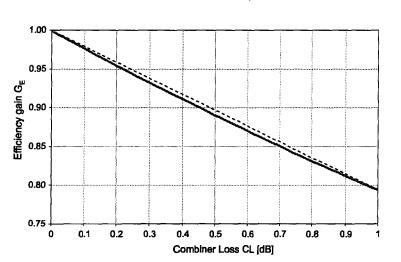

|                                                                                                                                                                    | Reduction of efficiency gain $G_E$ influenced by combiner loss CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48                                                                                                               |

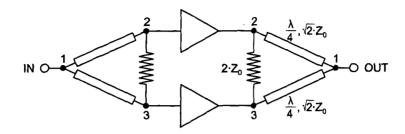

|                                                                                                                                                                    | In-phase power combiner using single-section Wilkinson power combiners.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                                                               |

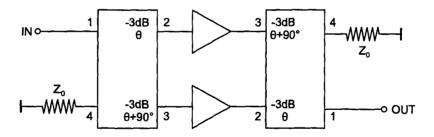

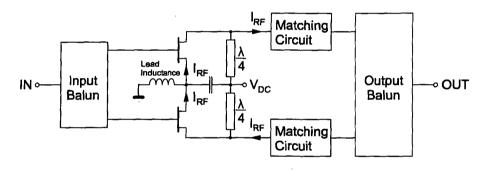

|                                                                                                                                                                    | Configuration of balanced amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                               |

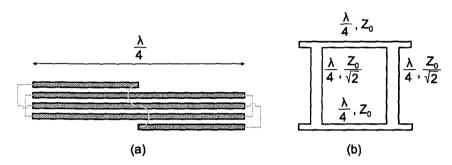

|                                                                                                                                                                    | Quadrature 3 dB couplers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                               |

|                                                                                                                                                                    | Balanced power amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                               |

| 3.35                                                                                                                                                               | RF push-pull amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                                                               |

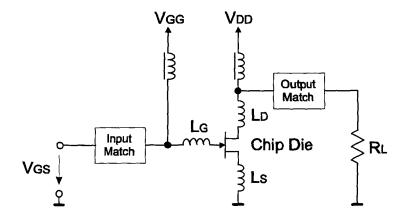

| 3.36                                                                                                                                                               | Amplifier schematic illustrating parasitic extrinsic inductances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                                                               |

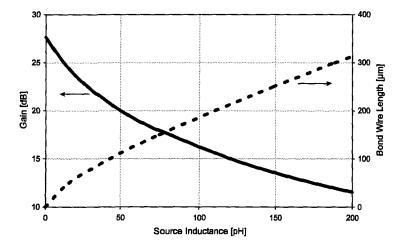

| 3.37                                                                                                                                                               | Influence of source inductance on amplifier gain and associated bond wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                  |

|                                                                                                                                                                    | length.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                                               |

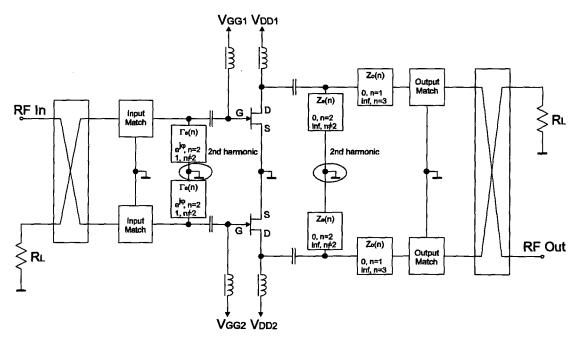

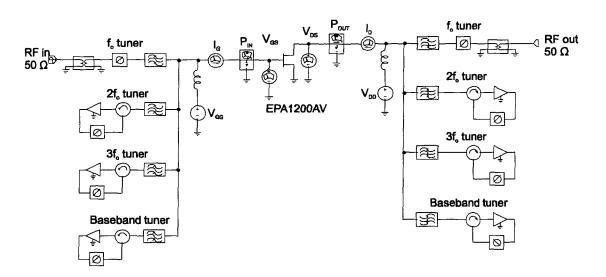

| 3.38                                                                                                                                                               | Balanced concept for complete DAB amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                                                               |

|                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                  |

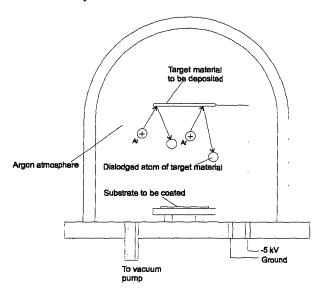

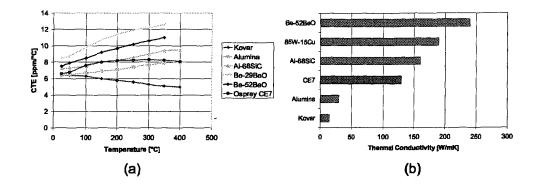

| 4.1                                                                                                                                                                | DC sputtering chamber.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60                                                                                                               |

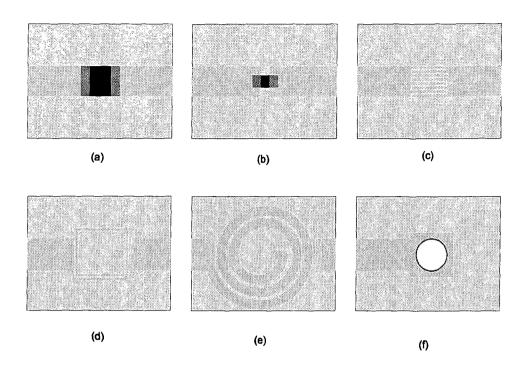

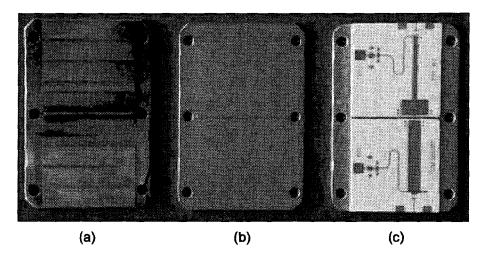

| 4.2                                                                                                                                                                | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                                                               |

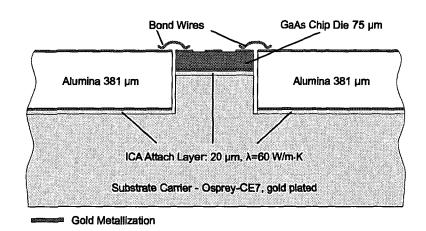

| $\begin{array}{c} 4.2 \\ 4.3 \end{array}$                                                                                                                          | Test structures       Packaging cross section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c} 64 \\ 65 \end{array}$                                                                          |

| $4.2 \\ 4.3 \\ 4.4$                                                                                                                                                | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>65                                                                                                   |

| $4.2 \\ 4.3 \\ 4.4 \\ 4.5$                                                                                                                                         | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 64 \\ 65 \end{array}$                                                                          |

| $4.2 \\ 4.3 \\ 4.4$                                                                                                                                                | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>65<br>66                                                                                             |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$                                                                                                     | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>65                                                                                                   |

| $4.2 \\ 4.3 \\ 4.4 \\ 4.5$                                                                                                                                         | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>67                                                                                             |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$                                                                                                     | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>65<br>66                                                                                             |

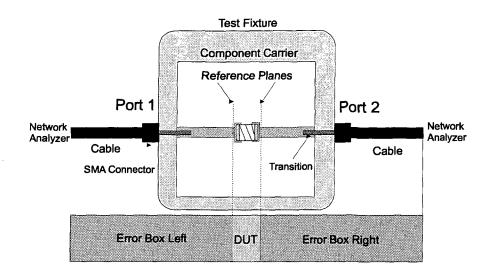

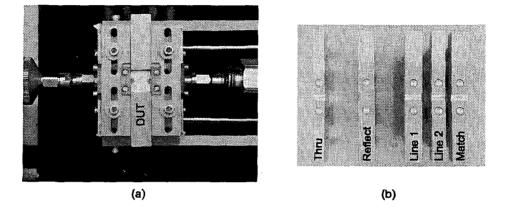

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                                                                           | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>67<br>68                                                                                       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>                                                 | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>67<br>68<br>69<br>69                                                                           |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                                                                                       | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>67<br>68<br>69<br>69<br>70                                                                     |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                                                               | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>67<br>68<br>69<br>69                                                                           |

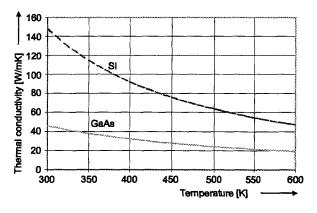

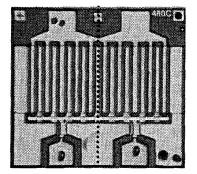

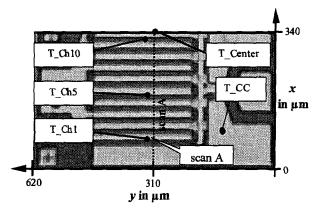

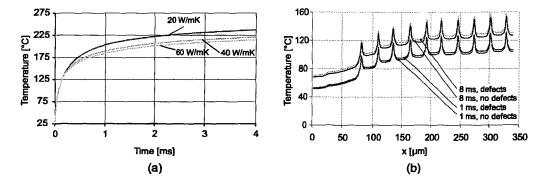

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ \\ 4.7 \\ \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \end{array}$                                                  | Test structures       Packaging cross section.         Packaging cross section.       Temperature dependent thermal conductivity of Si and GaAs.         Microscopic view of the top side of the investigated GaAs power FET.       Significant points and line scans used for illustrating the thermal behavior of the transistor.         Simulation results of the influence of ICA thermal conductivity and bonding defects.       Metal alloys – thermal parameters.         Substrate assembly procedure.       Measurement setup with test fixture and network analyzer.         ICM test fixture.       ConneXion Rosenberger test fixture.                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>65<br>66<br>67<br>68<br>69<br>69<br>70<br>71<br>72                                                   |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \end{array}$                                                | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>65<br>66<br>67<br>68<br>69<br>69<br>70<br>71                                                         |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \end{array}$                                        | Test structures       Packaging cross section.         Packaging cross section.       Temperature dependent thermal conductivity of Si and GaAs.         Microscopic view of the top side of the investigated GaAs power FET.       Significant points and line scans used for illustrating the thermal behavior of the transistor.         Simulation results of the influence of ICA thermal conductivity and bonding defects.       Metal alloys – thermal parameters.         Substrate assembly procedure.       Measurement setup with test fixture and network analyzer.         ICM test fixture.       ConneXion Rosenberger test fixture.                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>66<br>67<br>68<br>69<br>69<br>70<br>71<br>72<br>72                                                   |

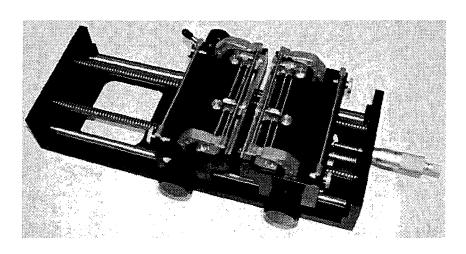

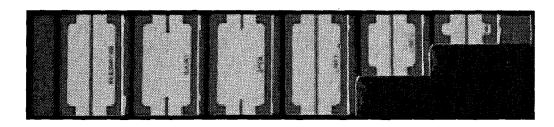

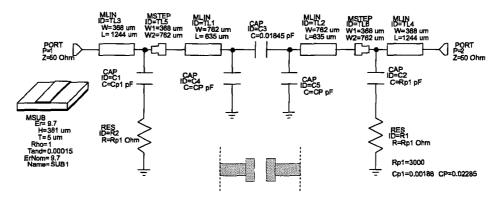

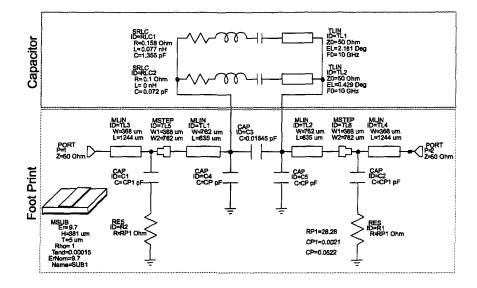

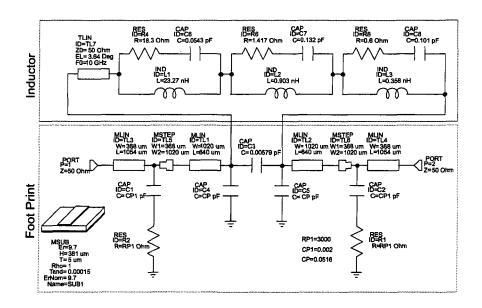

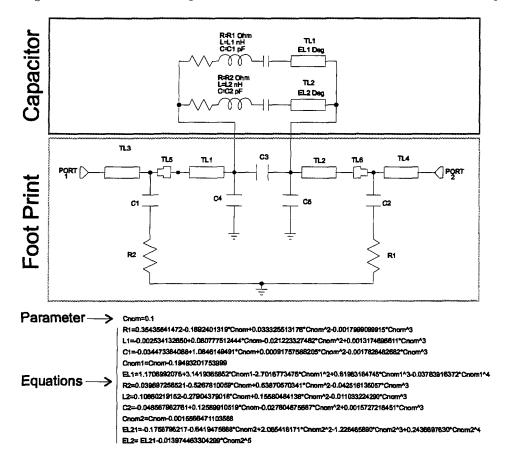

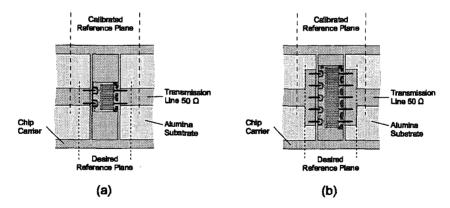

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ \end{array}$ $\begin{array}{c} 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \end{array}$ | Test structures       Packaging cross section.         Packaging cross section.       Temperature dependent thermal conductivity of Si and GaAs.         Microscopic view of the top side of the investigated GaAs power FET.       Significant points and line scans used for illustrating the thermal behavior of the transistor.         Simulation results of the influence of ICA thermal conductivity and bonding defects.       Metal alloys – thermal parameters.         Metal alloys – thermal parameters.       Metal analyzer.         Measurement setup with test fixture and network analyzer.       ConneXion Rosenberger test fixture.         Calibration kit for the ConneXion Rosenberger test fixture.       Equivalent circuit diagram for device foot print.                                                                                                                                                                                                   | 64<br>65<br>65<br>66<br>67<br>68<br>69<br>69<br>70<br>71<br>72<br>72<br>74                                       |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \end{array}$                        | Test structures       Packaging cross section.         Packaging cross section.       Temperature dependent thermal conductivity of Si and GaAs.         Microscopic view of the top side of the investigated GaAs power FET.       Significant points and line scans used for illustrating the thermal behavior of the transistor.         Simulation results of the influence of ICA thermal conductivity and bonding defects.       Metal alloys – thermal parameters.         Metal alloys – thermal parameters.       Metal analyzer.         Substrate assembly procedure.       Measurement setup with test fixture and network analyzer.         ConneXion Rosenberger test fixture.       Calibration kit for the ConneXion Rosenberger test fixture.         Equivalent circuit diagram for an ATC500 BMC capacitor, 1.3 pF.       Metal alloys - 1.3 pF.                                                                                                                  | 64<br>65<br>65<br>66<br>67<br>68<br>69<br>69<br>70<br>71<br>72<br>72<br>72<br>74<br>75                           |

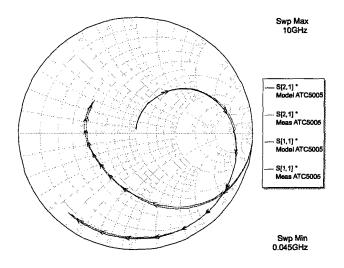

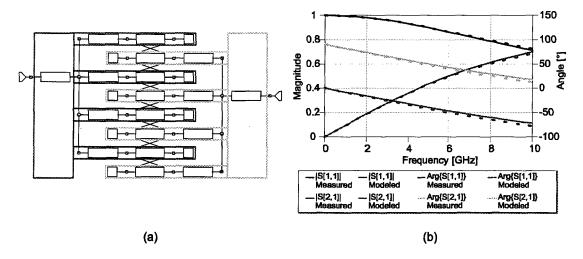

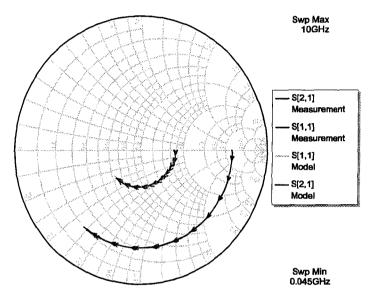

| $\begin{array}{r} 4.2\\ 4.3\\ 4.4\\ 4.5\\ 4.6\\ 4.7\\ 4.8\\ 4.9\\ 4.10\\ 4.11\\ 4.12\\ 4.13\\ 4.14\\ 4.15\\ 4.16\\ 4.17\end{array}$                                | Test structures       Packaging cross section.         Packaging cross section.       Temperature dependent thermal conductivity of Si and GaAs.         Microscopic view of the top side of the investigated GaAs power FET.       Significant points and line scans used for illustrating the thermal behavior of the transistor.         Simulation results of the influence of ICA thermal conductivity and bonding defects.       Metal alloys – thermal parameters.         Metal alloys – thermal parameters.       Substrate assembly procedure.         Measurement setup with test fixture and network analyzer.       ICM test fixture.         ConneXion Rosenberger test fixture.       Calibration kit for the ConneXion Rosenberger test fixture.         Equivalent circuit diagram for device foot print.       Equivalent circuit diagram for an ATC500 BMC capacitor, 1.3 pF.         Modeled vs. measured S-parameters of an ATC500 capacitor.       Subscience. | $\begin{array}{c} 64\\ 65\\ 65\\ 66\\ 67\\ 68\\ 69\\ 70\\ 71\\ 72\\ 72\\ 74\\ 75\\ 75\\ \end{array}$             |

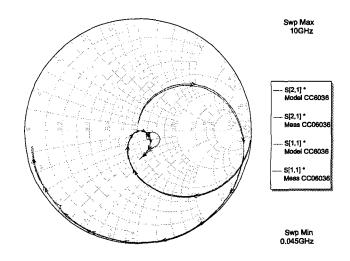

| $\begin{array}{r} 4.2\\ 4.3\\ 4.4\\ 4.5\\ 4.6\\ 4.7\\ 4.8\\ 4.9\\ 4.10\\ 4.11\\ 4.12\\ 4.13\\ 4.14\\ 4.15\\ 4.16\\ 4.17\\ 4.18\end{array}$                         | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 64\\ 65\\ 65\\ 66\\ 67\\ 68\\ 69\\ 70\\ 71\\ 72\\ 72\\ 74\\ 75\\ 76\\ \end{array}$             |

| $\begin{array}{c} 4.2\\ 4.3\\ 4.4\\ 4.5\\ 4.6\\ 4.7\\ 4.8\\ 4.9\\ 4.10\\ 4.11\\ 4.12\\ 4.13\\ 4.14\\ 4.15\\ 4.16\\ 4.17\\ 4.18\\ 4.19\\ \end{array}$               | Test structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 64\\ 65\\ 65\\ 66\\ 67\\ 68\\ 69\\ 70\\ 71\\ 72\\ 72\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\end{array}$ |

iv

| 4.21     | Comparison of modeled and measured 50 $\Omega$ resistor                                | 79  |

|----------|----------------------------------------------------------------------------------------|-----|

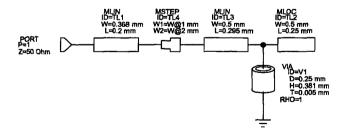

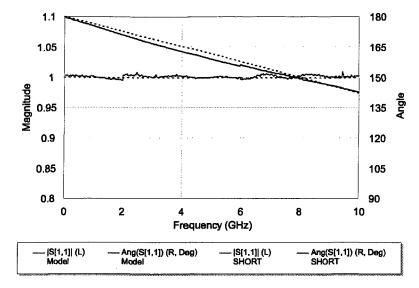

| 4.22     | Via model                                                                              | 79  |

| 4.23     | Comparison of modeled and measured via interconnect.                                   | 80  |

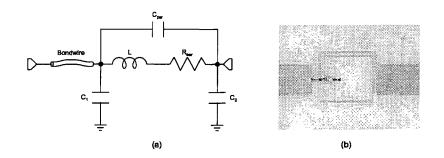

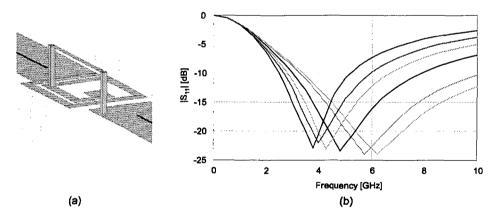

| 4.24     | Spiral inductor model and layout                                                       | 81  |

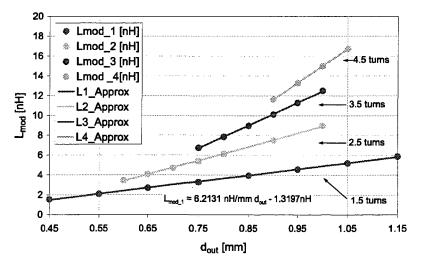

|          | Inductance $L_{mod}$ vs. the outer diameter $d_{out}$ for various number of turns.     | 81  |

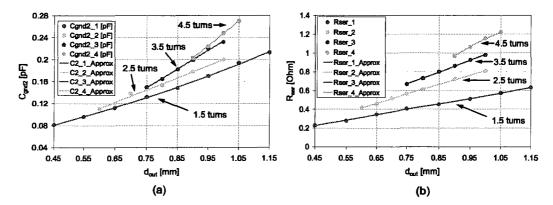

|          | Parasitics vs. outer diameter $d_{out}$ .                                              | 82  |

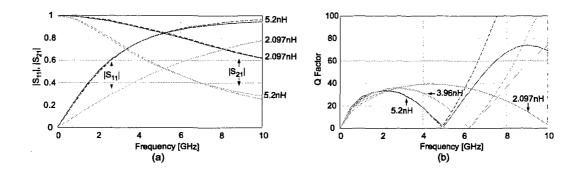

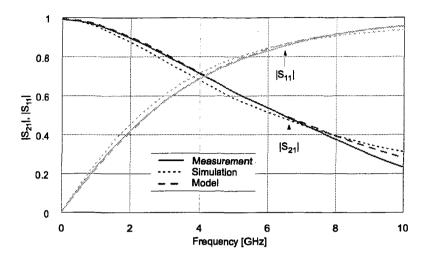

|          | Comparison of EM simulation and modeling results.                                      | 83  |

|          | Comparison of measured, simulated, and modeled scattering parameters                   | 84  |

|          | Tuning the inductor value.                                                             | 84  |

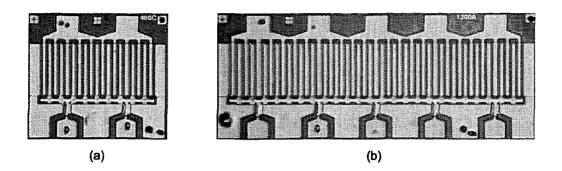

|          | Transistor layout                                                                      | 86  |

|          | PHEMTs mounted on chip carrier                                                         | 86  |

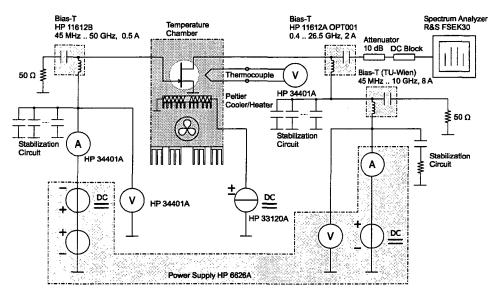

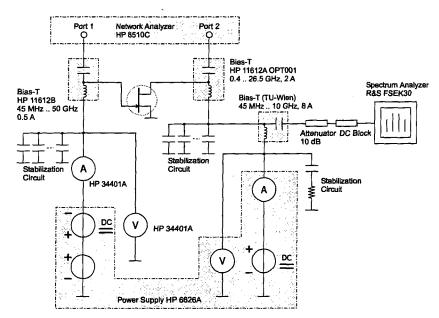

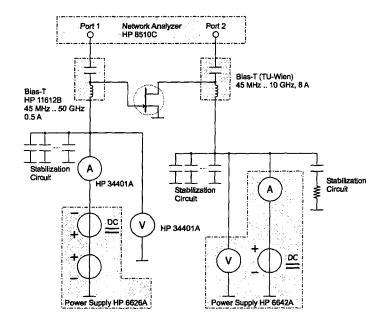

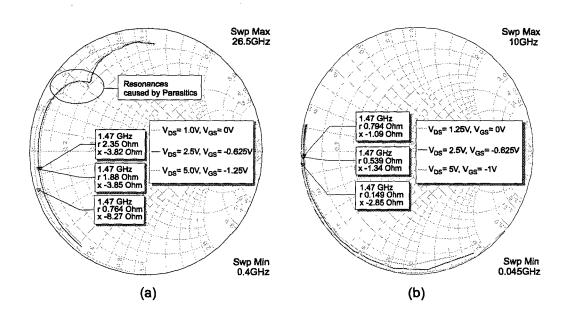

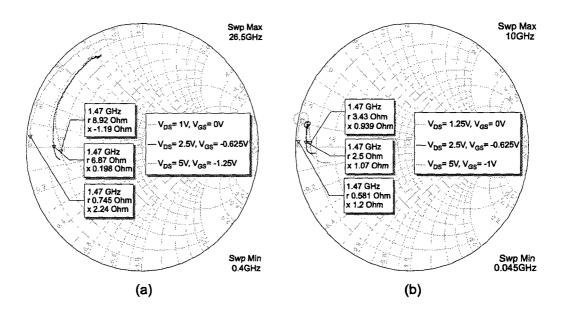

|          | High frequency DC test setup with temperature control                                  | 88  |

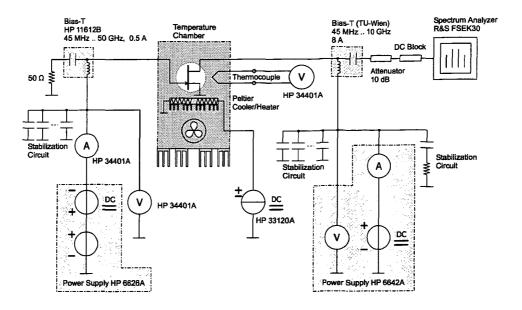

|          | High current DC test setup with temperature control                                    | 89  |

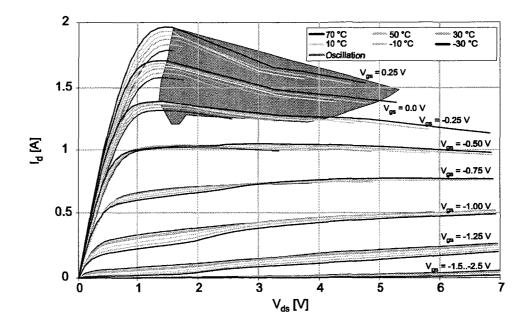

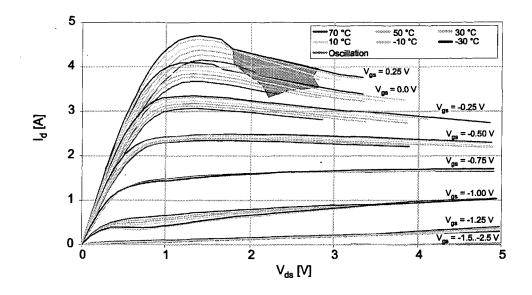

|          | DC I/V characteristic of a EPA480CV device measured at different ambient               |     |

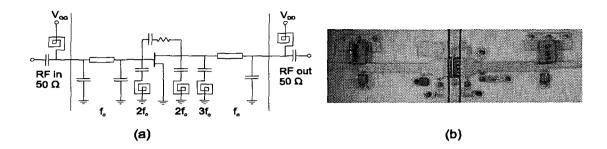

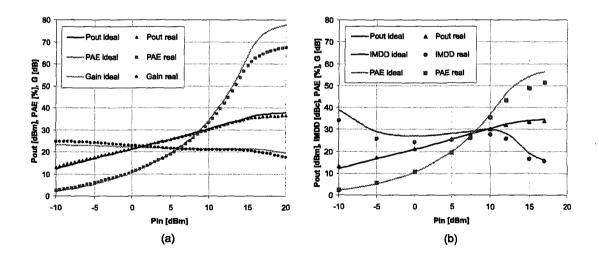

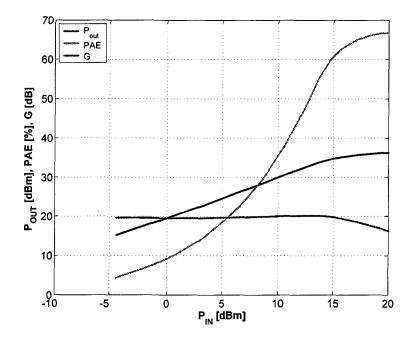

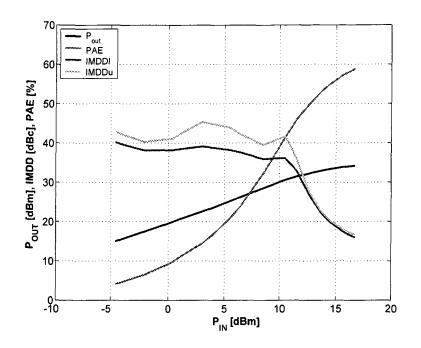

| <u>-</u> | temperatures                                                                           | 89  |