Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## DISSERTATION

# Code Optimizations for Digital Signal Processors

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

ao.Univ.Prof. Dipl.-Ing. Dr. Andreas Krall

E185

Institut für Computersprachen

eingereicht an der Technischen Universität Wien

Fakultät für Technische Naturwissenschaften und Informatik

von

## Dipl.-Ing. Erik Eckstein

9125255 Vöslauerstrasse 26/2/3 2500 Baden

Wien, am 5. November 2003

## Kurzfassung

Digitale Signal Prozessoren (DSPs) spielen im Marktsegment der *Eingebetteten Computer Systeme* eine wichtige Rolle. Die Einsatzgebiete reichen von Mobiltelefonie, digitaler Bildverarbeitung bis hin zur Motorsteuerung. Die Anforderungen an die Signalprozessoren sind dabei meist hohe Rechenleistung bei niedrigem Stromverbrauch. Bis vor wenigen Jahren wurden DSPs in Assemblercode programmiert, da sonst die Anforderungen nicht zu erfüllen gewesen wären. Mittlerweile haben sowohl die Applikationen wie auch die Prozessorarchitekturen einen derart hohen Komplexitätsgrad erreicht, dass der Einsatz automatischer Übersetzer notwendig ist. Ein Übersetzer erzeugt aus einem Hochsprachenprogramm ein Maschinenprogramm, das auf dem DSP ausgeführt wird. Durch die Verwendung einer Hochsprache können die Software-Entwicklungskosten erheblich verringert werden. Entscheidend ist jedoch, dass der Übersetzer eine Code-Qualität erzeugt, die mit dem handoptimierten Assemblercode vergleichbar ist.

Die Übersetzer-Technologie wurde hauptsächlich für reguläre Prozessorarchitekturen entwickelt. Da DSP Architekturen viele Irregularitäten und applikationsspezifische Funktionalitäten aufweisen, können konventionelle Optimierungsmethoden des Übersetzerbaues nicht ohne weiteres für DSP-Übersetzer eingesetzt werden.

In dieser Dissertation werden Algorithmen vorgestellt, die drei wesentliche Problemstellungen im Übersetzerbau abdecken: Code-Generierung, Auswahl von Adressierungsmodi und Register-Allokation. Alle drei Algorithmen werden mit Hilfe von *Partitionierten Boolschen Quadratischen Problemen* (PBQP) beschrieben. Ein PBQP ist eine Art von quadratischem Zuordnungsproblem, das im Allgemeinen NP-vollständig ist und daher sehr schwierig zu lösen ist. Die Darstellung eines PBQP erfolgt als Kostenfunktion oder als PBQP-Graph, der mit Kostenvektoren und Kostenmatrizen annotiert ist. Es wird ein Lösungsverfahren präsentiert, das eine optimale Lösung berechnen kann, sofern der PBQP-Graph mit Hilfe von definierten Reduktionsregeln reduzierbar ist. Falls der Graph nicht reduzierbar ist, muss auf eine Heuristik zurückgegriffen werden. Da der Berechnungsaufwand nur linear mit der Anzahl der Knoten steigt, liefert der Lösungsalgorithmus meist sehr schnell ein Ergebnis.

In der Code-Generierung eines Übersetzers werden aus der Zwischendarstellung des zu übersetzenden Programms Instruktionen für die Zielarchitektur generiert. Traditionelle Algorithmen gehen dabei von einer baumartig strukturierten Zwischendarstellung aus. Durch einen gerichteten zyklischen Graphen kann der Datenfluss einer Funktion genauer beschrieben werden als durch einen Baum. Der vorgestellte Algorithmus bildet das Code-Generierungsproblem auf ein PBQP ab. Da die meisten PBQP-Graphen reduzierbar sind, findet der Lösungsalgorithmus in vielen Fällen die optimale Instruktionsreihenfolge. Viele DSP-Architekturen besitzen spezielle Funktionseinheiten zur Adressgenerierung. Die Aufgabe des Übersetzers ist es, die Adressierungsmodi so auszuwählen, dass die Codegröße oder die Ausführungszeit des Programms minimiert wird. Die Beschreibung als PBQP erlaubt es verschiedenartige und irreguläre Adressierungsmodi zu modellieren. Aufgrund der Beschaffenheit der PBQP-Graphen kann für das Adressierungsmodi Problem in fast allen Fällen eine optimale Lösung berechnet werden.

Die Register-Allokation bildet eine meist große Anzahl von Programmvariablen auf eine beschränkte Anzahl von Prozessor-Registern ab. Die meisten Register-Allokations-Algorithmen basieren auf der Methode des Färbens von Interferenz-Graphen. Obwohl diese Methode für reguläre Architekturen sehr gute Ergebnisse liefert, hat sie den Nachteil, dass andere Optimierungsparameter, außer Register-Interferenzen, nur bedingt einfließen können. Mithilfe eines PBQPs ist es möglich irreguläre Optimierungsparameter genau zu beschreiben. Da jedoch die resultierenden PBQP-Graphen meist nicht reduzierbar sind, baut die Heuristik im PBQP-Lösungsalgorithmus auf einen Graph-Färbungsalgorithmus auf um die Vorteile beider Methoden zu vereinen.

Alle vorgestellten Algorithmen wurden in einen Übersetzer für einen kommerziellen DSP integriert. Anhand von typischen DSP Applikationen wurden sie mit existierenden Methoden verglichen. Dabei zeigte sich, dass durch die Verwendung des PBQP-Lösungsansatzes erhebliche Verbesserungen in allen drei Optimierungsbereichen erzielt wurden.

## Abstract

Digital Signal Processors (DSPs) play an important role in the embedded systems market. The application areas range from mobile telecommunication, digital image processing to engine control. The requirements for signal processors are often high performance at low power consumption. In the past years DSPs were merely programmed in assembly language to meet the hard requirements. In recent times the complexity of both the DSP applications and the DSP architectures have increased dramatically. Therefore the use of compilers became necessary. A compiler translates a high level language into machine code, which can be executed on a DSP. The use of a high level language reduces the software development times significantly. The compiler has to generate a code quality which is comparable to hand-optimized assembly code.

Compiler technology was mainly developed for regular processor architectures. As DSP architectures contain many irregularities and application specific functions, conventional optimization methods can not be directly applied to DSP compilers.

In this work, algorithms are presented which cover three important compilation problems: code generation, addressing mode selection and register allocation. All three algorithms are described with the help of *partitioned boolean quadratic problems* (PBQPs). A PBQP is a kind of quadratic assignment problem, which is NP-complete in general and therefore it is hard to solve. A PBQP can be formulated as a cost function or as a PBQP-graph, which is annotated with cost vectors and cost matrices. The presented solver is able to calculate a optimal solution if the PBQP-graph is reducible with defined reduction rules. If the graph is not reducible, heuristics are used to obtain a solution. The computational complexity is linear with the number of nodes in the PBQP-graph. Therefore the solver yields a solution in short time.

The code generation phase in a compiler translates the intermediate representation of a program to instructions for the target architecture. Traditional methods assume a tree-like intermediate representation. But cyclic directed graphs can describe the data flow of a function more precisely. The presented algorithm maps the code generation problem to a PBQP. As most of the PBQP-graphs are reducible, the solver can find an optimal instruction selection in many cases.

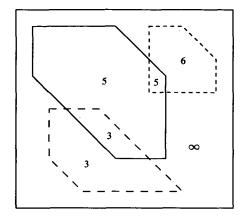

Many DSP architectures provide functional units for generating addresses. The task of the compiler is to select addressing modes so that the execution time or code size of the program is minimized. The formulation as a PBQP allows modeling of various irregular addressing modes. The PBQP-graphs of the addressing mode selection problem are reducible in almost all cases, enabling the calculation of optimal results.

Register allocation maps a large number of program variables to a limited number of processor registers. Most register allocation algorithms are based on the method of coloring an interference graph. This method yields good results for regular architectures, but it is difficult to model register constraints other than interferences. The PBQP enables the exact formulation of all kinds of irregular register constraints. As the resulting PBQP-graph are not reducible in many cases, the graph coloring heuristics are integrated into the PBQP solver. This combines the advantages of both methods.

All presented algorithms were integrated into a compiler for a commercial DSP. Typical DSP applications were used to compare the algorithms with existing methods. The results have shown that the PBQP method achieved significant improvements for all three optimization problems.

## Acknowledgments

Many people have contributed to this work. Without the help of the people from university and the company, my family and my friends I couldn't have completed or even started writing this thesis.

First of all, I would like to thank Professor Andreas Krall, my thesis adviser. Andreas Krall motivated me for doing this work at all. He helped and inspired me since I started doing compiler research. Most of my compiler knowledge I owe to him. Many thanks go to Eduard Mehofer, my secondary adviser, for reviewing the thesis.

I'd like to thank all the people which I am glad to work with. Especially I want to thank Bernhard Scholz. We spent a lot of time together and many ideas were born in countless fruitful discussions I had with him. Almost all of the research work contained in this thesis was done together with him. Bernhard is not only a great colleague but also a good friend who encouraged me in good and in bad times. Finally I thank him for reviewing this thesis.

Many thanks go to my colleagues at Atair Software, especially to Oliver König, Christian Pirker, Albrecht Kadlec, Alexander Wolf, Paul Wögerer and Sylvain Lelait. Being able to work together with this great team was the indispensable base for doing compiler research – and it is a lot of fun. Special thanks to Oliver for implementing the SSA-graph matcher. I like to thank Anton Ertl from the University of Technology in Vienna for his comments on pattern matching. I'd also like to thank R. Nigel Horspool from the University of Victoria for reviewing the thesis and for giving valuable comments.

Finally I give my wholehearted thanks to my family. I'd like to thank my beloved parents, Elsa Eckstein and Kurt Eckstein for supporting me throughout my life and enabling me to go to the university.

Especially I want to thank Heidi Rotteneder for being the sunshine in my life. She encouraged and supported me all over the time. Thanks to my two little children, Rahel and Esther, for bringing so much joy into my life.

v

## Contents

,

| Kurzfassung     |                                          |                                        |     |  |  |  |  |  |  |  |  |  |  |  |

|-----------------|------------------------------------------|----------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|--|

| Ał              | ostrac                                   | t                                      | iii |  |  |  |  |  |  |  |  |  |  |  |

| Acknowledgments |                                          |                                        |     |  |  |  |  |  |  |  |  |  |  |  |

| 1.              | Intro                                    | oduction                               | 1   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.1.                                     | Overview                               | 2   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.2.                                     | DSP Architectures                      | 2   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.3.                                     | Code Generation                        | 4   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.4.                                     | Contribution of this Work              | 5   |  |  |  |  |  |  |  |  |  |  |  |

| 2.              | Rela                                     | Related Work                           |     |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.1.                                     | Overview                               | 8   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.2.                                     | Code Generation                        | 9   |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.3.                                     | Addressing Code Optimization           | 13  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.4.                                     | Register Allocation                    | 16  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.5.                                     | Partitioned Boolean Quadratic Problems | 21  |  |  |  |  |  |  |  |  |  |  |  |

| 3.              | Partitioned Boolean Quadratic Problems 2 |                                        |     |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.1.                                     | Overview                               | 26  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.2.                                     | Background                             | 26  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.3.                                     | PBQP Definition                        | 28  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.3.1. The PBQP-Graph                  | 31  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.3.2. PBQP Complexity                 | 32  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.4.                                     | Optimal Solver                         | 33  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.4.1. Phase 1: Reduction              | 34  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.4.2. Phase 2: Trivial Solution       | 38  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.4.3. Phase 3: Back Propagation       | 39  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.4.4. Simplifications                 | 40  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.5.                                     | General Solver                         | 41  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                          | 3.5.1. Local Minimum                   | 41  |  |  |  |  |  |  |  |  |  |  |  |

### Contents

|    |      | 3.5.2. Recursive Enumeration          |

|----|------|---------------------------------------|

|    | 3.6. | Implementation                        |

|    |      | 3.6.1. Complexity of the Solver       |

| 4. | Cod  | e Generation 47                       |

|    | 4.1. | Overview                              |

|    | 4.2. | Motivation                            |

|    | 4.3. | The SSA-Graph                         |

|    | 4.4. | Mapping to a PBQP                     |

|    |      | 4.4.1. Normal Form                    |

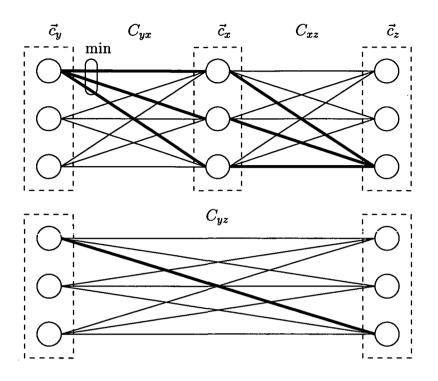

|    |      | 4.4.2. The PBQP-Graph                 |

|    |      | 4.4.3. Defining Cost Vectors          |

|    |      | 4.4.4. Defining Cost Matrices         |

|    | 4.5. | Solving the PBQP                      |

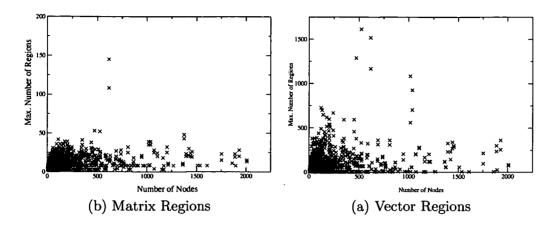

|    | 4.6. | Experimental Results                  |

|    |      |                                       |

| 5. |      | ressing Mode Selection 65             |

|    | 5.1. | Overview                              |

|    | 5.2. | Motivation                            |

|    | 5.3. | Modeling of the AMS Problem           |

|    |      | 5.3.1. Addressing Modes               |

|    |      | 5.3.2. Basic Idea                     |

|    | 5.4. | Mapping to a PBQP                     |

|    |      | 5.4.1. The PBQP-Graph                 |

|    |      | 5.4.2. Defining the Costs             |

|    | 5.5. | Solving the PBQP                      |

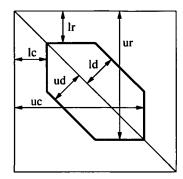

|    | 5.6. | Sparse Matrix Implementation          |

|    |      | 5.6.1. Sparse Matrix Representation   |

|    |      | 5.6.2. Sparse Vector Representation   |

|    |      | 5.6.3. Operations                     |

|    |      | 5.6.4. Complexity                     |

|    | 5.7. | Experimental Results                  |

| 6. | Reg  | ister Allocation 93                   |

|    | 6.1. | Overview                              |

|    | 6.2. | Motivation                            |

|    | _    | Register Constraints                  |

|    |      | 6.3.1. Constraints on one Live Range  |

|    |      | 6.3.2. Constraints on two Live Ranges |

|    | 6.4. | Mapping to a PBQP                     |

|    |      | 6.4.1. The PBQP-Graph                 |

|    |      |                                       |

-

viii

### Contents

|               |        | 6.4.2.<br>6.4.3.<br>The P<br>Experi | De<br>PBQ | finin<br>P So | g Co<br>lver | ost I<br>for 1 | Mat<br>Reg | rices<br>jiste: | 3<br>rAl | loc | <br>atio | <br>on | • | •   | • | ••• | • | • | <br> | • | • | <br> | • | • | 103<br>104 |

|---------------|--------|-------------------------------------|-----------|---------------|--------------|----------------|------------|-----------------|----------|-----|----------|--------|---|-----|---|-----|---|---|------|---|---|------|---|---|------------|

| 7. Conclusion |        |                                     |           |               |              |                |            |                 |          |     |          |        |   | 111 |   |     |   |   |      |   |   |      |   |   |            |

| A             | . Prod | ofs                                 |           |               |              |                |            |                 |          |     |          |        |   |     |   |     |   |   |      |   |   |      |   |   | 115        |

| Bibliography  |        |                                     |           |               |              |                |            |                 |          |     |          |        |   | 123 |   |     |   |   |      |   |   |      |   |   |            |

.

# 1. Introduction

-

· · ·

1

,

#### 1. Introduction

## 1.1. Overview

In recent years embedded systems have become very popular in the electronics industry. An embedded system is a computer system, consisting of hardware and software, which is part of a larger device.

The requirements of an embedded system are different from a general-purpose computer system, like a workstation or server. Many embedded systems operate inside a mobile device. Therefore low power consumption is an important aspect. On the other hand embedded systems often have to meet real-time constraints. Often the design of embedded systems is driven by the goal of reducing manufacturing costs, because they are produced in large quantities.

As a result, embedded systems usually have smaller memory sizes and run at a lower clock rate than general-purpose computers.

Digital signal processors (DSPs) play an important role in the embedded system market. DSPs evolved from custom digital hardware solutions which replaced analog signal processing circuits. The custom hardware was too error-prone and too inflexible. At this point DSPs provided a programmable alternative to expensive custom hardware. The application area of DSPs is computationally intensive signal processing algorithms. Since DSPs are often used in mobile devices they provide high computational performance with very low power consumption.

DSPs are used in many embedded devices like cellular phones, digital cameras, video game consoles, engine controls, medical equipments, network devices and many more. Two of the most prominent signal processing applications are GSM speech coding and decoding, and MP3 decoding.

## **1.2. DSP Architectures**

Nearly all architectural features in a DSP arise from the needs of signal processing algorithms. In this sense DSPs are application specific processors. As in the early days of digital signal processing DSPs were exclusively used for numerical signal processing, today's architectures are more general. The borders between micro-controllers and signal processors are diminishing. New DSP architectures include micro-controller functions and vice versa.

Although there are many different DSPs on the market today, they have some properties and features in common:

• *fixed point arithmetic:* Most DSPs do not have floating point units. Values are represented as fixed point values in the range from -1 to 1. Fixed point arithmetic is very similar to integer arithmetic. Minor differences are encountered with multiplications and divisions.

- 40 bit accumulator registers: With the help of 40 bit registers the fixed point value range of -1 to 1 is extended by 8 bits to -256 to 256. It is used to hold the overflow when performing accumulation loops.

- *explicit instruction level parallelism (VLIW):* To increase computational performance without having to push up the clock frequency, DSP architectures allow the execution of multiple instructions in parallel.

- single instruction, multiple data support (SIMD): To overcome the problem of large codes sizes in VLIW architectures, instructions are provided which can manipulate multiple data with a single instruction.

- *multiply-accumulate support:* The vector dot product is a very common operation in DSP applications. Therefore all DSP architectures incorporate a multiply-accumulate function, which enables the execution of a multiplication and addition in minimal time.

- high memory bandwidth: To cope with the high computational ability of a DSP it is necessary to fetch many operands from memory in short time.

- *memory spaces:* Many DSPs solve the memory-bandwidth-problem by implementing multiple memory spaces, which can be accessed in parallel.

- *addressing modes:* Some addressing modes allow the address registers to be updated and modified without any overhead. Therefore no explicit address arithmetic is necessary when accessing memory in a loop.

- *modulo addressing:* This kind of addressing mode allows implementation of circular buffers without any overhead.

- bit reverse addressing: For efficient implementations of fast Fourier transformations (FFT), which are very important in signal processing algorithms, DSPs provide an addressing mode for accessing buffers in a butterfly pattern. This is achieved by reversing the bit order of an incrementing address pointer.

- *zero overhead loops:* Most DSPs provide facilities to implement loops without any branching overhead. In most architectures special loop instructions perform this task.

- application specific functions: Dedicated instructions and registers are used to implement often used signal processing operations. An example is a decision back-trace register to implement Viterbi decoders.

- user responsible restrictions: Usually DSP hardware does not provide checks on the validity of instructions and operands. All hardware restrictions must be ensured by the user, this means by the assembler programmer or the compiler.

3

#### 1. Introduction

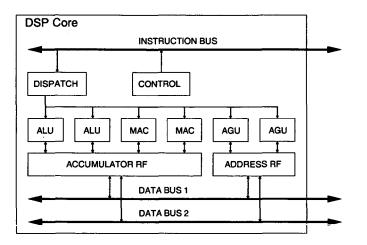

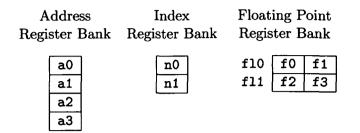

Figure 1.1.: Functional units of a DSP core

Figure 1.1 shows a block diagram of the functional units of a typical DSP. The instructions are fetched from the instruction bus and dispatched to the functional units. In this example the core contains two arithmetic units (ALU), two multiply-accumulate units (MAC) and two address generation units (AGU). The instruction stream contains one instruction for each unit (VLIW-architecture) so the units can operate in parallel. The units have access to the register files. The accumulator register file contains accumulators (e.g. 40 bits wide) to hold the calculation results. The address register file contains registers for generating addresses on the data busses. There are multiple data busses, e.g. one bus for each memory space, to increase the memory bandwidth of the system.

A DSP core is packed together with memory components, input-output (IO) components and other peripheral components on an integrated circuit. Large "system on a chip" designs may include multiple DSP cores together with other cores, like micro-controllers.

## 1.3. Code Generation

Code generation for DSPs started by programming applications in assembler. Early DSPs had very limited resources and good compilers were not available. Even today the heavily executed loop kernels are implemented in assembly language to achieve the required performance.

Nowadays most of signal processing software development is done with a high level language, in particular the C-language. The change from assembly language to C happened because of the following reasons: (1) DSP architectures got too complex for

5

hand coding, (2) the signal processing applications got very large, (3) time to market is reduced by using a high level language, (4) migration to a different architecture is eased with a high level language.

Compiler technology was mainly developed for RISC systems, which are very orthogonal. However, compilers for signal processors have to cope with irregularities:

- Fixed point arithmetic is not naturally expressible in C. Therefore C programs emulate fixed point calculations with integer arithmetic. The compiler must match the integer operations to the 40 bit fixed point arithmetic of the DSP.

- The compiler must handle all hardware restrictions of the DSP. The restrictions must be mapped to the optimization models in the compiler.

- Irregular instruction sets and register sets require flexible and configurable cost models in the compiler.

- DSP specific functions are not expressible in C, for example complex addressing modes, explicit memory spaces or application specific functions.

In addition to this requirements, the compiler must produce a code quality which is near to hand coded assembly language. Otherwise the code will not meet the constraints imposed by limited hardware resources.

Another aspect where code generation for embedded systems differs from RISC code generation is that code size is an important factor. The code size directly relates to the size of the silicon and to the power consumption, which is important for mobile devices. For this reason it must be possible to configure the compiler optimizations to either optimize for minimal execution time or to optimize for minimal code size. In signal processing applications the heavily executed loop kernels must be optimized for minimal execution time, the remaining code must be optimized for minimal code size.

### **1.4.** Contribution of this Work

This work presents an optimization framework to overcome the difficulties in code generation for DSP architectures. It allows us to generate exact models for irregular optimization problems. Although most of the problems are NP-complete we present an algorithm, which yields near optimal results. It is based on *partitioned boolean quadratic problems* (PBQPs).

The PBQP is an optimization problem which is similar to quadratic assignment problems used in operations research. We present a solver for the PBQP which runs in near linear time for a certain subclass of problems. For general general PBQPs a solver based on heuristics is used.

#### 1. Introduction

In this work we introduce three optimization problems where we employ the PBQP solver: code selection, addressing mode selection and register allocation. We show the mapping of the optimization problems to the PBQP and demonstrate how to model architecture specific constraints. The optimizers based on PBQP were implemented into an DSP production compiler which was used to obtain experimental results. The experiments show that the optimizers based on PBQP yield better results than traditional approaches.

In Chapter 2 we present the problems of code selection, addressing mode selection and register allocation. A survey of existing work on these optimization problems and quadratic assignment problems is given.

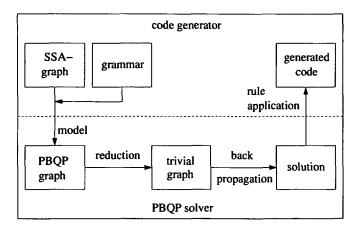

In Chapter 3 we introduce the PBQP and show that it is NP-complete. The PBQP can either be formulated as a quadratic equation or as a graph – the PBQP-graph. We present an optimal solver, which can derive a solution for the subclass of reducible PBQP-graphs. For non-reducible PBQP-graphs a general solver is used, which implements a heuristic.

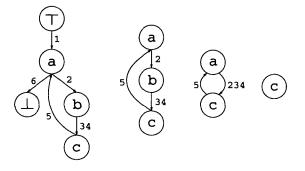

The code selection problem is addressed in Chapter 4. Code selection is performed by matching a graph, which represents the statements of the input program. The PBQP approach allows matching of a SSA-graph (which can be directly used as PBQPgraph), which includes all statements of a function. Even cyclic dependencies in the SSA-graph can be handled by the PBQP matcher. It is shown how to generate the PBQP formulation out of the grammar definition used by traditional tree pattern matchers.

In Chapter 5 the problem of *addressing mode selection* (AMS) is presented. The goal of AMS is to select addressing modes in the code instructions. Examples of widely used addressing modes are listed and it is demonstrated how to model them in the PBQP. With AMS, the PBQP-graph is derived from the control flow graph (CFG) of the input program.

The third optimization based on PBQP is introduced in Chapter 6. Various kinds of constraints are introduced, which are imposed by the register allocation problem in general and by irregular architecture features. The constraints are formulated as cost functions which are used to define the PBQP. The PBQP-graph is derived from the interference graph by adding edges which describe additional constraints.

Finally Chapter 7 concludes this work by comparing the three PBQP based optimization algorithms.

### 2.1. Overview

This work presents three applications of optimizations based on PBQP: SSA-graph matching, addressing mode selection and register allocation. They were first presented in [16, 18, 60]. All three applications can be assigned to the class of *back-end* optimizations.

In a compiler, the back-end optimizations are performed after high level optimizations to generate machine code from the high level intermediate representation (IR) of the program. High level optimizations [3, 51] are important for improving the result of the generated code. They include dead code elimination, constant propagation, function inlining, common subexpression elimination, arithmetic simplifications and strength reduction. An important class of high level optimizations is loop transformations [4], which are often used in DSP compilers to optimize numerical code. Loop transformations can rearrange the statements in a loop nest to improve the parallelism of the code.

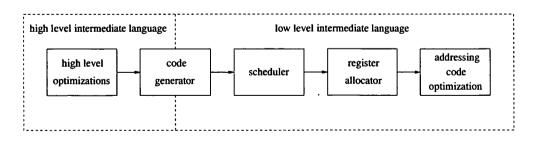

Traditionally there are three major building blocks in a compiler back-end: (1) the code generator, (2) the scheduler and (3) the register allocator. As this work is focused on back-end optimizations for embedded systems and especially for DSPs, we add a fourth important building part to the compiler back-end – the addressing code optimization (see Figure 2.1).

The execution order of the back-end optimizations may vary. Only the code generator is always performed first, because it represents the interface from the high level intermediate language to the low level intermediate language. The order of scheduling, addressing code optimization and register allocation imposes a phase ordering problem. In highly optimizing compilers these phases are performed multiple times.

In this work no attention is given to the scheduling part of the back-end optimizations. We used existing scheduling algorithms [28, 41, 58] and it turned out that they work well for our DSP compiler back-end. Therefore we did not investigate using a PBQP method for the scheduling optimizations in the compiler.

In the following sections we describe existing approaches to code generation, ad-

Figure 2.1.: Overview of a compiler

8

dressing code optimization and register allocation, and the relation to our work.

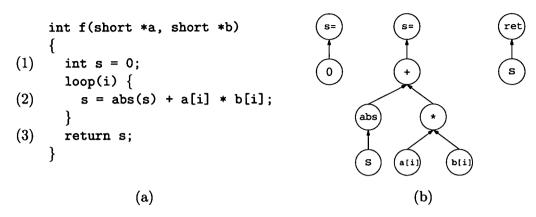

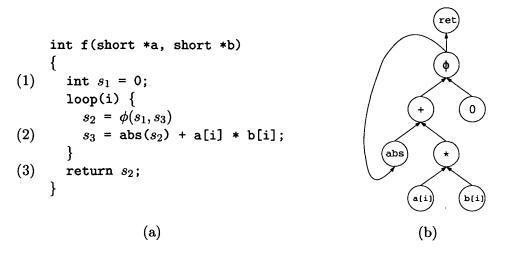

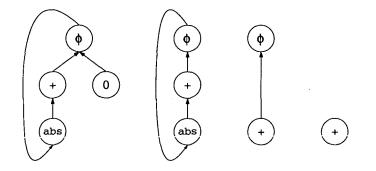

## 2.2. Code Generation

The code generator is the interface between the high level IR and the low level IR. It maps the high level IR statements to low level IR statements, which are strongly related to the machine instructions of the target architecture. Therefore code generation is also referred to as *instruction selection*. There are several approaches for code generation. Most approaches rely on a tree-like high level IR. The tree may be explicitly available as a graph structure or linearized in a string of symbols. Usually the unit of translation is a statement which represents a single data flow tree (DFT). The program to be compiled consists of many statements, so it is a collection of multiple DFTs. The nodes of a DFT are called *operators* and represent the expressions of the program.

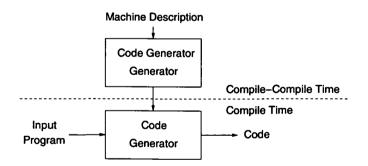

Modern code generators are built automatically from a machine description. The path from the machine description to the generated code involves two abstraction layers, which are shown in Figure 2.2. The code generator-generator builds the code generator from the machine description. This happens at *compile-compile time*, i.e. when the compiler is built. The code generator itself reads the input program and generates the code. This process runs at *compile time*.

Graham and Glanville [30] first identified the needs of a systematic method for building code generators. The method should have the same properties as methods for table-driven syntax analysis: modular, provable correct and easy to use. Graham and Glanville introduced a method which is very similar to a LR(1) parser. The differences are that the grammar for code generation is ambiguous and that a parse error would indicate a compiler bug. The format of the IR is a parenthesis-free prefix notation, which expresses the data flow trees.

A shift-reduce algorithm is used to parse the IR. The parser consists of a state S, a stack q and two tables. The NEXT-table is the state transition table, which selects

Figure 2.2.: Abstraction layers of code generation

a parser state depending on the current state and the next input symbol from the IR. The ACTION-table selects the action *shift*, *reduce*, *accept* or *error* depending on the state and the next input symbol. The *shift*-action pushes the next input symbol and the state onto the stack, whereas the *reduce*-action removes a whole right side of a grammar rule from the stack. At the *reduce*-actions, the code generation template of the reduced rule is emitted. The *accept*- and *error*-actions are the final states of the parser.

As the grammar is ambiguous conflicts may occur, which are solved by using a simple heuristic. For shift-reduce conflicts the parser performs the shift. This prefers "powerful" instructions, which map to larger parts of the IR. Reduce-reduce conflicts are either resolved by additional semantic constraints or by sorting the instructions according to a certain cost criteria.

A Graham-Glanville style code generator already has significant advantages compared to hand-crafted code generators: it produces good code, it is fast and it is automatically generated from a machine description – the grammar. Unfortunately the results are not optimal, because heuristics are used to resolve the ambiguities of the grammar. In addition the parsing is done in a left-to-right fashion. Therefore the selection for a left operand of an operator is always independent of the selection for the right operand.

Tree pattern matchers, based on the BURS (bottom-up rewrite systems) theory overcome the limitations of the Graham-Glanville style code generators. They were first introduced by Pelegri-Llopart and Graham [54].

A tree pattern matcher is defined by an ambiguous tree grammar. A reduction rule in the grammar describes a tree which is matched with a subtree in the DFT and replaced with the resulting non-terminal. Such rules are called *pattern rules* and are of the form  $nt \rightarrow pattern$ , where the pattern contains a tree with non-terminals and terminals. The terminals are operators in the DFT. In addition to pattern rules, a grammar may contain *chain rules* (of the form  $nt1 \rightarrow nt2$ ) which allow transitions between non-terminals. Both types of rules have an associated cost value and a code generation action. For each reduction the code generation action inserts low level code in the output IR. The cost value represents the execution time or code size of the inserted code. As the grammar is ambiguous, there may be many possible matches for a tree. The task of the matcher is to select an *optimal match*, which is the cover of the IR tree so that the sum of all applied rule costs is a minimum.

A BURS-based code generator contains a state automaton and works in two phases: labeling and reducing. In the labeling phase the DFT is traversed bottom-up and the operators are labeled with the states. In the second phase the code is emitted in a top-down walk by using the state information. The BURS automaton is built by constructing all possible states from the grammar using dynamic programming at compile-compile time. A state corresponds to a set of items, containing three pieces of information: the derived non-terminal, the relative costs and the rule, which generated the non-terminal. In an implementation an *itemset* is an array of  $\{rule, cost\}$  pairs, indexed by the non-terminal. The relative costs are the costs normalized to the minimum cost value in the itemset. Therefore each itemset contains at least one cost value of zero. In the state construction algorithm all state transitions for each state and operator combination are generated. This process is repeated until no more new states are derived.

The advantage of a BURS-based code generator is that it is very fast, because the hard work of building the state transition table is done at compile-compile time and not at compile time. But there are two problems which must be addressed. First the state transition table can get very large. If the number of states is n, a direct encoding of the state transition table of a binary operator would contain  $n^2$  entries. As the number of states can be large (e.g. up to 1000 on a CISC machine [56]), this leads to large table sizes. Proebsting proposed several methods to reduce the table sizes [56, 57].

The second problem is that the cost values in the grammar must be available at compile-compile time. Therefore it is not possible to compute them dynamically in the code generator. For example a cost value could be depend on a constant value in an operator. In some cases this problem can be avoided by splitting rules into separate rules for each distinct cost value.

A popular example for a BURS-based matcher generator is BURG, which was presented by Fraser et al. [24]. It generates a code generator from machine specification, which is similar to the rule syntax of YACC [34]. Fraser et al. also proposed a modification of BURG, called IBURG, which performs the dynamic programming at compile time (in contrast to compile-compile time). This eliminates the two drawbacks of the BURS code generators at the expense of a sightly higher runtime.

In the labeling phase of the IBURG code generator the minimum costs are calculated for each node and each non-terminal combination and stored in cost vectors in the nodes. This is done by traversing the DFT bottom-up. A cost vector element represents the reduction with minimal cost for this node and non-terminal. For each node first all applicable base rules are checked. Then all chain rules are applied for a node until the cost vector does not change any more. In the second phase, the reduction phase, the DFT is traversed top-down, starting at the root node while selecting the non-terminal with minimal cost. The rule, which led to the selected non-terminal is identified at each node and its code generation action is applied.

The matcher generators IBURG [23] and BEG [19] use this technique. The time consumed for each node of the DFT is  $n^2$  where n is the number of non-terminals in the grammar. Obviously this is slower than the constant time needed for a state transition in a BURS-based code generator. But the advantage is that no large state transition table is needed and the rule costs can be selected at compile time.

The drawback of all techniques outlined above is that they can only be performed on trees. This is a considerable limitation, because even if IRs are tree-like they contain

DAG structures in some ways. DAGs are either introduced by common subexpressions or by multiple def-use relations. If the computational flow inside the IR is taken into account, the input graphs for code generation are even directed graphs, which may contain cycles.

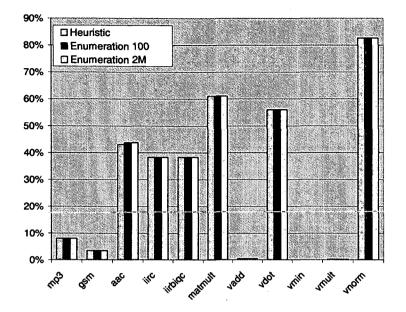

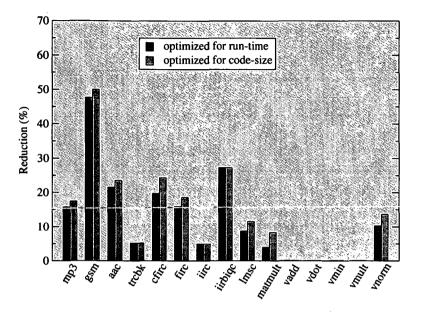

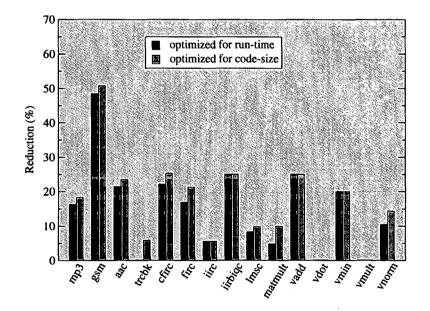

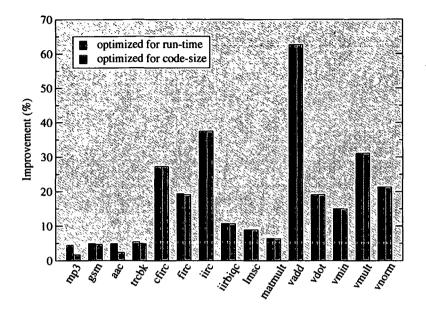

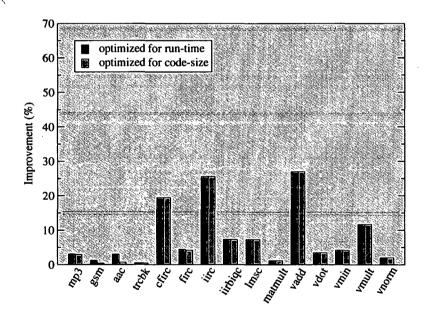

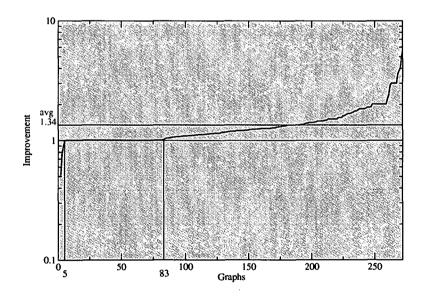

Unfortunately pattern matching on DAGs or directed graphs is NP-complete [55]. Several approaches have been proposed to overcome this problem. Many code generators simply split the DAG into trees and perform the pattern matching on the trees [2, 22, 19]. In our experiments we compare our SSA-graph matcher with this approach. It is shown that splitting the DAG into trees yields suboptimal results in many cases. The performance difference is up to 83%.

In the work of Anton Ertl [20] an approach is presented, which modifies the tree pattern matcher algorithm so that it can be used on DAGs. The tree traversal algorithm is extended by a visited flag so that it can be used on DAGs. Apart from that change, the labeling and reduction phase work like in the tree pattern matcher. The question arises if this straight forward extension also yields optimal results for DAGs. Ertl shows that this depends on the grammar. A checker, called *DBURG*, analyzes the grammar and reports if the grammar, applied on DAGs, does not yield optimal results. The checker constructs an inductive proof over all DAGs. For all ways of sharing a subgraph it is checked if all derivations are optimal. This approach differs from our approach in some points: First, for a shared node, code may be duplicated, because for each share a different non-terminal may be selected and code is generated for all selected non-terminals. Second, it is not possible to perform the algorithm on a graph containing cycles, because it still relies on the bottom-up and top-down phases of the tree pattern matcher. Cycles occur in the SSA-graph for example if the input program contains loops. As loops are important to optimize, the code generator should be able to handle cycles.

Liao et al. [46] formulate DAG pattern matching as *binate covering problem*. The algorithm works in three steps. First all matches of rules in the subject DAG are identified. A boolean variable represents the successful match of a rule for a node in the DAG. In the second step a covering matrix is built. The matrix expresses the conditions for a legal cover of the DAG. For each match, i.e. boolean variable, there is a column in the matrix. The rows represent disjunctive clauses where each variable appears with its true and complement form (therefore the problem is called binate covering problem). There are rows for each node which describe the possible matches for the nodes. In addition there are rows which are needed to formulate the dependencies — that means the connections — between the matches.

In the third step a cover with minimum cost is generated, where the cost of a match (column) is the cost of the corresponding pattern. A set of columns is selected with minimum total cost by not violating the clauses represented by the rows. A branch and bound algorithm is used to obtain the cover.

In addition to the DAG pattern matching problem, this approach also allows the

#### 2.3. Addressing Code Optimization

inclusion of other code generation tasks in the problem formulation. Liao et al. formulate DAG pattern matching, scheduling and spill code generation for a single accumulator architecture. Unfortunately exact solutions can only be found for small to medium sized basic blocks because of the exponential complexity of the binate covering problem. In addition this approach still does not consider the computational flow of functions.

Leupers introduced code generation to utilize SIMD instructions, based on *integer linear programming* (ILP) [42]. The difficulty of SIMD instruction selection is that a single SIMD instruction represents operations in different data flow trees. Leupers uses an algorithm which first performs tree pattern matching for each data flow tree separately. But the matcher is modified so that it gives the set of *all* optimal matches instead of one optimal match. The second part of the algorithm selects between the optimal matches to maximize SIMD instructions. This selection is formulated as an ILP problem.

## 2.3. Addressing Code Optimization

Addressing code optimization is a rather new topic in the field of back-end optimizations. An overview of current research work can be found in [1]. The goal of addressing code optimization is to utilize the address generation units (AGUs) of the target CPU. DSPs feature AGUs to efficiently generate memory addresses in numerical algorithms. But AGUs can also be found in micro controllers and CISC architectures (like the Motorola 68K) AGUs can be found. The main purpose of AGUs is to perform address calculations in parallel with other units of the processor. The most prominent operation of an AGU is to automatically increment or decrement an address register after accessing the memory.

Addressing code optimization is a collection of different optimization techniques. It mainly consists of three separate optimization domains:

- Offset assignment: allocating memory locations (offsets) for local variables to utilize the auto-increment addressing modes.

- Address register assignment: assigning address registers to access data for which the memory layout has been already defined.

- Addressing Mode Selection (AMS): selecting the best addressing modes for the instructions. AMS is used in offset assignment and address register assignment to generate the resulting code.

Much work has been done in the field of offset assignment and address register assignment. On the other hand there is little work concerning addressing mode selection. Although AMS is used in offset assignment and address register assignment

algorithms, the AMS problem was first formulated as a separate problem in [18]. The AMS problem is independent from offset assignment and address register assignment and this work focuses only on addressing mode selection. Nevertheless offset assignment and address register assignment can be used to improve the result of AMS.

Offset assignment is the problem of assigning a frame-relative offset to each of the local variables of a function to minimize the number of address-arithmetic instructions required to execute a basic block. Bartlay [8] was the first to address the offset assignment problem and presented an approach based on finding a Hamiltonian path of maximum weight on the graph.

Liao [47, 48] et al. formulated the simple offset assignment problem (SOA) which is an offset assignment problem with a single address register. They modeled the problem as a graph theoretic optimization problem similar to Bartlay and showed that the SOA problem is equivalent to the maximum weighted path covering (MWPC) problem and proved that it is NP-complete. In addition they extended the SOA to the general offset assignment (GOA) problem, which can handle multiple address registers. They proposed a heuristic algorithm to solve both the SOA and GOA problems. The work of Liao et al. built the base for a set of extensions. Leupers and Marwedel [44] proposed a tie-breaking heuristic and a variable partitioning strategy to improve the SOA and GOA result. They also used modify registers to reduce the solution costs. Sudarsanam et al. [62] extended the SOA and GOA problems by allowing an autoincrement/decrement addressing mode within a range from -l to +l.

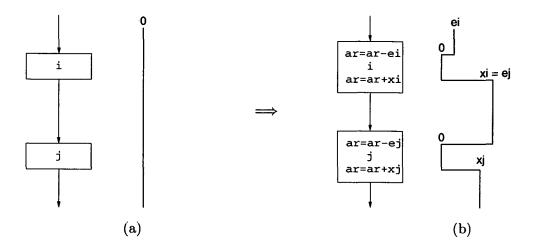

In [48] Liao also deals with the generation of auto-increment values for a given access sequence, which in fact is a basic form of addressing mode selection. The calculation of auto-increment values is trivial within a linear sequence of accesses, i.e. a basic block: the increment value is the difference between the offset of two consecutive accesses. The calculation of auto-increment values for a whole control flow graph (CFG) is more complicated. Liao proposes an algorithm which first identifies equivalence classes of edges. Two edges are in the same class if they have the same predecessor or successor node. An edge class represents an zig-zag pattern in the CFG. This method of identifying edge classes is also used in our approach for building the PBQP-graph for AMS. Liao argues that the number of edges in a class is limited to a small number. The problem is to find the places and values for update instructions for an edge class so that the execution time penalty is minimal. Due to the small number of possibilities, Liao's algorithm enumerates all variants and selects the one with smallest costs. The limitation of this approach is that every basic block must contain at least one access and only post modification addressing modes can be handled. Only these assumptions allow the use of the local solution within the adjacent basic blocks of a single edge class. As soon as a basic block contains no accesses or - for example indirect-with-offset addressing modes are available, information can flow across basic block boundaries and the local solution is not guaranteed to be optimal.

In [17] we already described the problem of selecting post modifications, with the

#### 2.3. Addressing Code Optimization

possibility of basic blocks containing no memory accesses. But the proposed algorithm uses a heuristic and therefore it can not yield the optimal solution in many cases.

Address register assignment is used to assign address registers to variable accesses for which the offsets have been already determined. The goal is to reduce update instructions by using a minimal set of address registers to access arrays or variables inside a loop. The problem of assigning address registers to array references inside a single basic block was first described by Araujo [6] and Leupers [43]. They introduced the *local reference allocation* (LRA) problem which is solved by formulating a path covering problem on an *indexing graph* (IG). The nodes of the IG represent array references in the basic block. For each possibility for an auto-increment or autodecrement addressing mode between two accesses, the IG contains an edge. So a path in the IG represents a sequence of accesses which can be addressed by a single address register with exclusively using auto-increment or auto-decrement.

Cintra et al. [14] and Ottoni et al. [52] extended the LRA problem to the global reference allocation (GRA) which can handle multiple basic blocks rather than a single basic block. In the GRA algorithm, live range merging tries to utilize all available address registers to minimize update instructions in a loop. The used technique is called *live range growth* (LRG) which repeatedly merges pairs of address register live ranges. The algorithm starts by assigning a range to each reference in the loop. Then ranges are merged pairwise until the number of live ranges is no greater than the number of available address registers. The key point of the algorithm is a merge operator which determines the costs of merging. It yields the number of explicit update instruction which is imposed by merging two live ranges.

For evaluating the merge operator Ottoni et al. construct a  $\phi$ -dependence graph  $(DG_{\phi})$ , which is derived from a static single assignment form (SSA) of the program. The  $DG_{\phi}$  represents an equation system where the unknowns are *virtual references*. Each  $\phi$  term forms an equation which imposes a decision of update values between the virtual references of the  $\phi$  term arguments and the virtual reference of the  $\phi$  term result. The problem of solving the equation system is NP-complete. A  $\phi$ -Solution graph  $(SG_{\phi})$  is derived from the  $DG_{\phi}$  which represents all possible solutions. If the  $DG_{\phi}$  is a tree an optimal solution can be found using an algorithm based on dynamic programming which operates on the  $SG_{\phi}$ . Otherwise heuristics are used to calculate a solution.

The evaluation of the merge operator is very similar to the definition of addressing mode selection, because the merge operator minimizes the number of update instructions needed for a live range merge. Compared to our approach for addressing mode selection, the merge operator algorithm has some significant limitations:

- Only auto-increment, auto-decrement and update instructions are considered. It is not possible to define other addressing modes with a flexible cost model.

- The algorithm works for a single loop. It is not obvious how to handle the control

flow graph of a whole procedure.

• In many cases the  $DG_{\phi}$  is not a tree and heuristics are used to obtain a solution. In contrast our solver for the AMS problem yields an optimal solution in almost all cases, even if the  $DG_{\phi}$  is not a tree.

## 2.4. Register Allocation

Register allocation is an essential part in a compiler back-end. It maps live ranges to physical registers. A live range is the collection of program points where a data value (e.g. a local variable or temporary) is live. Before register allocation the input program may contain a large number of live ranges which have to be mapped to a – for most embedded architectures – small number of CPU registers. If no mapping can be found for a live range, it is spilled to memory and additional load and store instructions are inserted.

Register allocation algorithms can be classified by the scope they operate on.

- Local register allocation is performed on a linear sequence of instructions, i.e. a basic block. It is often used as a pre-pass to global register allocation.

- Global register allocation allocates registers for a procedure. All basic blocks of the control flow graph are taken into account. The main focus in research has been put on global register allocation and many commercial compilers implement only this kind of register allocation. If not explicitly stated otherwise, the term "register allocation" refers to global register allocation.

- Inter-procedural register allocation selects which registers are available for each procedure in the program. The register allocator decides which registers must be saved during a function call.

In the following we concentrate on global register allocation and use the term "register allocation" for this allocation method. For details on local and inter-procedural register allocation the reader may refer to [21] and [40], respectively.

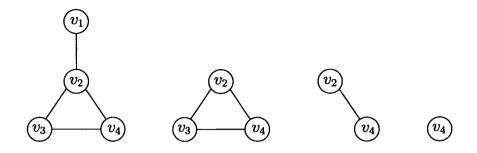

The commonly used technique for register allocation is graph coloring. It was first introduced by Chaitin et al. [12]. In the graph coloring approach an *interference graph* is first built. The nodes of this graph represent live ranges and the edges represent interferences, i.e. there is an edge between two live ranges if they are both live at some point in the program. Coloring the interference graph with k colors models the allocation problem if k CPU registers are available.

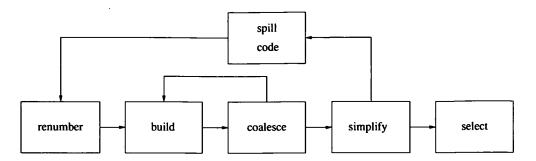

Figure 2.3 shows the phases of Chaitin's algorithm. The renumber phase identifies the live ranges in the program and in the build phase the interference graph is built. Coalescing tries to allocate two live ranges, which are in a copy relation, to the same

Figure 2.3.: The phases of Chaitin's register allocator

CPU register to minimize copy instructions. The simplify and select phases actually perform the graph coloring.

A node of degree less than k is trivial to color. Therefore the simplify phase eliminates nodes of degree less than k (low-degree node) from the graph and pushes them onto a stack. Eventually the graph is empty or all remaining nodes have a degree of at least k (significant-degree nodes). In the latter case a significant-degree node is marked as spilled, removed from the graph and simplification continues. Finally the select phase assigns colors, i.e. CPU registers, to the live ranges by popping nodes from the stack. For each popped node a color is selected which is distinct from the adjacent node colors. The simplify-select heuristics for solving graph coloring proved to be very efficient.

Chow and Hennessy proposed the *priority-based coloring* algorithm [13]. It has several significant differences to Chaitin's algorithm. First the register allocation runs *before* code generation on the high level IR. This means that temporary registers introduced by the code generator are not handled by register allocation. Instead of this, a fixed number of CPU registers are reserved for being used as temporaries (Chow and Hennessy propose to reserve four registers). This strategy might be a problem on embedded architectures, which typically have a small number of CPU registers. The priority-based allocator does not need to handle coalescing constraints, because it leaves this task to high level optimizations, which run earlier.

The second important difference to Chaitin's allocator is the coloring algorithm. In Chaitin's algorithm the starting point is that all live ranges are assumed to be in registers. During the algorithm some live ranges may be allocated in memory, i.e. spilled. In the priority-based algorithm at the starting point all live ranges are assumed to be in memory. Live ranges are assigned to registers in an order determined by a priority function. The algorithm stops if no more registers are available. Therefore there is no need to iterate the register allocator, like in Chaitin's model.

Another difference between the register allocation algorithms is the unit of allo-

cation. Chaitin's allocator takes an instruction as smallest unit whereas the prioritybased allocator works on whole basic blocks. This makes the register allocator faster at the expense of a coarser granularity of allocation.

Chow and Hennessy also proposed a technique, called *live range splitting* to improve the coloring. If no color can be found for a live range, the live range is split so that at least a part of the original live range can be allocated to a register. The splitting algorithm starts with a basic block, preferably a definition at the entry point of the live range. Then all successor blocks are added where a CPU register is available for the live range. This is repeated in a breath-first traversal of the CFG. The so created new live range can be colored. If the remaining live range can also be colored the splitting algorithm terminates. Otherwise it is applied on the remaining live range again. The second possibility for termination is that the remaining live range can not be split anymore. In this case it is allocated to memory.

Almost all work on register allocation is based on Chaitin's or on Chow and Hennessy's approaches. Briggs et al. [10] improved Chaitin's coloring algorithm by a method called *optimistic coloring*. If only significant-degree nodes are left, such a node is pushed onto the stack instead of spilling it (it is called *potential spill*). In the select phase it is popped from the stack and tried to color. If still no color is available, it is spilled (*actual spill*). By delaying the spill decision to the select phase there is a chance that some significant-degree nodes can still be colored.

In their work, Briggs et al. also proposed an extension called *rematerialization*. For values, which are never killed, it is possible to reconstruct the value where it is needed instead of spilling and reloading it. Such values include all kinds of constant values and addresses in the static data area and in the stack frame. The algorithm for rematerialization works on the SSA-form of the procedure which in fact is a method for live range splitting. The values are propagated through the SSA-graph by using a algorithm similar to Wegman and Zadeck's constant propagation algorithm [64]. Code generation for  $\phi$ -nodes is performed by inserting copy instructions. The aggressive coalescing used in Chaitin's register allocator coalesces all copy-related nodes. Therefore it would also eliminate all these copy instructions and destroy the benefit of split live ranges. To overcome this problem Briggs et al. proposed conservative coalescing which coalesces two nodes only if it is guaranteed that the resulting node is not spilled.

George and Appel [26] experienced that in their compiler aggressive coalescing produced too many spills, but conservative coalescing left too many copy instructions. Therefore they proposed *iterated coalescing*. They integrated conservative coalescing tightly into a loop together with the simplify step. This increases the chances of coalescing to identify that the resulting node after coalescing will not be spilled.

But even that missed some optimization opportunities. Park and Moon [53] concentrated on the positive aspects of aggressive coalescing. They transferred the idea of optimistic coloring to *optimistic coalescing*. In their register allocator first aggressive coalescing removes all copy-related live ranges. Later if a coalesced live range becomes an actual spill, then the live range is split by undoing the coalescing.

Vegdahl addresses another potential for improvements in register allocation. In [63] he proposes an algorithm to improve the graph coloring heuristics used inside the Chaitin style register allocators. Nodes of the interference graphs are merged which results in a better coloring.

Ambrosch et al. address another problem of interference graph based register allocation in [5]. Usually the interference graph is built from the instruction lists in the basic blocks of the control flow graph. But as this order is dependent on previous passes in the compiler, the number of edges in the interference graph may vary. Ambrosch et al. introduce a *minimal interference graph*, which is built from the data dependence graph. It contains only those interferences which are required to maintain the data dependencies. They also propose a new coloring method, called *dependence-conscious register selection*. It tries to minimize anti-dependencies to improve the scheduling of the resulting allocation.

The drawback of all the interference graph based coloring methods is that they can not be extended to irregular architectures in a straight forward way. It is not possible to model register constraints other than interferences. Even the coalescing constraint, which is also very important on regular architectures, is done in a separate phase.

Beside the traditional graph coloring approaches, which are a success story for RISC-like architectures, there is some work on allocating registers for irregular architectures. Briggs [9] and Smith et al. [61] address the problem of allocating register pairs. Register pairs can be found on many CPU architectures. For example pairs of single-precision registers are used to hold double-precision floating point values. Usually two constraints are imposed by register pairs: First, the registers of the pair must be adjacent (e.g. register R3, R4) and second, the pair must be aligned on an even register number (e.g. R2, R3). Both Briggs and Smith et al. concentrate on computing the colorability of the interference graph nodes, which is used by the simplify phase to distinct between low- and significant-degree nodes. Briggs modifies the interference graph by adding edges to nodes which represent paired registers. The intention is that the degree of a node always reflects its colorability, regardless of whether the node represents a single register or a register pair.

Smith et al. do not add edges to the interference graph but define weights for all nodes, which represent the pairing constraints. They call the extended graph a *weighted interference graph*. The weights of a node and its adjacent nodes are then used in the simplify phase to compute the colorability of the node.

A similar approach is presented by Runeson and Nyström in [59]. They formulate a  $\langle p, q \rangle$ -test for computing the colorability of a node. In contrast to Smith and Holloway's approach, the  $\langle p, q \rangle$ -test covers a wider range of irregularities and it is shown how to generate the test automatically from formal architecture descriptions.

The drawback of these approaches is that the computed colorability is a worst case value. If any of the adjacent and aligned constraints are imposed, the worst case

value does not reflect the real colorability and potential spills are generated in the simplify-phase. Moreover these techniques can handle only a small subset of possible register constraints.

Koseki et al. [38] introduced *preference directed graph coloring* for handling irregularities. The idea of this method is that register preferences can be satisfied by choosing the right order of registers in the select phase. Koseki et al. build a *register preference* graph and a color preference graph which are used to determine the coloring order of nodes in the interference graph. The register preference graph describes register preferences among live ranges. In their paper they list four types of such preferences:

- Dedicated register usage: a register is dedicated for a special purpose, like parameter or return value passing.

- Limited register usage: some instructions can only operate on a limited set of registers.

- Preferred register usage: registers are preferred for a live range, e.g. non-volatile registers are preferred for live ranges over function calls.

- Dependent register usage: the register selection for a live range depends on another live range. Examples are coalescing and paired registers.

In the selection algorithm the color for a live range is chosen by honoring the preferences to already allocated live ranges. Therefore the result of the allocation highly depends on the order of node selection. The color preference graph represents all possible orders which do not destroy the colorability. So the register selector tries to find the ordering of selection which allows it to honor as many preferences as possible. No separate coalescing phase is employed in the algorithm. Koseki et al. show in their experiments that the preference directed algorithm has the same coalescing capabilities as the optimistic coalescing approach [53]. If the register model has irregularities, which are not handled by the optimistic coalescing register allocator, the preference directed graph coloring yields better results in terms of execution time.

The preference directed register allocator – and all other approaches based on Chaitin's graph coloring algorithm – perform the register selection for a single live range at one time. Therefore the solution for a single live range is only a locally optimal solution, but not a global optimal solution for the whole problem. This seems to be sufficient for regular architectures, but leads to suboptimal results if many irregular constraints are involved.

Hirnschrott, Krall and Scholz compare two register allocation methods in [32]. The first is based on Briggs' allocator with aggressive coalescing. In addition Smith and Holloway's extension for handling irregularities [61] is included. The second method is based on our first PBQP approach [60], but enabling exhaustive recursive enumeration

#### 2.5. Partitioned Boolean Quadratic Problems

for obtaining optimal results. The comparison shows that the Chaitin-based algorithm causes significantly more spill costs than the optimal algorithm. The difference is even larger if only a few registers are available and spills occur often. Because of the exponential complexity, the optimal algorithm can only find a solution for small problem sizes in acceptable time.

Beside the graph coloring approaches, a register allocation algorithm based on integer linear programming (ILP) was introduced by Goodwin and Wilken [31] and improved by Fu and Wilken [25]. The approach maps the register allocation problem to an integer linear program which is solved by an NP-complete ILP-solver. Each allocation decision is mapped to a binary decision variable. It has the value 1 (the allocation action is performed) or 0 (the allocation action is not performed). Allocation actions include decisions, whether a live range should be mapped to a CPU register, whether the allocation should continue, or whether a spill or restore should be executed. The decisions have to be made at specific points in the input program. A 0-1 integer program is constructed and solved by a commercial integer program solver.

The work of Goodwin and Wilken was extended by Kong and Wilken [36] for irregular architectures. As an example, they chose the IA-32 architecture and added additional features such as address mode selection. The approach can handle irregularities very nicely. However, the algorithms for solving the integer linear programs have exponential running time and are therefore not used in commercial compilers.

## 2.5. Partitioned Boolean Quadratic Problems

Our methods for code generation, addressing mode selection and register allocation are based on *partitioned boolean quadratic problems* (PBQPs). The PBQP is a kind of *quadratic assignment problem* (QAP) which can be found in the field of operational research. It was first formulated by Koopmans and Beckmans in [37] for describing the problem of assigning plants to locations. Burkard et al. give a comprehensive overview of the QAP and related problems in [11]. They state that the QAP is one of the hardest optimization problems.

The QAP can be described as the problem of assigning facilities to locations. The goal of the optimization is to minimize cost. The distance and flow between the facilities and the cost of a facility assigned to a location contribute to the total cost. The original formulation of the QAP is as follows:

$$\min_{\phi \in S_n} \sum_{i=1}^n \sum_{j=1}^n f_{ij} d_{\phi(i)\phi(j)} + \sum_{i=1}^n e_{i\phi(i)}$$

(2.1)

where n is the number of facilities and locations. The set N = 1, ..., n and  $S_n$  is the set of all assignments  $\phi : N \to N$ . The values  $f_{ij}$  describe the flow between facility i

and j and  $d_{kl}$  is the distance between the location k and l. The value  $e_{ik}$  is the cost of placing facility i at location k.

The QAP can also be formulated as a quadratic integer program as shown in Equation 2.2. In this form the boolean variables  $x_{ij}$  select the assignment.

$$\min \sum_{i=1}^{n} \sum_{j=1}^{n} \sum_{k=1}^{n} \sum_{l=1}^{n} f_{ij} d_{kl} x_{ik} x_{jl} + \sum_{i,j=1}^{n} e_{ij} x_{ij}$$

(2.2)

subject to

$$\sum_{i=1}^{n} x_{ij} = 1, \ j = 1, 2, \dots, n$$

(2.3)

$$\sum_{j=1}^{n} x_{ij} = 1, \ i = 1, 2, \dots, n \tag{2.4}$$

$$x_{ij} \in \{0,1\}, \ i,j=1,2,\ldots,n$$

(2.5)

Burkard et al. list several algorithms for exact and heuristic solutions. In addition they describe a number of similar problems to the QAP. One related problem is the *Quadratic Semi-Assignment problem* (QSAP), which can be compared to our definition of the PBQP. The QSAP was investigated by Malucelli and Pretolani in [49, 50].

The difference between the QSAP and the QAP is that in the QAP there must be the same number of facilities and locations and in the QSAP there may be n facilities and m locations. In the QAP the assignment is bijective, i.e. each location gets a single facility. This is enforced by equations 2.3 and 2.4. In the QSAP each location can have zero, one or many facilities assigned. The quadratic integer programming formulation of the QSAP is equivalent to the QAP formulation, except that the constraint 2.3 is not included.

An example for the QSAP is the assignment of n processes to m processors [49]. Process i exchanges  $f_{ij}$  units of information with process j whereas the flow of one unit from processor k to processor l takes  $d_{kl}$  time. Process i needs  $e_{ik}$  time to run on processor k.

The QSAP formulation can be easily transformed to a PBQP formulation (Definition 1 in Section 3.3) by setting  $C_{ij}(k,l) = f_{ij} \cdot d_{kl}$  and  $\vec{c}_i(j) = e_{ij}$ . The boolean vectors in the PBQP correspond to the boolean variables in the QSAP:  $\vec{x}_i(j) = x_{ij}$ . In contrast to a QSAP, the decision vectors in the PBQP can have different sizes.

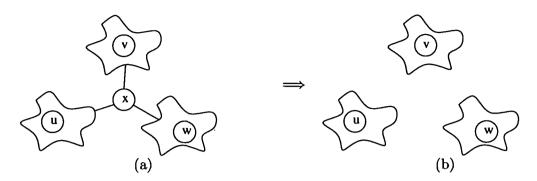

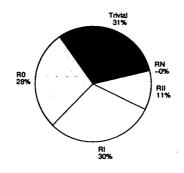

Malucelli and Pretolani identify a class of QSAPs which can be solved in polynomial time. These are problems whose associated communication graph are reducible by application of three reduction rules: (1) *tail reduction*, which is applied on nodes with degree one, (2) *series reduction*, which is applied to nodes with degree two and (3) *parallel reduction*, which is applied to parallel edges between two nodes. The rules are applied until a single node remains or all nodes have a degree more than two. In

the first case the result is exact, in the latter case the QSAP can not be solved in polynomial time.

This reduction method is also used by our optimal PBQP solver. The PBQP solver uses reduction rule RI which corresponds to the tail reduction. Rule RII is a combination of the series and parallel reduction.

Malucelli and Pretolani also propose methods to solve general QSAPs. They use a branch and bound algorithm and try to obtain a sharp lower bound for the QSAP. This differs to our approach, because the general PBQP solver uses heuristics if the point of non-reducibility is reached. This is fast and it is sufficient for our PBQP applications. In addition to the QSAP algorithm we employ simplifications on the PBQP-graph to improve the reducibility.

Beside of the QSAP there are other related problems to the QAP, like the bottleneck quadratic assignment problem (BQAP) and the bi-quadratic assignment problem. However these QAP variants have fewer similarities to the PBQP than the QSAP and the QAP and are therefore not in the focus of our work.

# 3. Partitioned Boolean Quadratic Problems

3. Partitioned Boolean Quadratic Problems

## 3.1. Overview

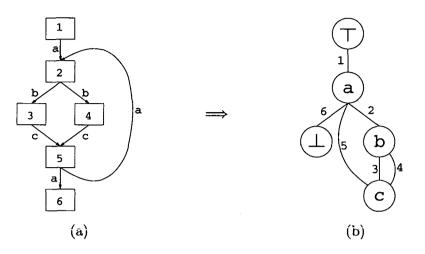

This chapter introduces the *partitioned boolean quadratic problem* (PBQP). It is used to formulate the optimization problems presented in this work – SSA-graph matching, addressing mode selection and register allocation.

The PBQP formulation has two main advantages over conventional approaches. First, the PBQP provides a unified interface to describe the problems with the help of cost vectors and cost matrices. So it is easy to formulate irregularities imposed by the target architecture. Second, there exists a solver which can yield optimal or near-optimal solutions for our optimization problems.

A PBQP can be described as a cost function or a graph problem. The cost function is the formal definition, whereas the graph representation is more descriptive. The graph representation is used by the solver.

As the complexity of a PBQP is NP it can not be solved optimally in general. But for a certain subclass of PBQPs an optimal solution can be computed in polynomial time. We present an optimal solver which computes the optimal solution if it is possible. If the optimal solver fails, a general solver can be used which employs heuristics for solving general PBQPs.

## 3.2. Background

**Vectors and Matrices** A matrix A is any rectangular array of elements. If a matrix A has m rows and n columns, we call A a  $m \times n$  matrix. Let A(i, j) be the  $ij^{th}$  element in the  $i^{th}$  row and  $j^{th}$  column. The  $i^{th}$  row is denoted by A(i, :) and the  $j^{th}$  column by A(:, j). A matrix in which all elements are zero is called a zero matrix.

A vector  $\vec{v}$  is a  $1 \times n$  matrix with *n* elements. Let  $\vec{v}(i)$  be the  $i^{th}$  element of the vector and let  $|\vec{v}| = n$  be the length of a vector. Vector  $\vec{1}$  in which all elements are one is called a one vector.

Given any  $m \times n$  matrix A, the transpose for A (written  $A^T$ ) is the  $n \times m$  matrix whose  $ij^{th}$  element  $A^T(i,j) = A(j,i)$ . Let A and B be two  $m \times n$  matrices. The matrix C = A + B is defined to be the  $m \times n$  matrix whose  $ij^{th}$  element is C(i,j) =A(i,j) + B(i,j). The matrix product  $C = A \cdot B$  of A and B is the  $m \times n$  matrix whose  $ij^{th}$  element is determined by  $C(i,j) = \sum_{k=1}^{l} A(i,k)B(k,j)$  where l is the number of columns in matrix A and the number of rows in matrix B. The product of two vectors  $\vec{u}$  and  $\vec{v}^T$ , both of length n, is called the *dot product*. It yields a  $1 \times 1$  matrix – a scalar.

A quadratic form is defined to be a vector-matrix-vector product  $\vec{x}A\vec{y}^T$ , which has the following properties:

$$\vec{x}A\vec{y}^T = \vec{y}A^T\vec{x}^T \tag{3.1}$$

$$\vec{x}A\vec{y}^T + \vec{x}B\vec{y}^T = \vec{x}(A+B)\vec{y}^T$$

(3.2)

26

In this work vector and matrix elements represent cost values. They are defined over the domain of real numbers including infinity  $(\infty)$ . We define the arithmetic operations for  $\infty$  as follows:

$$\infty \cdot 0 = 0 \cdot \infty = 0$$

$$\infty \cdot x = x \cdot \infty = \infty \quad \forall x \neq 0$$

$$\infty + x = x + \infty = \infty \quad \forall x$$

$$x \leq \infty \quad \forall x$$

**Minimum Operation** The minimum over parameter x of function f(x) is defined as follows,<sup>1</sup>

$$\min f(x) = f(\bar{x}) \quad | \quad \exists \bar{x} \in D, \forall x \in D : f(\bar{x}) \le f(x)$$

(3.3)

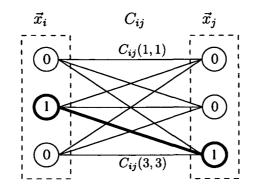

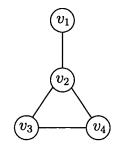

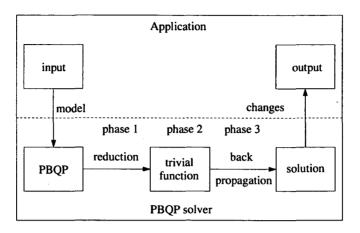

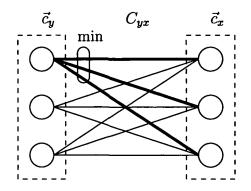

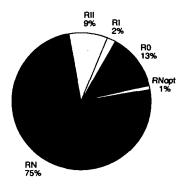

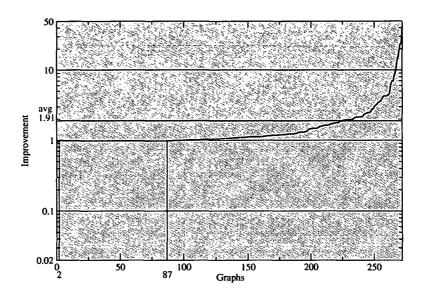

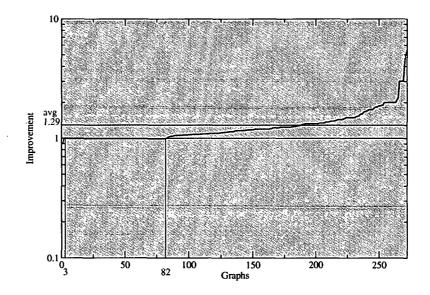

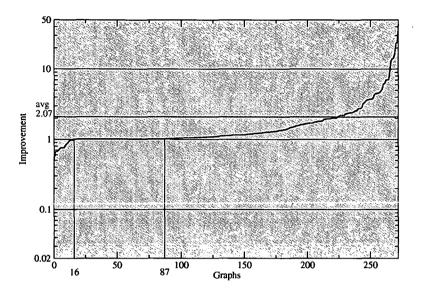

where D is the domain of x and  $\bar{x}$  is a solution of the minimum operation.<sup>2</sup> The partial minimum over parameter x of function f(x, y) is defined as follows,