Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## DIPLOMARBEIT

# A Superscalar 16 Bit Microcontroller for Real-Time Applications

ausgeführt am Institut für

Technische Informatik, Embedded Computing Systems Group Technische Universität Wien

unter der Anleitung von a.o.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger und Univ.Ass. Dipl.-Ing. Martin Delvai

durch

Gottfried Fuchs Canavesegasse 14 1230 Wien

Wien, 9. Dezember 2003

Für meine Eltern

### Danksagung

Für die fachliche und persönliche Unterstützung möchte ich folgenden Personen danken, die zum Gelingen dieser Diplomarbeit beigetragen haben: Martin Delvai, Thomas Handl, Wolfgang Huber, Peter Tummeltshammer und Angela Schörgendorfer

Besonderer Dank gebührt meinen Eltern und Großeltern, die mir dieses Studium durch ihre finanzielle, vor allem aber durch ihre seelische Unterstützung ermöglicht haben.

#### Kurzfassung

Im Zuge dieser Diplomarbeit wurde LANCE, ein superskalarer 16 Bit Mikrocontroller für Echtzeitanwendungen, entwickelt. LANCE ist Teil eines Baukastensystems für Mikrocontroller und basiert auf dem SPEAR Prozessor (Scalable Processor for Embedded Applications in Real-Time Environments), welcher am Institut für Technische Informatik - Embedded Computing Systems Group an der Technischen Universität Wien entwickelt wurde. Das Baukastensystem besteht aus mehreren Prozessorkernen, an die über eine generische Schnittstelle eine Reihe von Extension Modulen angeschlossen werden kann. Die Extension Module werden verwendet um den Prozessor an anwendungsspezifische Aufgaben anzupassen. Extension Module, welche für einen bestimmten Prozessorkern entwickelt wurden, können aufgrund der standardisierten Schnittstelle ohne jegliche Änderung von allen anderen Prozessoren verwendet werden. Die grundsätzliche Idee hinter dem LANCE-Entwurf war, einen Prozessorkern mit deutlich höherer Leistung als SPEAR zu entwickeln, ohne dabei die Code-Kompatibilität zu verlieren. Des Weiteren muss das Zeitverhalten von LANCE (wie auch von SPEAR) im Detail vorhersagbar sein, damit der Entwurf von Echtzeit-Systemen erleichtert wird. Um die zuvor genannten Anforderungen zu erfüllen, musste beträchtlicher Aufwand investiert werden um den Befehlsspeicher und das Register File dem Superskalar-Entwurf anzupassen. Aufgrund der Tatsache, dass LANCE zwei Befehle parallel ausführt, hat sich die Anzahl der Speicherzugriffe im Vergleich zu SPE-AR verdoppelt. Die Notwendigkeit für massives Daten-forwarding zur Aufrechterhaltung der Code-Kompatibilität zu SPEAR, wie auch die erwähnte Verdopplung der Speicherzugriffe pro Taktzyklus, waren die größten Herausforderungen während der Entwicklung von LANCE. Ein weiteres Problem entstand aus der bereits definierten Extension Module Schnittstelle, welche nur einen Modulzugriff pro Taktzyklus zulässt. Die oben genannten Probleme konnten durch sorgfältigte Abstimmung der parallelen Pipelines gelöst werden, sodass schließlich ein funktionsfähiger Prototyp vorliegt.

#### Abstract

In the course of this diploma thesis LANCE, a superscalar 16 bit microcontroller for real-time applications, has been developed. The LANCE design is part of a modular construction system for real-time applications and based on the SPEAR processor (Scalable Processor for Embedded Applications in Real-Time Environments), which has been developed at the *Institute for Computer Engineering - Embedded Computing Systems Group* at the *Vi*enna University of Technology. The modular construction system consists of several processor cores, a set of different so-called extension modules and a generic interface between these two types of components. The extension modules are used to adapt the processor core to different requirements imposed by a specific application. An extension module developed for one processor core can be used without any modification in all the others due to the standardized interface.

The basic idea behind the LANCE design was to design a processor core with significantly higher processing power than SPEAR without losing code compatibility. Furthermore, LANCE has to be temporally predictable like SPEAR to offer enhanced support of embedded real-time system design. To satisfy the previously mentioned requirements, considerable effort had to be invested to fit the instruction memory and register file to the superscalar design approach. Due to the fact that two instructions are executed in parallel, the memory access rate has doubled compared to SPEAR. The need for massive data forwarding to achieve code compatibility and the increased memory accesses per clock cycle were topics of great concern during the design of LANCE. Moreover, the extension module access implicated further problems due to the already defined module interface which only supports one access per clock cycle. The above introduced problems have been resolved by carefully tuning the parallel pipelines, which finally lead to a fully operative prototype.

### Contents

| 1        | Intr           | roduction                                                                                       | 1  |

|----------|----------------|-------------------------------------------------------------------------------------------------|----|

|          | 1.1            | Motivation                                                                                      | 1  |

|          | 1.2            | Processor Cores                                                                                 | 4  |

|          |                | 1.2.1 SPEAR                                                                                     | 4  |

|          |                | 1.2.2 NEEDLE                                                                                    | 6  |

|          | 1.3            | Extension Modules                                                                               | 8  |

|          |                | 1.3.1 Processor Control Unit                                                                    | 9  |

|          | 1.4            | Program Download                                                                                | 13 |

|          | 1.5            | Chapter Organization and Overview                                                               | 14 |

| <b>2</b> | Sup            | erscalar Designs - State of the Art                                                             | 15 |

|          | 2.1            | Intel Pentium                                                                                   | 15 |

|          | 2.2            | Motorola 68060 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 18 |

|          | 2.3            | PowerPC 601                                                                                     | 21 |

|          | 2.4            | Intel Pentium 4                                                                                 | 23 |

| 3        | $\mathbf{Spe}$ | cification                                                                                      | 25 |

|          | 3.1            | Instruction Set                                                                                 | 26 |

|          | 3.2            | Instruction Set Features                                                                        | 29 |

|          |                | 3.2.1 Conditional Instructions                                                                  | 29 |

|          |                | 3.2.2 Framepointer Operations                                                                   | 30 |

|          |                | 3.2.3 Subroutine Calls                                                                          | 31 |

|          |                | 3.2.4 Immediate Instructions                                                                    | 31 |

|          |                | 3.2.5 Exceptions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        | 32 |

|          | 3.3            | Code Restrictions                                                                               | 33 |

| 4        | Ove            | erall Design of the Microcontroller                                                             | 34 |

|          | 4.1            | Increasing Speed                                                                                | 34 |

|          | 4.2            | Superscalar Design Issues                                                                       | 37 |

|          | 4.3            | Microcontroller Architecture                                                                    | 40 |

|          | 4.4                  | Micro                       | controller Implementation       | 41 |  |  |  |  |

|----------|----------------------|-----------------------------|---------------------------------|----|--|--|--|--|

|          |                      | 4.4.1                       | Instruction Memory and Boot-ROM | 43 |  |  |  |  |

|          |                      | 4.4.2                       | Register File                   | 45 |  |  |  |  |

|          |                      | 4.4.3                       | Instruction Decode              | 47 |  |  |  |  |

|          |                      | 4.4.4                       | Exception Vector Table          | 48 |  |  |  |  |

|          |                      | 4.4.5                       | ALU                             | 49 |  |  |  |  |

|          |                      | 4.4.6                       | Data Memory                     | 50 |  |  |  |  |

|          |                      | 4.4.7                       | Extension Module Access         | 51 |  |  |  |  |

|          | 4.5                  | Data l                      | Forwarding                      | 53 |  |  |  |  |

| <b>5</b> | Dev                  | velopm                      | ent Environment                 | 55 |  |  |  |  |

|          | 5.1                  | APEX                        | K FPGA Family                   | 55 |  |  |  |  |

|          | 5.2                  | DIGII                       | LAB 20Kx240 Prototyping Board   | 60 |  |  |  |  |

|          | 5.3                  | Desigr                      | n Flow                          | 62 |  |  |  |  |

|          |                      | 5.3.1                       | VHDL Coding                     | 63 |  |  |  |  |

|          |                      | 5.3.2                       | Behavioral Simulation           | 63 |  |  |  |  |

|          |                      | 5.3.3                       | Synthesis                       | 63 |  |  |  |  |

|          |                      | 5.3.4                       | Pre-Layout Simulation           | 64 |  |  |  |  |

|          |                      | 5.3.5                       | Place and Route                 | 65 |  |  |  |  |

|          |                      | 5.3.6                       | Post-Layout Simulation          | 66 |  |  |  |  |

| 6        | $\operatorname{Res}$ | ults                        |                                 | 67 |  |  |  |  |

|          | 6.1                  | Test E                      | Environment                     | 67 |  |  |  |  |

|          | 6.2                  | 2 Processor Characteristics |                                 |    |  |  |  |  |

|          | 6.3                  | Differe                     | ent Implementations             | 73 |  |  |  |  |

|          | 6.4                  | Evalua                      | ation                           | 75 |  |  |  |  |

|          | 6.5                  | Real-7                      | Fime Capability                 | 77 |  |  |  |  |

| 7        | Con                  | nclusio                     | n                               | 79 |  |  |  |  |

| 8        | Outlook              |                             |                                 |    |  |  |  |  |

|          | 8.1                  | Task t                      | to Pipe                         | 82 |  |  |  |  |

|          |                      |                             |                                 |    |  |  |  |  |

| 8.2  | Fault Tolerant System        | . 83 |

|------|------------------------------|------|

| 8.3  | FPGA Optimizations           | . 84 |

| ААр  | pendix - The Instruction Set | 85   |

| В Ар | pendix - Assembler Code      | 88   |

### List of Figures

| 1                                                                                                                                  | Modular Construction System                                                       | 3                                                  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|

| 2                                                                                                                                  | SPEAR Architecture                                                                | 5                                                  |

| 3                                                                                                                                  | SPEAR Pipeline Architecture                                                       | 6                                                  |

| 4                                                                                                                                  | NEEDLE Architecture                                                               | 7                                                  |

| 5                                                                                                                                  | Generic Extension Module Interface                                                | 8                                                  |

| 6                                                                                                                                  | Processor Control Extension Module                                                | 10                                                 |

| 7                                                                                                                                  | Register Interface of the Processor Control Extension Module                      | 11                                                 |

| 8                                                                                                                                  | Program Download                                                                  | 13                                                 |

| 9                                                                                                                                  | Intel Pentium Pipeline Architecture                                               | 16                                                 |

| 10                                                                                                                                 | Motorola 68060 Pipeline Architecture                                              | 18                                                 |

| 11                                                                                                                                 | PowerPC 601 Pipeline Architecture                                                 | 21                                                 |

| 12                                                                                                                                 | Pentium 4 Pipeline Architecture                                                   | 23                                                 |

| 13                                                                                                                                 | Framepointer Stack                                                                | 31                                                 |

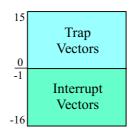

| 14                                                                                                                                 | Exception Vector Table                                                            | 32                                                 |

| 15                                                                                                                                 | Critical Path                                                                     | 34                                                 |

|                                                                                                                                    |                                                                                   |                                                    |

| 16                                                                                                                                 | SPEAR Architecture Extended by an Additional Pipeline Stage                       | 35                                                 |

| $\frac{16}{17}$                                                                                                                    | SPEAR Architecture Extended by an Additional Pipeline Stage<br>LANCE Architecture | $\frac{35}{40}$                                    |

|                                                                                                                                    |                                                                                   |                                                    |

| 17                                                                                                                                 | LANCE Architecture                                                                | 40                                                 |

| 17<br>18                                                                                                                           | LANCE Architecture                                                                | 40<br>41                                           |

| 17<br>18<br>19                                                                                                                     | LANCE Architecture                                                                | 40<br>41<br>43                                     |

| 17<br>18<br>19<br>20                                                                                                               | LANCE Architecture                                                                | 40<br>41<br>43<br>46                               |

| 17<br>18<br>19<br>20<br>21                                                                                                         | LANCE Architecture                                                                | 40<br>41<br>43<br>46<br>51                         |

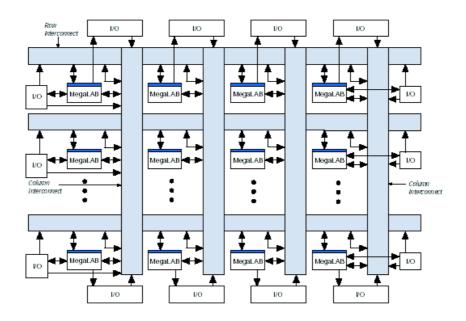

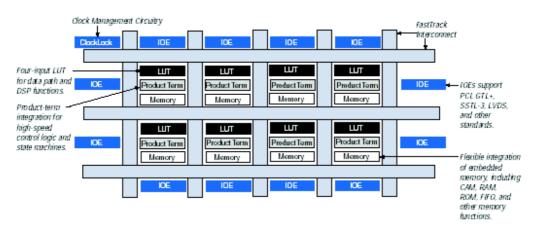

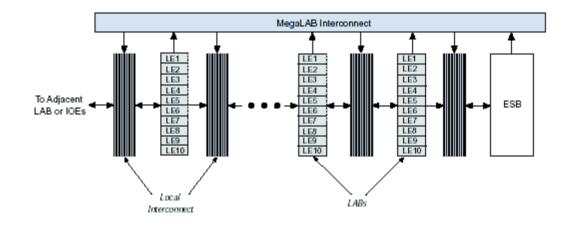

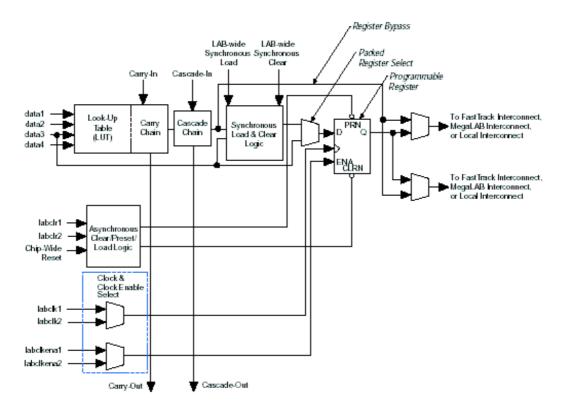

| 17<br>18<br>19<br>20<br>21<br>22                                                                                                   | LANCE Architecture                                                                | 40<br>41<br>43<br>46<br>51<br>56                   |

| <ol> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> </ol>                                     | LANCE Architecture                                                                | 40<br>41<br>43<br>46<br>51<br>56<br>57             |

| <ol> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> </ol>                         | LANCE Architecture                                                                | 40<br>41<br>43<br>46<br>51<br>56<br>57<br>58       |

| <ol> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>25</li> </ol>             | LANCE Architecture                                                                | 40<br>41<br>43<br>46<br>51<br>56<br>57<br>58<br>59 |

| <ol> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>25</li> <li>26</li> </ol> | LANCE Architecture                                                                | 40<br>41<br>43<br>51<br>56<br>57<br>58<br>59<br>60 |

| 30 | ALTERA Quartus                                              | 66 |

|----|-------------------------------------------------------------|----|

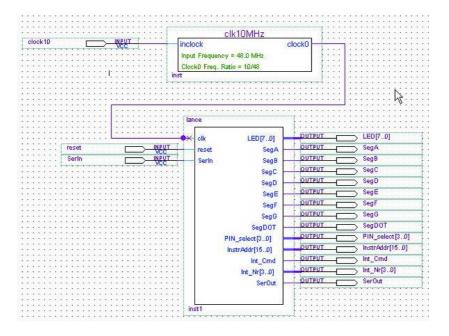

| 31 | Test Environment                                            | 68 |

| 32 | The LANCE Processor                                         | 70 |

| 33 | Quartus - Timing Report                                     | 72 |

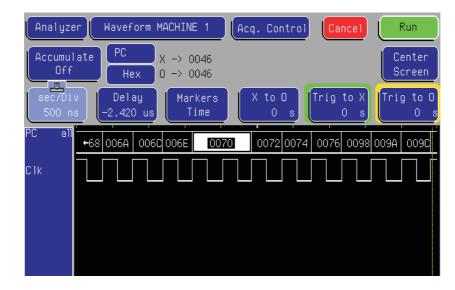

| 34 | Logic Analyzer Screenshot - Instructions out of the IRAM $$ | 75 |

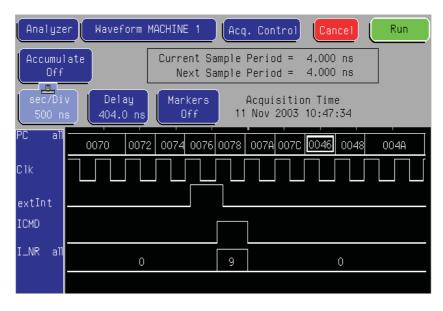

| 35 | Logic Analyzer Screenshot - Interrupt Response              | 77 |

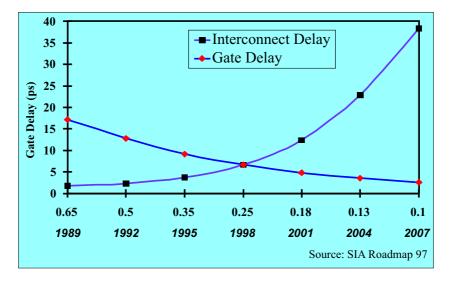

| 36 | Interconnect Delay                                          | 80 |

| 37 | Boot-ROM Assembler Code                                     | 88 |

### List of Tables

| 1 | Comparison of the NEEDLE, SPEAR and LANCE Processor |    |

|---|-----------------------------------------------------|----|

|   | Characteristics                                     | 71 |

| 2 | Different LANCE Implementations                     | 73 |

#### 1 Introduction

Embedded systems are used in a wide range of devices in everyday life such as refrigerators, microwave ovens, TVs, VCRs, DVD-players, printers, cameras, automotive control equipment (e.g. climate control, ABS, engine control, etc.), aircrafts and many more. There are many definitions of embedded systems, but all of them can be combined into a single concept: hardware and software, which are expected to function without human intervention and together form a component of some larger system [11].

#### 1.1 Motivation

Why develop another 16-bit microcontroller? The ongoing miniaturization progress of electronic and electro-mechanic components will provide even more possible application areas for embedded computer systems in the future. An example application which is becoming more and more important these days are embedded networks. Usually embedded networks comprise a lot of different sensors to receive information from the environment, a processing unit to treat this information and a certain number of actuators to interact with the environment. To simplify the system and to reduce costs, sensors and actuators are not connected directly to the processing unit, but networked by a so-called field-bus [14]. This implies that each sensor/actuator has to be equipped with a network interface that implements the communication protocol. Such an interface comprises a microcontroller and a communication unit. An additional benefit of this local intelligence is that the microcontroller can also be used to preprocess the data in order to reduce the traffic on the field-bus. Furthermore, failure detection mechanisms and recovery strategies can be implemented in each network node to improve safety and reliability of the entire network. Due to the fact that such networks contain various nodes with different requirements in terms of processing speed, memory size and interfaces, different standard microcon-

trollers have to be used within the same network. This implies that the communication protocol, which is the same for all nodes [18], has to be implemented and tested for each microcontroller separately. This makes the development process costly and error-prone. Therefore it would be desirable to use the same microcontroller for all network nodes including the processing unit, but this would result in a waste of resources (silicon area, power consumption, etc.). Hence an ideal development system for embedded networks should provide a microcontroller that features modularity and is scalable in terms of computational power and functionality. Another problem arises if an embedded system has to provide real-time functionality. In real-time computer systems correctness of the system behavior depends not only on the logical results of the computations, but also on the instant at which these results are produced [24], therefore response and delay time of the embedded system have to reside in guaranteed boundaries. Common off-the-shelf processors, which are optimized for average performance, make it difficult to calculate exact worst-case behavior of executed program code. Worst-case assumptions (only cache misses, hazards, mispredicted branches, etc.) made for such systems lead to unrealistic bad performance.

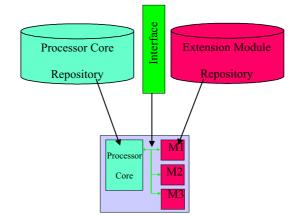

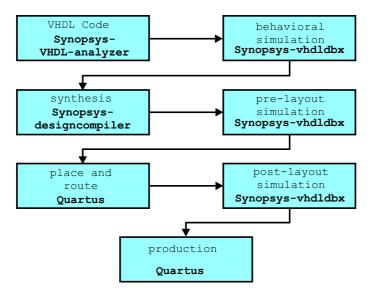

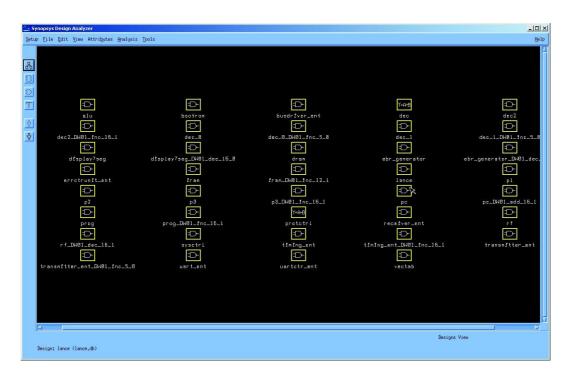

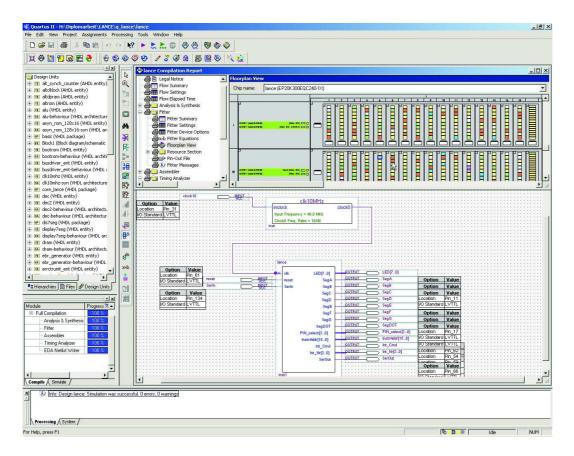

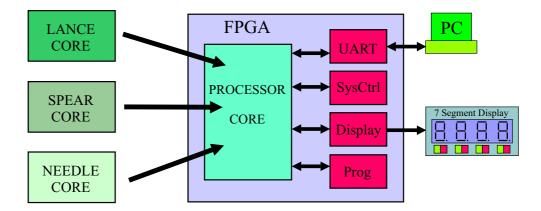

Based on the requirements mentioned above, a modular construction system for real-time applications [8][9] (shown in Figure 1) has been developed at our institute. All components of the modular construction system have been implemented as VHDL designs [3] and tested on an APEX-FPGA development board [1][13]. Scalability of the microcontroller with respect to computational power is achieved by providing different processor core implementations of the same instruction set. Extension modules can be used to customize the various processor cores to application-specific requirements (extension modules and their interface are shown in section 1.3). A central role in this concept plays the standardized interface between processor core and extension modules, which ensures that all extension modules can be attached to any of the available cores. Three different code-compatible real-time processors are provided, while the design and implementation of the LANCE processor is the objective of this diploma thesis.

Figure 1: Modular Construction System

The LANCE design is intended to provide the modular construction system with more computational power than the two already existing processor cores NEEDLE and SPEAR are able to offer (NEEDLE and SPEAR are described in detail in section 1.2). The basic idea behind the LANCE design is to create a processor with twice as much processing power as SPEAR, without losing code compatibility and real-time capability. Performance gain shall not only be achieved through higher clock rates, but also by extending the SPEAR processor to a superscalar design. Independent from clock rate, the superscalar approach will lead to a major improvement of the instruction execution rate. The effects of both, increased clock rate and superscalar design, should provide LANCE with significantly higher overall performance than the SPEAR processor core.

#### 1.2 Processor Cores

The two already existing, fully code-compatible 16-bit real-time processor cores SPEAR and NEEDLE will be presented in detail in this section.

#### 1.2.1 SPEAR

SPEAR stands for "Scalable Processor for Embedded Applications in Realtime environments" [6][7]. The SPEAR design has been developed to provide moderate computational power and represents a RISC architecture which executes instructions through a three-stage-deep pipeline. The instruction set comprises 80 instructions which are described in detail in section 3.1 and appendix A. The main components of the processor are:

- Extended Register File

- Exception Vector Table

- Data Memory

- Instruction Cache

- Extension Modules

- ALU

Instruction and data memory are both 4 kB in size, but it is possible to add up to 128 kB of external instruction memory and 127 kB of additional data memory. The uppermost 1 kB of the data memory is reserved for memory mapping of the extension modules. As a result of the memory mapping, no dedicated instructions for extension module access are needed (common load/store instructions are used) which satisfies the RISC [28] philosophy of our approached design. The register file holds 32 registers which are split into 26 general purpose and 6 special function registers, three of which are used to construct stacks efficiently (see frame pointer operations in section 3.2.2) and the remaining three are used to save the return address in case of an interrupt or subroutine call. SPEAR supports 32 exceptions, 16 of which are hardware exceptions (=interrupts) and 16 can be activated by software (=trap). The entries of the exception vector table hold the corresponding jump addresses to the interrupt/exception service routines for each interrupt or exception. The SPEAR ALU performs all provided arithmetic and logical functions, but is also responsible for offset calculation on jumps. Furthermore, the ALU is used to pass through data out of the exception vector table or register file. Figure 2 shows a block diagram of the SPEAR processor.

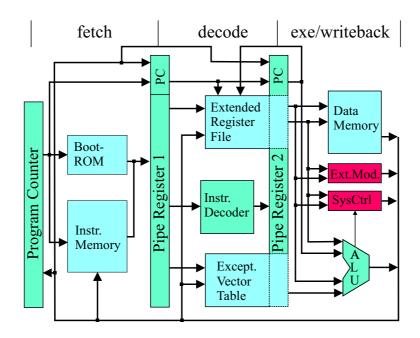

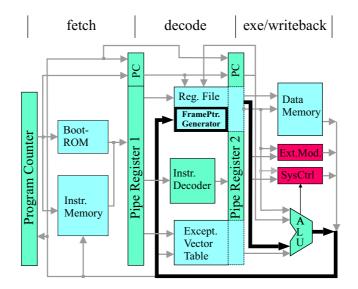

Figure 2: SPEAR Architecture

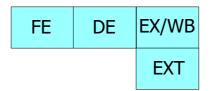

The SPEAR Pipeline shown in Figure 3 is structured into an: instruction fetch (FE), instruction decode (DE) and combined execute/writeback (EX/WB) stage. Inside the fetch cycle, instruction memory is accessed and one instruction opcode is passed to the decode stage. During the decode cycle the control signals for the memories and the ALU are generated, furthermore the instruction's operands are retrieved from the register file. The execute/writeback stage performs the instruction's intended operation and writes the resulting value to the appropriate memory location. If an extension module access (EXT) happens, it is also executed during the EX/WB cycle.

Figure 3: SPEAR Pipeline Architecture

#### 1.2.2 NEEDLE

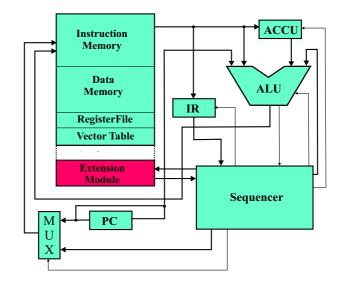

The NEEDLE processor core [12] is fully code-compatible to SPEAR and is intended to pay attention to a compact design, therefore it is primarily optimized to reduce silicon area. NEEDLE uses the same extension module interface as SPEAR does, and an identical Processor Control Unit (which is presented in chapter 1.3). NEEDLE has no pipeline and requires several clock cycles per instruction. To minimize chip area, instruction- and data memory, the register file and the exception vector table have been mapped into the same physical memory. This way only one address- and data bus is necessary to access all memory elements which leads to reduced silicon area. The physical memory block is 4 kB in size, of which 2 kB are used as instruction memory and 1.92 kB as data memory. The remainder is allocated to the register file and the exception vector table. Additionally the processor core comprises only an ALU, a multiplexor, three registers (program counter, instruction register, accumulator register) and a sequencer. The block diagram of NEEDLE is shown in Figure 4.

The instruction register (IR) is needed to store the currently processed instruction. The accumulator register (ACCU) is used to store one operand for the ALU and the program counter (PC) contains the address of the next instruction. The most complex part of NEEDLE is the sequencer which has been implemented as eight-stage state machine. The sequencer's task is to distinguish between the 80 different instructions and generate the appropriate control signals for the ALU and the memory. Instructions are executed within three phases, the fetch, the decode and the execute phase. As the write-back to the memory runs parallel to the fetch phase, some of the instructions only need two instead of three clock cycles to be processed. The NEEDLE processor supports 32 exceptions as well, 16 of which are hardware exceptions (= interrupts) and 16 can be activated by software (= traps).

Figure 4: NEEDLE Architecture

#### **1.3** Extension Modules

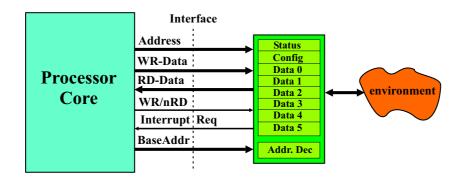

As mentioned in chapter 1.1, extension modules are used to fit the processor for different applications. For reason of simplicity and lucidity, the integration of and the access to extension modules should work the same way for all of them. Thus a generic interface for all extension modules has been defined [16]. All extension modules are mapped to a unique location at the upper most region of the data memory. The modules are accessed via eight registers using simple load and store instructions, since from the processors point of view the extension modules are simply memory locations. A block diagram of the generic extension module interface is shown in Figure 5. The first two registers are the module's *status* and *confiq* registers, of which the status register is **read only**. The lower 8 bit of these registers are defined within the interface specification, hence they are identical for all extension modules, whereas the upper 8 bit are module specific. The status register tells the processor the current state of the extension module. Among other things it shows if an interrupt has been activated, an error has occurred, or the extension module is still busy. The *config* register is used to specify parameters for the module's operations. Next to a softreset bit, which is used to deactivate the extension module, an interrupt acknowledge bit exists to reset the interrupt status. The remaining six registers Data 0 - Data 5 are allocated for module specific issues.

Figure 5: Generic Extension Module Interface

Dependening on their functionality there are three different types of extension modules:

- *Processor Control Modules*: These modules have direct influence on the processor core's behavior. An example for such a module is the "protection control module", which provides the processor core with the possibility to restrict memory access to specific locations. This is necessary if the processor runs an operating system.

- *Function Modules* are used to provide the processor core with hardware implementations of different functions like integer multiplication, floating point operations or even complex algorithms.

- *I/O Modules*: Since the processor core has no direct interface to the environment, all interaction is aided by I/O extension modules. Examples for I/O extension modules are: RS-232, USB, 7-segment display, VGA, PS/2, etc.

#### 1.3.1 Processor Control Unit

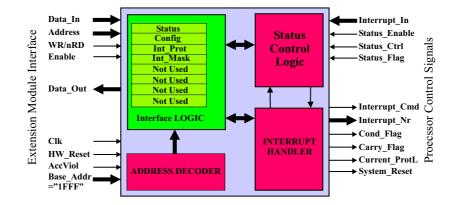

The processor control unit plays a major role among the extension modules, because it contains the processor status register as well as the interrupt handler. As the status register and the interrupt handler are vital components of the processor core, the processor control unit can be accounted as proper component of the processor. The status register and the interrupt handler have been moved to an extension module due to compatibility issues. This way all processor cores use the same processor control unit and therefore it is guaranteed that the status register and the interrupt mechanism act exactly the same way in all processor cores. Since the processor would not work without the processor control unit, it is always mapped to the uppermost address of the data memory. As depicted in Figure 6, the processor control unit is subdivided into four parts:

Figure 6: Processor Control Extension Module

- Generic Interface: The registers of the interface hold the status and config register as well as the interrupt protocol and interrupt mask register.

- Status Control Logic: The status control logic provides the processor with correct status values and is responsible for updating and saving the status register.

- Address Decoder: Each extension module is mapped to a unique memory location within the data memory. The address decoder recognizes if the modules is accessed and activates it.

- Interrupt Handler: The interrupt handler is responsible for synchronizing and logging incoming interrupts and provides the processor with the correct interrupt number.

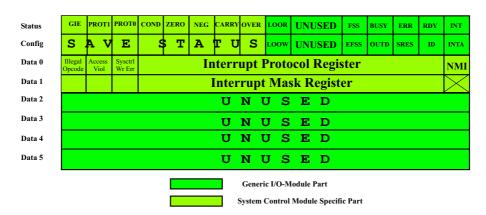

Figure 7 depicts the register interface of the *processor control module*, the status register and essential parts of the config register will be illustrated below. The first two registers of the generic interface are the status and the config register (as described in the previous section). The module specific part of the status register holds the processor status register, and can only be

read by the processor. Besides common status flags (zero-, carry-, overflowand negative flag) the processor status register holds, additional flags:

Figure 7: Register Interface of the Processor Control Extension Module

- **GIE**: If the global interrupt enable (GIE) is set (='1') all interrupts are accepted by the processor control unit; if GIE is deactivated the interrupts are only logged but not executed (with the exception of the non maskable interrupt NMI which is always executed and mapped to bit 0).

- **PROT1/PROT0**: Protection bits 1 / 0 show the protection level of the current processor task. "11" for zero protection, "10" for low protection, "01" for high protection and "00" for the supervisor mode (will be ignored if the protection control module has not been activated).

- **COND**: The condition flag is used to determine if conditional instructions will be executed or not. The cond flag is only set or deleted by compare or bit-test instructions.

- **ZERO**: The zero flag indicates that the result of the last ALU operation was zero.

- **NEG**: The negative flag is set if the result of the ALU operation is negative.

- CARRY: The carry bit is used for arithmetic instructions.

- **OVER**: The overflow bit indicates an overflow of a calculation.

The module specific part of the config register is used to save the processor status if an interrupt/exception occurs.

The interrupt protocol register is responsible for the logging of all incoming interrupts. All interrupts that are masked within the interrupt mask register (bit set at the corresponding position) will be logged, but the interrupt service routine will not be executed.

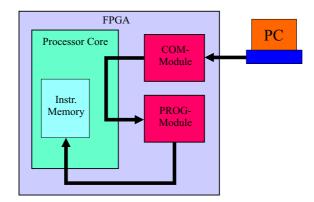

#### 1.4 Program Download

To provide the user of the microprocessor with a versatile programming interface between PC and microprocessor the download hardware has been split into two parts, the communications unit (COM-Module) and the programmer module (PROG-Module) which includes a *Boot-ROM* for startup. This approach has the advantage that it is quite simple to change the download medium. Only the communications module and the corresponding initialization program code (situated inside the programmer's *Boot-ROM*) have to be replaced. The communications unit transports the downloaded program code into the processor, but the actual programming into the instruction memory is done by the programmer module. Figure 8 depicts dataflow during the programming procedure.

The programmer module's *Boot-ROM* is used to set up the communication module and initiates the data transfer from the communication unit to the programmer and the instruction memory. After the download is finished the programmer module switches from the *Boot-ROM* to the instruction memory and the processor starts to execute instructions out of the instruction memory.

Figure 8: Program Download

#### 1.5 Chapter Organization and Overview

Chapter two gives an overview on superscalar designs considering three different past and one state of the art processor designs.

In chapter three a detailed specification of the microcontroller is given, furthermore the instruction set is described in detail. This chapter ends with a survey of code restrictions that may arise due to the superscalar approach.

Chapter four treats the design of LANCE and gives deep insights into the design decisions on each component of the microprocessor.

Chapter five focuses on the hardware design flow and the development environment.

Chapter six presents the test environment and the results, and gives a comparison of NEEDLE, SPEAR and LANCE.

Chapter seven covers the conclusion of this diploma thesis.

In Chapter eight an outlook on topics for further research is given.

### 2 Superscalar Designs - State of the Art

In this chapter different superscalar designs are introduced to give an overview of how superscalar processors can be designed. The term "superscalar" is used for architectures which are able to execute two or more instructions in parallel. The Intel Pentium, Motorola 68060 and PowerPC 601 were chosen due to the fact that all three designs are the first superscalar approach in their product families and therefore less complex than currently available processors. Furthermore, a short overview on the Intel Pentium 4 architecture will be given to show one state of the art superscalar design.

All the presented superscalar designs are commercial off-the-shelf processors for use in workstations and personal computers. They are all optimized for best performance using standard application software. This optimization concept led to several architectural constructs like caches, dynamic branch prediction or out-of-order execution which improve average performance, but make it very difficult (in some cases impossible) to calculate exact WCET (Worst Case Execution Time) boundaries for executed program code [38].

#### 2.1 Intel Pentium

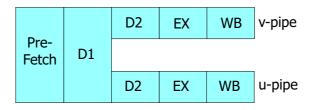

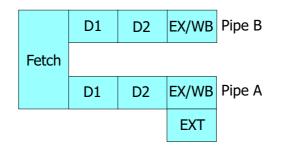

The first superscalar member of the Intel processor family for Personal Computers is the Intel Pentium [19][20]. The processor core consists of two parallel pipelines, the u-pipe and the v-pipe, as shown in Figure 9. The upipe handles any kind of instruction, whereas the v-pipe only supports simple integer and simple floating-point instructions. Each pipeline is able to execute frequently used instructions in a single clock cycle. Together these two pipelines can issue two integer instructions or one complex floating-point instruction in one clock cycle. The pipes are organized as five-stage-deep pipelines. The pipeline stages are as follows:

• PF Prefetch

- D1 Instruction Decode

- D2 Address Generate

- EX Execute ALU and Cache Access

- WB Writeback

Figure 9: Intel Pentium Pipeline Architecture

The first pipeline stage is the Prefetch (PF) stage in which instructions are prefetched from the on-chip instruction cache. Because the processor has separate caches for data and instructions (Harvard-Architecture), prefetches do not conflict with data references. In the PF stage two independent pairs of prefetch buffers work in conjunction with the branch target buffer (BTB). One of these two buffers prefetches instructions sequentially while the other retrieves instructions according to the BTB predictions.

The pipeline stage after the PF stage is Decode1 (D1), in which two parallel decoders issue the next two sequential instructions. The decoders also determine whether the instructions can be paired (executed in parallel) or not. When instructions are paired, the instruction issued to the v-pipe is always the next sequential instruction after the one issued to the u-pipe. Instructions with data dependencies or complex instructions (which require both pipelines) are not allowed to be paired. Jumps can only be paired if they are issued to the v-pipe. More details on instruction pairing is provided in [20]. The D1 stage is followed by the Decode2 (D2) in which addresses of memory resident operands are calculated.

In the Pentium processor the Execute (EX) stage of the pipeline is used for both ALU operations and data cache access. In EX, all u-pipe and v-pipe instructions are also verified for correct branch prediction. If the BTB has mispredicted a branch, both pipelines have to be flushed and a new instruction stream will be fetched.

The final pipeline stage is Writeback (WB), in which the instructions are enabled to modify the processor state and complete execution.

During their progression through the pipeline, instructions may be stalled due to certain conditions. The u-pipe and the v-pipe instructions enter and leave D1 and D2 at the same time. If there is a stall in one pipeline, the instruction in the other pipeline is also stalled at the same pipeline stage. No instructions are allowed to enter EX stage of either pipeline until the instructions in both pipelines have advanced to WB. This concept of instruction issuing is know as *in-order execution*.

#### 2.2 Motorola 68060

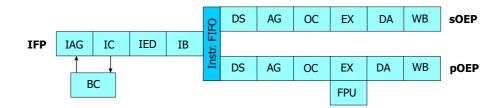

The Motorola 68060 [5][26][4] is the forth generation microprocessor of the M68000 Family and it is code compatible with previous family members. The 68060 employs a deep pipeline, dual-issue superscalar execution, a branch cache, a floating point unit and 8 kB each of on-chip instruction and data cache.

As shown in Figure 10, the 68060 consists of two distinctive parts: a fourstage Instruction Fetch Pipeline (IFP) for prefetching instructions and loading them into the FIFO instruction buffer, and dual four-stage operand execution pipelines (OEPs) which perform the actual instruction execution. The four stages of the IFP are:

- IAG Instruction Address Generation

- IC Instruction Fetch Cycle

- IED Instruction Early Decode

- IB Instruction Buffer

Figure 10: Motorola 68060 Pipeline Architecture

The first pipeline stage in the IFP is the Instruction Address Generation (IAG) which calculates the next prefetch address. The Branch Cache (BC), which improves prefetch efficiency by detecting changes in the sequential flow of the fetch stream based on past execution history, is also accessed in this pipeline stage.

After the IAG sends the correct address to the instruction cache, the Instruction Fetch Cycle (IC) stage performs the cache lookup and fetches the bit pattern of the next instruction.

The Instruction Early Decode (IED) stage implements a lookup table function to provide the OEPs with decode information concerning instruction resource requirements along with controlling information for the superscalar dispatch algorithm. The IED stage also converts the variable length instructions with multiple formats into a fixed-length extended operation word. At the end of the IFP the prefetched and converted instruction along with the extended operation word are issued to the Instruction Buffer (IB).

In the IB stage the instructions are read from the FIFO and loaded into the dual OEPs.

The Operation Execution Pipelines, known as the primary OEP (pOEP) and the secondary OEP (sOEP), are partitioned into a four-stage-deep pipeline. The pOEP supports all instructions, whereas the sOEP only executes a subset of the instruction set. The four OEP stages are:

- DS Decode and Select

- AG operand Address Generation

- OC Operand Cycle

- EX Execute cycle

For instructions writing data to memory, there are two additional pipeline stages:

- DA Data Available

- ST Store

The Decode and Select (DS) stage determines the next state for the entire operand pipeline and also selects the components required for operand address calculation. If multiple instructions can issue into the AG stage, the first and the second instruction move into the respective AG stages. If only a single instruction can issue (because of architectural restrictions), the first instruction issues into pOEP and the second and third instruction will be used for pairing in the next cycle, which leads to a sliding two-instructionwindow to examine possible pairs of instructions.

In the operand Address Generation (AG) stage each pipeline calculates the effective address for instructions requiring data from memory.

The Operand Cycle fetches register and memory operands.

Finally the Execute (EX) stage performs the desired instruction executions in the integer and floating point units including condition flag updating. The 68060 performs condition code checking inside the EX stage, which leads to a penalty of seven clock cycles if a branch has been mispredicted. To minimize this effect the microprocessor employs a sophisticated branch cache.

The two additional stages Data Available (DA) and Store (ST) are needed to complete operand store operations.

The Motorola 68060 issues all instructions according the to *in-order execution* concept. One special feature, implemented for solving data hazards, is register renaming. This renaming optimization, performed in the DS stage, substitutes internal pipeline register contents for general register contents. For more details, see [4][37].

#### 2.3 PowerPC 601

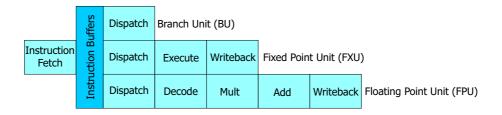

The PowerPC 601 [35][25] combines a RISC architecture with a superscalar machine organization. The 601 contains a 32kB cache (combined instructionand data cache) and is capable of dispatching, executing and completing up to three instructions per clock cycle. As shown in the block diagram in Figure 11, the 601 consists of three different execution pipelines, which are:

- BU Branch Unit

- FXU Fixed Point Unit

- FPU Floating Point Unit

Figure 11: PowerPC 601 Pipeline Architecture

The Branch Unit (BU) uses a static branch prediction algorithm to predict the direction of unresolved branches and executes them. This prediction algorithm simply predicts a branch as *taken* if the displacement of the target address is negative, and as *not taken* if it is positive.

The Fixed Point Unit (FXU) serves as master pipeline and is used for all integer ALU operations. It also handles all processor Load and Store instructions (including the Floating Point Loads and Stores).

The Floating Point Unit (FPU) pipeline contains six stages and is able to execute all single precision instructions fully pipelined, only double precision multiplication and division are *double pumped* through the Mult and Add stages.

The different pipeline stages will now be described in more detail.

Inside the Fetch pipeline stage the unified cache is accessed, with instructions having lower priority than data. To provide the pipelines with a continuous stream of instructions, up to eight instructions are fetched into the instruction buffers in a single cycle, even though the absolute maximum processing rate is three instructions per clock cycle.

Instructions are dispatched within the Dispatch stage to the FXU and FPU. The Branch Unit (BU) also decodes, predicts and executes branches inside the Dispatch stage.

The Decode stage is responsible for decoding instructions, furthermore all source registers are read. Instructions going to the FXU are dispatched and decoded in this pipeline stage.

All fixed-point operations are executed inside the Execute stage, moreover in case of a load/store instruction the address processing and cache lookup take place.

The Mult pipe stage is responsible for floating point multiplications and hands its results over to the Add stage where the final floating point result is calculated.

The Writeback pipeline stage performs the register update, for the FPU pipeline it also takes care of result rounding and normalization.

Instructions may be dispatched out of order which makes it possible to get instructions out of the instruction buffers even while one pipeline is blocked. To keep track of the program order, a unique tagging and counting mechanism has been implemented. Although *out-of-order dispatch* is more complex to implement, it also allows to minimize potential dispatch stalls. Furthermore, the PowerPC 601 provides register renaming [37] (only FXU) and full data forwarding between pipeline stages to resolve as many data hazards as possible. If there are still any hazards left, they are automatically interlocked by hardware (stall cycles are inserted).

#### 2.4 Intel Pentium 4

Intel's current flagship for desktop computers is the Intel Pentium 4 Processor. The Pentium 4 introduces a few new terms like the *NetBurst Micro-Architecture*, *Rapid Execution Engine*, *Hyper-Pipelined Technology* and *Hyper-Threading Technology*[15][23].

The *Hyper-Pipelined Technology* refers to the 20-stage pipeline of the Net-Burst micro-architecture (shown in Figure 12). This pipeline is twice as long as its predecessor on the P6, and therefore provides Intel with the possibility of reaching much higher clock rates (if less work has to be done in each clock cycle, the cycle time can be shortened).

#### 10 12 13 16 18 19 6 11 14 15 Sch Sch Sch Disp Disp TC Nxt IP RF RF Que Fγ Flas Br Ck

Figure 12: Pentium 4 Pipeline Architecture

The NetBurst instruction execution is broken down into three main parts: an *in-order* issue front end, an *out-of-order* superscalar execution core and an *in-order* retirement. The front end feeds a continuous stream of up to three micro-operations to the execution engine. The decode unit can decode one IA-32 [22] instruction per clock cycle and stores the resulting  $\mu$ ops to the Execution Trace Cache. The trace cache can hold up to 12k  $\mu$ ops, which for most of the time preserves the processor from the need of instruction decoding. The execution engine can have up to 126 instructions "in-flight" at once, 48 of which may be loads and 24 stores. The Pentium 4 core can dispatch up to 6  $\mu$ ops per cycle and uses register renaming to resolve as many data hazards as possible. Retirement in NetBurst reorders the instructions executed in an out-of-order manner to ensure that the system state is left as the programmer intended.

Rapid Execution Engine refers to the integer execution units of the Pentium 4. These low latency integer ALUs are able to perform fully dependent integer ALU operations at twice the main clock rate. Two instructions are issued by calculating one during the first half of the clock cycle and the second during the second half.

Hyper-Threading Technology (HT) [21] stands for the ability of a processor to execute more than one thread at a time and to appear to the Operating System as two logical processors. HT has been developed to increase usual processor utilization (about 35%). By sending two threads into the processor at the same time, execution units that would otherwise have been idle can be used by the second thread, which can increase processor utilization by up to 50%. The trace cache is shared between the two threads, furthermore the trace cache and the retirement logic alternate between the threads and therefore ensure that both logical processors can progress on program execution.

In the case of a mispredicted branch the 20-stage-deep pipeline leads to average costs of 20 cycles, which makes branch prediction the single most important unit inside the Pentium 4 architecture (and therefore more advanced than in any other intel processor).

The NetBurst processor architecture was designed to provide a platform which desktop processors for the next few years will be based on. Intel claims that this 20-stage pipeline will allow them to reach clock frequencies of 10 GHz in the future without changing the micro-architecture.

### 3 Specification

This chapter gives a detailed specification of all requirements and constraints regarding the design of LANCE. The basic idea behind LANCE is to design a processor with twice as much processing power as SPEAR. A major requirement was to maintain code compatibility to SPEAR and NEEDLE as far as possible. This ensures that program code developed for one processor can be used without any modification on another one, which supports rapid prototyping concepts. From there, it is also necessary to implement exactly the same extension module interface.

Top priority issue during the design of LANCE has been to maintain realtime capability, therefore following requirements have to be met:

- predictable program execution time at an accuracy of one clock cycle to support WCET analysis

- deterministic interrupt response time

- support of priority levels to ensure immediate response on operating system tasks

The performance gain which is intended to be achieved should result out of two approaches, in the first place by increasing the clock rate due to architectural optimizations. The second approach will extend the SPEAR processor to a dual-issue superscalar design. The effects of both increased clock rate and superscalar design should provide the LANCE processor with significantly higher overall performance than SPEAR. Due to the fact that the generic extension module interface only supports one extension module access each clock cycle, special architectural mechanisms have to be integrated to ensure fully predictable timing behavior (extension module access integration is shown in detail in section 4.4.7).

# 3.1 Instruction Set

Following a RISC architecture concept, the instruction set of NEEDLE, SPEAR and LANCE comprises 80 different one-word instructions. The instructions can be separated into five distinctive groups:

- two-register-instructions

- one-register-instructions

- instructions using one constant

- register-constant-instructions

- instructions without arguments

**two-register-instructions**: these instructions have two register addresses as arguments and can be further subdivided into:

- load/store instructions where the first register is the operation's destination/source register and the second register holds the memory address that has to be accessed, for example LDW r1, r2 : mem(r2) - >r1

- arithmetic operations like ADD r1, r2; OR r1, r2; AND r1, r2 where the first and second register hold instruction source values, furthermore the first register serves as destination register.

**one-register-instructions**: only operate on the contents of one register. The result of the operation can either be written back to the same register e.g. *NOT r1; SL r1; RR r1; SRA r1;* or may be used as branch target e.g. *JMP r1; JSRY r1*.

## instructions using one constant:

JMPI offset; (jump immediate) performs a near jump to the instruction address calculated from the program counter and the given offset (PC + offset). The offset is a 10-bit signed integer and therefore provides a jump range of -512 and +511. • TRAP n4; activates one of 16 possible software interrupts (trap) and saves the return address to register 31. TRAP 5 for example leads to a jump to the address stored on position 5 inside the exception vector table (further details on interrupts, traps and the exception vector table are provided in section 3.2.5).

**register-constant-instructions**: have one register and one constant as parameters. These instructions can be subdivided into several instruction subclasses:

- LDL r1, n8; (load low) is used to initialize the lower 8 bit of register r1 with the binary representation of the constant n8. (the instruction performs sign-extension of two's complement numbers, this means that the constants MSB is copied to bit 9 to 15 of r1)

- LDH r1, n8; (load high) In contrast to LDL this instruction stores the 8-bit constant n8 to bit 9 to 15 of register r1 without affecting the lower 8 bit.

- *CMPI\_EQ r1, n5* compares the register contents of r1 with the signed integer constant n5, if r1 and n5 are equal the condition flag is set.

- ADDI r1, n5 adds register r1 and the signed integer constant n5 and writes the result back to register r1.

- LDOFX, LDOFY, LDOFZ, STOFX, STOFY, STOFZ r1, n5; loadwith-offset and store-with-offset instructions are dedicated framepointer operations. The registers r26 (framepointer X) to r28 (framepointer Z) are coupled with the framepointer load and store instructions. For example, STOFY r11, 7 stores the content of r11 at the memory location which is given by the sum of r27 and the signed integer value 7. (more details on framepointer operations are provided in section 3.2.2)

- STVEC r1, n5; LDVEC r1, n5; are required to store and read back the exception vector table entries. Register r1 holds the jump address for the exception/interrupt service routine and the 4-bit signed integer constant specifies the position load/store position at the vector table

- BTEST r1, n4; BSET r1, n4; BCLR r1, n4; the 4-bit unsigned integer constant specifies the bit position of register r1 on which a bit set, clear or test is performed. E.g. BTEST r12, 7; tests bit number 7 of register 12, if it is set to '1' the condition flag will be set.

instructions without argument: *NOP* (no operation), *ILLOP* (illegal opcode), *RTSX*, *RTSY* (return from subroutine) the return address is stored in register r29 respectively register r30 and *RETI* (return from interrupt) the return address is stored in register r31.

## **3.2** Instruction Set Features

Knowing the worst-case execution time (WCET) of programs is crucial for real-time systems. Safe WCET bounds for all time-critical tasks of a realtime system have to be established to verify the correct timing behavior of the whole real-time computer system. Analyzing execution paths as performed by static WCET analysis is supported by the instruction set due to constant instruction execution time of any single instruction. Furthermore, the instruction set supports the ONE-PATH programming paradigm [30] by providing constant-time conditional instructions like  $MOV_-CF$  (move if condition is false). Using those conditional instructions there is the possibility to implement logical branches as strictly sequential program code.

#### 3.2.1 Conditional Instructions

As mentioned above, constant-time conditional instructions are needed to support real-time system design, especially the ONE-PATH programming paradigm (32 out of 80 instructions are conditional). Conditional instructions like  $MOV_CT \ r1, \ r2$  evaluate the processors condition flag (set by a previous compare or bit-test instruction) to determine if the operation has to be executed or if a NOP is going to be executed. Inserting a NOP if the condition is false is necessary to provide data-independent constant execution time. The condition flag, which is located inside the processor status register, remains in its current state until the next compare or bit-test operation alters it. This approach simplifies execution of program blocks like:

```

if condition then evaluate condition

expression 1;         expression1_CT;

expression 2;         expression2_CT;

else         expression3_CF;

expression 3;         end;

end if;

```

The implementation on the left side executes either *expression 1* and *expres*sion 2 or expression 3, whereas the implementation on the right side which uses conditional instructions in any case performs all three expressions. Executing all instructions of the *if-then-else* block provides constant execution time regardless of the condition and does not necessarily lead to loss of performance. If there is a small amount of instructions within the *if-then-else* block, the implementation with conditional instructions will lead to equal or even better performance than the common implementation (left side). The common *if-then-else* block implementation typically consists of at least two jump instructions. One jump may take place after the condition has been evaluated and leads to expression 3 (else-part), the other jump is performed after expression 2 is executed and leads to the end of the *if-then-else* block. Each jump instruction implicates significant performance loss within pipelined processors, since the content of both pipelines has to be flushed (if the processor implements jump-prediction the amount of pipeline flushes can be minimized at the cost of more complex WCET analysis).

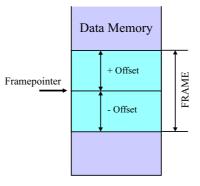

#### **3.2.2** Framepointer Operations

Framepointer operations are used for efficiently building stacks inside the data memory (shown in Figure 13). In contrast to common stacks, data can be written to or read from any memory location within the frame (there is no need for emptying the whole stack to get data that has been pushed at the beginning). Framepointer operations are coupled with the registers r26, r27 and r28 (framepointer register X, Y and Z), hence three independent stacks can be built. To use framepointer operations, first of all a framepointer (e.g. framepointer X which corresponds to register r26) has to be set to the desired memory location to provide a base address for the stack. After that, a simple summation of the framepointer and the 5-bit offset performed by *LDOFX*, *LDOFY*, *LDOFZ* ("load with offset") or *STOFX*, *STOFY*, *STOFZ* ("store with offset") instructions lead to the intended stack operation.

Figure 13: Framepointer Stack

## 3.2.3 Subroutine Calls

Two independent subroutine calls are supported by the instruction set. In case of a subroutine call the return address (address of the succeeding instruction of the subroutine call) is automatically stored to register r29 (subroutine X) or register r30 (subroutine Y) respectively, hence a subroutine nesting depth of two levels is provided. If further subroutine nesting is required, the programmer is responsible for saving and restoring the correct return address.

## 3.2.4 Immediate Instructions

There are three different types of immediate instructions to aid compact program code design:

- *CMPI\_EQ r1, n5;* (compare immediate equal) The contents of register r1 and the sign extended 5-bit constant n5 are examined. If they are equal, the condition flag (inside the processor status register) is set.

- ADDI r1, n5; (add immediate) adds up the contents of register r1 and the signed extended 5-bit constant n5 (the carry flag will be ignored by this instruction).

• *JMPI offset;* (jump immediate offset) performs a near jump to the target address given by the signed 10-bit offset value. The signed 10-bit offset results in a jump range of -512 and +511 instructions.

#### 3.2.5 Exceptions

Exceptions can be subdivided into two groups:

- 1. interrupts, which are generated by hardware

- 2. traps, which are activated by software via the TRAP instruction.

Apart from the way they are activated, interrupts and traps show the same behavior: the program status register is saved and the program counter is copied to register r31 to ensure that the actual processor state can be recovered after the service routine is finished.

Typically the exception vector table (shown in Figure 14) is initialized with the service routine address for each exception during program start-up using the STVEC instruction. If an interrupt or trap occurs, a jump to the corresponding service routine takes place.

Figure 14: Exception Vector Table

## **3.3** Code Restrictions

The superscalar approach implicates various considerable problems regarding code compatibility due to possible data dependencies, for example:

instr.A: ADD r1, r2; instr.B: ADD r4, r1;

If these two instructions are going to be executed in the same clock cycle, forwarding of register r1 (the result of instruction A) to instruction B has to take place inside the ALU. Of course not only the ALU, but also the data memory and other components of the processor core require data forwarding. Obviously a lot of forwarding paths between the two instruction execution pipelines will be necessary to resolve all code restrictions, which will lead to a notable increase of the processors gate count. The example given above also indicates that the need for forwarding will increase the latency of the pipeline stages (in the given example two sequential ALU operations have to be executed within one clock cycle). Another forwarding problem of great concern is given by the following example:

instr.A: CMP\_EQ r1, r2; instr.B: MOV\_CT r4, r1;

During the decode pipeline stage SPEAR determines if a conditional instruction is going to be executed or not (the SPEAR architecture has been shown in section 1.2.1). In case of the superscalar approach the shown example needs special treatment to ensure that the condition flag is available in time to serve the conditional instruction as input.

How the code restrictions have been resolved and whether there are any left or not will be discussed in detail in chapter 4

# 4 Overall Design of the Microcontroller

In this chapter all design decisions for LANCE will be explained in detail. The LANCE processor is intended to extend the SPEAR design to a more powerful superscalar design. Therefore, an in-depth analysis of the SPEAR architecture will be presented and all design relevant issues of the superscalar approach will be discussed. Furthermore, important implementation details of the architectural components like instruction memory, register file, data memory, etc. are pointed out.

# 4.1 Increasing Speed

The first approach to improve the throughput of LANCE with respect to the SPEAR processor leads to detailed analysis of all data paths within the SPEAR architecture. As highlighted in Figure 15, the identified critical processing path comprises the register file (pipe register 2), the data multiplexors at the ALU input ports, the ALU and the write-back bus to the register file framepointer generator.

Figure 15: Critical Path

The following piece of code shows an operation along the critical path:

ADDI r26, 12 STOFX r2, 9

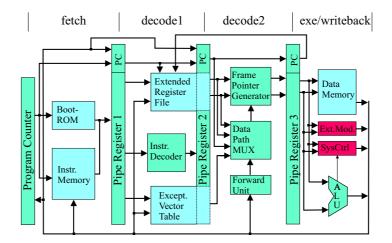

To provide the correct values for the initialization of register r26, which is coupled with the framepointer X operations, the input data for the *ADDI* instruction is multiplexed to the ALU input ports inside the execute/writeback pipeline stage. Concurrently (inside the decode pipeline stage) the succeeding STOFX framepointer operation has to sum up register r26 and the given offset to generate the appropriate memory location to store register r2. Therefore, the result of the ADDI instruction is forwarded out of the ALU to the *framepointer generator* where it is used for the address calculation. The ALU input multiplexor inside the execute/writeback, as well as the framepointer address generator inside the decode stage and the resulting unbalanced workload on these pipeline stages, limit the maximum clock rate of SPEAR. To resolve these limitations which result from the above identified bottlenecks, another pipeline stage (decode2) has been inserted between the SPEAR decode and execute/writeback stages, shown in the block diagram in Figure 16.

Figure 16: SPEAR Architecture Extended by an Additional Pipeline Stage

The additional pipeline stage allows to balance the workload of the pipeline stages which results in increase of clock rate and hence higher throughput. The address calculation for framepointer operations (*baseaddress* + *offset*) has been transferred to the decode2 pipeline stage. Moreover the multiplexor which provides the two ALU input ports with correct input data (out of the *program counter, the exception vector table* or the *register file*), also moves to the decode2 stage to speed up the execute/writeback cycle. For further increase of the ALU processing speed the ALU input data is preprocessed (details on preprocessing in section 4.4.3).

## 4.2 Superscalar Design Issues

One way to increased processing power while disregarding clock frequency arises from the superscalar design approach. The LANCE architecture consists of two operand execution pipelines called *Pipe A* and *Pipe B* (similar to the pentium design presented in section 2.1) and therefore represents a dual-issue superscalar architecture. The superscalar design of LANCE faces three main problems:

- 1. Data dependencies arise from the concurrent execution of two instructions per clock cycle

- 2. The number of possible *instruction memory*, register file, exception vector table and data memory accesses doubles in comparison to SPEAR.

- 3. Only one extension module access per clock cycle is supported by the standardized module interface.

To resolve as many code restrictions as possible both pipelines are able to execute any instruction of the instruction set. One for the programmer transparent restriction regarding extension module access exists within Pipe B (described in detail in section 4.4.7). As denoted in section 3.3, several data dependencies arise from the concurrent execution of two instructions. To ensure code compatibility to NEEDLE and SPEAR, considerable forwarding effort is necessary to resolve these data dependencies. It has been ensured that Pipe B always issues the succeeding instruction of Pipe A to limit the needed forwarding mechanisms to an absolute minimum (minimizing the number of forwardings also results in less silicon area). This constraint also assures that only forwarding from Pipe A to Pipe B is needed, but not vice versa. Section 4.4.1 gives detailed insights into the applied fetching mechanisms. Furthermore, section 4.5 points out implementation details on data forwarding. As discussed in section 4.1, framepointer address generation has moved to the decode2 pipeline stage to achieve more balanced pipeline stages. This design decision implicates a code restriction illustrated by the following lines of code:

Pipe A: ADDI r26, 16; Pipe B: LDOFX r22, -3;

The ADDI instruction alters the position of framepointer X inside the execute/writeback stage, but the LDOFX instruction has already calculated the memory address inside the decode2 pipeline stage. The resulting code restriction can not be resolved via simple data forwarding. Only inserting an additional framepointer address generator within the execute/writeback stage can solve this restriction. Since this extra hardware will extend the critical path, the code restriction is not resolved via hardware but has to be kept in mind during program code generation. Inserting a filler operation (an independent instruction or NOP) between the operation that sets the framepointer and the one that uses it is essential to achieve correct results. The drawback of this code restriction should be minor, because framepointers are only set infrequently and in many cases an independent filler operation can be found by code reordering mechanisms. Due to the fact that code compatibility to SPEAR and NEEDLE should be provided as far as possible, no further code restrictions were added to the LANCE design.

As LANCE determines whether a conditional instruction is going to be executed or not within the *pipeline register 3* (decode2 pipeline stage), the following code sequence introduced in section 3.3 demands special treatment:

Pipe A: CMP\_EQ r1, r2; Pipe B: MOV\_CT r4, r1;

All compare and bit-test instructions issued to Pipe A perform their condition flag calculation inside the decode2 pipeline stage. Thus condition evaluation of conditional instructions which have been issued to Pipe B can take place within *pipe register 3* as usual. Condition flag calculation of compare and bittest instructions issued to Pipe B are performed within execute/writeback stage and the result is forwarded to *pipeline register 3* for further use by conditional instructions.

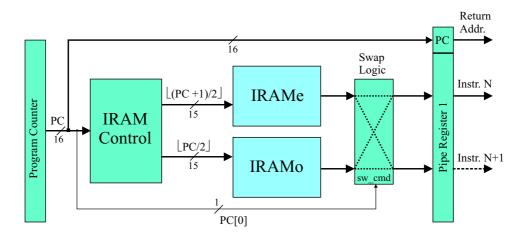

To ensure that each clock cycle two sequential instructions are read out of the *instruction memory*, the memory has been split into two blocks. One block holds all instructions with even addresses, the other block those with odd addresses. As mentioned above, Pipe A is loaded with the preceding instruction of that issued to Pipe B. A detailed description of the whole instruction fetch mechanism is given in section 4.4.1.

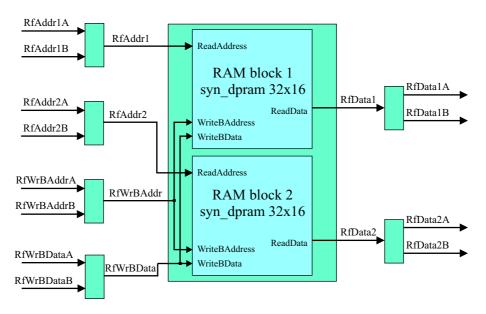

The *register file* has to be able to perform two independent write- and four read-accesses per clock cycle. As there are no memory modules within the APEX standard memory modules (an APEX-FPGA represents the desired target device) that meet those requirements, two different implementations have been verified. Both *register file* designs are presented in section 4.4.2.

*Data Memory* has to handle two read, two write or one read and one write action per clock cycle. To provide this functionality there have also been two approaches that will be shown in detail in section 4.4.6.

Finally the *exception vector table* also needed adapting to the superscalar design to provide both pipelines with the possibility to read and store the service routine jump addresses. Section 4.4.4 presents the implementation details.

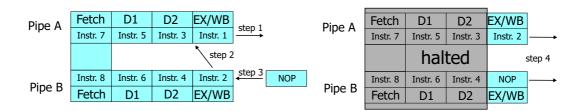

The restriction that only one extension module access can be processed each clock cycle (due to the fact that the standardized interface does not support more) has been resolved by hardware. The extension module interface is only connected to Pipe A, therefore all extension module accesses occurring in Pipe B are handed over to Pipe A for further processing. Details on the whole hand-over mechanism are given in section 4.4.7.

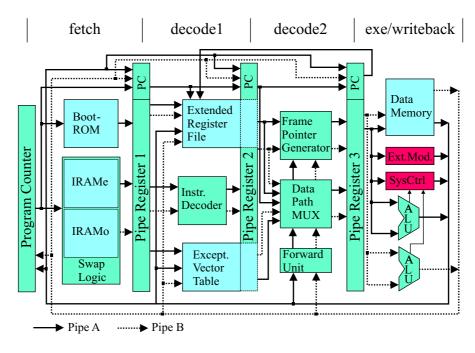

# 4.3 Microcontroller Architecture

The LANCE processor aims to be code-compatible with and more powerful than SPEAR. All design issues discussed in section 4.1 and 4.2 led to a pipelined dual-issue superscalar design with a four-stage-deep pipeline, as shown in Figure 17. The presented LANCE architecture is able to execute any program code written for NEEDLE and SPEAR due to extensive data forwarding and special treatment of extension module accesses. However, the code restriction regarding framepointer operations, introduced in section 4.2, has to be considered.

Figure 17: LANCE Architecture

# 4.4 Microcontroller Implementation

As mentioned earlier, LANCE comprises two instruction execution pipelines, Pipe A and Pipe B as shown in Figure 18. Both pipelines are able to handle any instruction within the instruction set of the processor. However, extension module accesses are processed, in a manner transparent for the programmer, via Pipe A only since the extension module interface does not support concurrent access to modules (section 4.4.7 provides detailed information on the implemented extension module access mechanism). Pipe A and Pipe B are organized as four-stage-deep scalar pipelines. The pipeline stages are as follows:

- Instruction Fetch (Fetch)

- Instruction Decode 1 (D1)

- Instruction Decode 2 (D2)

- Execute and Writeback (EX/WB)

Figure 18: LANCE Pipeline Architecture

The first pipeline stage is the Fetch stage in which instructions are read from Boot-ROM or instruction memory and stored to the pipe register 1. On system startup instructions are always fetched from the Boot-ROM at a rate of one instruction per clock cycle, therefore only Pipe A has to execute instructions (Pipe B is filled with NOPs). Performing the boot sequence only