DISSERTATION

# Monolithic Microwave Integrated Circuits in SiGe:C Bipolar Technology

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

> Ao. Univ. Prof. Dr. Arpad L. Scholtz E389

Institut für Nachrichtentechnik und Hochfrequenztechnik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Werner Perndl Matrikelnummer 9625329 Tröstlberg 33 A-4431 Haidershofen

Haidershofen, im November 2004

Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at). The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

Begutachter:

.

Ao. Univ. Prof. Dr. Arpad L. Scholtz Univ. Prof. Dr. Peter Weger

# Zusammenfassung

Die vorliegende Arbeit befasst sich mit der Entwicklung und Optimierung von monolithisch integrierten Schaltungen in Silizium-Germanium (SiGe) Bipolartechnologie für Anwendungen im Mikrowellenbereich. Kostengünstige Hochfrequenzschaltungen ermöglichen ein rasantes Wachstum des Marktes für Kommunikationsdienste. Insbesondere mobile Anwendungen wie zum Beispiel WLAN (wireless local area network), GPS (global positioning system) und die Mobiltelefonie (GSM, UMTS), aber auch drahtgebundene Breitbandsysteme erfuhren ernorme Wachstumsraten in den letzten Jahren. Auch Anwendungen im Mikrowellenbereich wie zum Beispiel Abstandsradar für die Automobilindustrie aber auch Breitbandsysteme für die schnelle Datenübertragung könnten zum Massenprodukt werden, falls die Systemkosten wesentlich gesenkt werden. Dies könnte durch eine integrierte Realisierung in einer kostengünstigen silizium-basierten Halbleitertechnologie ermöglicht werden. SiGe bietet neben der Eignung für hohe Frequenzen auch den Vorteil einer hohen Integrationsfähigkeit, die wesentlich die Gesamtkosten eines Systems bestimmt.

Am Beginn der vorliegenden Arbeit wird ein Überblick über die verwendete SiGe:C Bipolartechnologie gegeben. Anschließend wird anhand ausgewählter Beispiele die Realisierung monolithisch integrierter Analogschaltungen für den Mikrowellenbereich gezeigt.

Als erstes Beispiel wird die Entwicklung und die Optimierung eines Breitbandverstärkers zur Verstärkung von Datensignalen sehr hoher Bitrate, aber auch sehr hochfrequenter Sinussignale, demonstriert. Neben einer hohen 3-dB Bandbreite zählen eine flache Übertragungsfunktion sowie ein hoher Ausgangshub zu den wesentlichen Entwurfszielen. Durch sorgfältige Optimierung der Schaltung wird eine Übertragung von Datensignalen mit einer Datenrate von 100 Gbit/s bei gleichzeitig hohem Ausgangshub erreicht. Diese Ergebnisse, welche in [Perndl04b] publiziert wurden, zeigen eine höhere Datenrate als alle bisher veröffentlichten Analogschaltungen, nicht nur in silizium-basierten, sondern auch in GaAs- und InP-Technologien.

Als zweites Beispiel einer monolithisch integrierten Mikrowellenschaltung dient ein Abwärtsmischer für den Frequenzbereich von 76 GHz bis 81 GHz. Dieses Frequenzband ist für Abstandssensoren in der Automobilindustrie vorgesehen. Bei dieser Schaltung handelt es sich um den ersten Abwärtsmischer für diesen Frequenzbereich, der in siliziumbasierter Technologie gefertigt wurde. Eine Zusammenfassung dieser Ergebnisse ist in [Perndl 04a] veröffentlicht.

Schließlich wird ein monolithisch integrierter spannungsgesteuerter Oszillator beschrieben. Das wesentliche Entwicklungsziel dieser Schaltung ist eine möglichst hohe Ausgangsfrequenz. Unter Anwendung innovativer Schaltungskonzepte, wie zum Beispiel eines integrierten Lambda-Viertel-Transformators am Ausgang der Schaltung, gelingt es, eine Ausgangsfrequenz von 98 GHz zu erreichen. Die Ergebnisse dieser Schaltung sind in [Perndl 03] und [Perndl 04c] veröffentlicht.

# Abstract

This thesis deals with design and optimization of monolithically integrated circuits for applications at microwave frequencies fabricated in a state-of-the-art low-cost silicon germanium (SiGe) bipolar technology. The rapid growth of the communication market is enabled due to low-cost high-frequency solutions. Especially wireless applications like wireless local area networks (WLAN), global positioning systems (GPS) and mobile telephony (GSM and UMTS) as well as wireline broadband systems came up over the past years. Additionally, applications at microwave frequencies like distance sensors for automotive and industrial systems as well as high-speed data communication could become a new mass market, if system costs can be reduced significantly. For monolithically integrated realization of such systems, silicon germanium bipolar technologies seem to be a promising candidate. Due to constant progress in technology development as well as accurate optimization during the circuit design process, monolithic integrated circuits in the microwave frequency range fabricated in low-cost silicon-based technologies become feasible.

At the beginning of this thesis an overview of the SiGe:C bipolar technology, in which the chips of this work have been fabricated, is presented. Subsequently, monolithic integration of analog building blocks is demonstrated on the basis of three representative circuits for different microwave applications.

The first circuit presented in this work is a broadband amplifier. The amplifier is intended for multiple applications like a preamplifier of high data rate signals, an amplifier for high-frequency single-tone signals and a linear amplifier in conventional high-frequency systems. Due to contradicting requirements of the different applications, tradeoffs between circuit parameters are necessary. A flat frequency response and a high 3-dB bandwidth are the main design targets. By careful optimization of the circuit, outstanding measurement results up to 100 Gbit/s are achieved. These results, which have been published in [Perndl 04b], show the highest bit rate for analog high-frequency circuits in silicon-based as well as GaAs and InP technologies.

The second example of a fully monolithically integrated microwave circuit is a downconversion mixer in the frequency range from 76 GHz to 81 GHz. This frequency band is intended for automotive distance sensors. With this design, a monolithically integrated active down-conversion mixer for microwave frequencies around 77 GHz is demonstrated for the first time in silicon-based technologies. A summary of these results is published in [Perndl 04a].

Finally, a voltage-controlled oscillator is shown. The main design target is to reach an output frequency as high as possible at reasonable values of phase noise and output power. By application of innovative circuit concepts like a quarter-wave transformer at the output of the circuit an operation frequency up to 98 GHz is reached. These results are published in [Perndl 03] and [Perndl 04c].

# Contents

.

| 1        | Intr  | oduction 1                                                    |

|----------|-------|---------------------------------------------------------------|

|          | 1.1   | Objective of the Work                                         |

|          | 1.2   | Thesis Outline   2                                            |

| <b>2</b> | Silio | con Germanium Bipolar Technology 4                            |

|          | 2.1   | Double-polysilicon Self-aligned Transistor Configuration      |

|          | 2.2   | Simulation Models                                             |

|          |       | 2.2.1 Large Signal Model                                      |

|          |       | 2.2.2 Small Signal Model                                      |

|          |       | 2.2.3 Modeling of Parasitic Resistances                       |

|          |       | 2.2.4 Modeling of Parasitic Capacitances                      |

|          | 2.3   | Transistor Effects                                            |

|          |       | 2.3.1 The Early Effect                                        |

|          |       | 2.3.2 The Kirk Effect                                         |

|          |       | 2.3.3 Quasi Saturation                                        |

|          |       | 2.3.4 Emitter Current Crowding                                |

|          |       | 2.3.5 Base Conductivity Modulation                            |

|          | 2.4   | Electrical Characteristics                                    |

|          | 2.5   | Passive Devices                                               |

|          | 2.6   | Metallization                                                 |

| 3        | Des   | ign of a Broadband Amplifier for 100 Gbit/s Data Signals 21   |

|          | 3.1   | Introduction                                                  |

|          |       | 3.1.1 State of the Art                                        |

|          |       | 3.1.2 Specification of Circuit Parameters                     |

|          | 3.2   | Fundamental Circuit Characteristics                           |

|          |       | 3.2.1 Broadband Amplifier Concepts                            |

|          |       | 3.2.2 Frequency Response                                      |

|          |       | 3.2.3 Operation in Limiting Mode                              |

|          |       | 3.2.4 Linearity                                               |

|          |       | 3.2.5 Third-Order Intercept Point                             |

|          |       | 3.2.6 1-dB Compression Point                                  |

|          |       | 3.2.7 Relationship between 1-dB Compression and IP3 Points 31 |

|          | 3.3   | Circuit Design                                                |

|   |     | 3.3.1   | Schematic of the two-stage Amplifier                                                                           |   |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------|---|

|   |     | 3.3.2   | Simulation Results                                                                                             |   |

|   | 3.4 | •       | ;                                                                                                              |   |

|   | 3.5 | Measu   | $rement Results \ldots 3'$ |   |

|   |     | 3.5.1   | S-Parameter                                                                                                    | 7 |

|   |     | 3.5.2   | Single-Tone Compression Point                                                                                  | 0 |

|   |     | 3.5.3   | Two-Tone Third-Order Intermodulation                                                                           | 1 |

|   |     | 3.5.4   | High Data Rate Signals                                                                                         | 2 |

|   | 3.6 | Summa   | ary                                                                                                            | 6 |

| 4 | An  | Active  | Mixer for 77 GHz Applications 4'                                                                               | 7 |

|   | 4.1 | Intrody | $\operatorname{uction}$                                                                                        | 7 |

|   |     | 4.1.1   | State of the Art                                                                                               | 9 |

|   |     | 4.1.2   | Specification of Circuit Parameters                                                                            | 1 |

|   | 4.2 | Funda   | mental Mixer Characteristics                                                                                   | 2 |

|   |     | 4.2.1   | Mixer Topologies                                                                                               | 2 |

|   |     | 4.2.2   | Performance Parameters                                                                                         | 4 |

|   | 4.3 | Circuit | $5$ Design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $56$                                          | 6 |

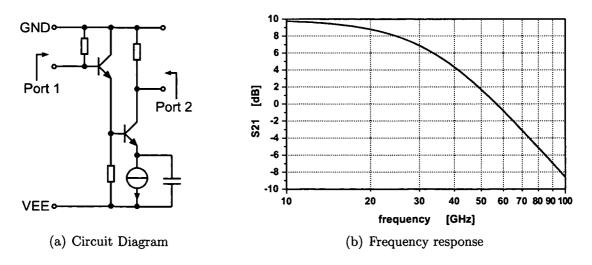

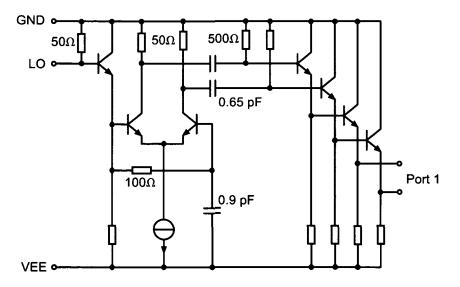

|   |     | 4.3.1   | LO buffer                                                                                                      | 7 |

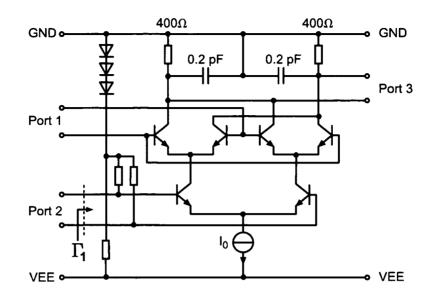

|   |     | 4.3.2   | Mixer Core                                                                                                     | 7 |

|   |     | 4.3.3   | LC balun                                                                                                       | 9 |

|   |     | 4.3.4   | IF buffer                                                                                                      | 2 |

|   | 4.4 | Layout  | 5                                                                                                              | 3 |

|   | 4.5 | Measu   | rement Results                                                                                                 | 3 |

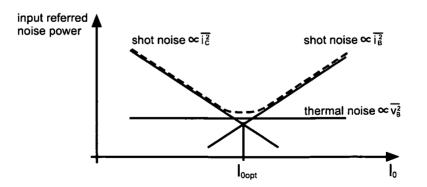

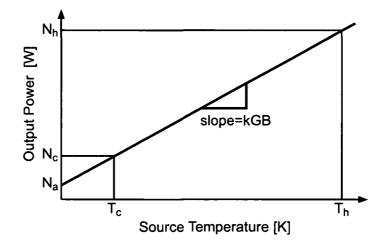

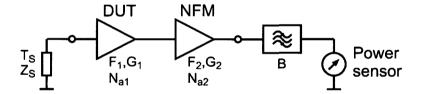

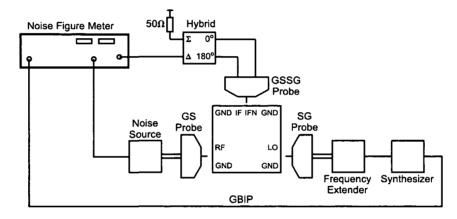

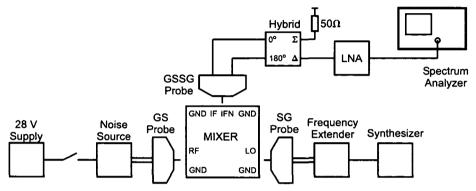

|   |     | 4.5.1   | Y-Factor Method for Noise Figure Measurement                                                                   | 4 |

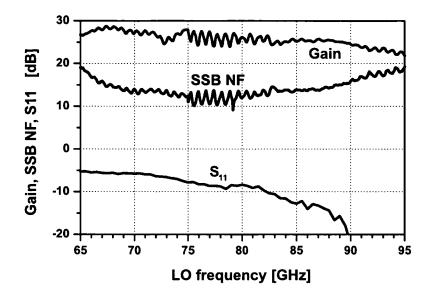

|   |     | 4.5.2   | Gain and Noise Figure versus LO Frequency                                                                      | 7 |

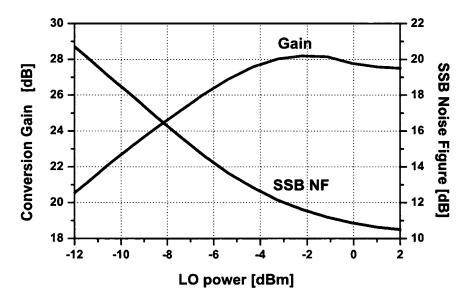

|   |     | 4.5.3   | Gain and Noise Figure versus LO Power                                                                          | 7 |

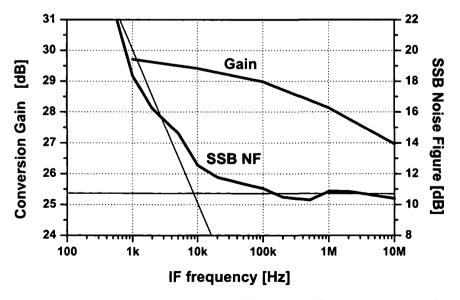

|   |     | 4.5.4   | Gain and Noise Figure versus IF Frequency                                                                      | 9 |

|   |     | 4.5.5   | Single-Tone Compression Point                                                                                  | 0 |

|   |     | 4.5.6   | Time-Domain Signal                                                                                             | 1 |

|   |     | 4.5.7   | RF Input Reflection                                                                                            | 2 |

|   | 4.6 | Summ    | $\operatorname{ary}$                                                                                           | 3 |

| 5 | A 9 | 8 GHz   | Voltage Controlled Oscillator 74                                                                               | 4 |

|   | 5.1 | Introd  | $\operatorname{uction}$                                                                                        | 4 |

|   |     | 5.1.1   | State-of-the-Art                                                                                               | 5 |

|   |     | 5.1.2   | Specification of VCO Properties                                                                                | 6 |

|   | 5.2 | Funda   | mentals of Oscillator Design                                                                                   | 7 |

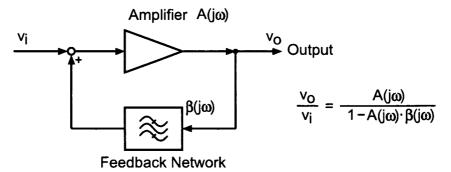

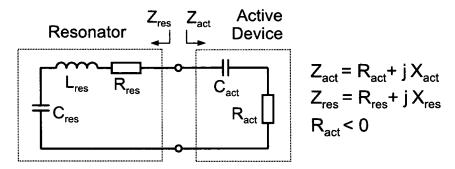

|   |     | 5.2.1   | Oscillator Model                                                                                               | 7 |

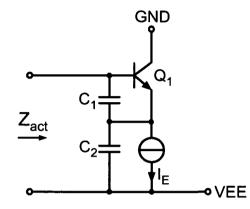

|   |     | 5.2.2   | Colpitts Oscillator                                                                                            | 9 |

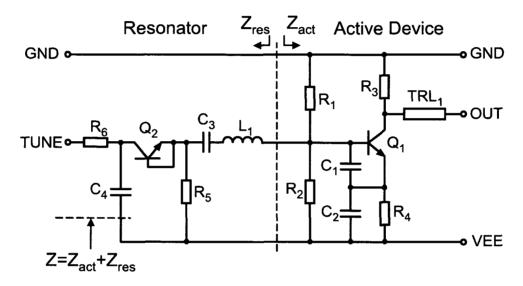

|   | 5.3 | Circuit | b Design                                                                                                       | 0 |

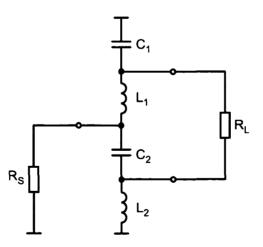

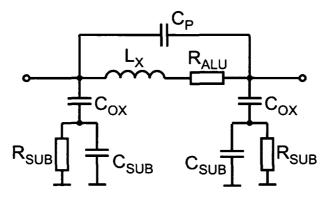

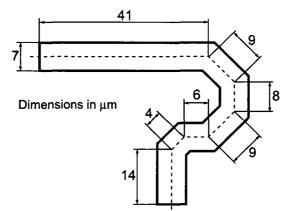

|   |     | 5.3.1   | Resonator                                                                                                      | 0 |

|   |     | 5.3.2   | Output Matching                                                                                                | 2 |

|    |                     | 5.3.3   | Small Signal Design                     | 83  |

|----|---------------------|---------|-----------------------------------------|-----|

|    |                     | 5.3.4   | Large Signal Design                     | 85  |

|    | 5.4                 | Layout  | ••••••••••••••••••••••••••••••••••••••• | 86  |

|    | 5.5                 | Measu   | rement Results                          | 86  |

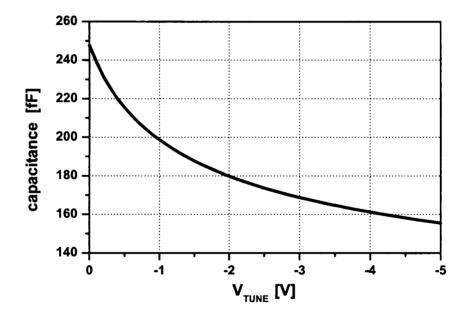

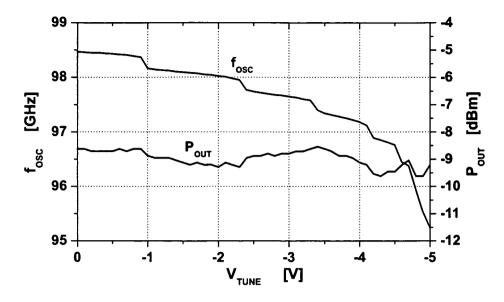

|    |                     | 5.5.1   | Tuning Characteristic and Output Power  | 87  |

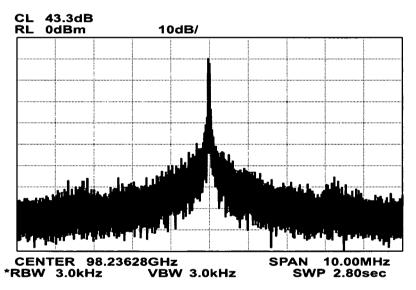

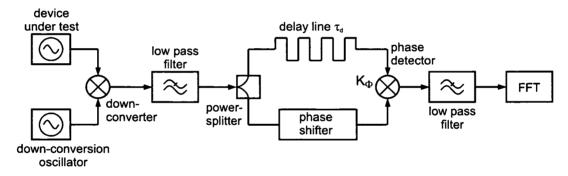

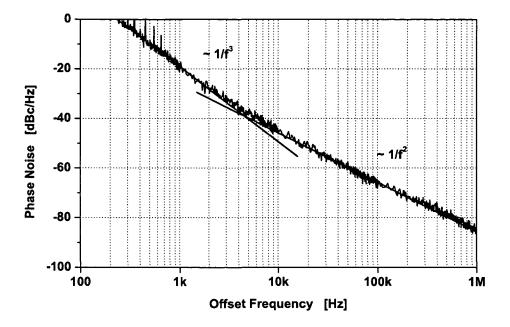

|    |                     | 5.5.2   | Phase Noise Measurements                | 88  |

|    |                     | 5.5.3   | Influence of the Measurement Equipment  | 92  |

|    | 5.6                 | Summa   | ary                                     | 95  |

| 6  | Con                 | clusior | n and Outlook                           | 96  |

| Li | st of               | Abbre   | eviations                               | 98  |

| Bi | bliog               | raphy   |                                         | 101 |

| C  | ırricı              | ılum V  | Vitae                                   | 111 |

| A  | Acknowledgement 112 |         |                                         |     |

# Chapter 1

# Introduction

The rapid growth of wireless communication systems such as wireless telephony, global positioning systems (GPS) and wireless local area networks (WLAN) as well as wireline communication systems such as broadband data services is enabled by low-cost and high-performance semiconductor solutions. This evolution tends continuously towards higher operation frequencies, higher integration levels and lower power consumption.

The choice of an appropriate technology for a specific application is of particular importance. Due to the fast progress of technology development this choice is subject to fast changes. Over the past years especially silicon-based technologies made outstanding progress. The introduction of the double-polysilicon self-aligned transistor configuration as well as improvements in the doping profile enabled a strong increase in the transistor's speed. Also the analog properties of the transistors have been improved by enhancements of technological processes. The target of system development is to implement both analog and digital building blocks on a single chip in order to reduce system costs. Due to the different requirements of analog and digital circuits it is a great challenge to monolithically integrate both functions into one semiconductor. State-of-the-art silicon germanium bipolar technologies seem to be promising candidates for such applications due to the capability of high integration levels as well as the constantly increasing speed.

Applications in the microwave frequency range like WLAN at 60 GHz, optical communication at 80 Gbit/s and radar systems at 77 GHz can be realized up to now only in III-V semiconductor technologies. Recent advances in SiGe bipolar technology have stimulated research activities to investigate the realizability of applications at microwave frequencies in silicon-based technologies.

## 1.1 Objective of the Work

The aim of this work is to demonstrate monolithic integration of analog building blocks for applications at microwave frequencies in a state-of-the-art low-cost SiGe bipolar technology. This will be demonstrated on the basis of a broadband amplifier for high data rate communication systems as well as a down-conversion mixer and a voltage controlled oscillator for distance sensors in automotive and industrial applications. Due to the very high operation frequencies, wave propagation on chip becomes a substantial concern even though chip dimensions are very small. At a frequency of 77 GHz, the wavelength  $\lambda$  in silicon dioxide is only 2 mm, so  $\lambda/10$  is smaller than typical chip dimensions. Due to this property, new possibilities in circuit design arise. New circuit architectures become possible and open a wide field of research.

At first, for each design specifications and targets are defined as well as an overview of state-of-the-art circuits is made. Then, circuit architecture and technology have to be selected. The circuit architecture mainly depends on the technology in which the chip is fabricated. Both, active components (transistors) as well as passive components like resistors, capacitors, varactors and the metal layer stack decide whether a circuit concept is feasible in a certain technology or not. If circuit architecture and technology are fixed, the main task is to optimize the various functional blocks of the circuit. At this time, it is essential to make use of the specialities of the technology as well as to compensate for deficiencies of the specific technology by innovative circuit design. Next, the components of the circuit should be optimized regarding an optimum compromise between contradicting circuit characteristics.

Usually this design process consists of several iterations since it is possible that a chosen circuit architecture turns out to be not optimal after intensive investigation. Consequently, the optimization of a circuit requires experience for selecting the architecture, innovation in finding new solutions, creativity for implementation of the various functional blocks, as well as technical know-how about individual components of the technology.

## **1.2** Thesis Outline

After the introduction, Chapter 2 provides basics of the SiGe:C technology, which is chosen for the fabrication of the chips of this work. Because this technology is still in development, the status quo of September 2004 is provided. First the transistor configuration, the process concept and basics of the fabrication process are explained. Simulation models for large and small signal simulation are provided as well as transistor effects are discussed. Properties of different transistor geometries are pointed out. Transistor results as well as characteristics of passive components and the metal layer stack are shown. In Chapter 3 design and optimization of a broadband amplifier in SiGe:C bipolar technology are presented. At first, an optical communication system which utilizes the broadband amplifier is introduced and basics about broadband amplifiers are explained. The circuit design process of the amplifier is based on the analysis of a differential amplifier with emitter followers at its input. Then the circuit is adapted to the particular specification. S-parameter measurements, large signal measurements as well as excitation with high data rate signals are presented.

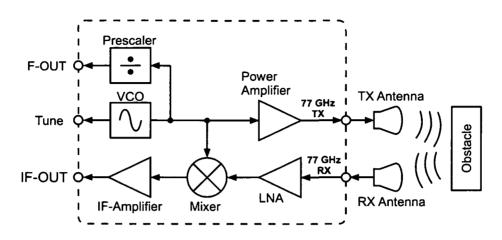

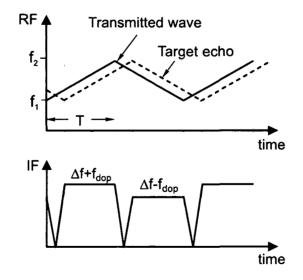

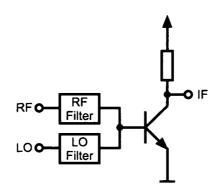

In Chapter 4 the design of a fully integrated active mixer for microwave applications at 76 GHz to 81 GHz is presented. This mixer is intended for distance sensors in automotive and industrial systems based on the frequency modulation continuous wave (FMCW) radar principle. At the beginning of the chapter the FMCW-principle is described as well as an overview about mixer properties is given. Then circuit design of the mixer is presented. The mixer core is based on the Gilbert cell. An LC balun and an LO buffer are used in order to provide differential signals to the mixer core. Finally, the layout and measurement results are presented.

In Chapter 5 a voltage controlled oscillator (VCO) with an output frequency up to 98 GHz is presented. This oscillator is based on the Colpitts oscillator. At the output, the circuit includes a novel quarter-wave transformer for impedance transformation which increases the maximum oscillation frequency. Design and optimization of the oscillator core and the resonator are presented. The measurement results as well as the influence of the measurement system on this particular oscillator are discussed.

Chapter 6 summarizes the results of the work and gives an outlook on future developments in monolithic microwave integrated circuit design.

# Chapter 2

# Silicon Germanium Bipolar Technology

The aim of this chapter is to present the silicon germanium (SiGe) bipolar technology in which the chips of this work are fabricated. This technology is still in development, so the status quo of September 2004 is described. The chips of this work are fabricated in wafer runs at different stages of the development. The substantial differences are mentioned in the respective chapter.

The first section of this chapter describes the process concept of the technology. Comments on the fabrication process and transistor results are given. Then transistor models for large and small signal simulation are introduced. These models are the starting point for circuit design. Additionally important transistor effects are discussed which must be considered during the design process. Finally passive components and the metallization of the technology is presented.

# 2.1 Double-polysilicon Self-aligned Transistor Configuration

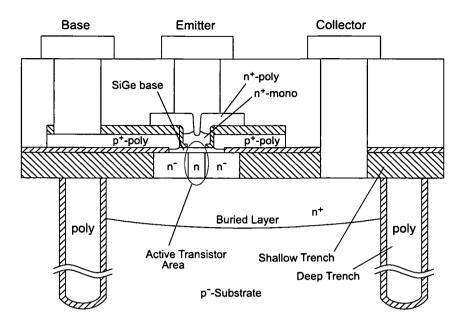

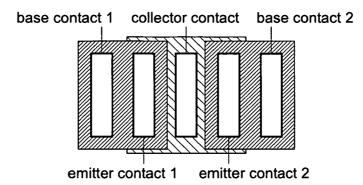

Figure 2.1 shows the schematic cross section of an npn transistor of Infineon's preproduction process B10HF. The active area of this transistor, which is located beneath the emitter contact, is only small compared to the whole transistor. But the dimension of the external inactive transistor is restricted due to design-rules of the technology, e.g. there are minimum width and minimum spacing of the first metal layer which specify the minimum distance between base, emitter, and collector contact. Optimization of the transistor performance includes both to speed up the intrinsic transistor (active area of the transistor) and to reduce parasitics like capacitances and resistances of the external inactive transistor.

Figure 2.1: Schematic cross section of an npn transistor

Infineon's B10HF silicon germanium bipolar technology is based on a double-polysilicon self-aligned transistor configuration with a selective epitaxial grown SiGe base layer. "Double-polysilicon" means that both, emitter and base contact are realized with polysilicon. This configuration exhibits low parasitic capacitances and a low extrinsic base resistance. The term "self-aligned" refers to the emitter-base isolation which is realized by thin dielectric layers. These so-called spacers are manufactured using anisotropic plasma etching and allow the construction of structures smaller than the lithographic limits.

A double-polysilicon self-aligned transistor with selectively epitaxially grown base was first realized without germanium (Ge) in [Meister 92]. Important further developments of the extrinsic transistor are a silicided polysilicon layer for contacting the base of the active transistor [Böck 98]. As a result of this silicided layer, the external base resistance is reduced by about one decade. Another feature of the technology is a mono-crystalline emitter contact [Meister 03] which reduces the emitter resistance considerably, as compared to conventional polysilicon emitters. Further, the collector-substrate capacitance is reduced by more than 40 % by introducing deep trench (DT) and shallow trench isolation (STI) [Schwerd 03, Böck 04].

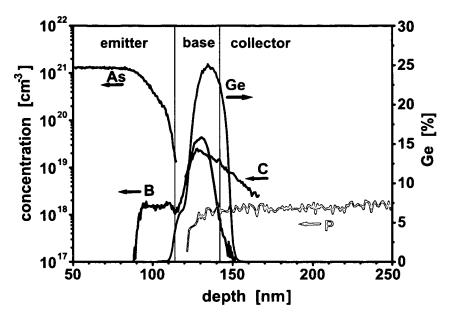

The integration of Ge into the base of the transistor enables bandgap engineering and the fabrication of heterojunction bipolar transistors (HBTs) in silicon-based materials [Meister 95]. In the SiGe HBT, germanium is selectively introduced into the base region of the transistor. The smaller base bandgap of SiGe compared to Si enhances electron injection, producing a higher current gain for the same base doping level compared to a Si device. Thus, the base can be doped more heavily in the SiGe HBT in order to lower the total base resistance. At the same time, the Ge content is graded across the base in order to achieve an accelerating drift field for the electrons to increase the cutoff frequency. A doping profile of the fabricated transistors is shown in Fig. 2.2. The ntype emitter is typically doped with arsenide (As), the doping material for the n-type collector is typically phosphor (P), and as acceptor material for the p-type base usually boron (B) is used. At the emitter side the base is lowly doped in order to obtain a small emitter-base capacitance. For realizing high cutoff frequency the thickness of the boron spike must be kept as thin as possible. The incorporation of carbon into the highly boron-doped SiGe base prevents the broadening of the base profile by subsequent processing steps [Böck 01].

Figure 2.2: Final doping profile of the transistors

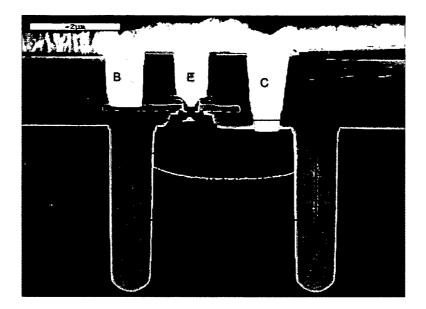

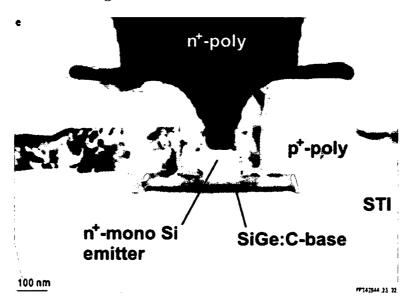

Figure 2.3 shows a TEM cross section of a whole npn transistor of Infineon's preproduction process B10HF including the dimensions. In Fig. 2.4 a TEM cross section of the emitter-base complex of a transistor is shown. Mono-crystalline n-type silicon of the emitter and the collector is depicted as light, uniformly colored areas, whereas polysilicon looks granular. The germanium fraction of the base results in a dark bar indicated as "SiGe:C-base".

## 2.2 Simulation Models

#### 2.2.1 Large Signal Model

The design of radio-frequency integrated circuits requires accurate and compact models of the bipolar transistors. A large variety of bipolar transistor models has been developed so far. The first compact model for bipolar transistors originates from the early 1950s by Ebers and Moll [Ebers 54]. This model describes the DC behavior of the transistor using

Figure 2.3: TEM of the transistor

Figure 2.4: TEM of the emitter base complex

four parameters: the ideal forward and reverse common-base current gain ( $\alpha_F$  and  $\alpha_R$ ) and the saturation current of the base-emitter and the base-collector diode ( $I_{BES}$  and  $I_{BCS}$ ). The Ebers-Moll model describes the fundamental DC behavior of the transistors, however many effects like the Early and Kirk effect as well as conductivity modulation are not covered. A compact model that is more appropriate for the descripton of the bipolar transistor is the Gummel-Poon model [Gummel 70]. This model is based on the integral charge control concept by introducing the normalized majority base charge  $q_b$ . So, many of the effects not contained in the basic Ebers-Moll model are incorporated in an integral, physical way. The Gummel-Poon model has been implemented in a slightly modified version into the circuit simulation tool SPICE [Nagel 75] (SPICE-Gummel-Poon model) and so it has become a standard for modeling of bipolar transistors. A comprehensive presentation of modeling high-frequency bipolar transistors can be found in [Reisch 03].

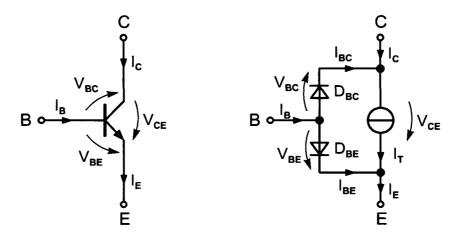

Figure 2.5: A simple equivalent circuit for modeling bipolar transistors [Reisch 03]

The equivalent circuit to describe the transistor characteristics which is shown in Fig. 2.5 is based on the Gummel-Poon model. It employs two diodes  $D_{BC}$  and  $D_{BE}$  representing the base-emitter (BE) and the base-collector (BC) junctions, together with a voltage-controlled current source, which describes the coupling of the two pn-junctions. In forward operation ( $V_{BE} \gg V_T$  and  $V_{BC} < 0$ ) the reverse biased BC diode can be neglected. Then  $I_{BC}=0$  and the collector current  $I_C$  equals the transfer current  $I_T$ ,  $I_C=I_T$ . Neglecting series resistances the following equations characterize the large signal behavior of the transistor [Reisch 03]:

$$I_C = I_S \left( 1 + \frac{V_{CE}}{V_{AF}} \right) exp \left( \frac{V_{BE}}{V_T} \right), \qquad (2.1)$$

$$I_B = \frac{I_S}{\beta_F} exp\left(\frac{V_{BE}}{V_T}\right),\tag{2.2}$$

$$\alpha_F = \frac{\beta_F}{1 + \beta_F} \quad , \tag{2.3}$$

where  $I_S$  is the transfer saturation current,  $V_T$  denotes the thermal voltage, and  $V_{AF}$  is the Early voltage.  $\beta_F$  is the common-emitter forward current gain which relates to the already mentioned common-base forward current gain  $\alpha_F$  via (2.3).

The SPICE-Gummel-Poon model also incorporates bias-dependent resistances for base and collector contact, an emitter resistance as well as diffusion and depletion capacitances. Further effects like carrier recombination in the space charge region and collector substrate coupling are considered, see [Reisch 03].

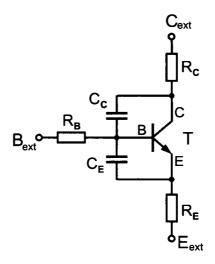

In practice, additionally to the SPICE-Gummel-Poon model parasitic elements are modeled by using a sub-circuit as shown in Fig. 2.5. In the external transistor circuit of Fig. 2.6,  $C_E$  and  $C_C$  characterize oxide capacitances between external contacts.  $R_B$ ,  $R_E$ , and  $R_C$  model the external resistances of base, emitter, and collector contact.

Figure 2.6: External model for the simulation of transistors. T represents an internal transistor model.

#### 2.2.2 Small Signal Model

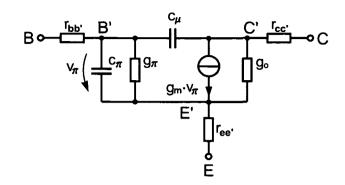

If the signal levels of analog circuits are small enough compared to bias currents and voltages, linearized small signal models can be used for the analysis of the circuits. In forward operation ( $V_{BC} < 0$  and  $V_{BE} \gg V_T$ ) the small signal equivalent circuit shown in Fig. 2.7 can be derived from the large signal model of Fig. 2.5.

The input conductance  $g_{\pi}$ , the transconductance  $g_m$ , and the output conductance  $g_o$  can be determined as partial derivatives of the current-voltage characteristics from (2.1) to (2.3) [Reisch 03]:

$$g_{\pi} = \left(\frac{\partial I_B}{\partial V_{BE}}\right)_{V_{CE}} = \frac{I_B}{V_T} , \qquad (2.4)$$

$$g_m = \left(\frac{\partial I_C}{\partial V_{BE}}\right)_{V_{CE}} = \frac{I_C}{V_T} , \qquad (2.5)$$

$$g_o = \left(\frac{\partial I_C}{\partial V_{CE}}\right)_{V_{BE}} = \frac{I_C}{V_{CE} + V_{AF}} \quad . \tag{2.6}$$

Figure 2.7: High frequency small signal equivalent circuit with series resistances based on the Giacoletto model;  $r_{bb'}$ ,  $r_{ee'}$ , and  $r_{cc'}$  represent linearized resistances of the potentially bias dependent contact resistances  $R_{bb'}$ ,  $R_{ee'}$ , and  $R_{cc'}$ .

Often the input resistance  $r_{\pi} = 1/g_{\pi}$  and the output resistance  $r_o = 1/g_o$  are used. The short-circuit, small signal current gain  $\beta_0$  depends on the DC operating point and can be calculated as:

$$\beta_0 = \left(\frac{\partial I_C}{\partial I_B}\right)_{V_{CE}}.$$

(2.7)

The high-frequency behavior of the transistor is modeled by two capacitances  $c_{\pi}$  and  $c_{\mu}$ , see Fig. 2.7. Each capacitance consists of a diffusion and a depletion part. In forward operation, the diffusion charge of the BC diode can be neglected, resulting in:

$$c_{\mu} = c_{jc} \text{ and } c_{\pi} = c_{je} + \tau_F g_m \tag{2.8}$$

where  $c_{je}$  and  $c_{jc}$  denote the depletion capacitances of the BE and BC diodes, and  $\tau_F$  is the forward transit time.  $\tau_F g_m$  denotes the diffusion capacitance of the BE diode. The frequency range of a transistor is usually specified by the frequency where the magnitude of the current gain  $\beta(f)$  falls to unity

$$\beta(f) = \frac{\beta_0}{1+j f/f_\beta} \rightarrow f_T = \beta_0 f_\beta$$

(2.9)

where  $f_{\beta}$  denotes the 3-dB cutoff frequency of  $\beta$ , and  $f_T$  denotes the cutoff frequency of the transistor.  $f_T$  depends on the bias conditions: for a low collector current  $I_C$ ,  $f_T$  can be calculated as [Reisch 03]:

$$f_T \approx \frac{g_m}{2\pi(c_{je} + c_{jc})} \tag{2.10}$$

which causes  $f_T$  to increase with  $I_C$ . For large values of  $I_C$ ,  $f_T$  results in [Reisch 03]:

$$f_T \approx \frac{1}{2\pi [\tau_F + (r_{ee'} + r_{cc'})c_{jc}]}$$

(2.11)

where  $\tau_F$  denotes the forward transit time. At high collector currents,  $\tau_F$  increases with  $I_C$  which causes  $f_T$  to decrease with increasing  $I_C$ . So there is an optimum collector current which leads to a maximum cutoff frequency, see Fig. 2.9.

Another important measure of transistor performance is the maximum oscillation frequency  $f_{max}$ . It is defined as the frequency where the unilateral power gain [Vendelin 82] of the transistor becomes unity. It can be calculated [Reisch 03]:

$$f_{max} \approx \sqrt{\frac{f_T}{8\pi (r_{bb'} + r_{ee'} + 1/g_m)c_{jc}}}$$

(2.12)

#### 2.2.3 Modeling of Parasitic Resistances

The base resistance  $R_{BB'}$  consists of an internal base resistance (within the active area) and an external contact resistance (poly-Si contact region). In order to yield a low base transit time, a very thin base is required. This affects the internal base resistance which depends on the base width, the width of the emitter window, and the doping density in the SiGe:C base. Further it depends on the bias condition of the transistor. The internal base resistance is modeled as [Reisch 03]:

$$R_{BB'} = R_{BM} + \frac{R_B - R_{BM}}{q_B}$$

(2.13)

where  $R_B$  and  $R_{BM}$  denote the maximum and the minimum base resistance, respectively, and  $q_B$  denotes the normalized majority base charge. Due to conductivity modulation and emitter current crowding (see Section 2.3), the internal base resistance decreases at high base and collector currents. The external part of the base resistance consists of the contact resistance and the resistance of the external base region. This part is modeled as an ohmic resistance.

The emitter resistance  $R_{EE'}$  acts as emitter degeneration and so it reduces the transconductance  $g_m$  of the transistor. As a result of the high doping level in the emitter, the resistance of the mono-crystalline emitter is small compared to the poly-contact resistance. Further, the contact resistances between metal and poly-Si as well as between poly-Si and mono-Si must be considered [Gabl 99]. The emitter resistance  $R_{EE'}$  is described as an ohmic resistance.

The collector resistance  $R_{CC'}$  consists of an internal and an external resistance, too. The external contact resistance is kept low due to a highly doped buried layer. The internal portion of the collector resistance can not be reduced without increasing the BC capacitance and reducing the BC breakdown voltage.  $R_{CC'}$  influences the saturation current of the transistor, therefore it is of particular interest in circuits which are subject to saturation and quasi-saturation (see Section 2.3). In our models,  $R_{CC'}$  is also described as ohmic resistance.

#### 2.2.4 Modeling of Parasitic Capacitances

Parasitic capacitances of the transistors comprise both pn-junction capacitances (depletion capacitances) and capacitances with silicon oxide as dielectric material.

The depletion capacitance of a pn-junction represents the charge stored by the junction under specified bias conditions. Depending on the applied forward voltage V, this capacitance can be calculated as [Reisch 03]:

$$c_j(V) = \frac{C_{J0}}{(1 - V/V_J)^M}$$

(2.14)

where  $V_J$  is the so-called built-in voltage and  $C_{J0}$  is the depletion capacitance at V=0 V. The exponent M depends on the doping profile of the pn-junction. For abrupt pnjunctions M equals 1/2 and for linear graded pn-junctions it is 1/3. Equation (2.14) is not valid for forward bias voltages greater than  $V_J/2$ . If  $V=V_J$ , (2.14) predicts that  $c_J(V)$ approaches infinity. As an approximation, the simulation program SPICE calculates  $c_J(V)$  for  $V > V_J/2$  by a linear extrapolation of (2.14).

The contact regions of the transistor are separated by silicon oxide. These regions also represent parasitic capacitances, which are modeled by splitting the capacitances into area and perimeter specific parameters.

## 2.3 Transistor Effects

#### 2.3.1 The Early Effect

The Early effect [Early 52] represents changes of the base-emitter and the base-collector junctions for different bias conditions. Especially an increase in the collector-base reverse bias voltage results in a wider BC depletion region and hence the width of the neutral base is reduced. This causes a steeper gradient of injected minority carriers. Consequently, an increase in collector-base reverse bias voltage leads to an increase in collector current. So the Early effect is observed as a non-zero output conductance. It is modeled by the Early voltage  $V_{AF}$ , see (2.1), which is the extrapolated intercept of the collector current

$I_C$  data with the collector-emitter voltage axis. The Early effect is also called "base width modulation".

#### 2.3.2 The Kirk Effect

The Kirk effect [Kirk 62] originates from the finite drift velocity of the electrons in the base-collector depletion region. At high collector currents, an additional negative space charge is present in the depletion region, which partly compensates the positive ionized donors in the n-type side of the depletion region. If the electron density is higher than the doping density, majority carriers from the base can move into the collector region, because there is no negative space charge that forces holes to stay in the base region. The dipole formed by the positively and negatively charged ionized donors and acceptors is pushed into the collector and replaced by positively charged ionized donors and a negatively charged electron accumulation layer. So the effective base width as well as the base transit time are increased substantially, which causes current gain and cutoff frequency to decrease. Increasing the collector doping can shift the Kirk effect towards higher currents. However, this also increases the base-collector capacitance and decreases the collector-base breakdown voltage. The Kirk effect is also referred to as "base-pushout".

#### 2.3.3 Quasi Saturation

Quasi-saturation [Kull 85] is an effect that occurs at high currents due to the collector resistance of the bipolar transistor. In forward operation, the BC diode is reverse biased  $(V_{BC} < 0 \text{ V})$ . If the voltage drop over the collector resistance is large enough, the BC diode can be forward biased even though it is externally reverse biased. Then holes are injected into the collector region, the base current increases, and  $\beta$  decreases. Due to the increasing base-collector capacitance, the transit frequency  $f_T$  decreases when quasi-saturation sets in.

#### 2.3.4 Emitter Current Crowding

Emitter current crowding occurs at high collector currents. The also high DC base current produces a lateral voltage drop in the base, so the BE diode is more forward biased at the edges of the emitter. This leads to a higher collector current at the edges of the emitter in comparison to the middle of the active area. Therefore the effective distance from the base contact to the active area is reduced and consequently the base resistance is reduced.

#### 2.3.5 Base Conductivity Modulation

At high transfer currents, the concentration of injected electrons into the base is comparable with the doping level in the base. This causes an increase in the hole diffusion charge in the base because the majority carriers in the base, the holes, neutralize the injected charge. This process is called dielectric relaxation. Due to the higher hole density, the conductivity of the base region is increased which reduces the lateral voltage drop. So, the base conductivity modulation effect and the emitter current crowding effect counteract each other, but both effects reduce  $R_B$ .

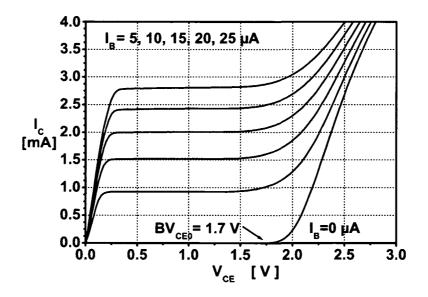

## 2.4 Electrical Characteristics

Figure 2.8 shows the common emitter DC output characteristics of transistors with an emitter area of  $0.14 \times 2.6 \,\mu\text{m}^2$ . The collector-emitter breakdown voltage  $BV_{CE0}$ , which is measured with open base, is 1.7 V and the open-emitter collector-base breakdown voltage  $BV_{CB0}$  is 5.8 V. The maximum sustainable operating voltage of a SiGe HBT generally lies between  $BV_{CE0}$  (worst case) and  $BV_{CB0}$  (best case).

Figure 2.8: Output characteristics  $(A_E = 0.14 \times 2.6 \,\mu\text{m}^2)$

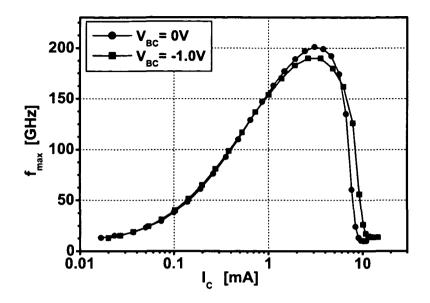

The high-frequency performance of the SiGe HBTs has been evaluated using S-parameter measurements up to 30 GHz. The cutoff frequency  $f_T$  has been extrapolated from the small signal current gain using transistors with an emitter area of  $0.14 \times 2.6 \,\mu\text{m}^2$ . Figure 2.9 shows the dependency of cutoff frequency  $f_T$  on the collector current  $I_C$  for different base-collector voltages  $V_{BC}$ . The transit frequency reaches its maximum of 200 GHz at  $V_{BC} = 0$  V and a collector current density of about  $8 \,\text{mA}/\mu\text{m}^2$ .

Figure 2.9: Cutoff frequency  $f_T$  vs. collector current  $I_C$   $(A_E = 0.14 \times 2.6 \,\mu\text{m}^2)$

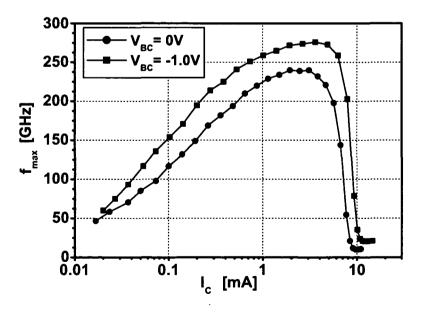

The maximum oscillation frequency  $f_{max}$  has been extrapolated from Mason's unilateral gain at 25 GHz with a slope of -20 dB/dec. Figure 2.10 shows the dependency of the maximum oscillation frequency on collector current. At  $V_{BC} = -1 \text{ V}$  the maximum oscillation frequency peaks at 275 GHz.

The high values of  $f_{max}$  originate from the integration of the thin base layer into a self-aligned transistor architecture providing low capacitances and extrinsic series resistances as well as a careful optimization of the highly boron doped base for achieving

Figure 2.10: Maximum oscillation frequency  $f_{max}$  vs. collector current  $I_C$  ( $A_E = 0.14 \times 2.6 \,\mu\text{m}^2$ )

simultaneously high cutoff frequency and low base sheet resistance. Table 2.1 summarizes the most important transistor parameters. The tradeoffs between these transistor parameters have been optimized for a balanced compromise to enable high-frequency circuit applications. The high values of cutoff frequency have been combined with a low base resistance  $R_B$  of 50  $\Omega$ . The values for emitter-base capacitance  $C_{EB}$ , base-collector capacitance  $C_{BC}$  and collector-substrate capacitance  $C_{CS}$  in Tab. 2.1 refer to unbiased junctions and include the wiring parasitic capacitances up to the first metallization layer. Taking into account the high base and collector doping levels, which have been employed in the technology for achieving high cutoff frequency, high current carrying capability, and low base resistance, the double-polysilicon self-aligned emitter-base configuration has provided reasonable low values for emitter-base and base-collector capacitances of 6.3 fF and 5.5 fF, respectively.

| $A_E$             | $0.14 \times 2.6~\mu\mathrm{m}^2$ |

|-------------------|-----------------------------------|

| β                 | 250                               |

| $R_{BI}$          | $2.8\mathrm{k}\Omega/\Box$        |

| $BV_{CE0}$        | 1.7 V                             |

| BV <sub>CB0</sub> | $5.8\mathrm{V}$                   |

| $C_{EB}$          | $6.3\mathrm{fF}$                  |

| $C_{BC}$          | $5.5\mathrm{fF}$                  |

| $C_{CS}$          | $3.7\mathrm{fF}$                  |

| $R_B$             | $50\Omega$                        |

| $R_E$             | $3.5\Omega$                       |

| $R_C$             | $7.5\Omega$                       |

| $f_T$             | $200\mathrm{GHz}$                 |

| $f_{max}$         | $275\mathrm{GHz}$                 |

| gate delay        | $3.5\mathrm{ps}$                  |

Table 2.1: Device parameters

#### **Transistor Geometries**

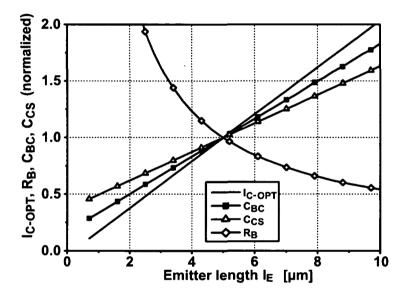

Design packages usually provide transistors with different geometries. The choice of the correct transistor geometry is of great importance in order to minimize the influence of parasitic capacitances and resistances. In case of maximizing the high frequency capability of the transistor, the optimum collector current  $I_{C-OPT}$  is defined by the effective emitter area and the collector current density at maximum cutoff frequency. In this case, the emitter width is usually chosen as small as possible, according to the design rules, in order to assure the lowest base resistance which is possible. The emitter length results from the desired collector current.

For transistors with a low emitter length the area ratio of the "external" to the "internal" transistor becomes worse. But in order to guarantee low power dissipation, collector currents must be kept low which leads to a low emitter length. For high operation frequencies the collector current must be chosen high enough, because parasitic capacitances must be charged very fast. In Fig. 2.11 the optimum collector current, the parasitic base-collector capacitance, the collector-substrate capacitance and the base resistance are compared at different emitter lengths. The diagram is normalized to the values of a transistor with an emitter length of  $5 \,\mu$ m. In Fig. 2.11 it can be seen, that for decreasing the emitter length, parasitic capacitances do not decrease as much as the maximum collector current. So, the high frequency behavior of transistors with a low emitter length is dominated by these parasitics.

Figure 2.11: Optimum collector current  $I_{C-OPT}$ , total base resistance  $R_B$ , total basecollector capacitance  $C_{BC}$ , and the collector-substrate capacitance  $C_{CS}$  vs. emitter length (normalized to an emitter length of  $5 \,\mu$ m)

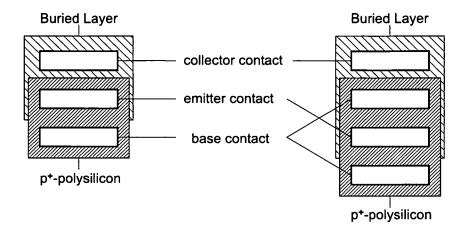

Base, emitter and collector contacts can be arranged in various ways, as long as design rules of the technology are fulfilled. For bipolar transistors the contacts are typically arranged as parallel bars, because this configuration exhibits a good tradeoff between all transistor parameters. Figure 2.12 shows transistors with one and two base contacts with a contact formation of BEC and BEBC, respectively. The double base transistor (BEBC) shows a reduced base resistance compared to the single base transistor (BEC), because the base is contacted from both sides. However the base-collector capacitance of this configuration is higher, because there is a larger overlap between collector and base contact. The collector-substrate capacitance is increased as well, because of the larger buried layer area. Further, there is a higher collector contact resistance because the distance between active transistor and collector contact is enlarged. Table 2.2 shows the quantitative changes of the main parasitics if a double base transistor is used instead of a single base transistor. It is assumed that both transistors operate at the same bias

Figure 2.12: Single and double base transistor configuration [Knapp 99]

| $R_B$       | $\begin{array}{c} -10\% \ (l_E{=}2\mu{\rm m}) \\ -18\% \ (l_E{=}10\mu{\rm m}) \\ -35\% \ (l_E{=}20\mu{\rm m}) \end{array}$ |

|-------------|----------------------------------------------------------------------------------------------------------------------------|

| $C_{BC}$    | +10%                                                                                                                       |

| $C_{CS}$    | +15%                                                                                                                       |

| $R_C$ +25 % |                                                                                                                            |

Table 2.2: Difference of parasitics  $R_B$ ,  $C_{BC}$ ,  $C_{CS}$ , and  $R_C$  from transistors with BEBC and BEC configuration. The relative decrease of  $R_B$  depends on the emitter length  $l_E$ .

conditions and that the only technological difference is the configuration of the contacts.

Depending on the most important parameter of Tab. 2.2 for the particular circuit performance, the optimal transistor geometry and the optimum emitter area must be chosen. In general, the BEBC configuration should be chosen for very long transistors or if especially low base resistances are required. Transistors in low-noise amplifiers or the RF transistors in mixers, for example, should exhibit a low base resistance because of its contribution to the overall noise performance. In many digital circuits, instead,  $C_{BC}$  is the most sensitive parameter, especially if low power consumption is required. In such cases, the BEC transistor configuration should be chosen.

In many circuits there are transistors which collectors are connected, e.g. the transistors of a Gilbert Cell are connected crosswise or the transistors of emitter followers in fullydifferential circuits. In such cases, it is better to use the transistor configuration shown in Fig. 2.13 instead of two transistors with their collector connected via metallization layers. The transistor configuration in Fig. 2.13 consists of two transistors that use the same collector contact. This configuration exhibits a smaller buried layer area compared to the use of two separated transistors. This results in a decrease of the collector-substrate

Figure 2.13: Double-transistor with a BECEB contact configuration [Knapp 99]

capacitance of 30% to 45%. Other transistor parameters are not affected. Especially for emitter followers in differential circuits an additional inductivity between the collector contacts due to wiring can deteriorate the transfer function. This is avoided by the use of transistors with BECEB configuration. A further advantage is that the double-transistor of Fig. 2.13 requires less space.

## 2.5 Passive Devices

To enable high performance circuit applications several additional devices have been added to the high frequency npn transistor. Three types of resistors and a MIM capacitor are available. The poly-resistors are made of the p+-polysilicon base electrodes but with less boron doping which results in sheet resistances of  $150 \Omega/_{\Box}$  and  $1000 \Omega/_{\Box}$ , respectively. The high precision TaN metal resistor and the MIM capacitor are described in more detail in [Schwerd 03]. The TaN metal resistor is placed between the first and the second copper metallization layer and has a sheet resistance of  $20 \Omega/_{\Box}$ . The MIM capacitor has a specific capacitance of  $1.4 \text{ fF}/\mu m^2$  and is integrated between the second and third metallization layer. The MIM capacitor uses a 50 nm thick Al<sub>2</sub>O<sub>2</sub> dielectric layer which has been deposited by atomic layer deposition.

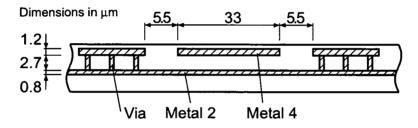

# 2.6 Metallization

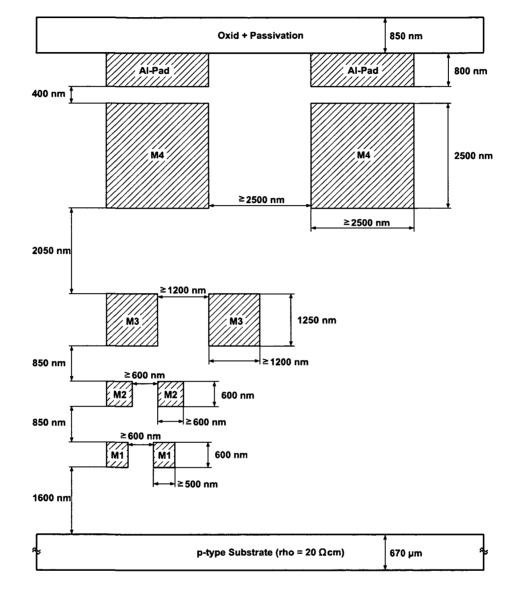

Figure 2.14 shows the metallization stack of Infineon's preproduction technology B10HF.

Figure 2.14: Schematic cross section of the metal layer stack including design rules

# Chapter 3

# Design of a Broadband Amplifier for 100 Gbit/s Data Signals

In this chapter a broadband amplifier in SiGe bipolar technology is presented. The amplifier is based on lumped elements and is designed for very high bit rate applications as well as for amplification of sinusoidal signals of very high frequencies. At first a short introduction and an overview of state-of-the art broadband amplifiers are given. Then important circuit characteristics are discussed before details of the circuit design are presented. Finally the layout and measurement results for sinusoidal signals and data signals are shown.

## 3.1 Introduction

In the last decade the demand on data communication has exploded and it is still growing. Innovative compression algorithms try to reduce the amount of data but they can not keep pace with the increasing volume of data traffic. Due to this trend, continuous development of communication systems towards higher bit rates is required.

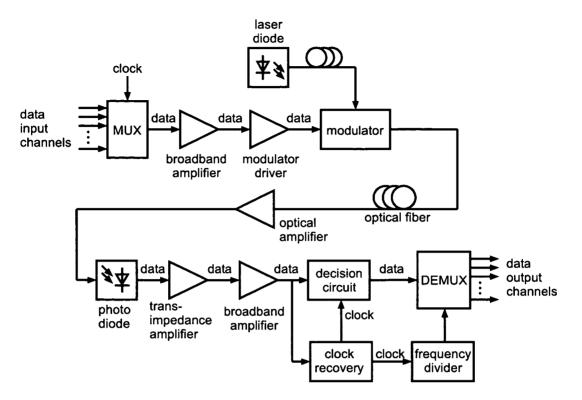

In Fig. 3.1 an optical communication system is shown. On top of the figure there is the transmitter which consists of a multiplexer (MUX), the modulator, and the laser. The multiplexer combines parallel data channels of low bit rate into one data stream of high bit rate by time division multiplex. The conversion of electrical into optical signals is done either by switching a laser on and off or by modulating a constant laser source. Optical transceivers for very high bit rates usually use a modulator because of its higher bandwidth. This modulator needs an excitation around 2 to 5  $V_{PP}$ . On this account the high bit rate data signal must be amplified with as little distortion on the signal waveform as possible.

Figure 3.1: Block diagram of an optical transmission system

The modulated light is injected into an optical fiber which transmits the light to the receiver. In wide area networks, optical fiber amplifiers are used in order to enhance the maximum distance between transmitter and receiver.

At the receiver a photodiode converts the high bit rate optical data stream back into an electrical signal. A transimpedance amplifier provides low-noise amplification of the data sequence. The subsequent amplifier is used for further amplification and for limiting the amplitude, which is done by either automatic gain control or by operation in the limiting mode. This signal is sampled and digitized in the decision circuit and then separated into its original, low bit rate data signals in the demultiplexer (DEMUX). The clock signals for the decision circuit and the demultiplexer are generated by the clock recovery unit and a frequency divider, respectively.

The performance of the transmission system is basically defined by the analog components (transimpedance amplifier, modulator driver and broadband amplifier) and the optoelectronic interconnections (modulator and photodiode). Digital circuits have been published so far up to much higher data rates, e.g. in [Meghelli 04a] a 4:1 multiplexer up to 108 Gbit/s, in [Wohlgemuth 04] a demultiplexer up to 86 GHz and in [Rylyakov 04] and [Knapp 03] state-of-the-art static frequency dividers are shown. In [Meghelli 04b], [Reinhold 01], and [Wurzer 98] clock recovery systems up to a data rate of 43 Gbit/s and 40 Gbit/s, respectively, are presented. These circuits have been fabricated in siliconbased technologies. Analog building blocks have not reached such high data rates up to now. In [Weiner 04] a SiGe transimpedance amplifier with a measured output data stream of  $40 \,\text{Gbit/s}$  is presented. Broadband amplifiers and modulator drivers are reported also for data rates up to slightly more than  $40 \,\text{Gbit/s}$ . An overview of state-of-the-art broadband amplifiers is given in Tab. 3.1.

The aim of this work is the design and optimization of broadband amplifiers based on lumped elements using an advanced SiGe bipolar technology. The amplifier is intended as preamplifier of high bit rate data streams either in front of the modulator driver or in front of the decision circuit or the clock recovery, see Fig. 3.1. In this field of applications the amplifier should provide clear data signals with sufficiently high amplitude.

Another application area is the amplification of single-frequency signals like the clock signals in Fig. 3.1. Although these signals are narrow-band, a broadband amplifier is advantageous. Especially in the development stage the system is tested with various clock rates, so a broadband amplifier with a high bandwidth covers the whole frequency range.

Further fields of application are as linear amplifier in conventional high frequency systems. The amplifier is also applicable in ultra wideband (UWB) communication systems like orthogonal frequency division multiplex (OFDM) systems for terrestrial TV tuners or wideband radar detectors.

## 3.1.1 State of the Art

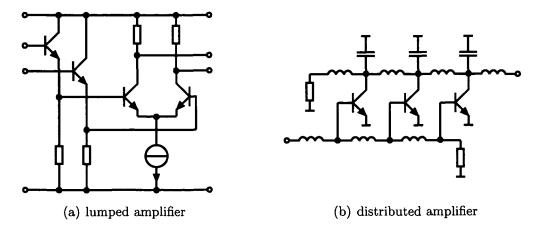

Broadband amplifiers are either based on a lumped or on a distributed concept. In Section 3.2 the two concepts are discussed. In this section outstanding results for broadband amplifiers of both concepts are mentioned and an overview of state-of-the-art amplifiers is given.

In Tab. 3.1 published broadband amplifiers are compared. In the upper part of the table, lumped broadband amplifiers are listed. The lower part of the table gives results for broadband amplifiers based on a distributed concept.

Broadband amplifiers based on lumped elements are presented in [Wohlgemuth 03], [Baeyens 02], and [Choudhury 04]. In [Wohlgemuth 03] an amplifier using SiGe hetero junction bipolar transistors (HBTs) is presented which exhibits a gain of 36 dB and a bandwidth of 26 GHz. An InP HBT amplifier is described in [Baeyens 02] with 21 dB gain and 38 GHz bandwidth. Another InP HBT based wideband amplifier with bessel transfer function, a gain of 11 dB, and a bandwidth of more than 50 GHz is presented in [Choudhury 04].

Broadband amplifiers based on distributed concepts using InP high electron mobility transistors (HEMTs) are presented in [Masuda 02] and [Meliani 02] and exhibit a bandwidth of more than 110 GHz and 92 GHz, respectively. The highest bandwidth of a

distributed amplifier using SiGe HBTs reaches a bandwidth of 80 GHz [Wohlgemuth 03]. In the summary of this chapter the results achieved in this work are compared with the state of the art.

| Reference       | measured<br>3-db<br>bandwidth | measured<br>gain | measured<br>eye<br>diagram | Technology  |

|-----------------|-------------------------------|------------------|----------------------------|-------------|

|                 | [GHz]                         | [dB]             | [Gbit/s]                   |             |

| [Lao 97]        | 30                            | 36               |                            | GaAs HEMT   |

| [Krishnan 00]   | 80                            | 8.2              |                            | InAs HBT    |

| [Krishnan 00]   | 50                            | 18               |                            | InAs HBT    |

| [Ohhata 01]     | 47.8                          | 21.5             | 40                         | GaAs HEMT   |

| [Baeyens 02]    | 38                            | 21               | 40                         | InP HBT     |

| [Freeman 02]    | 35                            | 28               | 40                         | SiGe BiCMOS |

| [Toifl 03]      | 23                            | 18               | 30                         | CMOS        |

| [Wohlgemuth 03] | 26                            | 36               | 43                         | SiGe HBT    |

| [Choudhury 04]  | 50                            | 11               |                            | InP HBT     |

| [Krishnan 00]   | 80                            | 11.5             |                            | InAs HBT    |

| [Leich 01]      | 66                            | 12               | 40                         | GaAs HEMT   |

| [Baeyens 02]    | 80                            | 25               |                            | InP HBT     |

| [Baeyens 02]    | 58                            | 15               | 40                         | InP HBT     |

| [Masuda 02]     | 110                           | 7.5              | _                          | InP HEMT    |

| [Masuda 02]     | 94                            | 14.5             |                            | InP HEMT    |

| [Meliani 02]    | 92                            | 13               |                            | InP HEMT    |

| [Wohlgemuth 03] | 81                            | 13               |                            | SiGe HBT    |

| [Wohlgemuth 03] | 37                            | 27               | 43                         | SiGe HBT    |

| [Shigematsu 04] | 39                            | 4                | 40                         | CMOS        |

| [Kim 04]        | 90                            | 11               |                            | CMOS        |

| Table 3.1: Comparison of state-of-the-art monolithical integrated broadband amplifiers.     |

|---------------------------------------------------------------------------------------------|

| In the upper part of the table lumped amplifiers are listed, in the lower part of the table |

| data for distributed broadband amplifiers is given.                                         |

## 3.1.2 Specification of Circuit Parameters

In this work a broadband amplifier for multiple applications is designed. The amplifier should be applicable for high bit rate data streams, as well as high frequency sinusoidal signals and ultra-wideband signals. Due to different fields of applications, tradeoffs between circuit parameters are necessary. The most important requirements for the broadband amplifier of this work are:

1. Differential gain =  $16 \, dB$ :

High Gain and high bandwidth are contradicting requirements. In this design the bandwidth of the amplifier is optimized for a differential gain of 16 dB.

2. Bandwidth:

High bandwidth is of particular importance in the case of amplifying sinusoidal signals of high frequencies, for example, clock signals. In digital applications a gradual decrease of the gain opposed to high bandwidth often avoids excessive group delay peaking and deteriorated eye diagrams. Therefore, in this work bandwidth is maximized after specification of a transfer characteristic.

3. Frequency response:

In this work, a Butterworth characteristic is chosen as frequency response since it is a good compromise between high bandwidth and small overshoot of the step response in the time domain.

4. Output Voltage Swing  $\geq 1 V_{PP}$ :

A high output voltage swing is required for excitation of the modulator driver. Recent developments of electroabsorption modulators tend to driving voltages of 1.1 V [Fukano 04], so a broadband amplifier with high output voltage swing can replace the modulator driver.

5. Data rate  $\geq 80 \, \text{Gbit/s:}$

The aim of this development is to reach clear output eye diagrams at a bit rate of 80 Gbit/s or more.

- 6. Matching at input and output: Due to the high operation frequency and the high bandwidth, matching at the input and the output is required within the whole frequency range.

- 7. Linearity:

If the broadband amplifier is used as linear amplifier a high 1-dB compression point and a high 3<sup>rd</sup>-order intercept point are desirable. High linearity can be achieved more easily in combination with a high output voltage swing.

8. Supply Voltage:

A negative supply voltage of -5 V is chosen.

# **3.2** Fundamental Circuit Characteristics

## 3.2.1 Broadband Amplifier Concepts

Basically, there are two concepts on which broadband amplifiers can be based on, see Fig. 3.2. The lumped broadband amplifier, shown in Fig. 3.2(a) consists of one or several stages of emitter follower and differential amplifier combinations. The total gain of lumped amplifiers is the product of the gain of each stage. However, the overall bandwidth is less than the bandwidth of each stage because the gain fall-off in each stage will accumulate. The inherent parasitic capacitances of the transistors cause the bandwidth limitation in broadband amplifiers.

An approach to increase the bandwidth of broadband amplifiers is distributed amplification [Wong 93]. A distributed amplifier, see Fig. 3.2(b), consists of gain stages which are separated by transmission lines. The total gain of distributed amplifiers is the sum of the gain of each stage. Distributed amplifiers obtain high bandwidth by absorbing the transistor capacitances into a synthetic transmission line at the input and at the output. Equal delays of the input and output transmission line are required, so that the output currents of the stages are added in-phase at the load. Since input capacitances are usually larger than output capacitances, additional capacitances at the output line are necessary. In the absence of loss, the gain-bandwidth product of the amplifier can be improved arbitrarily by increasing the number of stages. In practice, the improvement is limited by the loss of the transmission line, which is composed of the loss in each transmission line segment between the stages and the input resistance of the transistors. Due to the parasitic base resistance of bipolar transistors the distributed concept is particularly suitable for field-effect based devices, like CMOS transistors or HEMT's.

The design of distributed amplifiers requires careful electromagnetic simulations and very accurate modeling of transistor parasitics in order to obtain a constant gain. It is very

Figure 3.2: Basic concepts of broadband amplifiers

difficult to simultaneously yield a linear phase over the pass-band which is required in order to avoid distortion of data signals.

A disadvantage of distributed amplifiers is that there is a DC level at the input and output line which involves AC coupling. From this it follows that there is a lower cutoff frequency, so distributed amplifiers do not work at DC or low frequencies. In order to yield high gain with distributed amplifiers, many stages are required since the gain is added from all stages as compared to lumped amplifiers where the gain of all stages is multiplied. Distributed amplifiers often exhibit a very sharp gain fall-off which leads to excessive group delay peaking and deteriorated eye diagrams.

Due to the wide-spread field of applications the amplifier of this work is intended for, a concept based on lumped elements is chosen. The main difficulties are to maximize the bandwidth of the circuit at a predefined gain.

#### 3.2.2 Frequency Response

A broadband amplifier should exhibit a near-constant gain and linear phase in the passband at a high bandwidth. Between these requirements a compromise is necessary. Constant gain at high bandwidth causes group delay peaking. A flat group delay (=linear phase) results in a slowly decaying gain, which can only be realized at a lower bandwidth. In this work, Butterworth characteristic is chosen as frequency response since it is a good compromise between high bandwidth, a flat group delay, and a small overshoot of the step response in the time domain. Above all, a differential amplifier with emitter followers at its input shows a frequency response which is similar to the Butterworth characteristic.

The frequency response |H(f)| of a Butterworth low-pass filter at a frequency f can be calculated as

$$|H(f)|^{2} = 10 \log\left(\frac{1}{1 + (f/f_{c})^{2n}}\right)$$

(3.1)

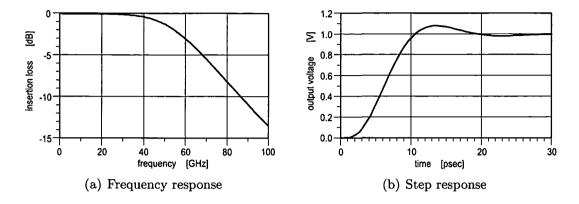

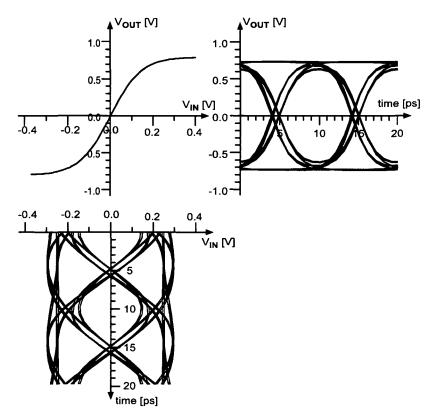

where  $f_c$  denotes the 3-dB bandwidth and n is the order of the filter. In Fig. 3.3(a) this frequency response and the step response for a  $3^{rd}$ -order Butterworth filter with a bandwidth of 60 GHz are plotted. The step response of the Butterworth filter exhibits overshoot depending on the filter order, see Tab. 3.2.

In Fig. 3.4 simulated output eye diagrams at a data rate of 100 Gbit/s from a transmission system with a Butterworth transfer characteristic of  $3^{rd}$ -order are shown for different filter bandwidths. It can be seen that a filter-bandwidth to data rate ratio of 2:3 is sufficient for obtaining clear eye diagrams. Further, an increase of the time-jitter at the zero-crossings at lower filter bandwidths can be observed.

Figure 3.3: Simulated frequency response and step response of a  $3^{rd}$ -order Butterworth filter with a 3-dB bandwidth of 60 GHz

Figure 3.4: Simulated 100 Gbit/s eye diagrams at the output of a system with a Butterworth transfer characteristic (filter order = 3, filter bandwidth = 40, 60, 80 and 100 GHz)

| Filter order | Overshoot |  |

|--------------|-----------|--|

| 2            | 4%        |  |

| 4            | 11%       |  |

| 6            | 14%       |  |

| 8            | 16%       |  |

Table 3.2: Time-domain performance comparison of Butterworth low-pass filters with different order [Horowitz 89]

## 3.2.3 Operation in Limiting Mode

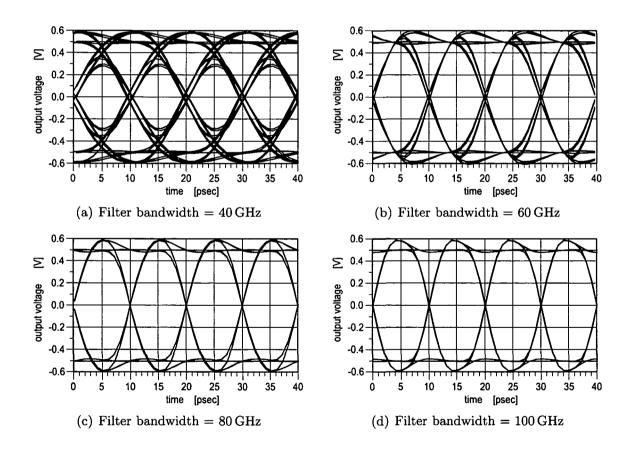

A typical transfer characteristic of an amplifier is shown in Fig. 3.5. In the case of small signal excitation the amplifier exhibits an almost linear behavior. In case of high amplitudes, the top and bottom portions of the waveform are clipped. This property can be beneficial for amplification of distorted data signals. In Fig. 3.5 regeneration of a distorted data signal is provided by operation of the amplifier in limiting mode.

Figure 3.5: Differential amplifier in limiting mode

#### 3.2.4 Linearity

In the case of small signal excitation the amplifier can be treated in good approximation as linear circuit. The limits of the linear operation region are characterized by the 1-dB compression point and the 3<sup>rd</sup>-order intercept point, which are the most common measures of linearity. A nonlinear transfer function can be written as series expansion:

$$v_{OUT}(t) = k_0 + k_1 v_{IN}(t) + k_2 v_{IN}^2(t) + k_3 v_{IN}^3(t) + \dots$$

(3.2)

In the following calculations (3.2) is assumed as a noninverting function with compression at high signal amplitudes V, which results in  $k_1 > 0$  and  $k_3 < 0$ . Due to the nonlinear behavior, harmonics and mixing products occur at the device output at signal frequencies of  $2\omega_1, 2\omega_2, 3\omega_1, 3\omega_2, \omega_1 \pm \omega_2, 2\omega_1 \pm \omega_2, 2\omega_2 \pm \omega_1, \ldots$ . Harmonics and even order mixing products are uncritical because they can be easily filtered out. Of all unwanted terms, mixing frequencies  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  are the most troublesome, since they are near the signal frequencies, if  $\omega_1$  is close to  $\omega_2$ . Table 3.3 shows amplitudes of signal components of the output of a nonlinear device excited by a single or double tone input signal. For this calculation the first three terms of the series expansion are considered.

| frequency              | $v_{IN} = V \left[ \cos(\omega_1 t) + \cos(\omega_2 t) \right]$ | $v_{IN} = V \cos(\omega t)$ |  |

|------------------------|-----------------------------------------------------------------|-----------------------------|--|

| DC                     | $k_0 + k_2 V^2$                                                 | $k_0 + \frac{1}{2}k_2 V^2$  |  |

| $\omega_1$             | $k_1 V + rac{9}{4} k_3 V^3$                                    | $k_1V+rac{3}{4}k_3V^3$     |  |

| $\omega_2$             | - 4 -                                                           | - 4                         |  |

| $2\omega_1 - \omega_2$ | $\frac{3}{4}  k_3  V^3$                                         |                             |  |

| $2\omega_2 - \omega_1$ | 4 [                                                             |                             |  |

Table 3.3: Amplitudes of frequency components of an output signal  $v_{out}$  for single and double tone excitation of a nonlinear function. The nonlinear behavior is described by a series expansion of third order, see (3.2).

#### 3.2.5 Third-Order Intercept Point

The third-order intercept point is measured by applying two signals with frequencies  $\omega_1$ and  $\omega_2$  and equal amplitudes to the circuit. The third-order intercept point (IP3) is a theoretical point either referred to the input or the output where the output amplitudes of the intermodulation tones at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  are equal to the amplitudes of the fundamental tones at  $\omega_1$  and  $\omega_2$ . For small amplitudes V the fundamental tone rises linearly (20 dB/decade) and the intermodulation products of 3<sup>rd</sup>-order rise as the cube of the input (60 dB/decade). So the 3<sup>rd</sup>-order intercept point can be expressed as:

$$\frac{k_1 V}{\frac{3}{4} |k_3| V^3} = 1 \tag{3.3}$$

This can be solved for  $V = V_{IP3}$ :

$$V_{IP3} = 2 \sqrt{\frac{k_1}{3 |k_3|}} \tag{3.4}$$

where  $V_{IP3}$  is the input voltage at the 3<sup>rd</sup>-order intercept point.

#### **3.2.6** 1-dB Compression Point

The 1-dB compression point is measured by applying only one signal to the circuit. The 1-dB compression point is the power level, referred to the input or the output, where the output power is 1 dB less than it would have been with an ideally linear device. The input voltage at the 1-dB compression point can be calculated as the ratio of the real to the ideal amplitude of the fundamental tone:

$$\frac{k_1 V + \frac{3}{4} k_3 V^3}{k_1 V} = 0.89125 \tag{3.5}$$

where 0.89125 corresponds to  $-1 \,dB$ . Provided that  $k_1 > 0$  and  $k_3 < 0$  the voltage  $V = V_{1dB}$  results to:

$$V_{1dB} = 0.381 \sqrt{\frac{k_1}{|k_3|}} \tag{3.6}$$

Note that this analysis is valid for third order nonlinearity. For higher order nonlinearities additional components occur. Third order approximation gives a good estimate of the behavior.

#### 3.2.7 Relationship between 1-dB Compression and IP3 Points

The relationship between the 1-dB compression point and the IP3 can be derived from (3.4) and (3.6) as:

$$\frac{V_{IP3}}{V_{1dB}} = \frac{2\sqrt{\frac{k_1}{3|k_3|}}}{0.381\sqrt{\frac{k_1}{|k_3|}}} = 3.04 \triangleq 9.66 \,\mathrm{dB}$$

(3.7)

The voltage ratio of 3.04 corresponds to approximately 10 dB. So it is a good estimate that the IP3 is about 10 dB higher than the 1-dB compression point.

## 3.3 Circuit Design

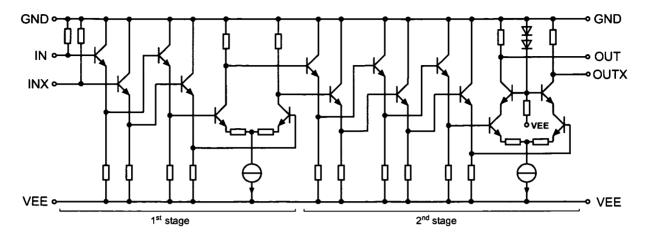

The broadband amplifier in this work consists of two stages. Each stage comprises a differential amplifier with emitter followers at its input. At first, a differential amplifier is analyzed with one, two, and three emitter followers at the input. Then the design of the two stage amplifier is shown.

Emitter followers are often used as a buffer circuit due to the high input impedance and the low output impedance at a almost unity gain. In [Gray 84] the input and output impedances of the emitter follower as a function of frequency are derived for resistive source and load termination. It is calculated that the input impedance appears capacitively and that the output can show inductive behavior. This inductive output behavior can result in resonances, especially when capacitive loads are driven. This resonances can be used in order to increase the bandwidth of the whole stage. The size of the transistors and their current densities must be carefully optimized in order to yield a high bandwidth and in order to avoid resonant peaks in the frequency response.

#### Differential Amplifier with one Emitter Follower

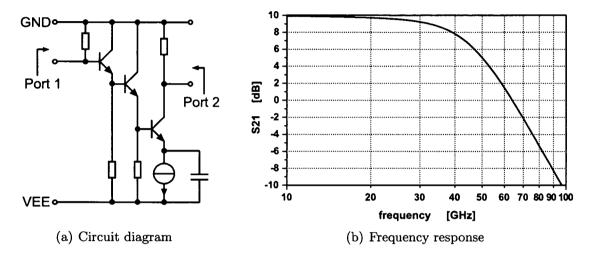

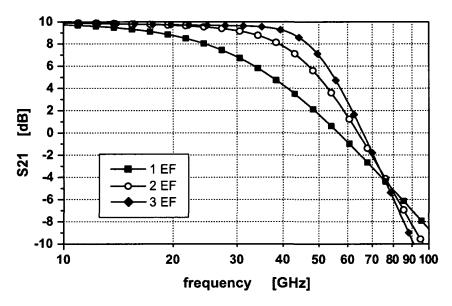

In Fig. 3.6 the circuit diagram and the frequency response of a differential amplifier with one emitter follower at its input is shown. In this and the following representations an equivalent half-circuit of the fully differential circuit is simulated. The circuits of Fig. 3.6, Fig. 3.7, and Fig. 3.8 are designed for equal gain and equal output voltage swing. The 3-dB bandwidth of the circuit in Fig. 3.6 is simulated to 29.3 GHz.

Figure 3.6: Differential amplifier with one emitter follower

#### Differential Amplifier with two Emitter Followers

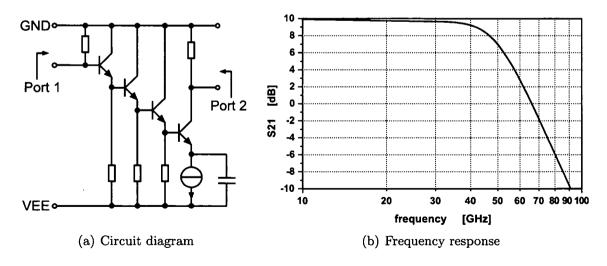

In Fig. 3.7 the circuit diagram and the frequency response of a differential amplifier with two emitter followers at its input is shown. The 3-dB bandwidth of this circuit is simulated to 43.3 GHz.

Figure 3.7: Differential amplifier with two emitter followers

#### Differential Amplifier with three Emitter Followers

In Fig. 3.8 the circuit diagram and the frequency response of a differential amplifier with three emitter followers at its input is shown. In this case the 3-dB bandwidth results to 49.9 GHz.

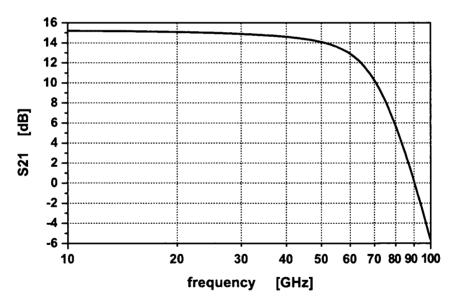

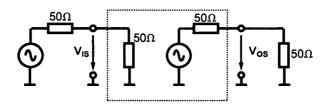

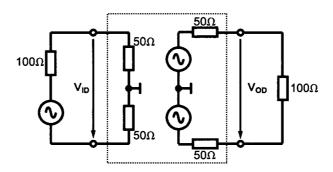

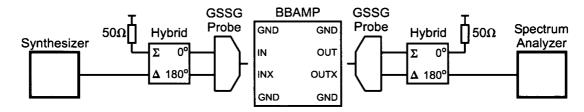

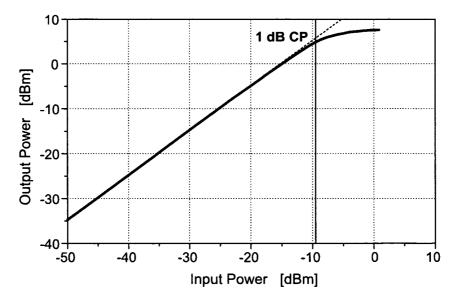

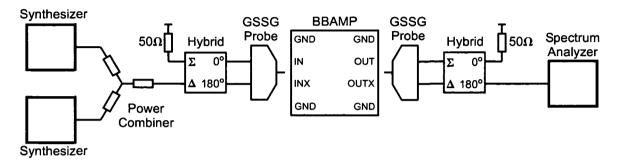

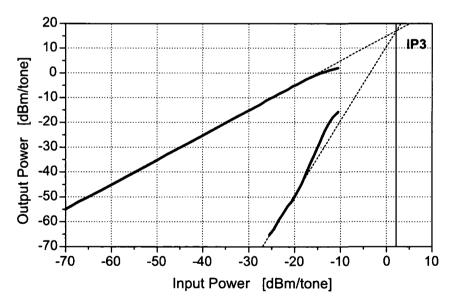

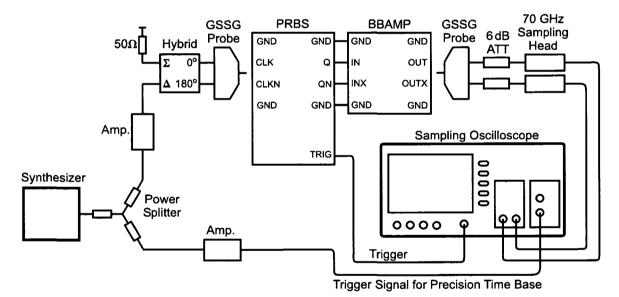

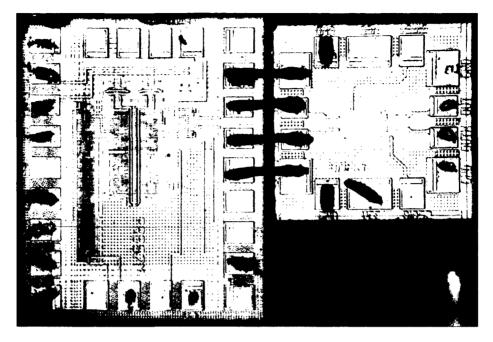

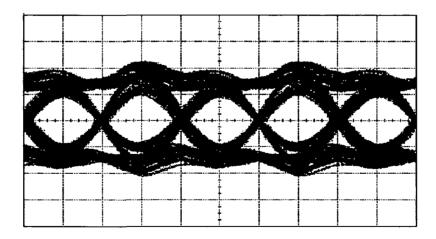

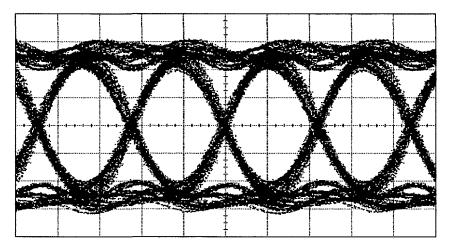

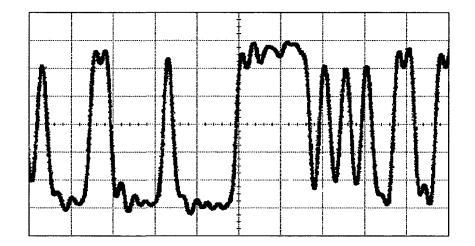

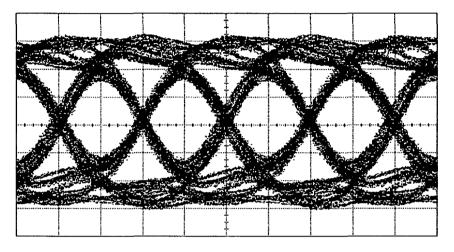

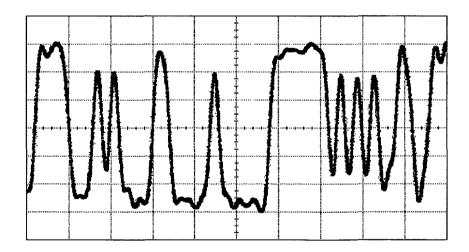

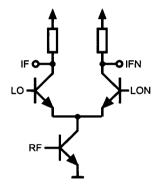

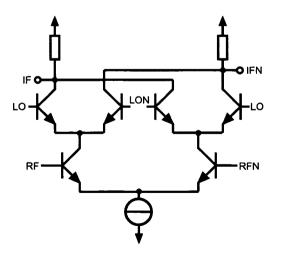

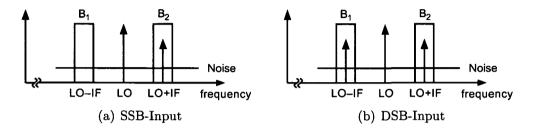

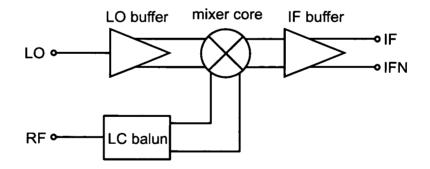

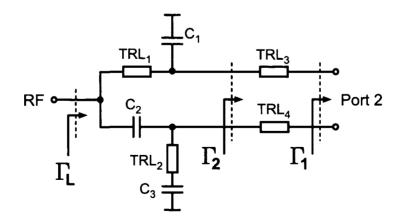

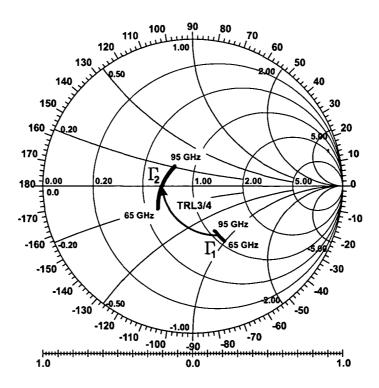

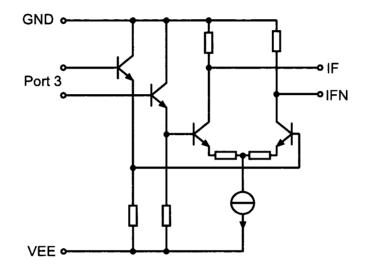

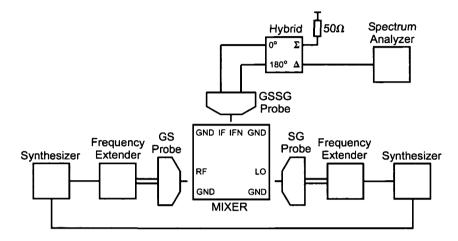

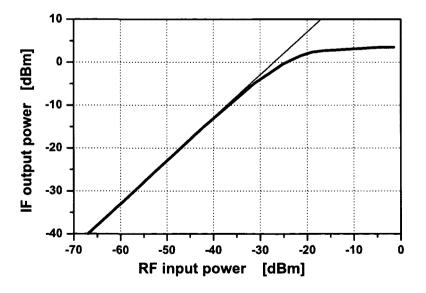

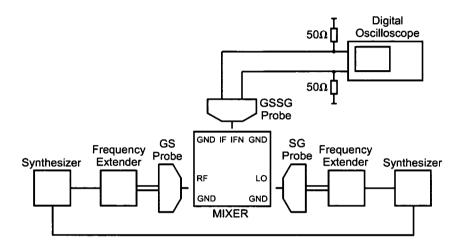

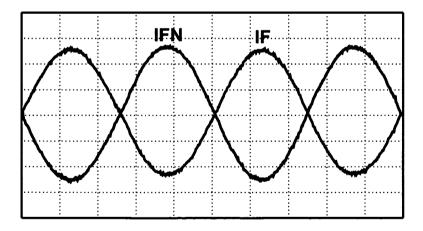

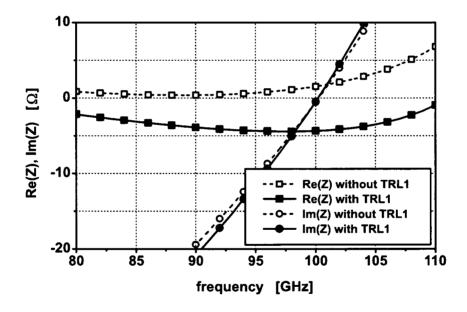

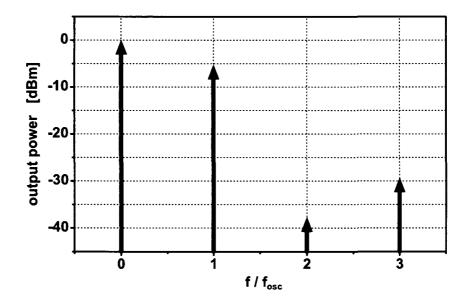

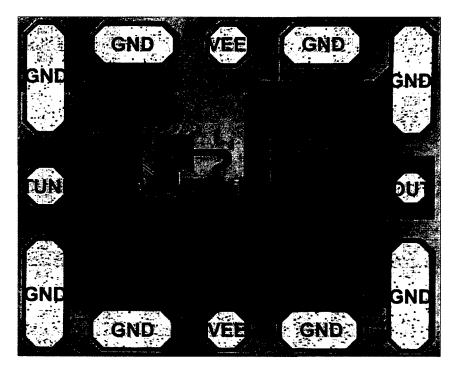

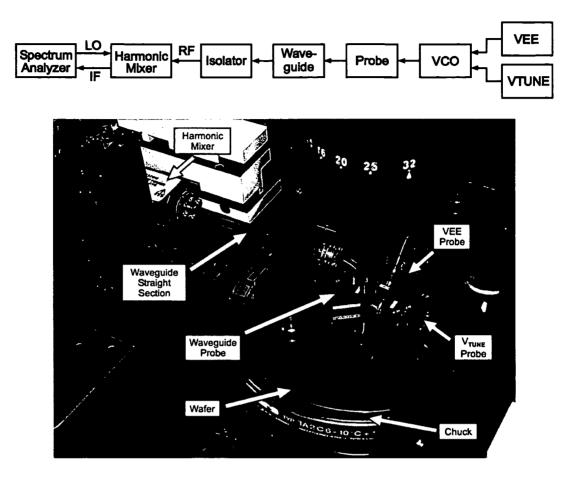

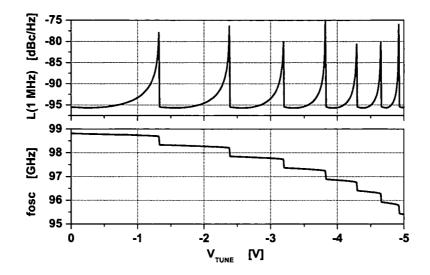

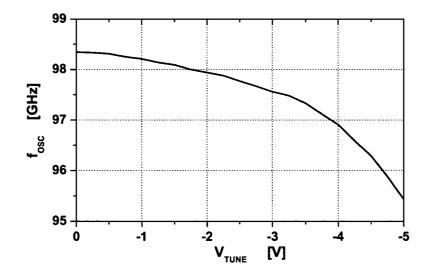

Figure 3.8: Differential amplifier with three emitter followers