## Dissertation

# Automatic SIMD Vectorization

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Ao. Univ.-Prof. Dipl.-Ing. Dr. techn. Christoph W. Überhuber E101 – Institut für Analysis und Scientific Computing

> eingereicht an der Technischen Universität Wien Fakultät für Informatik

> > von

## Dipl.-Ing. Jürgen Lorenz

Matrikelnummer 9525135 Zenogasse 3/4 1120 Wien

Wien, am 16. März 2004

for long

## Kurzfassung

Automatisch generierter numerischer Quellcode kann von handelsüblichen Compilern nicht optimal verarbeitet werden. Algorithmische Strukturen werden nur unzureichend erkannt und dementsprechend schlecht ausgenutzt. Es werden daher spezialisierte Compilertechniken benötigt um zu einem zufriedenstellend effizienten Zielcode zu gelangen.

Die immer weiter fortschreitende Zunahme der Bedeutung von Multimedia-Anwendungen hat zur Entwicklung von SIMD-Befehlssatzerweiterungen auf allen gängigen Mikroprozessoren geführt. Die konventionellen Vektorisierungsmethoden der handelsüblichen Compiler sind jedoch nicht in der Lage, Parallelismus in einem längeren numerischen Straight-Line-Code zu erkennen.

In dieser Dissertation werden Techniken, die speziell die Übersetzung numerischer Routinen zum Ziel haben, vorgestellt. Die *automatische 2-fach-SIMD-Vektorisierung* entdeckt den in einer Routine vorhandenen SIMD-Parallelismus und garantiert einen zufriedenstellenden Grad der Nutzung von SIMD-Befehlen. Die *Gucklock-Optimierung* ersetzt bestimmte Kombinationen von Instruktionen durch effizientere. Für den letzten Teil der Übersetzung werden *synthese-spefizische Techniken* eingesetzt, die deutlich zur Steigerung der Qualität des übersetzten Programmcodes – über das Maß handelsüblicher Übersetzer hinaus – beitragen.

Die in dieser Dissertation präsentierten Konzepte stellen die Grundlage des Special Purpose Compilers MAP [70, 71, 72, 73, 75] dar, der speziell für die effiziente Vektorisierung großer numerischer Straight-Line-Codes entwickelt wurde. MAP unterstützt die führenden automatischen Performance-Tuning-Softwareprodukte: FFTW<sup>1</sup>, SPIRAL<sup>2</sup> und ATLAS<sup>3</sup>. Damit werden die wichtigsten Algorithmen der numerischen linearen Algebra und der digitalen Signalverarbeitung abgedeckt.

Zu den praktischen Ergebnissen dieser Dissertation zählen: (i) die schnellsten derzeit verfügbaren FFT-Codes für AMD Athlon basierte Systeme; (ii) automatisch erzeugte FFT-Codes für den Intel Pentium 4, die vergleichbare Leistung wie die schnellsten handoptimierten Codes liefern und (iii) die schnellsten derzeit verfügbaren FFT-Codes für den IBM PowerPC 440 FP2 Prozessor, der im derzeit von IBM entwickelten Supercomputer BlueGene/L Verwendung findet.

Die experimentellen Resultate wurden durch Anwendung des MAP Special Purpose Compilers auf von FFTW (Frigo and Johnson [35]), SPIRAL (Moura et al. [88]) und ATLAS (Whaley et al. [115]) erzeugten Code erzielt.

<sup>&</sup>lt;sup>1</sup>FFTW ist die Abkürzung von "Fastest Fourier Transform in the West" (schnellste Fourier-Transformation des Westens).

<sup>&</sup>lt;sup>2</sup>SPIRAL ist die Abkürzung von "Signal Processing Algorithms Implementation Research for Adaptive Libraries" (Implementierungsforschung an Signalverarbeitungsalgorithmen für adaptive Software).

<sup>&</sup>lt;sup>3</sup>ATLAS ist die Abkürzung von "Automatically Tuned Linear Algebra Software" (automatisch angepasste Software für Probleme der Linearen Algebra).

## Summary

General purpose compilers produce suboptimal object code when applied to automatically generated numerical source code. Moreover, general purpose compilers have natural limits in deducing and utilizing information about the structure of the implemented algorithms. Specialized compilation techniques, as introduced in this thesis, are needed to realize such structural transformations.

Increasing focus on multimedia applications has resulted in the addition of short vector SIMD extensions to most existing general-purpose microprocessors. This added functionality comes primarily with the addition of short vector SIMD instructions. Unfortunately, access to these instructions is limited to proprietary language extensions, in-line assembly, and library calls. Generally, it has been assumed that vector compilers provide the most promising means of exploiting multimedia instructions. But although vectorization technology is well understood, it is inherently complex and fragile. Conventional vectorizers are incapable of locating SIMD style parallelism within a basic block without introducing unacceptably large overhead. Without the adoption of SIMD extensions, 50% to 75% of a machine's possible performance is wasted, even in conjunction with state-of-the-art performance tuning software. Automatic exploitation of SIMD instructions therefore requires new compiler technology.

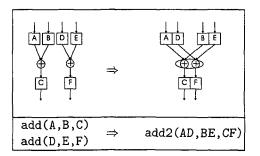

This thesis presents techniques tailor-made for the compilation of numerical straight line code: (i) Automatic 2-way SIMD vectorization extracts SIMD parallelism out of numerical straight line code in a way that guarantees a satisfactory level of SIMD utilization. (ii) Peephole optimization rewrites the SIMD vectorized code in a domain specific manner to further improve efficiency. (iii) Backend specific techniques are used for compiling the vectorized and optimized code, yielding object code whose performance is significantly better than the performance of code produced by general purpose compilers.

The new compiler techniques presented in this thesis form the basis of the "MAP Vectorizer and Backend" [70, 71, 72, 73, 75], a special purpose compiler, which was designed especially for the efficient vectorization and backend optimization of large basic blocks of numerical straight line code. MAP is currently applicable to the state-of-the-art performance tuning systems FFTW<sup>4</sup>, SPIRAL<sup>5</sup> and ATLAS<sup>6</sup>. Thus, MAP is covering a broad range of highly important algorithms in the fields of digital signal processing and numerical linear algebra.

The experimental results were obtained using the MAP vectorizer and backend in connection with FFTW [35], SPIRAL [88] and ATLAS [115].

<sup>&</sup>lt;sup>4</sup>FFTW is the abbreviation of "Fastest Fourier Transform in the West".

<sup>&</sup>lt;sup>5</sup>SPIRAL is the abbreviation of "Signal Processing Algorithms Implementation Research for Adaptive Libraries".

<sup>&</sup>lt;sup>6</sup>ATLAS is the abbreviation of "Automatically Tuned Linear Algebra Software".

# Contents

| K        | urzfas              | sung/Summary 2                            |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----------|---------------------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| In       | trodu               | <b>ction</b>                              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 1        | Hard                | ware vs. Algorithms                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 1.1                 | Current Hardware Trends                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 1.2                 | Performance Implications                  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 1.3                 | Automatic Performance Tuning              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| <b>2</b> | Stan                | dard Hardware                             |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 2.1                 | Processors                                |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 2.2                 | Advanced Architectural Features           |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 2.3                 | The Memory Hierarchy                      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3        | Shor                | t Vector Hardware                         |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 3.1                 | Short Vector Extensions                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 3.2                 | Intel's Streaming SIMD Extensions         |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 3.3                 | AMD's 3DNow!                              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 3.4                 | The IBM BlueGene/L Supercomputer          |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 3.5                 | Vector Computers vs. Short Vector SIMD    |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 4        | Fast                | Algorithms for Linear Transforms          |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 4.1                 | Discrete Linear Transforms                |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 5        | Mat                 | <b>ix Multiplication</b>                  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 5.1                 | The Problem Setting                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6        | A Portable SIMD API |                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 6.1                 | Definition of the Portable SIMD API       |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 7        | Auto                | matic Vectorization of Straight-Line Code |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.1                 | Vectorization of Straight Line Code       |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.2                 | The Vectorization Approach                |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.3                 | Benefits of The MAP Vectorizer            |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.4                 | Virtual Machine Models                    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.5                 | The Vectorization Engine                  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|          | 7.6                 | Pairing Rules                             |  |  |  |  |  |  |  |  |  |  |  |  |  |

## CONTENTS

| 8            | Rew                | riting and Optimization                 |

|--------------|--------------------|-----------------------------------------|

|              | 8.1                | Optimization Goals                      |

|              | 8.2                | Peephole Optimization                   |

|              | 8.3                | Transformation Rules                    |

|              | 8.4                | The Scheduler                           |

|              |                    |                                         |

| 9            | Bacl               | kend Techniques for Straight-Line Code  |

|              | 9.1                | Optimization Techniques Used in MAP     |

|              | 9.2                | Backend Optimization Goals              |

|              | 9.3                | One Time Optimizations                  |

|              | 9.4                | Feedback Driven Optimizations           |

| 10           |                    | 110                                     |

| 10           | -                  | erimental Results                       |

|              | 10.1               | Experimental Layout                     |

|              | 10.2               | BlueGene/L Experiments                  |

|              | 10.3               | Experiments on IA-32 Architectures      |

| C            | onclue             | sion and Outlook                        |

| Ŭ            | onera              |                                         |

| Α            | The                | Kronecker Product Formalism             |

|              | A.1                | Notation                                |

|              | A.2                | Extended Subvector Operations           |

|              | A.3                | Kronecker Products                      |

|              | A.4                | Stride Permutations                     |

|              | A.5                | Twiddle Factors and Diagonal Matrices   |

|              |                    |                                         |

| В            | Com                | piler Techniques                        |

|              | B.1                | Register Allocation and Memory Accesses |

|              | B.2                | Instruction Scheduling                  |

| C            | Donf               | ormance Assessment                      |

| U            |                    |                                         |

|              | C.1                | Short Vector Performance Measures       |

|              | C.2                | Empirical Performance Assessment        |

| D            | Shor               | t Vector Instruction Set                |

|              | D.1                | The Intel Streaming SIMD Extensions 2   |

|              | 2.1                |                                         |

| $\mathbf{E}$ | The                | Portable SIMD API                       |

|              | E.1                | Intel Streaming SIMD Extensions 2       |

|              | E.2                | BG/L Double FPU SIMD Extensions         |

|              | <b></b> , <b>~</b> |                                         |

| $\mathbf{F}$ | SPIF               | RAL Example Code                        |

|              | F.1                | Scalar C Code                           |

|              | F.2                | Short Vector Code                       |

|              |                    |                                         |

$\mathbf{5}$

### CONTENTS

| G  | $\mathbf{FFT}$ | W Exa  | ample  | $\mathbf{e} \mathbf{C}$ | ode | ) |   | • |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   | • |   |   |   |   | 175 |

|----|----------------|--------|--------|-------------------------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|    | G.1            | 000101 |        |                         |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|    | G.2            | Short  | Vecto  | r Co                    | ode | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | • | • | • | • | • | • |   | 176 |

| н  | ATL            | AS Ex  | ampl   | e C                     | od  | e |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 179 |

|    | H.1            | Scalar | · C Co | ode                     |     |   | • |   |   |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   | 179 |

|    | H.2            | Short  | Vecto  | r Co                    | ode | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | • | • | 181 |

| Ta | ble of         | f Abbr | reviat | ions                    | 5.  |   |   | • | • |   | • |   | • | • | • | • |   |   | • |   | • | • | • | • | • | • | • | • | • |   | 186 |

| Bi | bliogr         | aphy   |        |                         |     | • | • | • | • | • |   | • | • | • | • | • | • |   |   |   | • | • |   | • |   | • | • | • | • |   | 187 |

| Cu | urricu         | lum V  | itae   |                         | • • |   |   | • |   |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   | 197 |

## 6

## Acknowledgements

First of all, I would like to express my sincere gratitude to my Ph. D. advisor Christoph Ueberhuber, who gave me the opportunity of working in the ASCOT team operating in the interesting research field of scientific computing. I especially want to express my gratitude for leading my first steps in the area of high performance computing and for giving me the possibility to work at the forefront of scientific research. He supported my efforts with great dedication, not only during the work on my thesis, but also throughout the time of my diploma thesis. Finally I would like to thank him for spending enjoyable evenings talking about interesting this and that apart from work.

Very, very special thanks go to my colleague and friend Peter Wurzinger, with whom I have spent countless rewarding programming afternoons in nerd friendly atmosphere.

Franz Franchetti deserves great appreciation for his support and guidance throughout my work. His ideas and comments were invaluable. Without his effort of regulating my weird thoughts to their true semantically meaning, the writing style of this document and especially this work would not be as they are.

I truly want to thank the outstanding Stefan Kral, the most discriminating hacker I have ever met, for valuable discussions and for "gently" forcing me into avantgarde programming. Without his help and private advice, this work could not have been done at all.

I would like to thank all the people from the AURORA Project 5 and the Institute for Analysis and Scientific Computing at the Vienna University of Technology for having made the work on my thesis a rewarding and enjoyable experience.

In addition, I would like to acknowledge the financial support of the Austrian Science Fund FWF.

I want to thank all my friends, too many to list all of them, for their friendship and support.

Above all, I want to thank my family—my parents, grandparents and my brother—for always supporting me and for giving me guidance. I want to thank my parents for giving me the opportunity to study and for their support in all the years. I especially want to thank my mother for always believing in me.

Finally, I am grateful to Johann Sebastian Bach and John Coltrane for their invaluable music.

JÜRGEN LORENZ

A few years ago major vendors of *general purpose* microprocessors have started to include short vector single instruction, multiple data (SIMD) extensions into their instruction set architecture (ISA) with the main objective of improving the performance of multi-media applications. The fundamental idea behind SIMD architectures is that a single instruction operates concurrently on several data elements using several functional units, traditionally located on different processors.

Examples of SIMD extensions supporting both integer and floating-point operations include Intel's streaming SIMD extensions (SSE, SSE 2, and SSE 3), AMD's 3DNow! as well as its successors "enhanced 3DNow!" and "3DNow! professional", Motorola's AltiVec, and last but not least IBM's Double FPU floatingpoint unit for BlueGene/L supercomputers.

**Drawbacks of General Purpose Compilers.** Although the newly introduced SIMD instruction set extensions have the potential for outstanding speed-up, a significant obstacle to their application in signal processing and scientific computing has been the lack of compilers producing code comparable to carefully hand-optimized code, in terms of overall floating-point performance. Not fully exploiting the available short vector SIMD extensions wastes 50% to 75% of a processor's capabilities.

Automatic Performance Tuning. Extensive experience shows that in numerical linear algebra and in digital signal processing, high performance is achieved either by extremely costly hand optimization or by automatic performance tuning a new software paradigm in which optimized code for numerical computation is generated automatically [35, 88, 115].

All high performance numerical vendor-supplied libraries (Intel MKL, IBM ESSL, Apple vDSP,...) are hand-coded and/or hand-tuned to utilize SIMD extensions to a satisfactory degree. They have to be adapted to each new hardware generation by hand, thus they are not performance portable.

Apart from automatic performance tuning software, there is currently no other type of portable high-performance numerical software. However, at the moment, automatic performance tuning software does not include proper support for SIMD extensions. For example, FFTW 2—the de-facto standard for portable high performance FFT computation—does not include support for short vector SIMD extensions. This shortcoming demonstrates the need of short vector SIMD support in conjunction with numerical performance tuning software.

New Compiler Technology. This thesis presents new techniques for the compilation of automatically generated code coming out of automatic performance tuning systems like FFTW, SPIRAL, and ATLAS. The techniques introduced in

this thesis include automatic 2-way SIMD vectorization of numerical straight line code, domain-specific peephole optimization, and compiler backend optimization (see [71], [76] and [26]).

The newly introduced concepts are realized in the *MAP compiler*, which is capable of generating SIMD vectorized code for digital signal processing algorithms like FFTs, DCTs and DSTs, as well as algorithms in numerical linear algebra like matrix multiplication.

MAP achieves the same level of performance as hand-tuned vendor libraries while providing portability (see Chapter 10). Combined with leading-edge selftuning numerical software—FFTW, SPIRAL, and ATLAS—it produces

(i) the fastest FFTs running on x86 architecture machines (Intel and AMD processors) for both real and complex FFTs and for arbitrary vector sizes;

(*ii*) the only FFT routines supporting IBM's Power PC 440 FP2 double FPU used in BlueGene/L machines (see [25] and Section 3.4);

(*iii*) the only automatically tuned vectorized implementations of DSP transforms (including discrete sine and cosine transforms, Walsh-Hadamard transforms, and multidimensional transforms);

(iv) the only fully automatically vectorized ATLAS kernels.

This thesis points out the following major issues: (i) SIMD vectorization cannot be achieved easily. Nonstandard compiler techniques are required to obtain automatic performance tuning systems featuring satisfactory performance for processors with SIMD extensions. (ii) Performance portability across platforms and processor generations is not a straightforward matter, especially in the case of short vector SIMD extensions. Even the members of a family of binary compatible processors featuring the same short vector SIMD extension are different and adaptation is required to utilize them satisfactorily. (iii) Most standard vectorizing compilers are not able to deliver competitive performance due to the structural complexity of discrete linear transforms algorithms. (iv) Conventional vector computer libraries optimized for dealing with long vector lengths do not achieve satisfactory performance on short vector SIMD extensions.

## **Related Work**

As the implementation of short vector SIMD extensions in general purpose processors is a relatively new accomplishment, only few mathematical libraries and vectorizing compilers providing SIMD support are available.

#### Numerical Libraries with SIMD Support

A radix-4 FFT implementation for the NEC V80R DSP processor featuring a 4-way integer SIMD extension has been presented in 1999 [68]. Apple Computers Inc. included the vDSP library with AltiVec support into their operating system

MAC OS X [11, 17]. Intel's<sup>7</sup> math kernel library (MKL) and performance primitives (IPP) provide support for SSE, SSE 2, SSE 3, and the Itanium processor family [62]. An SSE split-radix FFT implementation has been published in an Intel application note [49]. SIMD-FFT [101] is a radix-2 FFT implementation for SSE and AltiVec.

ATLAS dgemm kernels featuring (partially hand-coded) SIMD support are available for several problem sizes and machines [1]. LIBSIMD [92] is an ongoing effort to develop a portable library utilizing short vector SIMD extensions.

#### Symbolic FFT Vectorization

The Kronecker product formalism (see Appendix A) was introduced in the early 1990s as a tool for developing FFT algorithms for parallel and vector machines [65]. The SCIPORT library [78] is a portable Fortran implementation of the proprietary Cray SCILIB library targeted at traditional vector computers. A SPIRAL based approach (i. e., SPIRAL-SIMD) to portably vectorize discrete linear transforms utilizing structural knowledge is presented in [24, 27, 28, 29, 31]. The method utilizes structural knowledge that is available on the algorithm level only. The vectorization algorithm translates DSP algorithms into vectorized DSP algorithms suitable for short vector SIMD architectures by means of algebraic algorithm can be mapped to any of the short vector architectures currently available. The vectorization algorithm works for arbitrary lengths of the data vectors and is parameterized by the short vector SIMD architecture's vector length  $\nu$ . The methods were incorporated into FFTW and SPIRAL.

#### Compiler Vectorization and Backends

Vectorizing compilers have to be divided into compilers targeted at (i) "classic" loop vectorization, and (ii) basic block vectorization. Krall and Lelait [77] give a good overview of loop vectorization techniques. as well as the implementation of vectorization by loop unrolling.

Loop Vectorization. Established vectorization techniques mainly focus on finding loop-constructs which can be vectorized. If vectorization is possible, compiler known functions, i. e., intrinsics, are inserted into the code through language extensions by the compiler. However, there is a strong need for complex techniques for analyzing the source program. Additionally, the inserted instructions have a great impact on the code generation steps following the vectorization process.

Intel's C++ compiler [50] and Codeplay's VECTOR C compiler [15] are able to vectorize loop code for both integer and floating-point short vector extensions.

<sup>&</sup>lt;sup>7</sup>http://developer.intel.com

An upgrade to the SUIF <sup>8</sup> compiler that vectorizes loop code for MMX is described in [104]. The compiler identifies parallel sections of the code using scalar and array dependence analysis. The enhanced compiler applies C source to source translation with inline assembly instructions for the vectorizable sections of the code. Another loop vectorization extension has been added to SUIF addressing Berkeley's Torrent MIPS-II compliant processor with vector enhancements as coprocessor (DeVries [18]).

A code generator for energy aware compilation on DSP processors using loop level vectorization for code improvement w.r.t. execution time and therefore energy consumption has been introduced in Lorenz et al. [81].

Basic Block Vectorization. Due to the complex analysis required for loop vectorization, proposed to perform the vectorization on basic blocks resulting from increased parallelism by applying loop unrolling. After that, scalar instructions whose semantics allow to be executed as SIMD instructions are *packed* into groups. Vectorization of basic blocks by loop unrolling has the advantage that the analysis is less complex compared to loop vectorization. However, for basic block vectorizers addressing a wide range of different codes, i. e., codes where no domain specific knowledge about code inherent parallelism is available, there is a high risk of increasing code size for loops which cannot be vectorized.

A vectorizing compiler exploiting superword level parallelism (i. e., SIMD style parallelism) has been introduced in Larsen and Amarasinghe [79]. It identifies blocks of scalar operations offering enough parallelism for vectorization and joins them with scalar code blocks not suited for vectorization via expensive data reorganization operations. IBM's XL C compiler for BlueGene/L [3] utilizes this vectorization technique.

A vectorization approach that performs a data-flow graph based *code selection* technique for media processors with support for SIMD instructions has been introduced in Leupers and Bashford [80]. This advanced approach exploits SIMD instructions in code selection for plain ANSI C code.

General purpose compilers are not capable of detecting potential parallelism in their standard, fast code selection techniques.

As this technique for basic block code selection is highly related to the vectorization techniques introduced in this thesis, a short comparison of the two approaches follows.

The main difference to the automatic vectorization approach introduced in this thesis is that (i) only consecutive load and store operations are allowed, (ii) instruction parings of different operation type (e.g., add/sub) are not allowed, and (iii) two scalar instructions are to be covered by *one* SIMD instruction.

The graph based code selection technique for processors with SIMD instruc-

<sup>&</sup>lt;sup>8</sup>SUIF is the abbreviation of "Stanford University Intermediate Format", a public domain compiler that takes either Fortran or C as input language and automatically translates sequential scientific programs into parallel code for scalable parallel machines.

tions deals with suboptimal cases by allowing an incomplete graph coverage by SIMD instructions. On the other hand, the approach introduced in this thesis always demands for a complete coverage but possibly with suboptimal SIMD utilization (cf. the vectorization levels in Section 7.5).

These differences stem from the different target architectures. While the code selection technique is targeted at embedded DSP processors, the vectorization technique of this thesis addresses general purpose SIMD processors. It is generally cheap to interleave scalar instructions with SIMD instructions for DSP processors, which is not the case for processors such as AMD's K7 or Intel's Pentium 4.

Basic Block Backend. Standard compilers are intended for handwritten code normally having only short basic blocks. However, code generated by *automatic performance tuning systems* often contains very large basic blocks of loop-unrolled code.

A compiler backend for MIPS processors targeting numerical straight-line code is presented in Guo et al. [44]. The simple *farthest first* algorithm [105] has been assessed as spilling strategy for register allocation used on large basic blocks. The test codes, the experiments were carried out with, have been generated by ATLAS and SPIRAL, two state of the art automatic performance tuning systems automatically generating completely or partly unrolled code. Experiments show that the farthest first algorithm is superior when used as spilling strategy for large blocks of straight-line code.

## Synopsis

This thesis introduces and discusses the MAP vectorizer and backend in detail. It consists of four main parts.

### Part I: Foundations

Chapter 1 discusses the reasons why it is hard to achieve high performance implementations of numerical algorithms on current computer architectures. The three major automatic performance tuning systems for discrete linear transforms— ATLAS, FFTW and SPIRAL—are discussed.

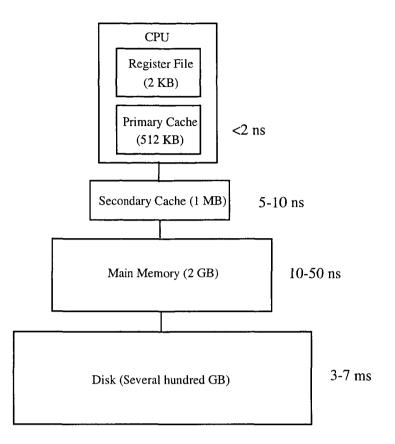

Chapter 2 describes current hardware trends and advanced hardware features. The main focus lies on CPUs and memory hierarchies.

Chapter 3 discusses current short vector SIMD extensions and available programming interfaces.

Chapter 4 deals with fast algorithms for discrete linear transforms, i.e., matrixvector products with specially structured matrices. The discrete Fourier transform is discussed in detail. Classical iterative and modern recursive algorithms are summarized. The mathematical approach of SPIRAL and FFTW is presented.

12

Chapter 5 covers the matrix-matrix multiplication in scientific computation. Differences between a straightforward implementation and the highly tuned BLAS library ATLAS are pointed out.

Chapter 6 introduces a *portable SIMD API* as a prerequisite for the implementation of the short vector algorithms presented in subsequent chapters.

#### Part II: The MAP Special Purpose Compiler

Chapter 7 describes a new method for the automatic 2-way SIMD vectorization of numerical straight line code. The new technique guarantees a satisfactory degree of SIMD utilization and has been successfully used to vectorize (i) complex FFT kernels of arbitrary length, (ii) real-to-halfcomplex FFT kernels of even lengths, (iii) various DSP transform kernels, and (iv) kernels used in numerical linear algebra.

Chapter 8 deals with domain-specific peephole optimization techniques used in the code generator of MAP.

Chapter 9 describes domain-specific backend optimization techniques implemented in the x86 compiler backend of MAP.

#### Part III: Experimental Results

Chapter 10 presents a number of experimental results. The MAP vectorizer and backend have been assessed in combination with ATLAS, FFTW and SPIRAL on a variety of target processors, including Intel's Pentium 4, AMD's Athlon, and IBM's PowerPC 440 FP2. Experimental evidence for the superior performance achievable by using the newly introduced methods is given.

#### Part IV: Appendices

Appendix A summarizes the mathematical framework required to express the results presented in this thesis. The Kronecker product formalism and its connection to programs for discrete linear transforms is discussed. The translation of complex arithmetic into real arithmetic within this framework is described.

Appendix B contains elementary information about the compiler techniques of register allocation and instruction scheduling.

Appendix C discusses the performance assessment of scientific software.

Appendix D summarizes the relevant parts of short vector SIMD instruction sets.

Appendix E shows the implementation of the portable SIMD API required for the numerical experiments of this thesis.

Appendix F displays example code obtained using the newly developed short vector SIMD extension for SPIRAL.

Appendix G contains codelet examples taken from the short vector SIMD version of FFTW.

## Chapter 1

## Hardware vs. Algorithms

The fast evolving microprocessor technology, following Moore's law, has turned standard, single processor off-the-shelf desktop computers into powerful computing devices with peak performances of, at present, several gigaflop/s. Thus, scientific problems that a decade ago required powerful parallel supercomputers, are now solvable on a PC. On a smaller scale, many applications can now be performed under more stringent performance constraints, e.g., in real time.

Unfortunately, there are several problems inherent to this development on the hardware side that make the development of top performance software an increasingly difficult task feasible only for expert programmers.

(i) Due to the memory-processor bottleneck the performance of applications depends more on the pattern, e.g., locality of data access rather than on the mere number of arithmetic operations.

(ii) Complex architectures make a performance prediction of algorithms a difficult, if not impossible task.

(*iii*) Most of the modern microprocessors introduce special instructions like FMA (fused multiply-add), or short vector SIMD instructions (like SSE on Pentium processors). These instructions provide superior potential speed-up but are difficult to utilize.

(iv) High-performance code, hand-tuned to a given platform, becomes obsolete as the next generation (in cycles of typically about two years) of microprocessors comes onto the market.

As a consequence, the development of top performance software, portable across architectures and time, has become one of the key challenges associated with Moore's law. As a result there has been a number of efforts recently, collectively referred to as *automatic performance tuning*, to automate the process of implementation and optimization for given computing platforms. Important examples include FFTW by Frigo and Johnson [34], ATLAS by Whaley et al. [115], and SPIRAL by Püschel et al. [98].

## 1.1 Current Hardware Trends

The gap between processor performance, memory bandwidth and network link bandwidth is constantly widening. Processor power grows by approximately 60% per year while memory bandwidth is growing by a relatively modest 6% per year. Although the overall sum of the available network bandwidth is doubling every

#### 1.1 Current Hardware Trends

year, the sustained bandwidth *per link* is only growing by less than 6% per year. Thus, it is getting more and more complicated to build algorithms that are able to utilize modern (serial or parallel) computer systems to a satisfactory degree.

Only the use of sophisticated techniques both in hardware architecture and software development allows to overcome these difficulties. Algorithms which were optimized for a specific architecture several years ago, fail to perform well on current and emerging architectures. Due to the fast product cycles in hardware development and the complexity of today's execution environments, it is of utmost importance to provide users with easy-to-use self-adapting numerical software.

The development of algorithms for modern high-performance computers is getting more and more complicated due to the following facts. (i) The performance gap between CPUs, memories, and networks is widening. (ii) Hardware tricks partially hide this performance gap. (iii) Performance modelling of programs running on current and future hardware is getting more and more difficult. (iv) Non-standard processor extensions complicate the development of programs with satisfactory performance characteristics.

In the remainder of this section, these difficulties are outlined in detail.

#### **Computing Cores**

Computing power increases at an undiminished rate according to Moore's law. This permanent performance increase is primarily due to the fact that more and more non-standard computing units are incorporated into microprocessors. For instance, the introduction of *fused multiply add* (FMA) operations doubled the floating-point peak performance. The introduction of *short vector SIMD extensions* (e.g., Intel's SSE or Motorola's AltiVec) enabled the increase of the peak performance by another factor of 2 or 4.

Using standard algorithms and general purpose compiler technology, it is not possible to utilize these recently introduced hardware extensions to a satisfactory degree. Special algorithms have to be developed for high-performance numerical software to achieve an efficient utilization of modern processors.

#### Memory Subsystems

Memory access is getting more and more expensive relatively to computation speed. Caching techniques try to hide latency and the lack of satisfactory memory bandwidth but require locality in the algorithm's memory access patterns. Deep memory hierarchies, cache associativity and size, transaction lookaside buffers (TLBs), and automatic prefetching introduce another level of complexity. The parameters of these facilities even vary within a given computer architecture leading to an intrinsic problem for algorithm developers who try to optimize floating-point performance for a set of architectures. Symmetrical multiprocessing introduces the problem of cache sharing as well as cache coherency and the limited memory bandwidth becomes an even more limiting factor. Non-uniform memory access on some architectures hides the complexity of distributed memory at the cost of higher latencies for some memory blocks.

### **1.1.1 Performance Modelling**

For modern computer architectures, modelling of system characteristics and performance characterization of numerical algorithms is extremely complicated. The number of floating-point operations is no longer an adequate measure for predicting the required run time.

The following features of current hardware prevent the accurate modelling and invalidate current performance measures for a modern processor: (i) Pipelining and multiple functional units, (ii) super-scalar processors and VLIW processors, (iii) fused multiply-add (FMA) instructions, (iv) short vector SIMD extensions, (v) branch prediction, (vi) virtual registers, (vii) multi-level set-associative caches as well as shared caches, and (viii) transaction lookaside buffers (TLBs).

As modelling of algorithms with respect to their actual run time is not possible to a satisfactory degree, the only reasonable performance assessment is an empirical run time study carried out for given problems.

Chapter 2 explains performance relevant processor features and the respective techniques in detail. Appendix C explains the methodology of run time measurement and performance assessment.

## **1.2 Performance Implications**

This section exemplary shows the drawback of the standard approach of optimizing software to a given platform and shows that the asymptotic complexity and even the actual number of operations is no adequate performance measure.

The standard approach to obtain an optimized implementation for a given algorithm is summarized as follows.

- The algorithm is adapted to the hardware characteristics by hand, focussing, e.g., on the memory hierarchy and/or processor features.

- The adapted algorithm is coded using a high-level language to achieve portability and make the programming manageable.

- Key portions of the code may be coded by hand in assembly language to improve performance.

The complexity of current hardware and the pace of development make it impossible to produce optimized implementations which are available at or shortly after

#### 1.2 Performance Implications

| FFT Program             | Vector Length $N$ |          |          |          |  |  |  |  |  |  |

|-------------------------|-------------------|----------|----------|----------|--|--|--|--|--|--|

|                         | $2^{5}$           | $2^{10}$ | $2^{15}$ | $2^{20}$ |  |  |  |  |  |  |

| NAG/c60fcf              | 11.6              | 6.0      | 3.3      | 2.6      |  |  |  |  |  |  |

| IMSL/dfftcf             | 2.0               | 1.7      | 2.7      | 3.9      |  |  |  |  |  |  |

| Numerical Recipes/four1 | 2.6               | 2.1      | 2.2      | 3.9      |  |  |  |  |  |  |

| FFTPACK/cfftf           | 1.4               | 1.0      | 2.1      | 4.0      |  |  |  |  |  |  |

| Green's FFT             | 1.6               | 1.1      | 1.0      | -        |  |  |  |  |  |  |

| FFTW 2.1.3              | 1.0               | 1.1      | 1.1      | 1.0      |  |  |  |  |  |  |

Table 1.1: Slow-down factors of various FFT routines relative to the run time of the best performing routine (with factor 1.0). Performance data were obtained on one processor of an SGI Power Challenge XL (Auer et al. [12]).

a processor's release date. This section shows the run time differences resulting from the intrinsic problems.

### 1.2.1 Run Time vs. Complexity

For all Cooley-Tukey FFT algorithms the asymptotic complexity is  $O(N \log N)$  with N being the length of the vector to be transformed. Even the constant is nearly the same for all algorithms.

#### Performance of Scalar Code

However, Table 1.1 shows that the run times of the corresponding programs vary tremendously. It is a summary of experiments described in Auer et al. [12] where the performance of many FFT routines was measured on various computer systems.

For instance, on one processor of an SGI Power Challenge XL, for a transform length  $N = 2^5$  the function c60fcf of the NAG library is 11.6 *times* slower than the fastest implementation, FFTW.

For  $N = 2^{10}$  cfftf of FFTPACK is the fastest program and c60fcf is six times slower while FFTW is a moderate 10% slower.

For  $N = 2^{20}$  FFTW is again the fastest program. c60fcf is 2.6 times slower and cfftf of FFTPACK is four times slower than FFTW.

This assessment study shows that (i) the performance behavior of FFT programs depends strongly on the problem size, and (ii) architecture adaptive FFTs are within 10% of the best performance for all problem sizes.

#### Performance of Short Vector SIMD Code

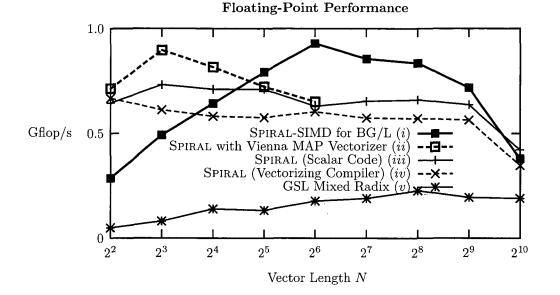

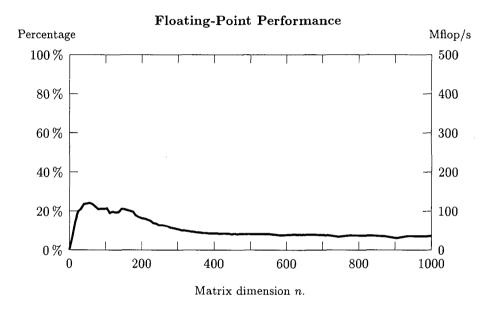

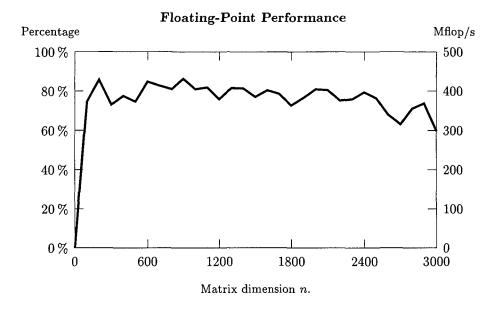

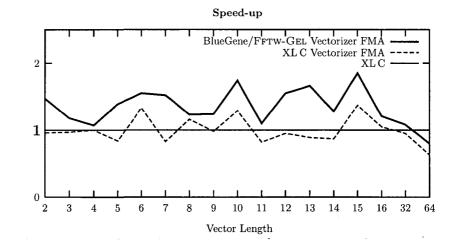

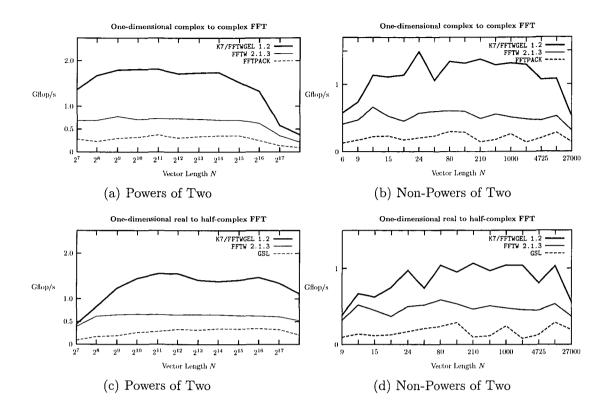

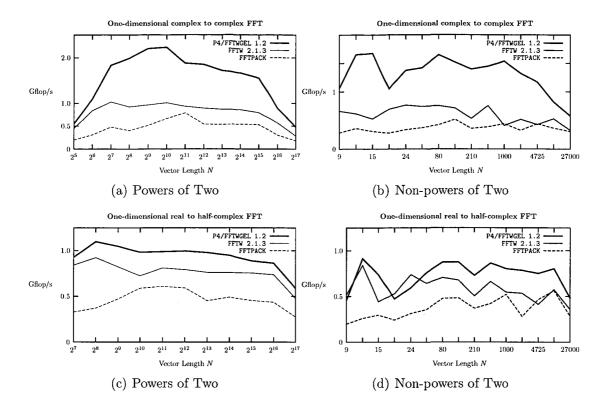

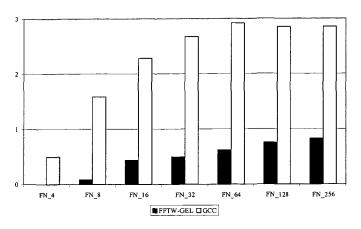

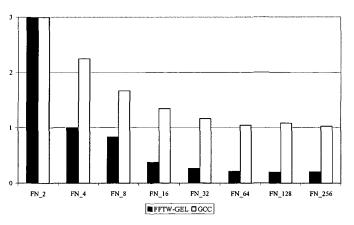

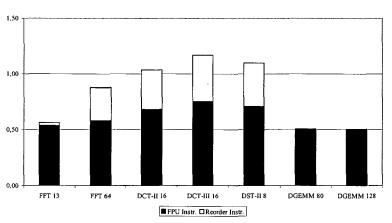

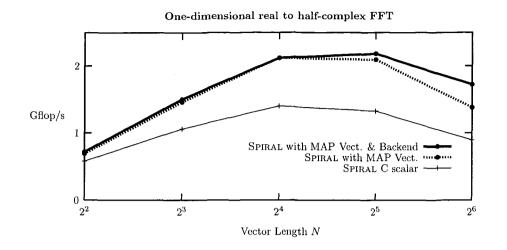

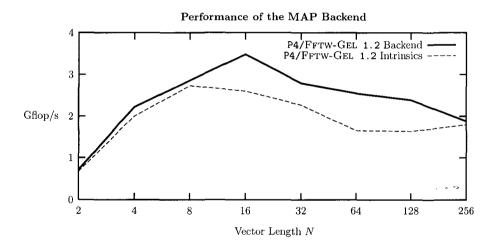

The arguments in favor of architecture adaptive software become even more striking by extending this study to machines featuring short vector SIMD extensions. Figure 1.1 shows the performance of various one dimensional complex FFT routines (SIMD and scalar) on one CPU of a prototype of BlueGene/L's PowerPC 440 FP2 running at 500 MHz featuring a *double FPU*. The *double FPU* provides two-way vector extensions (for single-precision and double-precision, respectively) resulting in a theoretical speed-up of two.

Figure 1.1: FFT Floating-point performance and speed-up of the vectorization techniques applied by the MAP vectorizer for BG/L and SPIRAL-SIMD for BG/L (formal vectorization) compared to the best scalar code and the best vectorized code (utilizing the VisualAge XL C for BG/L vectorizing compiler) found by SPIRAL. Performance is displayed in *pseudo Gflop/s*  $(5N \log N/\text{runtime with } N \text{ being the vector length; Frigo and Johnson [35]}.$

The following scalar and vectorization techniques were tested:

The MAP Vectorizer is one of the main subjects of this thesis and its vectorization techniques will be explained in detail in Chapter 7. MAP provides vectorization of single static assignment straight-line code for two-way short vector extensions as a source-to-source transformation. The source codes to be vectorized may contain array accesses, index computation, and arithmetic operations. Typically, such source codes consist of thousands of arithmetic operations. In addition to SIMD vectorization, MAP provides support for FMA instructions.

MAP was adapted to support BlueGene/L's double FPU and connected to the SPIRAL system to provide BlueGene/L specific vectorization of SPIRAL generated code. SPIRAL's SPL compiler was used to translate formulas generated by the formula generator into fully unrolled implementations leading to large straight-line codes. These codes were subsequently vectorized by MAP and thus transformed into a C program where all arithmetic operations and memory access operations are expressed using XL C's intrinsic functions. Finally the codes were compiled utilizing the XL C compiler with vectorization turned off. A detailed assessment of the MAP Vectorizer can be found in Chapter 10.

SPIRAL-SIMD. A SIMD vectorizing version of SPIRAL's SPL compiler that is portable across different SIMD architectures was adapted to vectorize codes for FFTs [28] targeting BlueGene/L's double FPU. Certain mathematical constructs used in SPIRAL's formula representation of a DSP algorithm are mapped to vectorized code by this compiler. These constructs occur in virtually every DSP algorithm. Furthermore, in several important cases, including the FFT, the formulas generated by SPIRAL are built exclusively from these vectorizable constructs, and thus can be completely vectorized using the adapted SIMD vectorizing SPL compiler.

In addition, a formally derived "short vector FFT variant" is utilized to vectorize FFT codes [30]. This variant guarantees, that the generated FFT codes fit to the need of generic short vector SIMD extensions. The short vector FFT variant was adapted to support BlueGene's double FPU.

Utilizing both methods of formal vectorization, FFT formulas generated by SPIRAL's formula generator are translated into vector code utilizing Blue-Gene/L's double FPU efficiently.

- **SPIRAL.** For scalar implementations, SPIRAL (besides FFTW) provides the currently fastest publicly available FFT programs. It delivers codes which are as fast as FFT programs specifically optimized for a given architecture. Thus, SPIRAL may serve as the baseline in Figure 1.1.

- **IBM XL C Compiler** extracts instruction level parallelism [79]. It identifies blocks of scalar operations offering enough parallelism for vectorization and joins them with scalar code blocks not suited for vectorization via expensive data reorganization operations. Therefore, it has no domain specific knowledge about the codes to vectorize. The IBM XL C compiler supports FMA extraction.

- **GNU GSL Mixed Radix.** The GNU scientific library GSL features sophisticated algorithms (without SIMD support) and is even much slower than the best scalar adaptive SPIRAL code. It is slower than the best SIMD vectorized codes by a factor of five and more.

**Experimental Results.** The presented scalar and vectorization techniques were evaluated on an early BlueGene/L prototype. Performance data of 1D FFTs with vector lengths  $N = 2^2, 2^3, \ldots, 2^{10}$  were obtained on a single PowerPC 440 FP2 running at 500 MHz.

In particular the following FFT implementations were tested: (i) The best vectorized code found by SPIRAL utilizing formal vectorization, (ii) the best vectorized code found by SPIRAL utilizing the MAP vectorizer, (iii) the best scalar FFT implementation found by SPIRAL (XLC's vectorizer and FMA extraction turned off), (iv) the best vectorized FFT implementation found by SPIRAL using the XLC compiler's vectorizer and FMA extraction turned on, and (v) the mixed-radix FFT implementation provided by the GNU scientific library (GSL). Fig. 1.1 displays the respective performance data.

The best scalar codes found by SPIRAL—referenced by (iii) in Fig. 1.1—serve as baseline for the assessment of the various vectorization techniques. These codes are very fast scalar implementations featuring no FMA instructions.

Formal vectorization—referenced by (i) in Fig. 1.1—provides up to 40% speed-up w.r.t. the best scalar codes generated by SPIRAL for problem sizes  $N \ge 64$ . Thus formal vectorization provides significant speed-up for larger problem sizes.

The MAP vectorizer—referenced by (ii) in Fig. 1.1—is restricted to problem sizes that can fully be unrolled fitting into instruction cache and the resulting code can be handled well by the XL C compiler's register allocator. For problem sizes  $N \leq 32$ , the MAP vectorizer provides the same level of performance as formal vectorization for larger problem sizes.

The third-party GNU GSL FFT library—referenced by (v) in Fig. 1.1—reaches about 30% of the performance of the best scalar SPIRAL generated code thus performing badly.

XL C's vectorization and FMA extraction—referenced by (iv) in Fig. 1.1 produces code 15% slower than scalar XL C without FMA extraction. Thus, the vectorization techniques to vectorize straight-line code currently used within the XL C compiler cannot handle SPIRAL generated FFT codes well.

**Conclusion.** The numerical experiments carried out on the BlueGene/L prototype summarized in Figure 1.1 show that automatic performance tuning in combination with the two newly developed vectorization approaches is able to speed up FFT code considerably, while vectorization by IBM's XLC compiler does not speed up the automatically generated scalar codes at all. The two vectorization approaches, the MAP vectorizer and SPIRAL-SIMD, are able to provide high-performance FFT kernels for BlueGene/L by fully utilizing the new double FPU.

These experiments provide evidence that modern (vectorizing) compilers are not able to generate fast machine code in conjunction with portable libraries. This gives an impression of how much performance can be gained by using automatic performance tuning and utilizing special processor features as short vector SIMD extensions.

The next section explains, why this performance gain is possible and gives an

short overview over current automatic performance tuning systems.

## **1.3 Automatic Performance Tuning**

Automatic performance tuning is a step beyond standard compiler optimization. It is required to overcome the problem that today's compilers on current machines cannot produce high performance code any more as outlined in the previous section.

Automatic performance tuning is a problem specific approach and thus is able to achieve much more than general purpose compilers are capable of.

Current automatic empirical optimization systems (AEOS) focus on (i) CPU level optimizations (loop unrolling, source code scheduling, FMA utilization), and (ii) memory hierarchy utilization (loop tiling, cache blocking). Actual code runtime is used to steer the automatic optimization process.

For instance, ATLAS' search for the correct loop tiling for carrying out a matrix-matrix product is a loop transformation a compiler could in principle do (and some compilers try to), if the compiler would have an accurate machine model to deduce the correct tiling. But compilers do not reach ATLAS' performance. The same phenomenon occurs with the source code scheduling done by SPIRAL and FFTW for straight line code, which should be done satisfactorily by the target compiler.

### 1.3.1 Compiler Optimization

Modern compilers make extensive use of optimization techniques to improve the program's performance. The application of a particular optimization technique largely depends on a static program analysis based on simplified machine models. Optimization techniques include high level loop transformations, such as loop unrolling and tiling. These techniques have been extensively studied for over 30 years and have produced, in many cases, good results. However, the machine models used are inherently inaccurate, and transformations are not independent in their effect on performance making the compiler's task of deciding the best sequence of transformations difficult (Aho et al. [2]).

Typically, compilers use heuristics that are based on averaging observed behavior for a small set of benchmarks. Furthermore, while the processor and memory hierarchy is typically modelled by static analysis, this does not account for the behavior of the entire system. For instance, the register allocation policy and strategy for introducing spill code in the backend of the compiler may have a significant impact on performance. Thus static analysis can improve program performance but is limited by compile-time decidability.

### 1.3.2 The Program Generator Approach

A method of source code adaptation at compile-time is code generation. In code generation, a *code generator* (i. e., a program that produces other programs) is used. The code generator takes as parameters the various source code adaptations to be made, e.g., instruction cache size, choice of combined or separate multiply and add instructions, length of floating-point and fetch pipelines, and so on. Depending on the parameters, the code generator produces source code having the desired characteristics.

Example 1.1 (Parameters for Code Generators) In genfft, the codelet generator of FFTW, the generation of FMA specific code can be activated using the -magic-enable-fma switch. Calling genfft using

genfft 4 -notwiddle -magic-enable-fma

results in the generation of a no-twiddle codelet of size four which is optimized for FMA architectures.

## 1.3.3 Compile-Time Adaptive Algorithms Using Feedback-Information

Not all important architectural variables can be handled by *parameterized* compile-time adaptation since varying them actually requires changing the underlying source code. This brings in the need for the second method of software adaptation, compile-time adaptation by *feedback directed* code generation, which involves actually generating different implementations of the same operation and selecting the best performing one.

There are at least two different ways to proceed:

(i) The simplest approach is to get the programmer to supply various hand-tuned implementations, and then to choose a suitable one.

(*ii*) The second method is based on automatic code generation. In this approach, parameterized code generators are used. Performance optimization with respect to a particular hardware platform is achieved by searching, i. e., varying the generator's parameters, benchmarking the resulting routines, and selecting the fastest implementation. This approach is also known as *automated empirical optimization of software* (AEOS) (Whaley et al. [115]).

In the remainder of this section the existing approaches are introduced briefly.

### PHiPAC

Portable high-performance ANSI C (PHiPAC) was the first system which implemented the "generate and search" methodology (Bilmes et al. [14]). Its code generator produces matrix multiply implementations with various loop unrolling

#### 1.3 Automatic Performance Tuning

depths, varying register and L1- and L2-cache tile sizes, different software pipelining strategies, and enables other options. The output of the generator is C code, both to make the system portable and to allow the compiler to perform the final register allocation and instruction scheduling. The search phase benchmarks code produced by the generator under various options to select the best performing implementation.

### ATLAS

The automatically tuned linear algebra software (ATLAS<sup>1</sup>) project [102, 115, 114, 113, 112] is an ongoing research effort (at the University of Tennessee, Knoxville) focusing on empirical techniques in order to produce software having portable performance. Initially, the goal of the ATLAS project was to provide a portably efficient implementation of the BLAS. Now ATLAS provides at least some level of support for all of the BLAS, and first tentative extensions beyond this level have been taken.

While originally the ATLAS project's principle objective was to develop an efficient library, today the field of investigation has been extended. Within a couple of years new methodologies to develop self-adapting programs have become established, the AEOS approach has been established which forms a new sector in software evolution. ATLAS' adaptation approaches are typical AEOS methods; even the concept of "AEOS" was coined by ATLAS' developers (Whaley et al. [115]). In this manner, the second main goal of the ATLAS project is the general investigation in program adaptation using AEOS methodology.

ATLAS uses automatic code generators in order to provide different implementations of a given operation, and involves sophisticated search scripts and robust timing mechanisms in order to find the best way of performing this operation on a given architecture.

The remainder of this chapter introduces the two leading projects dealing with architecture adaptive implementations of discrete linear transforms, SPIRAL and FFTW. One result of this thesis is the usage of the output codes of these systems with the newly developed MAP vectorizer and backend.

#### FFTW

FFTW<sup>2</sup> (fastest Fourier transform in the west) was the first effort to automatically generate FFT code using a special purpose compiler and use to the actual run time as optimization criterion (Frigo [33], Frigo and Johnson [34, 35, 36, 37]). Typically, FFTW performs faster than publicly available FFT codes and faster to equal with hand optimized vendor-supplied libraries across different machines. It provides comparable performance to SPIRAL). Several extensions to FFTW exist,

<sup>&</sup>lt;sup>1</sup>available from http://math-atlas.sourceforge.net/

<sup>&</sup>lt;sup>2</sup>available from http://www.fftw.org/

including the AC FFTW package and the UHFFT library. Currently, FFTW is the most popular portable high performance FFT library that is publicly available.

FFTW provides a recursive implementation of the Cooley-Tukey FFT algorithm. The actual computation is done by automatically generated routines called *codelets* which restrict the computation to specially structured algorithms called right expanded trees (see Section 4.1 and Haentjens [46]). The recursion stops when the remaining right subproblem is solved using a codelet. For a given problem size there are many different ways of solving the problem with potentially very different run times. FFTW uses dynamic programming with the actual run time of problems as cost function to find a fast implementation for a given DFT<sub>N</sub> on a given machine. FFTW consists of the following fundamental parts. Details about FFTW can be found in Frigo and Johnson [35].

**The Planner.** At run time but as a one time operation during the initialization phase, the *planner* uses dynamic programming to find a good decomposition of the problem size into a tree of computations according to the Cooley-Tukey recursion called *plan*.

The Executor. When solving a problem, the *executor* interprets the *plan* as generated by the planner and calls the appropriate codelets with the respective parameters as required by the plan. This leads to data access patterns which respect memory access locality.

The Codelets. The actual computation of the FFT subproblems is done within the codelets. These small routines come in two flavors, (i) twiddle codelets which are used for the left subproblems and additionally handle the twiddle matrix, and (ii) no-twiddle codelets which are used in the leaf of the recursion and which additionally handle the stride permutations. Within a larger variety of FFT algorithms is used, including the Cooley-Tukey algorithm, the split-radix algorithm, the prime factor algorithm, and the Rader algorithm (Van Loan [109]).

The Codelet Generator genfft. At install time, all codelets are generated by a special purpose compiler called the *codelet generator* genfft. As an alternative the preponderated codelet library can be downloaded as well. In the standard distribution, codelets of sizes up to 64 (not restricted to powers of two) are included. But if special transform sizes are required, the required codelets can be generated.

#### SPIRAL

SPIRAL<sup>3</sup> (signal processing algorithms implementation research for adaptive libraries) is a generator for high performance code for discrete linear transforms like the DFT, the discrete cosine transforms (DCTs), and many others by Püschel et al. [99], Moura et al. [87, 88, 89]. SPIRAL uses a mathematical approach that

24

<sup>&</sup>lt;sup>3</sup>available from http://www.ece.cmu.edu/~spiral/

#### 1.3 Automatic Performance Tuning

translates the implementation problem of discrete linear transforms into a search in the space of structurally different algorithms and their possible implementations to generate code that is adapted to the given computing platform. SPI-RAL's approach is to represent the many different algorithms for a transform as formulas in a concise mathematical language. These formula are automatically generated and automatically translated into code, thus enabling an automated search. Chapter 4 summarizes the discrete linear transforms and Appendix A summarizes the mathematical framework.

More specifically, the SPIRAL approach is based on the following observations.

- For every discrete linear transform transform there exists a *very large* number of different *fast* algorithms. These algorithms differ in dataflow but are essentially equal in the number of arithmetic operations.

- A fast algorithm for a discrete linear transform can be represented as a *formula* in a concise mathematical notation using a small number of mathematical constructs and primitives (see Appendix A).

- It is possible to *automatically generate* the alternative formulas, i. e., algorithms, for a given discrete linear transform.

- A formula representing a fast discrete linear transform algorithm can be mapped *automatically* into a program in a high-level language like C or Fortran.

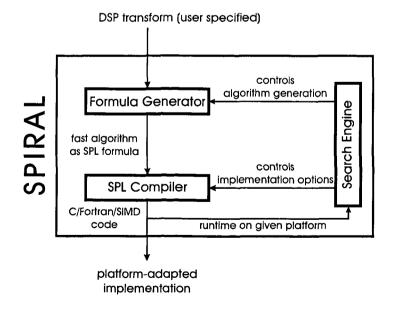

Figure 1.2: SPIRAL's architecture.

The architecture of SPIRAL is shown in Figure 1.2. The user specifies a transform to be implemented, e. g., a DFT of size 1024. The *formula generator* expands the transform into one (or several) formulas, i.e., algorithms, represented in the SPIRAL proprietary language SPL (signal processing language). The *formula translator* (also called SPL compiler) translates the formula into a C or Fortran program. The run time of the generated program is fed back into a *search engine* that controls the generation of the next formula and possible implementation choices, such as the degree of loop unrolling. Iteration of this process yields a platform-adapted implementation. Search methods in SPIRAL include dynamic programming and evolutionary algorithms. By including the mathematics in the system, SPIRAL can optimize, akin to a human expert programmer, on the implementation level *and* the algorithmic level to find the best match to the given platform. Further information on SPIRAL can be found in Püschel et al. [97], Singer and Veloso [103], Xiong et al. [116].

**GAP and AREP.** SPIRAL's formula generator uses AREP, a package by Egner and Püschel [22] implemented in the language GAP [107] which is a computer algebra system for computational group theory. The goal of AREP was to create a package for computing with group representations up to equality, not up to equivalence, hence, AREP provides the data types and the infrastructure to do efficient symbolic computation with representations and structured matrices which arise from the decomposition of representations.

Algorithms represented as formulas are written in mathematical terms of matrices and vectors which are specified and composed symbolically in the AREP notation. Various standard matrices and matrix types are supported such as many algebraic operations, like DFT and diagonal matrices, and the Kronecker product formalism.

One result of the work presented in this thesis will be the MAP vectorizer which allows for the automatic vectorization of computational kernels generated by selftuning numerical software and the MAP backend, a special purpose kernel backend to translate vectorized code into high-performance assembly code. The MAP vectorizer and backend can be connected to FFTW, SPIRAL, and ATLAS, thus addressing many different numerical computations ranging from FFTs and many other DSP transforms to BLAS kernels.

## Chapter 2

## Standard Hardware

This chapter gives an overview over standard features of single processor systems relevant for the computation of discrete linear transforms, i.e., microprocessors and the associated memory subsystem. Sections 2.1 and 2.2 discuss the features on the processor level while Section 2.3 focusses on the memory hierarchy.

Further details can be found, for example, in Gansterer and Ueberhuber [40] or Hlavacs and Ueberhuber [47].

## 2.1 Processors

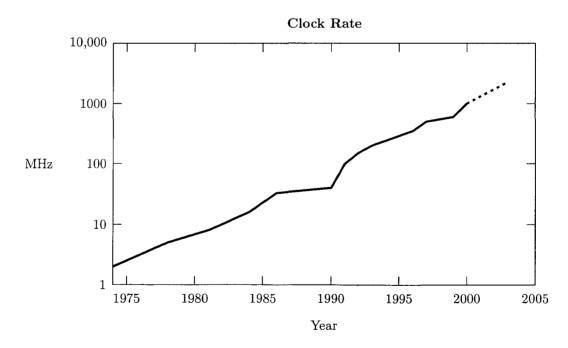

Due to packaging with increased density and architectural concepts like RISC, the peak performance of processors has been increased by about 60 percent each year (see Figure 2.1). This annual growth rate is likely to continue for at least another

Figure 2.1: Clock rate trend for off-the-shelf CPUs.

decade. Then physical limitations like Heisenberg's principle of uncertainty will impede package density to grow.

### 2.1.1 CISC Processors

The term CISC is an acronym for *complex instruction set computer*, whereas RISC is an acronym for *reduced instruction set computer*. Until the 1980s, practically all processors were of CISC type. Today, the CISC concept is quite out-of-date, though most existing processors are designed to understand CISC instruction sets (like Intel x86 compatibles). Sixth and seventh generation x86 compatible processors (Intel's Pentium II, III, and 4, and AMD's Athlon line) internally use advanced RISC techniques to achieve performance gains. They fetch x86 CISC style instructions from memory in order and translate them to an internal instruction format of one or more simpler fixed length RISC style instructions. Multiple RISC execution units are utilized to feed them into their multiple pipelines and other functional units.

#### Microcode

When designing new processors, it is not always possible to implement instructions by means of transistors and resistors only. Instructions that are executed directly by electrical components are called *hardwired*. Complex instructions, however, often require too much effort to be hardwired. Instead, they are emulated by simpler instructions inside the processor. The "program" of hardwired instructions emulating complex instructions is called *microcode*. Microcode makes it possible to emulate instruction sets of different architectures just by adding or changing ROMs containing microcode information.

Compatibility with older computers also forces vendors to supply the same set of instructions for decades, making modern processors to deal with old fashioned, complex instructions instead of creating new, streamlined instruction sets to fit onto RISC architectures.

**Example 2.1 (Microcode)** Intel's Pentium 4, and AMD's Athlon XP dynamically translate complex CISC instructions into one or more equivalent RISC instructions. Each CISC instruction thus is represented by a microprogram containing optimized RISC instructions.

### 2.1.2 RISC Processors

Two major developments paved the road to RISC processors.

High Level Languages. Due to portability and for faster and affordable software development high level languages are used instead of native assembly. Thus, optimizing compilers are needed that can create executables having an efficiency comparable to programs written in assembly language. Compilers prefer small and simple instructions which can be moved around more easily than complex instructions with more dependencies.

#### 2.1 Processors

**Performance.** Highest performance has to be delivered at any cost. This goal is achieved by either increasing the packaging density, by increasing the clock rate or by reducing the cycles per instruction (CPI) count. The latter is impossible when using ordinary CISC designs. On RISC machines, instructions are supposed to take only one cycle, yet several stages were needed for their execution. The answer is a special kind of parallelism: *pipelining*. Due to the availability of cheap memory it is possible to design fixed length instruction sets, the most important precondition for smooth pipelining. Also, cheaper SRAMs are available as caches, thus providing enough memory-processor bandwidth for feeding data to faster CPUs.

RISC processors are characterized by the following features: (i) pipelining, (ii) uniform instruction length, (iii) simple addressing modes, (iv) load/store architecture, and (v) more registers.

Additionally, modern RISC implementations use special techniques to improve the instruction throughput and to avoid pipeline stalls (see Section 2.2): (i) low grain functional parallelism, (ii) register bypassing, and (iii) optimized branches. As current processors understanding the x86 CISC instruction set feature internal RISC cores, these advanced technologies are used in x86 compatible processors as well.

In the remainder of this section the features are discussed in more detail.

### 2.1.3 Pipelines

Pipelines consist of several stages which carry out a small part of the whole operation. The more complex the function is that a pipeline stage has to perform, the more time it needs and the slower the clock has to tick in order to guarantee the completion of one operation each cycle. Thus, designers face a trade-off between the complexity of pipeline stages and the smallest possible clock cycle. As pipelines can be made arbitrarily long, one can break complex stages into two or more separated simple ones that operate faster. Resulting pipelines can consist of ten or more stages, enabling higher clock rates. Longer pipelines, however, need more cycles to be refilled after a pipeline hazard or a context switch. Smaller clock cycles, however, reduce this additional overhead significantly.

Processors containing pipelines of ten or more stages are called *superpipelined*.

**Example 2.2 (Superpipeline)** The Intel Pentium 4 processor core contains pipelines of up to 20 stages. As each stage needs only simple circuitry, processors containing this core are able to run at more than 3 GHz.

## 2.1.4 VLIW Processors

When trying to issue more than one instruction per clock cycle, processors have to contain several pipelines that can operate independently. In very long instruction

2. Standard Hardware

word (VLIW) processors, instruction words consist of several different operations without interdependence. At run time, these basic instructions can be brought to different units where they are executed in parallel.

The task of scheduling independent instructions to different functional units is done by the compiler at compile time. Typically, such compilers try to find a good mixture of both integer and floating-point instructions to form up long instruction words.

**Example 2.3 (VLIW Processor)** The *digital signal processors* (DSPs) VelociTI from TI, Trimedia-1000 from Philips and FR500 from Fujitsu are able to execute long instruction words.

The 64 bit Itanium processor family (IPF, formerly called IA-64) developed in a cooperation between Intel and HP, follows the VLIW paradigm. This architecture is also called EPIC (*explicit parallel instruction computing*).

It is very difficult to build compilers capable of finding independent integer, memory, and floating-point operations for each instruction. If no floating-point operations are needed or if there are much more integer operations than floating-point operations, for example, much of this kind of parallelism is wasted. Only programs consisting of about the same number of integer and floating-point operations can exploit VLIW processors efficiently.

### 2.1.5 Superscalar Processors

Like long instruction word processors, superscalar processors contain several independent functional units and pipelines. Superscalar processors, however, are capable of scheduling independent instructions to different units dynamically at run time. Therefore, such processors must be able to detect instruction dependencies. They have to ensure that dependent instructions are executed in the same order they appeared in the instruction stream.

Modern superscalar RISC processors belong to the most complex processors ever built. To feed their multiple pipelines, several instructions must be fetched from memory at once, thus making fast and large caches inevitable. Also, sophisticated compilers are needed to provide a well balanced mix of independent integer and floating-point instructions to ensure that all pipelines are kept busy during execution. Because of the complexity of superscalar processors their clock cycles cannot be shortened to the same extent than in simpler processors.

**Example 2.4 (Superscalar Processor)** The IBM POWER 4 is capable of issuing up to 8 instructions per cycle, with a sustained completion rate of five instructions. As its stages are very complex, it runs at only 1.30 GHz.

The AMD Athlon XP 2100+ processor running at 1733 MHz features a floating-point adder and a floating-point multiplier both capable of issuing one two-way vector operation per cycle.

## 2.2 Advanced Architectural Features

Superscalar processors dynamically schedule instructions to multiple pipelines and other functional units. As performance is the top-most goal, all pipelines and execution units must be kept busy in order to achieve maximum performance. Dependencies among instructions can hinder the pipeline from running smoothly, advanced features have to be designed to detect and resolve dependencies. Other design features have to make sure that the instructions are executed in the same order they entered the processor.

### 2.2.1 Functional Parallelism

As was said before, superscalar RISC processors contain several execution units and pipelines that can execute instructions in parallel. To keep all units busy as long as possible, it must be assured that there are always instructions to execute, waiting in buffers. Such buffers are called *reservation stations* or *queues*. Every execution unit can have a reservation station of its own or get the instructions from one global queue. Also, for each instruction leaving such a station, another one should be brought from memory. Thus, memory and caches have to deliver several instructions each cycle.

Depending on the depths of the used pipelines, some operations might take longer than others. It is therefore possible that instruction i + 1 is finished, while instruction i is still being processed in a pipeline. Also, an integer pipeline may get idle, while the floating-point unit is still busy. Thus, if instruction i + 1 is an integer operation, while instruction i is a floating-point operation, i + 1 might be put into the integer pipeline, before i can enter the floating-point unit. This is called *out-of-order* execution. The instruction stream leaving the execution units will often differ from the original instruction stream. Thus, earlier instructions must wait in a *reorder buffer* for all prior instructions to finish, before their results are written back.

### 2.2.2 Registers

Registers obviously introduce some kind of bottleneck, if too many values have to be stored in registers within a short piece of code. The number of existing registers depends on the designs of the underlying architecture. The set of registers known to compilers and programs is called the *logical* register file. To guarantee software compatibility with predecessors, the number of logical registers cannot be increased within the same processor family. Programs being compiled for new processors having more registers could not run on older versions with a smaller number of registers. However, it is possible to increase the number of *physical* registers existing within the processor and to use them to store intermediate values.

### 2.2.3 Fused Multiply-Add Instructions

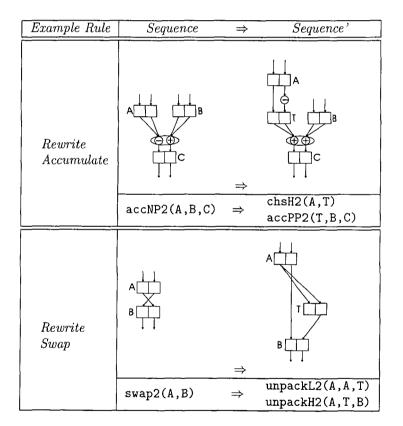

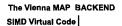

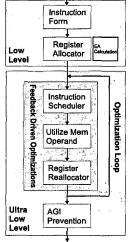

In current microprocessors equipped with fused multiply-add (FMA) instructions, the floating-point hardware is designed to accept up to three operands for executing FMA operations, while other floating-point instructions requiring fewer operands may utilize the same hardware by forcing constants into the unused operands. In general, FPUs with FMA instructions use a multiply unit to compute  $a \times b$ , followed by an adder to compute  $a \times b + c$ .