#### DISSERTATION

# An Integrated 17 GHz Receiver in $0.13 \,\mu m$ CMOS for Wireless Applications

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

> ao. Univ. Prof. Dr. Arpad L. Scholtz E389

Institut für Nachrichtentechnik und Hochfrequenztechnik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

#### Dipl.-Ing. Christoph Kienmayer

Matrikelnummer 9625303

Franz Diebl Str. 38 A-3921 Langschlag

Mostan fremange

Wien, im November 2004

Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at). The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# Contents

| 1 | Intr                   |                                   | 1  |

|---|------------------------|-----------------------------------|----|

|   | 1.1                    | Current State-of-the-Art          | 3  |

| 2 | Wir                    | eless LAN Systems                 | 5  |

|   | 2.1                    | Introduction                      | 5  |

|   | 2.2                    | Receiver Architectures            | 8  |

|   |                        |                                   | 8  |

|   |                        |                                   | 9  |

|   |                        | •                                 | 1  |

|   | 2.3                    |                                   | .2 |

|   |                        |                                   | .2 |

|   |                        |                                   | 2  |

|   |                        |                                   | 3  |

|   |                        | 1                                 | .4 |

|   |                        |                                   | 4  |

|   |                        | 2.0.0 Coung                       |    |

| 3 | $\mathbf{C}\mathbf{M}$ | OS Technology 1                   | 5  |

|   | 3.1                    | The nMOS Transistor               | .5 |

|   | 3.2                    | Passive Devices                   | 20 |

|   |                        | 3.2.1 Inductors                   | 20 |

|   |                        | 3.2.2 Capacitors                  | 24 |

|   |                        | 3.2.3 Varactors                   | 25 |

|   | 3.3                    | C11N CMOS Technology              | 29 |

| 4 | <b>D</b>               | since Anabitestone and Constitute | 51 |

| 4 | <b>Rec</b> 4.1         |                                   | 31 |

|   |                        |                                   |    |

|   | 4.2                    |                                   | 32 |

|   | 4.3                    |                                   | 32 |

|   |                        |                                   | 33 |

|   |                        | 8                                 | 34 |

|   |                        |                                   | 36 |

|   |                        |                                   | 86 |

|   |                        |                                   | 86 |

|   |                        |                                   | 86 |

|   | 4.4                    | Circuit Specification             | 39 |

.

| Bibliography                                                                                                                                                                                          | 102                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Acknowledgements                                                                                                                                                                                      | 101                                                  |

| Curriculum Vitae                                                                                                                                                                                      | 100                                                  |

| 7 Conclusion and Outlook                                                                                                                                                                              | 99                                                   |

| <ul> <li>6.8 Two-Tone Third-Order Intermodulation</li> <li>6.9 Noise Figure</li> <li>6.10 LO Leakage Radiation at the RF-Input</li> <li>6.11 Performance Summary</li> </ul>                           | . 96<br>. 97                                         |

| <ul> <li>6.5 Single-Tone Compression Measurement</li></ul>                                                                                                                                            | . 93                                                 |

| <ul> <li>6 Receiver Experimental Results</li> <li>6.1 Introduction</li></ul>                                                                                                                          | . 86<br>. 91                                         |

| 5.5 $1^{st}$ Down-conversion Mixer5.6Intermediate Frequency Amplifier5.7 $2^{nd}$ Down-conversion Mixer5.8Voltage Controlled Oscillator5.9I/Q-Divider5.10LO-Buffer5.11Operational-Amplifier           | . 56<br>. 65<br>. 69<br>. 73<br>. 78<br>. 82<br>. 83 |

| <ul> <li>5 Receiver Implementation</li> <li>5.1 Introduction</li></ul>                                                                                                                                | . 43<br>. 46                                         |

| 4.4.1Low Noise Amplifier4.4.2 $1^{st}$ -Mixer4.4.3IF Amplifier4.4.3IF Amplifier4.4.4 $2^{nd}$ -Mixer4.4.5Operational Amplifier4.4.6Voltage Controlled Oscillator4.5Specification Summary4.6Conclusion | . 39<br>. 39<br>. 39<br>. 40<br>. 40<br>. 40         |

# List of Figures

| 1.1  | Global wireless standards to ensure interoperability               | 1  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Home usage scenarios that could be wired or wireless               | 2  |

| 2.1  | Technology, mobility and data rates of communication systems.      | 7  |

| 2.2  | Block diagram of a homodyne I/Q receiver.                          | 9  |

| 2.3  | Frequency translation in a zero-IF receiver                        | 9  |

| 2.4  | Block diagram of a heterodyne receiver                             | 10 |

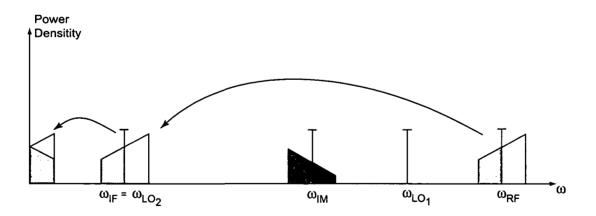

| 2.5  | Frequency translation in an IF receiver                            | 10 |

| 2.6  | Block diagram of a sliding IF receiver.                            | 11 |

| 2.7  | Frequency translation in a sliding IF receiver.                    | 11 |

| 2.8  | Outdoor scenario for a multipath link.                             | 13 |

| 2.9  | Block diagram of a receiver using antenna diversity (a), and a     |    |

|      | complete receive-chain diversity (b)                               | 14 |

| 3.1  | Typical sub- $\mu$ m CMOS technology transistor cross-section      | 15 |

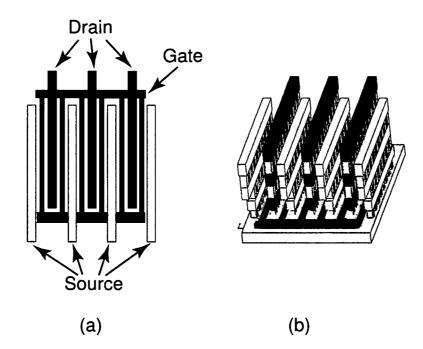

| 3.2  | Layout of a folded MOS transistor (a) planar cut (b) 3D view       | 16 |

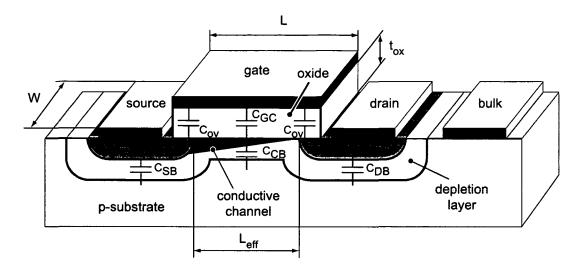

| 3.3  | n-channel MOSFET with parasitic capacitances                       | 17 |

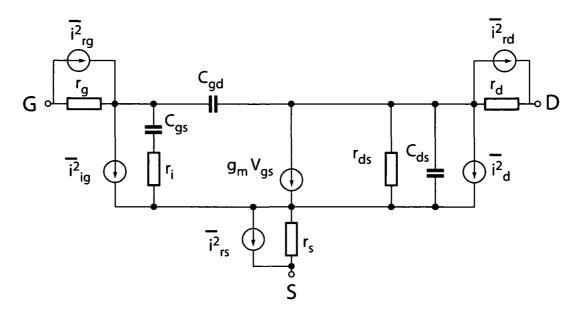

| 3.4  | Small signal model including the noise sources                     | 19 |

| 3.5  | Cross-coupled symmetrical inductor for a resonant frequency of 3.4 |    |

|      | GHz                                                                | 21 |

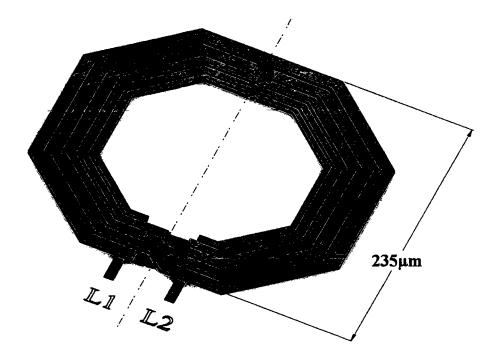

| 3.6  | Symmetrical inductor                                               | 22 |

| 3.7  | Inductor cross-section and parasitic components                    | 22 |

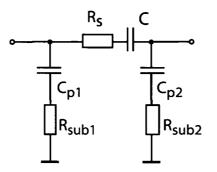

| 3.8  | Low order equivalent circuit                                       | 24 |

| 3.9  | Differential inductor lumped model                                 | 24 |

| 3.10 | RF-capacitor lumped model                                          | 25 |

| 3.11 | Cross-section of a conventional NMOS varactor in depletion (a)     |    |

|      | and the generally assumed model (b). The dashed line indicates     |    |

|      | the border of the depletion region                                 | 26 |

| 3.12 | Typical measured small-signal capacitance characteristic of a NMOS |    |

|      | varactor (bottom), the corresponding charges (top) and the rele-   |    |

|      | vant lumped elements (middle) at zero tuning voltage. Oxide, in-   |    |

|      | terface charges and charges at $pn$ junctions are not shown        | 27 |

| 3.13 | Typical multifinger structure of RF varactors. Dashed line indi-   |    |

|      | cates area of thin oxide.                                          | 28 |

|      |                                                                    |    |

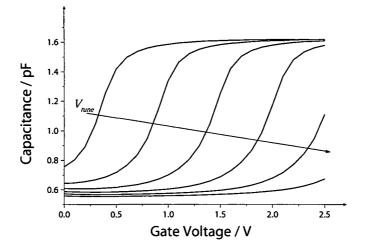

| 3.14  | Typical measured small-signal capacitance characteristic of a con-<br>ventional NMOS varactor at various tuning voltages (0V2.5V;<br>0.5V steps). | 29         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

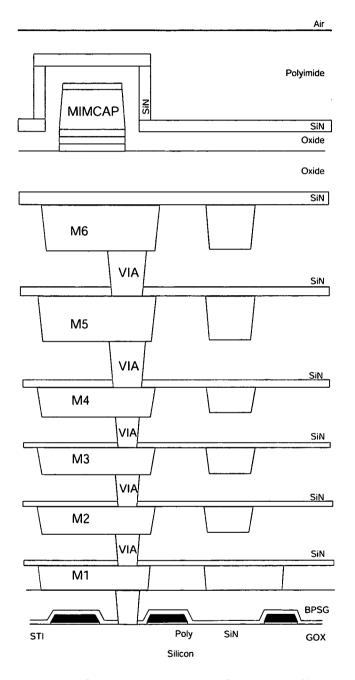

| 3.15  | Cross section of the C11N metallization.                                                                                                          | 30         |

| 4.1   | Overview of HIPERLAN Types, HIPERACCESS and HIPERLINK.                                                                                            | 31         |

| 4.2   | Block diagram of a double conversion receiver.                                                                                                    | 32         |

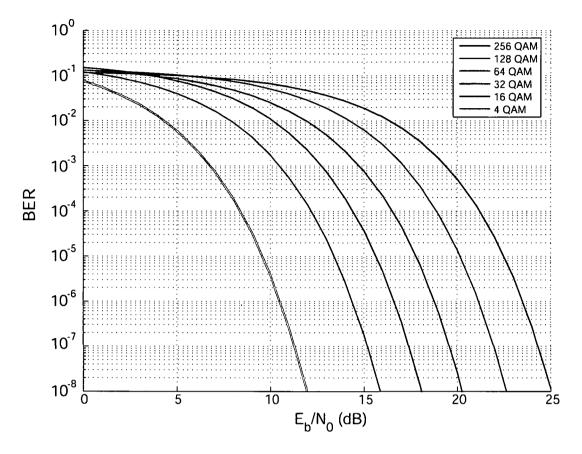

| 4.3   | Bit-error rate of uncoded QAM-signals as a function of $E_b/N_0$ .                                                                                | 34         |

| 4.4   | Propagation loss at 17.2 GHz for indoor and free space waves                                                                                      | 35         |

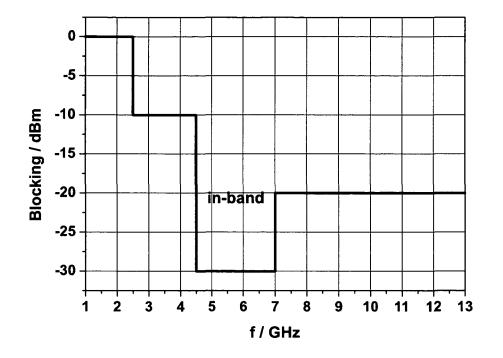

| 4.5   | The allowed blocking signal levels for a 5 GHz WLAN system                                                                                        | 37         |

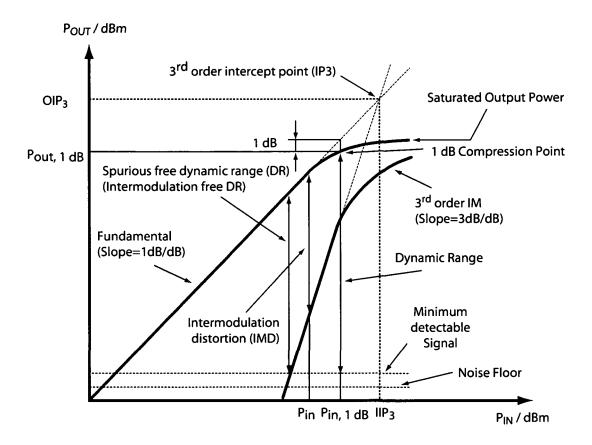

| 4.6   | Output power of fundamental and $IM_3$ versus input power                                                                                         | 38         |

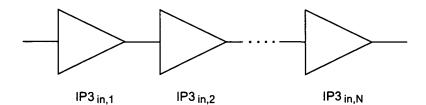

| 4.7   | System input $IP_3$ calculation                                                                                                                   | 38         |

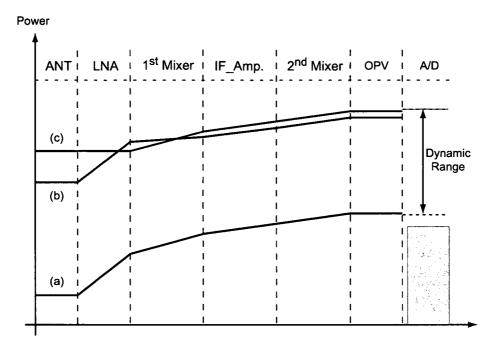

| 4.8   | Level diagram of the receiver.                                                                                                                    | 41         |

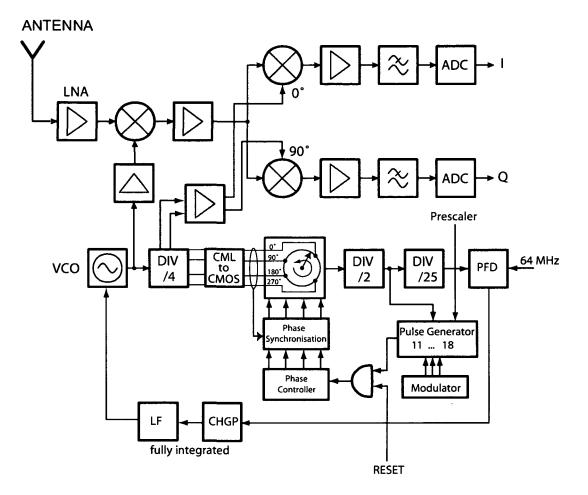

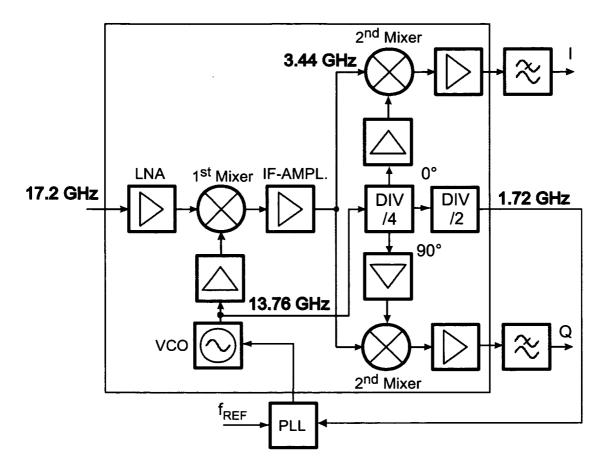

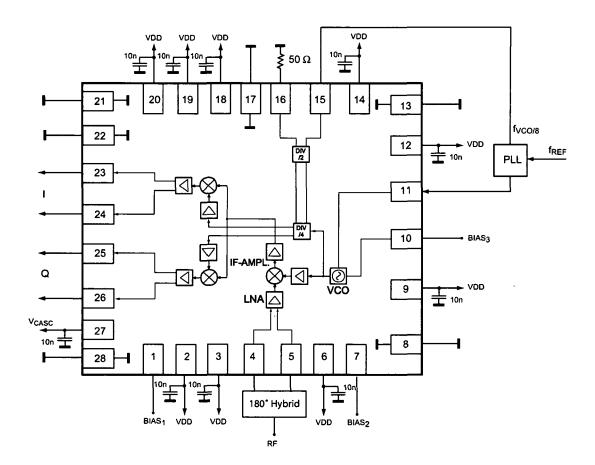

| 5.1   | Block diagram of the integrated receiver.                                                                                                         | 43         |

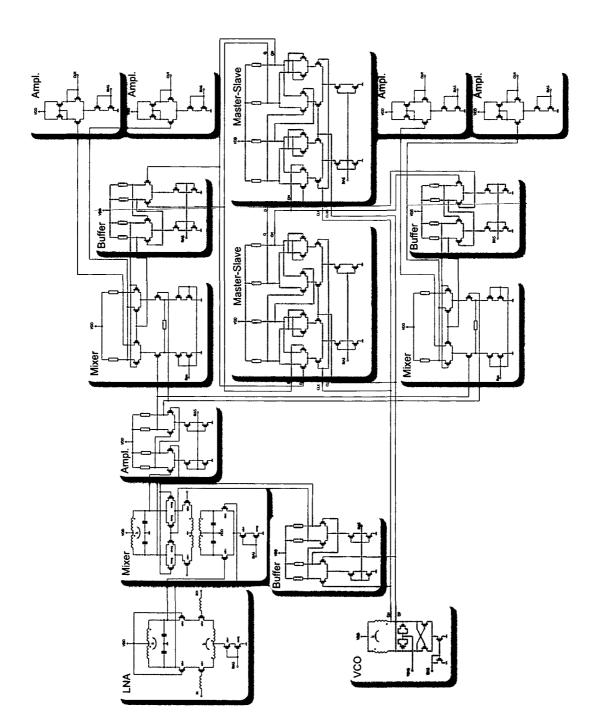

| 5.2   | Schematic of the receiver (signal and LO path are colored)                                                                                        | 44         |

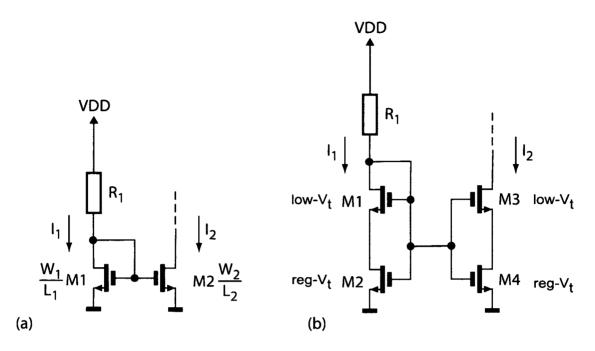

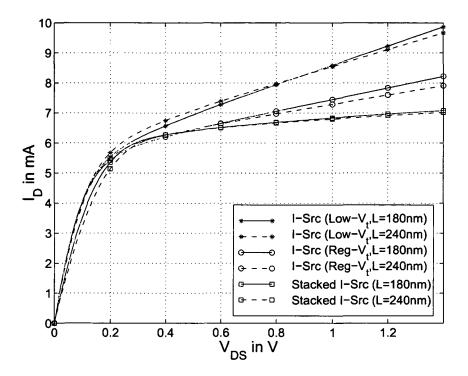

| 5.3   | Schematic of a conventional current mirror (a) and stacked current                                                                                |            |

|       | source (b)                                                                                                                                        | 47         |

| 5.4   | Current source characteristic of conventional current mirror with                                                                                 |            |

|       | low- $V_T$ and regular- $V_T$ devices and the stacked current source.                                                                             | 48         |

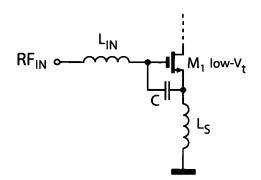

| 5.5   | Input matching of a LNA with two inductors.                                                                                                       | 49         |

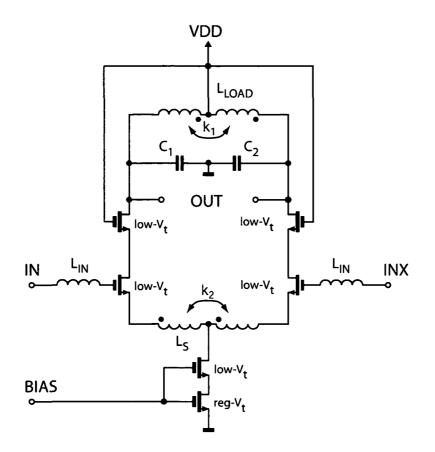

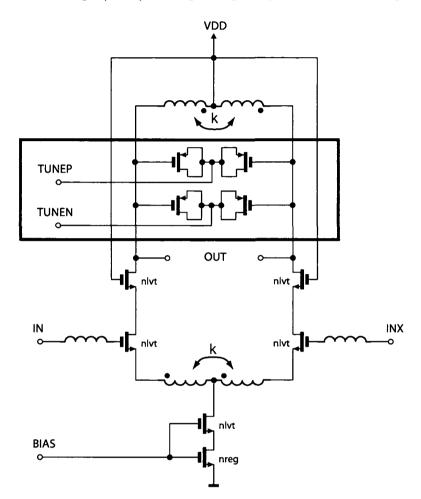

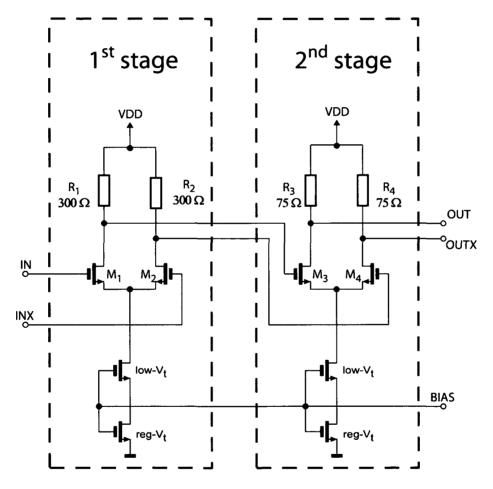

| 5.6   | Schematic of the LNA.                                                                                                                             | 50         |

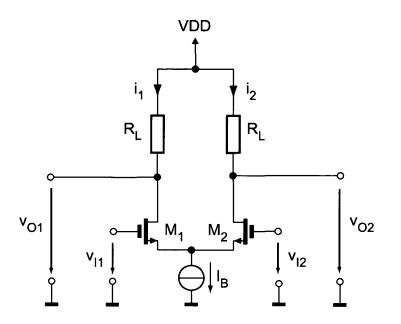

| 5.7   | MOS differential pair                                                                                                                             | 51         |

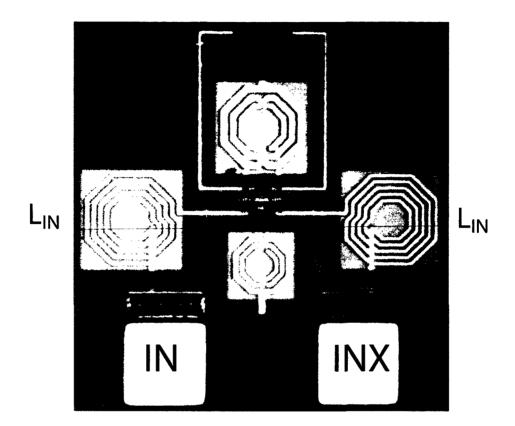

| 5.8   | Chip photograph of the LNA.                                                                                                                       | 53         |

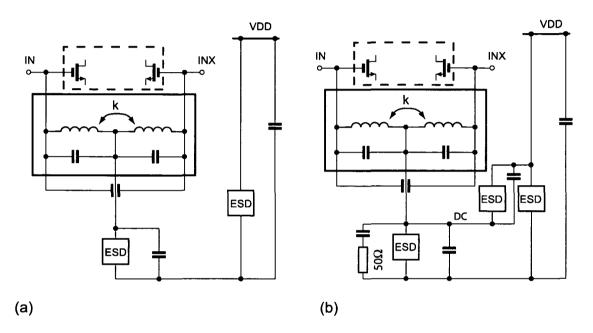

| 5.9   | Implementation example of a LNA with varactors                                                                                                    | 54         |

| 5.10  | Proposed ESD protection for differential input stages                                                                                             | 55         |

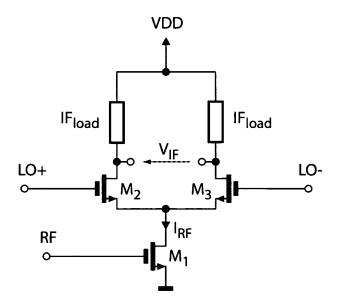

| 5.11  | 0                                                                                                                                                 | 56         |

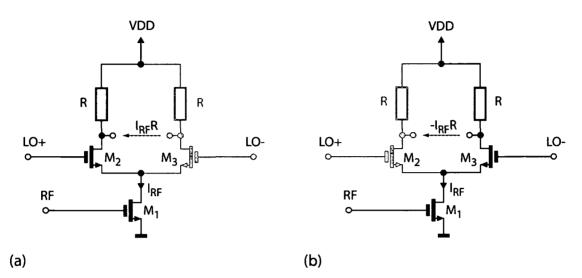

| 5.12  | Mixer in (a) LO+ phase: $M_2$ ON, $M_3$ OFF, (b) LO- phase: $M_2$ OFF, $M_3$ ON.                                                                  | 57         |

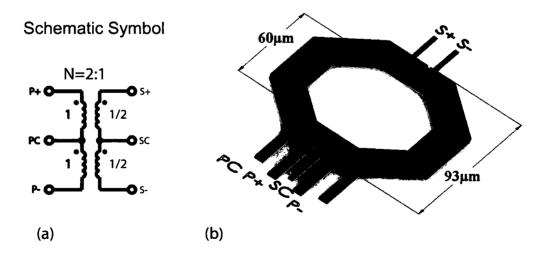

| 5 1 3 | Mixer transformer: (a) winding scheme (b) schematic symbol.                                                                                       | 58         |

|       | Mixer transformer equivalent circuit.                                                                                                             | 59         |

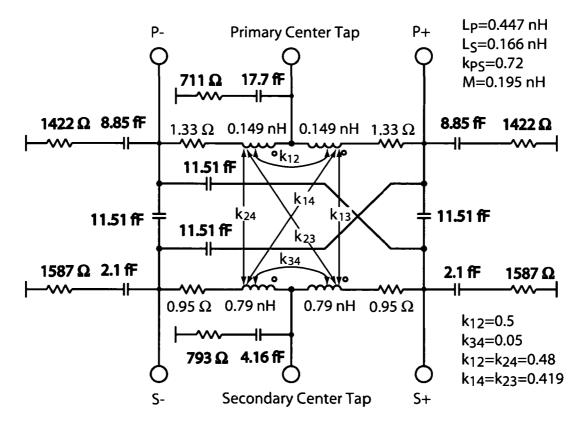

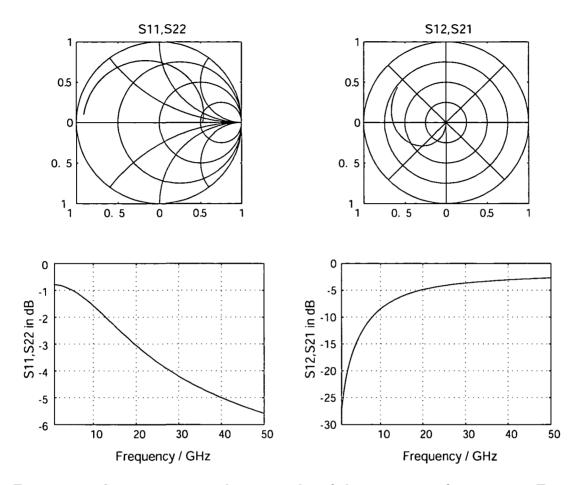

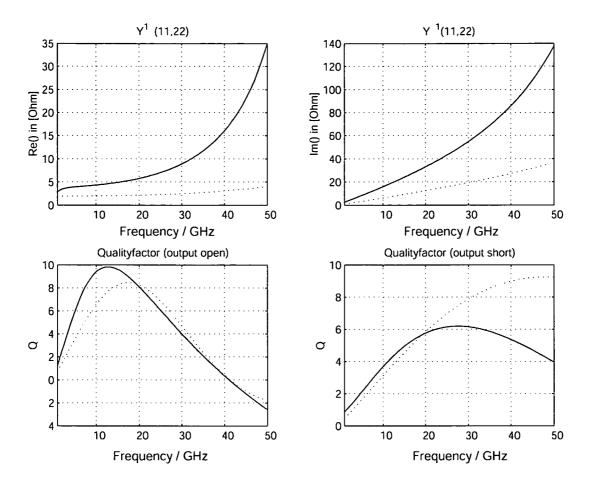

|       | S-Parameter simulation results of the input transformer using Fast-                                                                               | 00         |

| 0.10  | Trafo.                                                                                                                                            | 60         |

| 5 16  | $Y^{-1}$ -Parameter simulation results of the input transformer using                                                                             | 00         |

| 0.10  | Fast-Trafo                                                                                                                                        | 61         |

| 5 17  | Z-Parameter simulation results of the input transformer using Fast-                                                                               | 01         |

| 0.11  | Trafo.                                                                                                                                            | 62         |

| 5 18  | Schematic of the 6.6 nH inductor.                                                                                                                 | 62         |

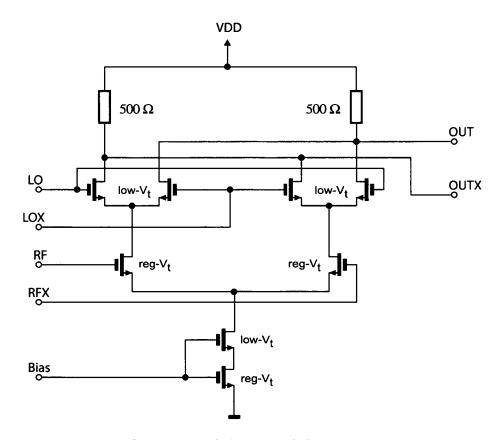

|       | Schematic of the first down-conversion mixer.                                                                                                     | 63         |

|       | Chip photograph of the first down-conversion mixer.                                                                                               | <b>6</b> 4 |

|       | Schematic of the intermediate frequency amplifier.                                                                                                | 65         |

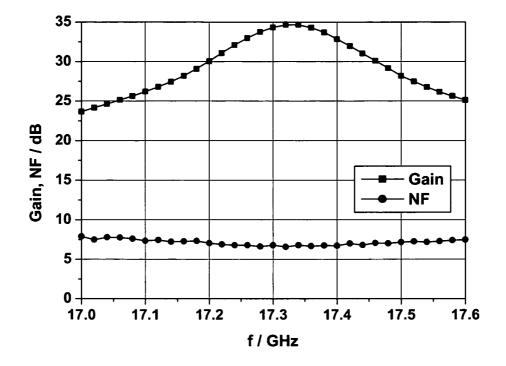

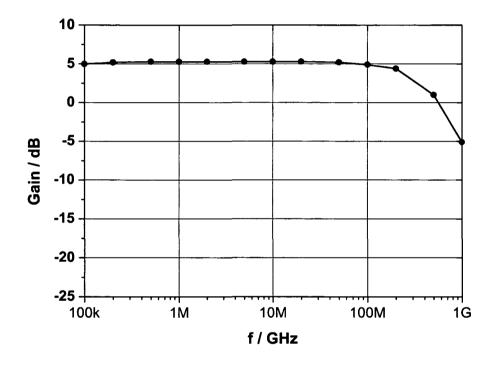

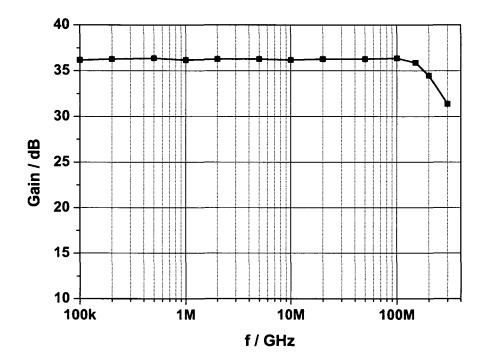

|       | Gain and noise figure versus frequency at a fixed IF of 3.4 GHz.                                                                                  | 67         |

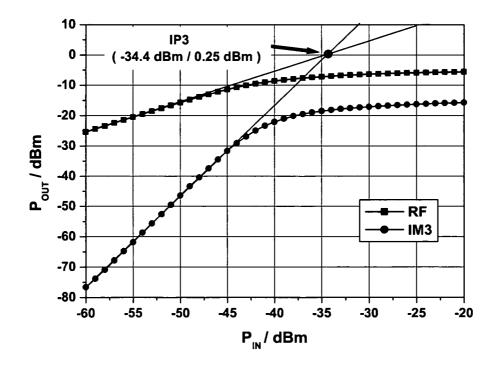

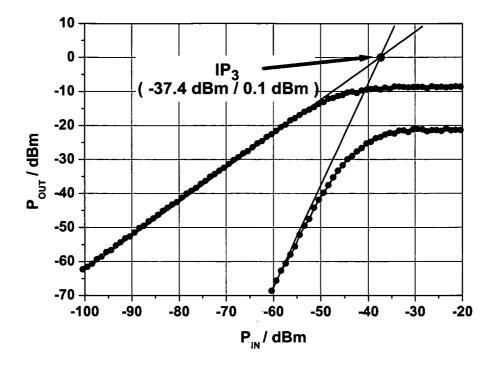

|       | Measured front-end two tone test.                                                                                                                 | 67         |

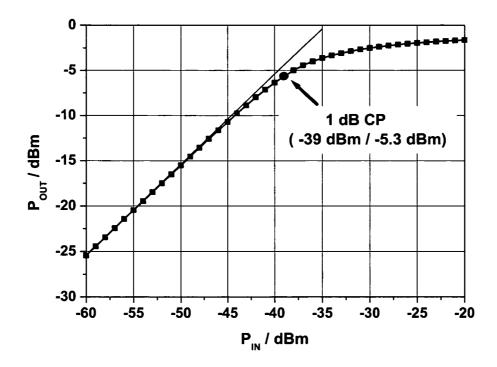

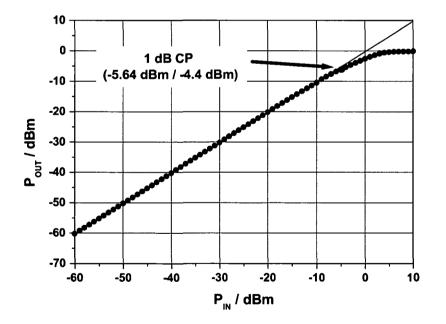

|       | Measured power transfer characteristic of the receiver.                                                                                           | 68         |

|       | Schematic of the second down-conversion mixer.                                                                                                    | 69         |

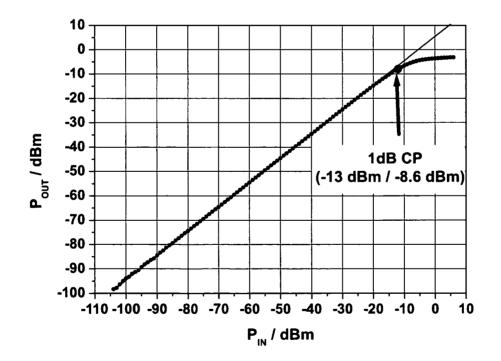

| 5.26 | Measured single-tone compression point.                                    | 70         |

|------|----------------------------------------------------------------------------|------------|

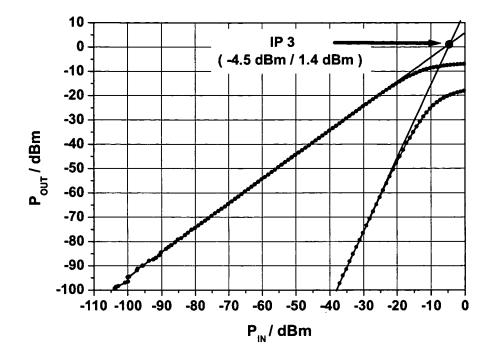

| 5.27 | Linearity measurement of the second down-conversion mixer                  | 71         |

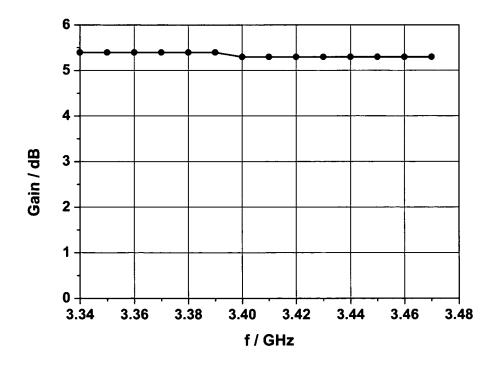

| 5.28 | Mixer gain versus input frequency at 1 MHz output frequency                | 71         |

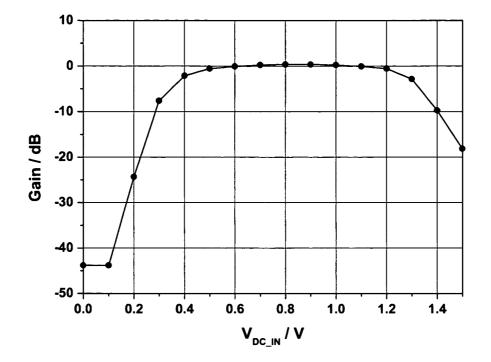

| 5.29 | Gain versus baseband frequency.                                            | 72         |

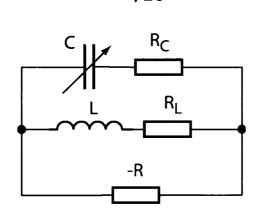

| 5.30 | Basic inductor-capacitor (LC) VCO.                                         | 73         |

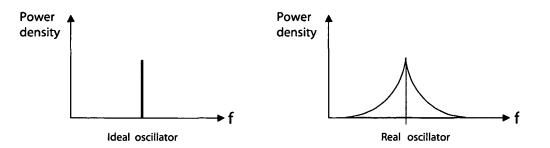

| 5.31 | Frequency spectrum of ideal and real oscillators                           | 74         |

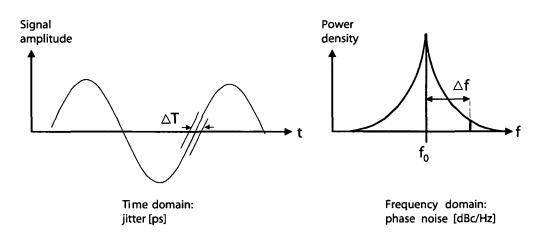

|      | Jitter in the time domain relates to phase noise in the frequency          |            |

|      | domain                                                                     | 74         |

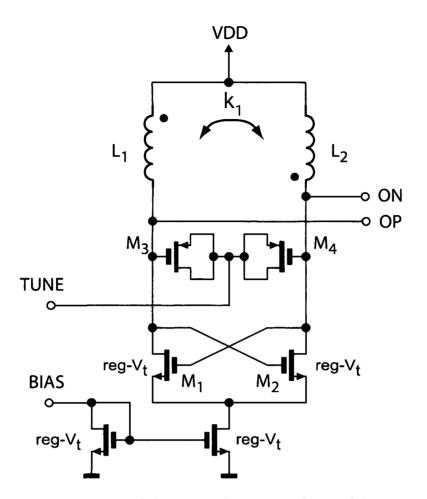

| 5.33 | Schematic of the 13.76 GHz VCO.                                            | 75         |

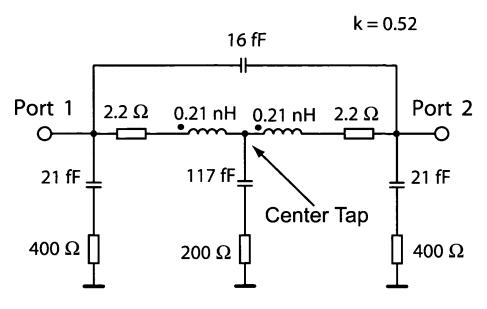

| 5.34 | VCO inductor equivalent circuit.                                           | 76         |

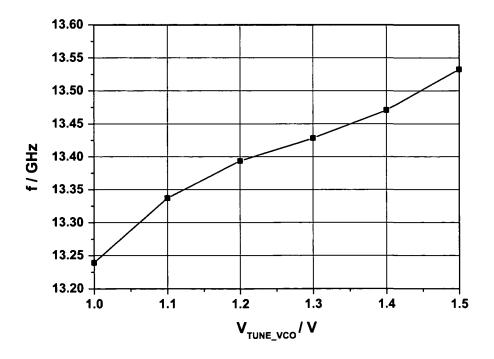

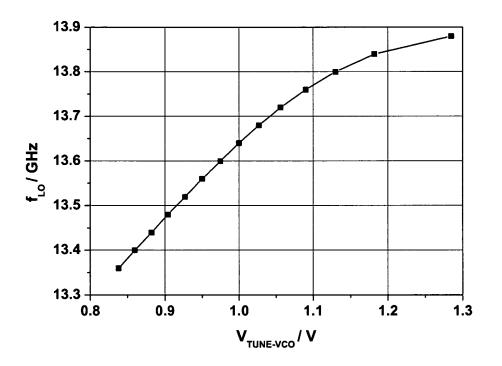

| 5.35 | VCO frequency versus tuning voltage                                        | 76         |

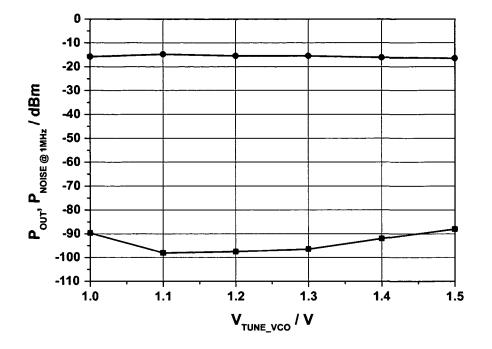

| 5.36 | Measured output power and phase noise power versus tuning voltage.         | 77         |

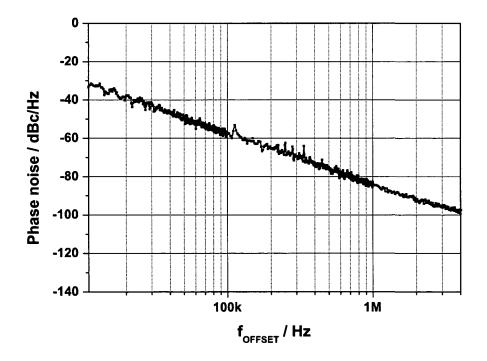

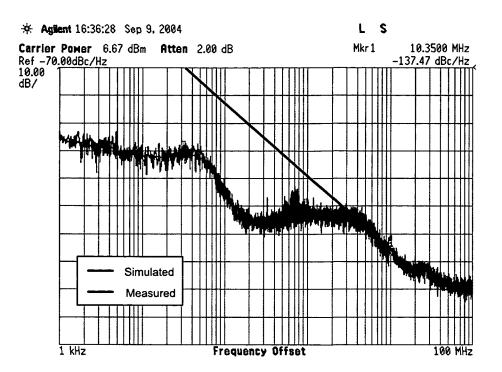

| 5.37 | Measured VCO phase noise at $V_{TUNE_VCO}$ of 1.5 V                        | 77         |

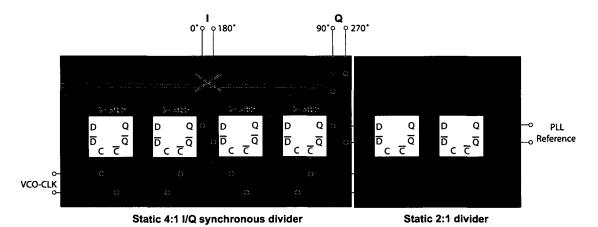

| 5.38 | Block diagram of clock generation with latches.                            | 78         |

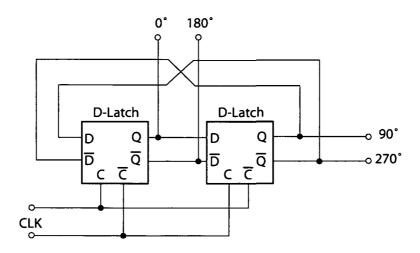

| 5.39 | Block diagram of a static frequency 2:1 divider.                           | 79         |

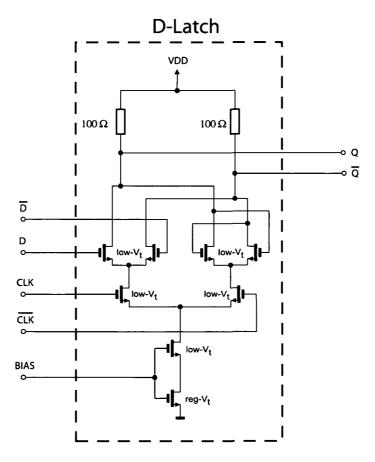

| 5.40 | D-latch circuit diagram.                                                   | 79         |

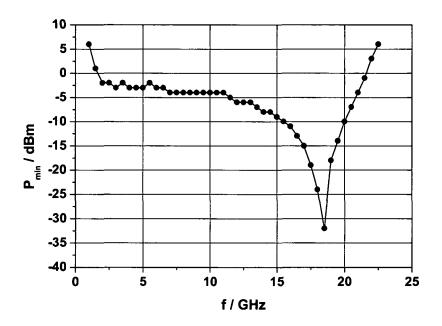

| 5.41 | Measured divider sensitivity versus input power                            | 80         |

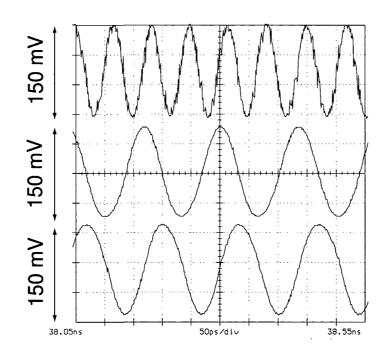

| 5.42 | Measured single ended input and output waveforms at the input              |            |

|      | frequency of 15 GHz.                                                       | 81         |

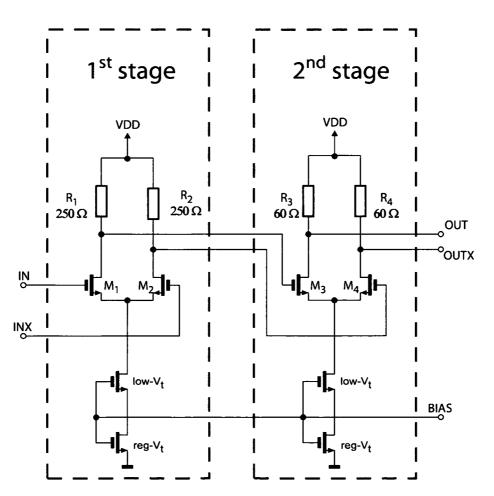

| 5.43 | Schematic diagram of the two stage LO-buffer                               | 82         |

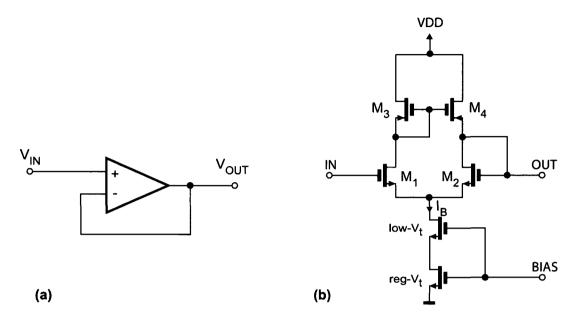

| 5.44 | Symbol (a) and schematic (b) of the operational amplifier                  | 84         |

| 5.45 | Linearity plot of the operational amplifier.                               | 84         |

| 5.46 | Gain versus DC bias voltage of the operational amplifier                   | 85         |

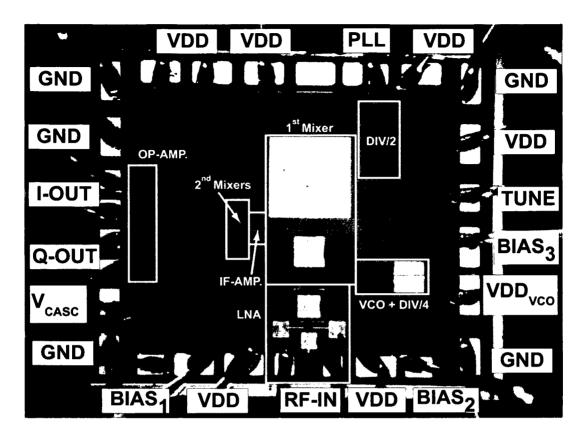

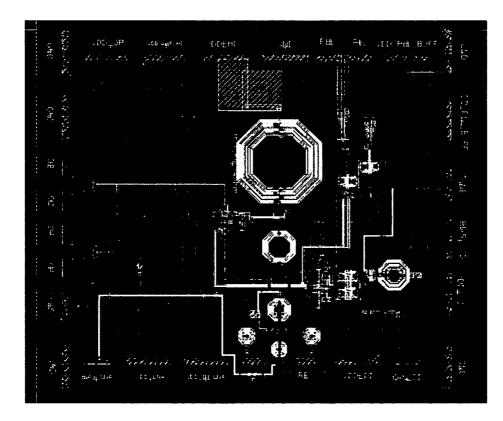

| 6.1  | Chip photograph of the receiver testchip (chipsize $1 \times 1.2  mm^2$ ). | 87         |

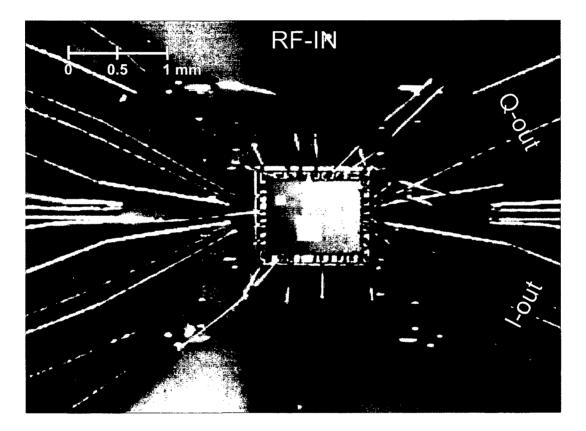

| 6.2  | Photograph of the bonded chip on a test-board (chipsize $1 \times$         | <b>~</b> . |

| •••  | $1.2  mm^2$ ).                                                             | 88         |

| 6.3  | Application circuit of the receiver.                                       | 89         |

| 6.4  | Layout of the receiver.                                                    | 90         |

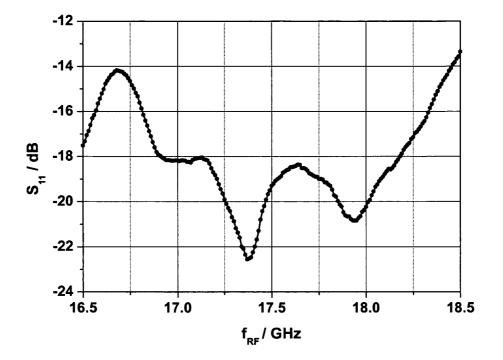

| 6.5  | Input reflection coefficient $(S_{11})$                                    | 92         |

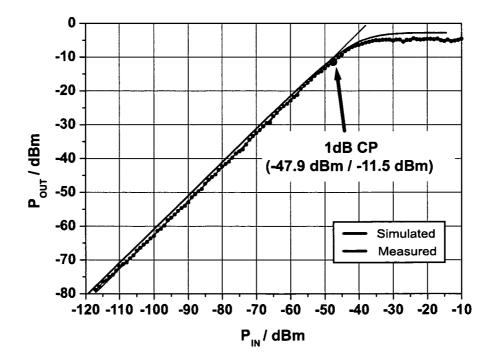

| 6.6  | 1 dB compression point at 1 MHz output frequency.                          | 92         |

| 6.7  | Conversion gain in the baseband.                                           | 93         |

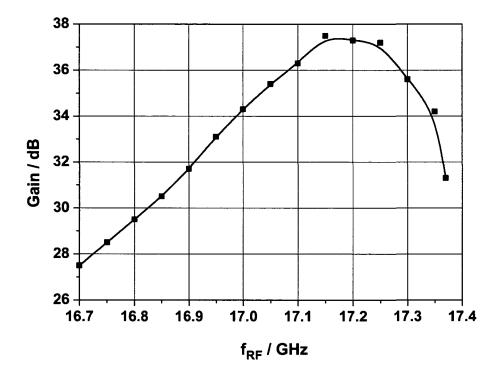

| 6.8  | Conversion gain in the 17.2 GHz ISM band.                                  | 94         |

| 6.9  | Measured frequency tuning of locked VCO.                                   | 95         |

|      | Measured phase noise of locked VCO compared to simulation of               |            |

|      | free running VCO.                                                          | 96         |

| 6.11 | Measured $IP_3$ compression point performance                              | 97         |

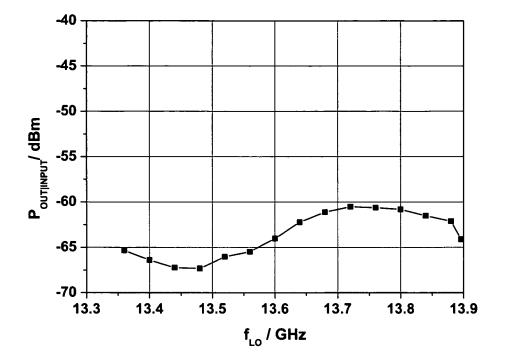

|      | LO leakage radiation at the input port.                                    | 98         |

|      |                                                                            |            |

.

# List of Tables

| 1.1 | 17 GHz WLAN versus UWB                                              | 3  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | Published state-of-the-art work.                                    | 3  |

| 2.1 | Summary of current BRAN system types and definitions                | 6  |

| 4.1 | Receiver performance requirements for a $5\mathrm{GHz}$ WLAN system | 34 |

| 4.2 | Summery of the derived specifications for the receivers building    |    |

|     | blocks                                                              | 40 |

| 6.1 | DC power consumption of receiver                                    | 91 |

| 6.2 | Performance summary of complete receiver.                           | 98 |

### List of Abbreviations

| ADC                  | Analog-Digital Converter                        |

|----------------------|-------------------------------------------------|

| AP                   | Access Point                                    |

| AWGN                 | Additive White Gaussian Noise                   |

| BER                  | Bit Error Rate                                  |

| BRAN                 | Broadband Radio Access Networks                 |

| $C_L$                | Load capacitance in F                           |

| $C_{CB}$             | Channel-bulk capacitance in F                   |

| $C_{DB}$             | Drain-bulk capacitance in F                     |

| $C_{GC}$             | Gate-channel capacitance in F                   |

| $C_{gd}$             | Parasitic gate-drain capacitance in F           |

| $C_{gs}$             | Parasitic gate-source capacitance in F          |

| $C_{ox}$             | Oxide capacitance per unit area in $F/m^2$      |

| $C_{OV}$             | Gate overlap capacitance in F                   |

| $C_{SB}$             | Source-bulk capacitance in F                    |

| $\sigma$             | Conductivity                                    |

| C11N                 | Infineons $0.13 \mu \text{m}$ CMOS technology   |

| CA                   | Collision Avoidance                             |

| CAD                  | Computer-Aided Design                           |

| CEPT                 | Conference of Postal and Telecommunication      |

| CMOS                 | Complementary Metal Oxide Semiconductor         |

| CSMA                 | Carrier Sense Multiple Access                   |

| D                    | Data                                            |

| DC                   | Direct Current                                  |

| DECT                 | Digital Enhanced Cordless Telecommunications    |

| DSSS                 | Direct Sequence Spread Spectrum                 |

| $\varepsilon_{ox}$   | Dielectric constant of oxide in As/Vm           |

| $\varepsilon_r$      | Relative permittivity in 1                      |

| EDGE                 | Enhanced Data for GSM Evolution                 |

| $\operatorname{ESD}$ | Electrostatic Discharge                         |

| $\operatorname{ERC}$ | European Resuscitation Council                  |

| ETSI                 | European Telecommunications Standards Institute |

| $f_{max}$            | Maximum oscillation frequency in Hz             |

| $f_t$                | Transit frequency in Hz                         |

| FHSS                 | Frequency Hopping Spread Spectrum               |

| FIB                  | Focused-Ion Beam                                |

| $\gamma$             | Bias-dependent parameter                        |

| GaAs                 | Gallium-Arsenide                                |

| GBW                  | Gain Bandwidth Product                          |

| GSM                  | Global System for Mobile communication          |

| GPIB                 | General Purpose Interface Bus                   |

|                      |                                                 |

| GPRS                      | General Packet Radio Service                              |

|---------------------------|-----------------------------------------------------------|

| $g_m$                     | Transconductance in S                                     |

| $g_{mn}$                  | Transconductance of nMOS device in S                      |

| $g_{mp}$                  | Transconductance of pMOS device in S                      |

| HB                        | Harmonic Balance                                          |

| $\mathbf{HF}$             | High Frequency                                            |

| $I_d$                     | Drain current in A                                        |

| $i_g$                     | Gate current in A                                         |

| I                         | Inphase Output                                            |

| IC                        | Integrated Circuit                                        |

| IEEE                      | Institute of Electrical and Electronics Engineers         |

| IF                        | Intermediate Frequency                                    |

| IMD                       | Intermodulation Distortion                                |

| ISDN                      | Integrated Services Digital Network                       |

| ISI                       | Intersymbol Interference                                  |

| ISM                       | Industrial, Scientific and Medical band                   |

| $J_D$                     | Drain current-density per drain width in A/m              |

| k                         | Boltzmann's constant in $J/K$ / Coupling coefficient in 1 |

| $\frac{\lambda}{\lambda}$ | Channel length modulation parameter in $V^{-1}$           |

| L                         | Transistor gate length in m                               |

| $\overline{L_{eff}}$      | Effective transistor gate length in m                     |

| $L_{min}$                 | Minimum transistor gate length in m                       |

| LAN                       | Local Area Network                                        |

| LDD                       | Lightly Doped Drain                                       |

| LO                        | Local Oscillator                                          |

| LNA                       | Low Noise Amplifier                                       |

| $\mu_n$                   | Mobility of electrons in $m^2/Vs$                         |

| $\mu_p$                   | Mobility of holes in $m^2/Vs$                             |

| MAN                       | Metropolitan Area Network                                 |

| MBS                       | Mobile Broadband System                                   |

| Mbps                      | Megabits per second                                       |

| MIM                       | Metal-Insulator-Metal capacitor                           |

| MS-FF                     | Master-Slave Flip-Flop                                    |

| OTA                       | Operational Transconductance Amplifier                    |

| PAN                       | Personal Area Network                                     |

| PC                        | Personal Computer                                         |

| PCB                       | Printed Circuit Board                                     |

| PDA                       | Personal Digital Assitant                                 |

| PIP                       | Poly-to-Poly capacitor                                    |

| Q                         | Quadrature output                                         |

| QI-Divider                | Frequency divider with inphase and quadrature component   |

| RF                        | Radio Frequency                                           |

| RFIC                      | Radio Frequency Integrated Circuit                        |

| $r_D$                     | Drain resistance of a MOS in $\Omega$                     |

| · D                       |                                                           |

| $r_{DS}$       | Drain-Source resistance of a MOS in $\Omega$     |

|----------------|--------------------------------------------------|

| $r_G$          | Gate resistance of a MOS in $\Omega$             |

| $r_i$          | Channel charging resistance of a MOS in $\Omega$ |

| $r_o$          | Drain output resistance of a MOS in $\Omega$     |

| R <sub>o</sub> | Output resistance of current source in $\Omega$  |

| $r_S$          | Source resistance of a MOS in $\Omega$           |

| RO4003         | Rogers microwave substrate                       |

| S              | Scaling factor                                   |

| Si             | Silicon                                          |

| SIG            | Bluetooth Special Interest Group                 |

| SiGe           | Silicon-Germanium                                |

| SOI            | Silicon-On-Insulator                             |

| $SiO_2$        | Silicon-dioxide                                  |

| SMA            | Sub-miniature A connector                        |

| SNR            | Signal-to-Noise Ratio                            |

| SRD            | Short Range Devices                              |

| STI            | Shallow trench isolation                         |

| $t_{ox}$       | Gate oxide thickness in m                        |

| Т              | Temperature in K                                 |

| TiN            | Titanium-Nitride                                 |

| UMTS           | Universal Mobile Telecommunication System        |

| USB            | Universal Serial Bus                             |

| UWB            | Ultra Wide-Band                                  |

| VCO            | Voltage Controlled Oscillator                    |

| VCVS           | Voltage-Controlled Voltage-Source                |

| $V_{ds}$       | Drain-source voltage in V                        |

| $V_{dsat}$     | Drain-source saturation voltage in V             |

| $V_{gs}$       | Gate-source voltage in V                         |

| $V_T$          | Threshold voltage in V                           |

| W              | Transistor width in m                            |

| WAN            | Wide Area Network                                |

| WLAN           | Wireless Local Area Network                      |

| $\omega_t$     | Transit angular frequency in Hz                  |

| $\omega_{max}$ | Maximum oscillation angular frequency in Hz      |

### Notation

Throughout the thesis, signals (voltages and currents) are denoted in accordance with:

- Constant voltages and currents: with capital letters and capital indices (e.g.  $V_{SS}$ )

- Total instantaneous voltages and currents: with capital letters and small indices (e.g.  $I_d$ )

- Small-signal voltages and currents in the time domain: with small letters and small indices (e.g.  $i_d$ )

- MOS transistors with a bulk- $V_{SS}$  connection are drawn as three-terminal device in the circuit diagrams.

# Abstract

This work presents the design and implementation of a fully integrated receiver in  $0.13 \,\mu\text{m}$  CMOS for the 17.2 GHz WLAN/ISM band. The main challenges are the high frequency of operation, high integration level and low power consumption. This thesis explores possible solutions for these challenges by careful active and passive component design, circuit design and receiver partitioning to achieve an optimum result.

The receiver has been designed using the  $0.13 \,\mu\text{m}$  CMOS process from Infineon Technologies AG. By avoiding the mandatory external filters of classical heterodyne receivers, a so-called "sliding-IF" double-conversion architecture offers more flexibility for the integration of a complete receiver on a single chip. As introduction, several receiver architectures are presented and the wave propagation effects at 17 GHz are discussed. Different levels of abstraction, starting with receiver specifications to building blocks are documented. Understanding the behaviour of a MOS transistor is important for high frequency circuit design. Integrated passive components are even more crucial to the performance of the building blocks and are described in depth. Design and measurement results of single building blocks, such as low noise amplifiers (LNA), mixers, dividers and voltage-controlled oscillators (VCO), demonstrate the functionality.

The fabricated testchip advances the state-of-the-art of receiver design. It has an area of only  $1.2 mm^2$ , and a power consumption of  $188.4 \,\mathrm{mW}$  from a  $1.5 \,\mathrm{V}$  supply. The receiver includes a low-noise amplifier, a first down-conversion mixer, an IF-amplifier, I/Q-mixers, a fully integrated VCO, a 4:1 I/Q-divider and baseband amplifiers to drive the  $50 \,\Omega$  I/Q-outputs.

The main improvements over the state-of-the-art are a very high-level of integration, operation at a radio frequency of 17 GHz, and outstanding low power consumption.

# Chapter 1

# Introduction

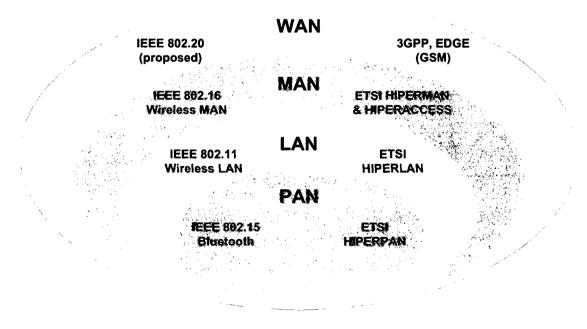

Drawing on the expertise of hundreds of engineers from the communications industry, a hierarchy of complementary wireless standards has been established. Figure 1.1 shows the hierarchy, starting with the Personal Area Network (PAN), the next standard is the Local Area Network (LAN), followed by the Metropolitan Area Network (MAN) and the proposed standards for the Wide Area Network (WAN). Each standard represents the optimized technology for a distinct market and usage model and is designed to complement the others.

#### **Global Wireless Standards**

Figure 1.1: Global wireless standards to ensure interoperability.

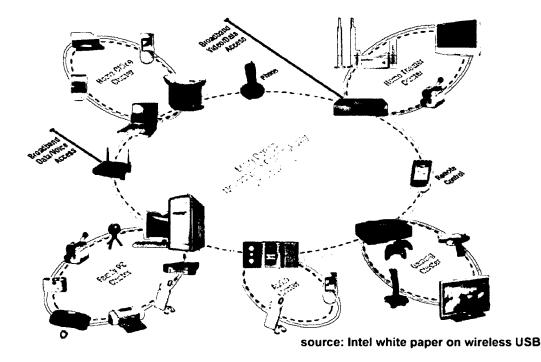

The trend towards smaller equipments, portability and mobility in consumer electronics devices has led to the emergence of new classes of products. These products have rich functionality, multimedia capabilities, and require connection to other devices. Within the home, for instance, a family may have a digital video camcorder, digital camera, portable MP3 player, personal digital assistant (PDA), wireless speakers and tablet personal computer (PC). Each of these portable devices needs to be connected to other devices such as PCs or stationary consumer electronics products, i.e. stereos, televisions, video records, or the like. Figure 1.2 shows such a scenario with clusters for short range connection but also a long range backbone network.

Figure 1.2: Home usage scenarios that could be wired or wireless.

Wireless Local Area Networks (WLAN) systems are increasingly used in offices, hotels and public places to provide high-speed wireless access for portable computers and other mobile devices. Wireless LANs are relatively cheap, easy to install and require no license for network operation. Current systems mostly use the 2.4 or 5 GHz frequency bands, where propagation conditions yield large cells and hence allow considerable area coverage with only a few Access Points (APs). If wireless traffic grows and network becomes congested, either the cell size must be reduced or an overlay network at another frequency band has to be deployed so that the increased capacity demand can be met.

In this work the second alternative is considered and a fully integrated 17 GHz CMOS receiver has been implemented and the performance was tested. The band between 17.1 and 17.3 GHz is suggested in [CEPT/ERC Rec 04] for the operation

of unlicensed Wireless LANs. In addition to provide larger bandwidth, operation at the 17 GHz band is also intended to be used as backbone for 2.4 or 5 GHz access points over a distance up to 100 m. Furthermore the 17 GHz link can be used as a short range high data rate wireless link. This is exactly the same application as the recently emerged wireless standard Ultra Wide-Band (UWB) [Intel 04]. Both applications are compared in Table 1.1.

|                 | UWB                             | 17 GHz WLAN                        |

|-----------------|---------------------------------|------------------------------------|

| Frequency       | 3-5 GHz                         | 17.1-17.3 GHz                      |

| Data Rate       | up to 480 MBit/s up to 155 MBit |                                    |

| Application     | wireless USB                    | standard WLAN &                    |

|                 | (short range, high speed)       | high speed - short range           |

| Standardization | open                            | open, but similar                  |

|                 |                                 | to WLAN at 2.4 and $5\mathrm{GHz}$ |

| Chip Size       | small $(5  \text{GHz})$         | very small (17 GHz)                |

Table 1.1: 17 GHz WLAN versus UWB.

### 1.1 Current State-of-the-Art

The Integrated Circuit (IC) technology for most of the transceivers is CMOS. The fundamentals of Radio Frequency (RF) CMOS are still a topic of research with a substantial work on the building blocks and modeling as well as technology characterization [Kienmayer 04,c]. Radio frequency receiver integrated circuits require a combination of expertise in the areas of circuit design and system architecture along with the choice of a suitable process technology for the various applications. Table 1.2 presents some recently published transceiver work.

|                 | Technology                        | Technology Level of   |                  |  |

|-----------------|-----------------------------------|-----------------------|------------------|--|

|                 |                                   | Integration           | consumption      |  |

| Chapter 6       | $0.13\mu{ m m~CMOS}$              | 17 GHz RX             | 188.4 mW         |  |

| [Ahola +04]     | $0.18\mu{ m m}{ m CMOS}$          | 2.4/5 GHz RX/TX       | $436\mathrm{mW}$ |  |

| [Yue 04]        | $0.18\mu\mathrm{m}$ SiGe-BiCMOS   | 17 GHz Down-converter | 63 mW            |  |

| [Bevilacqua 04] | $0.18\mu{ m m}$ CMOS              | 3.1 - 10.6 GHz LNA    | 9 mW             |  |

| [Guan 04]       | $0.18\mu{ m m~CMOS}$              | 24 GHz front-end      | $30\mathrm{mW}$  |  |

| [Girlando 04]   | $0.8\mu{ m m}$ SiGe               | 12 GHz RX             | $540\mathrm{mW}$ |  |

| [Hashemi 04]    | $0.18\mu\mathrm{m}~\mathrm{SiGe}$ | 24 GHz RX             | 910 mW           |  |

Table 1.2: Published state-of-the-art work.

As can be seen from the Table 1.2, the RX power consumption of the current receiver is comparable to the 5 GHz receiver from [Ahola +04]. Further, other

ICs for such high frequency applications make use of Silicon-Germanium (SiGe) technologies or use Silicon-on-Insulator (SOI) CMOS processes.

## Chapter 2

## Wireless LAN Systems

Wireless networks have enjoyed an increased demand from the general public as well as from business and other professional users. Section 2.1 introduces different wireless applications, especially WLAN. An overview of possible receiver architectures is presented in section 2.2 while propagation effects are discussed in Section 2.3.

### 2.1 Introduction

The IEEE 802.11 Wireless LAN specification was published to extend the functionality provided by the IEEE 802.3 Wired LAN standard. A radio interface for wireless communications adds considerable complexity. However, advances in highly integrated radio circuitry have made it possible to bring the cost of wireless devices down to affordable levels.

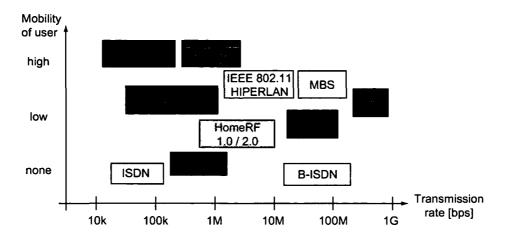

An alternative specification for WLAN is from the European Telecommunications Standards Institute (ETSI) suggested Broadband Radio Access Network (BRAN) HiperLAN/2, with more extensive services, but diminishing commercial support (Table 2.1). The operation of the radio frequency part is in a similar way to 802.11a standard. Numerous techniques have already used for wired LAN to deal with multiple users who have access to the central server, additional steps must be taken in order to deal with the sudden breaddown of WLAN links. A WLAN link has many less-than-ideal transmission characteristics, such as the dependency of signal errors on physical position and the possibility of nearby RF devices to "eavesdrop" or interfere. As the name implies, WLAN was designed to extend the data transfer function of a wired LAN. Table 2.1 shows an overview of current BRAN wireless system types and definitions. Mobility, data rates and power consumption will be the main requirements to WLAN systems. Figure 2.1 shows a comparison of technologies, mobility and data rates.

| BRAN System                       | Use                                 | Expected<br>majority use            | Frequency Band                        | Mobility | Range             | Rate<br>Mbit/s |

|-----------------------------------|-------------------------------------|-------------------------------------|---------------------------------------|----------|-------------------|----------------|

| HIPERLAN 1                        | wireless LAN                        | indoor                              | 5.15 to 5.25 GHz<br>[5.25 to 5.3] GHz | ambulant | 50 m              | 20             |

| HIPERLAN 2                        | wireless access,<br>ATM or IP       | indoor                              | around 5 GHz                          | ambulant | 50 m              | 25             |

| HIPERLINK                         | wireless<br>infrastructure          | indoor private<br>networks, outdoor | 17.1 GHz to<br>17.3 GHz               | fixed    | 150 m             | 155            |

| HIPERACCESS/E<br>HA/E<br>(Exempt) | wireless access,<br>ATM or IP       | outdoor,<br>private networks        | around 5 GHz                          | fixed    | 0.5 km to<br>5 km | 25             |

| HIPERACCESS/U<br>HA/U<br>(Urban)  | urban fixed<br>access, ATM or<br>IP | outdoor,<br>public operator         | >10 GHz                               | fixed    | 0.5 km to<br>5 km | 25             |

| HIPERACCESS/R<br>HA/R<br>(Rural)  | rural fixed<br>access, ATM or<br>IP | outdoor,<br>public operator         | <10 GHz                               | fixed    | 0.5 km to<br>5 km | 25             |

Table 2.1: Summary of current BRAN system types and definitions.

Figure 2.1: Technology, mobility and data rates of communication systems.

One can observe several applications in parallel:

- Bluetooth: A standard technology for low-cost, low power short range wireless communications. First specified in 1999 (Version 1.0) several promoter companies build up the Bluetooth Special Interest Group (SIG) [SIG 01]. The actual Bluetooth specification Version 1.1 uses the frequency range location of f = (2402 + k) MHz,  $k = 0, \ldots, 78$  for the majority of the countries around the world. Bluetooth uses frequency hopping spread spectrum (FHSS) technique with 1 MHz of frequency spacing. Furthermore, it features a maximum data throughput up to 1 Mbit/s.

- Wireless LAN: There exist several Wireless LAN standards, all starting with IEEE 802.11x. In the 2.4 GHz band, the most popular WLAN standard is IEEE 802.11b. It features a maximum throughput of 11 Mbit/s and uses a Direct Sequence Spread Spectrum (DSSS) modulation. Like coaxial cable based Ethernet IEEE 802.3 (10Base-2), it uses Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA). 802.11b operates between 2.4 and 2.483 GHz with 3 channels of each 11 Mbit/s allowing a maximum of 192 users.

- UWB: Wireless USB has a targeted bandwidth of 480 Mbps at launch, which is comparable to the current wired USB 2.0 standard, and will feature wireless high-data throughput with low power consumption for distances less than 10 meters. The Wireless USB interface will deliver the benefits of high-speed wireless connectivity, security, ease-of-use and backward compatibility to customers.

- WiMAX: WiMAX, or 802.16, is a fast-emerging wide-area broadband technology that shows great promise as the "last mile" solution for bringing high-speed Internet access into homes and businesses. It can provide data

rates up to  $75 \,\mathrm{Mbps}$  per base station with typically cell sizes of 2 to 10 kilometers.

- Cordless Phones: In U.S. DECT-like cordless phone standards are found in the 2.4 GHz frequency band with similar requirements as in the European counterpart.

- GSM/UMTS

- Wireless Audio/Video Connection Systems

- Movement Detection Systems

### 2.2 Receiver Architectures

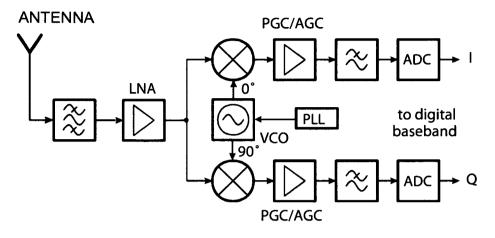

A wireless receiver is typically composed of two sections: an analog front end and a baseband digital processor. The analog section receives the modulated RF signal and the down-converted signal can be either demodulated in the analog domain or converted to a digital signal by means of an analog-to-digital converter (ADC) and then demodulated. In order to improve the sensitivity of the receiver, the RF signal is amplified before down-conversion. For the suppression of interferers, the baseband signal is applied to a channel-select filter before detection.

In this section, three different receiver architectures are compared. When designing RF receivers, the choice of architecture is primarily determined by criterias including complexity, aspects of the design, power dissipation, noise and the number of external components.

#### 2.2.1 Homodyne or Zero-IF Receiver

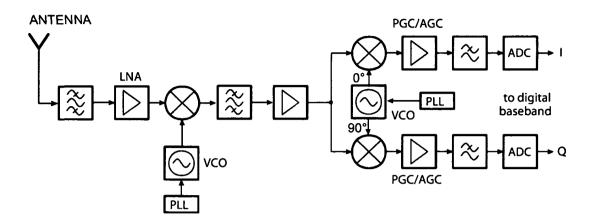

In a homodyne or direct conversion receiver, the incoming RF signal is directly down-converted to zero-IF in one step by mixing with an local oscillator (LO) output (see Figure 2.2 and 2.3). Therefore, in this type of the receiver, the LO frequency is equal to the RF. The baseband signal is then filtered with a low-pass filter to select the desired channel. This is illustrated in the block diagram in Figure 2.2.

For frequency- and phase-modulated signals, the down-conversion must provide quadrature outputs in order to avoid loss of information. The main advantage of a homodyne receiver is that it does not possess the image problem as the incoming RF signal is down-converted directly to baseband without any IF stage. Another advantage is its simplicity. The major disadvantage is that severe DC offsets can be generated at the output of the mixer when the leakage from the local oscillator is mixed with the local oscillator signal itself. This effect could saturate the following stages. Equally critical is the flicker noise of the mixer since the mixer output is a baseband signal and can be easily corrupted by large noise.

Figure 2.2: Block diagram of a homodyne I/Q receiver.

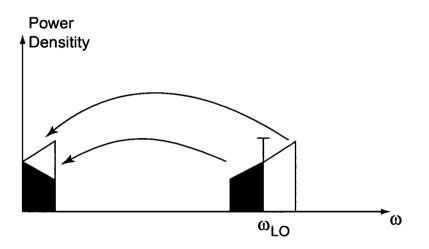

Figure 2.3: Frequency translation in a zero-IF receiver.

#### 2.2.2 Heterodyne or IF Receivers

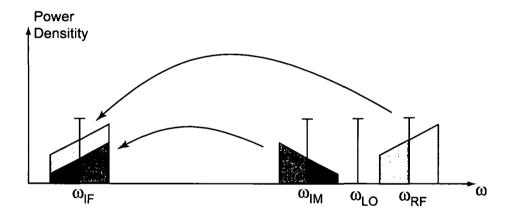

The most straightforward architecture for implementing a cellular receiver frontend is evidently the heterodyne receiver (see Figure 2.4 and 2.5). Its main feature is the use of an intermediate frequency (IF). For this reason the heterodyne receiver is often also called the IF receiver.

The RF signal from the antenna is first filtered by a band select filter that removes out-of-band signals. These signals could saturate the following stages. An LNA amplifies the signal, which is then filtered by an image-reject filter to remove the image. The image has an offset of twice the intermediate frequency (IF) from the desired channel signal, before being down-converted to the intermediate frequency by the mixer. A channel-select filter performs the channel selection of the IF and demodulation or detection is carried out to retrieve the desired information.

Figure 2.4: Block diagram of a heterodyne receiver.

Figure 2.5: Frequency translation in an IF receiver.

The image has to be suppressed before it is mixed down to the IF. This is done by the means of a high frequency (HF) filter. Such a HF filter can only be realized when the IF is high enough because the wanted signal must be relatively far away from the mirror frequency. However, the HF filter and the channel selection filter requires a very high Q-factor, which is defined as the ratio of the center frequency to the 3 dB bandwidth. If the IF is low, the channel selection has a more relaxed requirement, but proper image suppression becomes harder to achieve. HF filters are therefore always realized as discrete off-chip components, but these are very expensive and vulnerable in use. Off-chip components require extra handling, extra board space and an increased pin-count and come along with reduction of board yield.

#### 2.2.3 Sliding IF Receiver

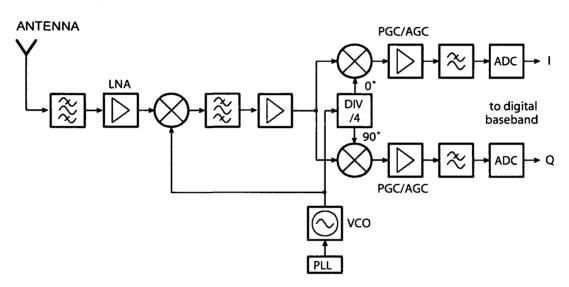

In a heterodyne architecture, the IF is fixed because of the external high quality filters. A sliding IF receiver makes use of only one oscillator for both mixing stages. In this case, the IF is no longer fixed and the signal is *sliding*. In Figure 2.6 a block diagram of such a sliding IF architecture is shown which is reported by [Tadjpour 01].

Figure 2.6: Block diagram of a sliding IF receiver.

Figure 2.7: Frequency translation in a sliding IF receiver.

The diagram shows a special case using a 4:1 divider, but in general any ratio for the second mixing stage can be chosen. As shown, innovation of only one VCO increases the integrity. Furthermore, the usage of two mixers suppresses the effects of flicker noise because the first and second down-converting mixers can be optimized for high gain and low flicker noise respectively.

### 2.3 Propagation Effects

Signal propagation is an external phenomenon that does not occur in the receiver but its effects have significant impact on the receiver signal integrity. In addition, better understanding of the overall system from the transmitter, through the propagation medium and to the receiver can provide the designer with very useful insight [Vaughan 03].

#### 2.3.1 Path Loss

In general, the path loss, as a deterministic parameter, is defined in the following way. Let  $P_T$  be the power delivered by the transmitter with antenna gain  $G_T$ while  $P_R$  is the received power with  $G_R$ , gain of the receiving antenna. The relation between the received power  $P_R$  and the transmitted power  $P_T$  is given the Friis transmission equation

$$\frac{P_R}{P_T} = G_T G_R \frac{1}{L_P}.$$

(2.1)

The path loss  $L_P$  in free space is given by the expression

$$L_P = \left(\frac{4\pi d}{\lambda}\right)^2 = \left(\frac{4\pi df}{c}\right)^2.$$

(2.2)

where d is the distance between transmitter and receiver, f the frequency,  $\lambda$  the wavelength and c is the speed of light in vacuum  $(3 \cdot 10^8 m/s)$ . The frequency of operation and the distance in a wireless communication link determine the path loss. The relationship 2.1 that describes the propagation of a signal from the transmitter, through the air to a receiver is also well known in its logarithmic form as

$$P_R = P_T + G_T - L_P + G_R [dBm].$$

(2.3)

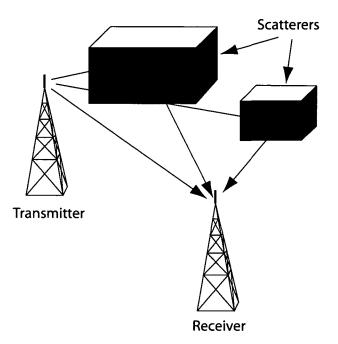

#### 2.3.2 Multipath and Fading

The signal from the transmitter arrives at the receiver not only along the direct path but also via various other paths as a result of reflection and diffraction caused by obstacles in the signal path.

Propagation conditions on these additional paths differ from those on the direct path. For instance, we can expect signals traveling via additional paths to exhibit:

- longer travel times because of increased path length

- various strengths

- different Doppler shifts

Because of the different travel times, the signals arrive with a different phase at the receiving antenna. Depending on this phase, components may be canceled or added to a high-quality signal which is received in a relatively short span of time. Figure 2.8 shows such a scenario, where multiple reflections of the same signal arrive at the receiving antenna with different phase and amplitude.

Figure 2.8: Outdoor scenario for a multipath link.

#### 2.3.3 Equalization

Equalization is used to reduce intersymbol interference (ISI) caused by multipath propagation within the channels. This form of interference occurs when the radio channel bandwidth truncates the signal modulation bandwidth, resulting in time spreading of modulation pulses.

To reduce ISI in a mobile environment, adaptive equalization is used to track the time-varying characteristics of the channel. Typically, a known training sequence is transmitted to characterize the channel. The received information is then manipulated to calculate and set the proper filter coefficients for equalization in the receiver back-end. The data is transmitted following the training sequence while the received data is corrected by the equalizer. In an adaptive equalizer, the filter coefficients of the equalizer are constantly optimized to compensate the changing radio channel.

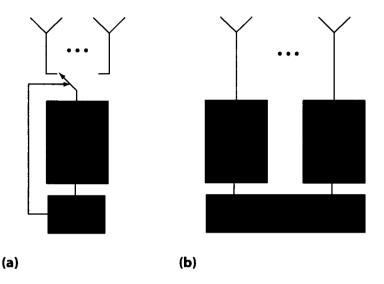

#### 2.3.4 Diversity

An alternative way to reduce severity of fading is diversity. There are several diversity techniques available such as polarization, time and frequency diversity, but the most common diversity technique is spatial diversity. In this technique, multiple receiver antennas are strategically placed at different locations which allows the antennas to receive different versions of the transmitted signal, thus providing the receiver with a choice of which version to use.

Figure 2.9: Block diagram of a receiver using antenna diversity (a), and a complete receive-chain diversity (b).

As shown in Figure 2.9, there are two different methods to implement a spatial diversity receiver. In one method, the receiver can switch between multiple antennas. This requires the receiver to first test each connected antenna and then make a decision. This is method is called antenna diversity. In the second method, multiple independent receiver paths with their own antennas are used. In this case, the receiver back-end has both signals available simultaneously and is able to choose the better one.

#### 2.3.5 Coding

Another method to improve the performance of the communication link is channel coding. In this technique, redundant data bits are added to the original message prior to modulation and transmission of the signal. These added bits follow specific code sequences that help the receiver to detect and correct some or all of the error created by the radio channel. The addition of coding bits however reduces the overall channel capacity but is very effective in reducing errors.

## Chapter 3

# **CMOS** Technology

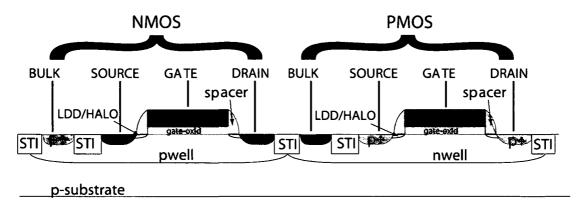

The C11N fabrication process is a CMOS  $0.13 \,\mu\text{m}$  generation foundry technology, designed for SRAM, logic, mixed signal and mixed-voltage I/O applications. It provides a platform technology for embedded DRAM. This chapter gives a short overview of the implemented CMOS technology.

Section 3.1 shows the behaviour of the nMOS transistor. Section 3.2 discusses the passive devices used for the circuit design. Section 3.3 presents an overview of the C11N CMOS technology, in particular.

### 3.1 The nMOS Transistor

A typical cross-section of commonly used sub- $\mu$ m CMOS technology transistor is presented in Figure 3.1. On the left side, an NMOS-transistor is depicted and

Figure 3.1: Typical sub- $\mu$ m CMOS technology transistor cross-section.

on the right side a PMOS-transistor, respectively. For both transistors, all four terminals including their backgates (bulks) are shown. Fabricated on a *p*-type substrate (also called the "bulk" or the "body"), the NMOS-device consists of

two heavily-doped n regions forming the source and drain terminals. A heavilydoped (conductive) piece of polysilicon (often simply called "poly") is operating as the gate while a thin layer of silicon dioxide  $(SiO_2)$  insulates the gate from the substrate. The desired action of the device occurs in the substrate region under the gate oxide. Note that the structure is symmetric with respect to source and drain. The PMOS-device consists of heavily-doped p regions instead of n regions. Current technologies use shallow trench isolations (STI) to isolate transistors enabling a higher transistor density. A lightly doped drain (LDD) extension is inserted to avoid hot electron effects which cause reliability and lifetime degeneration. Further, short channel device optimization is obtained through the HALOextension.

A typical  $0.13 \,\mu\text{m}$  standard CMOS transistor layout for high frequency operations is shown in Figure 3.2. Instead of one single transistor with a width W of  $21 \,\mu\text{m}$ , the transistor consists of 6 parallel connected  $3.5 \,\mu\text{m}$  wide transistor gates. This folded structure exhibits substantially less drain junction capacitance while providing the same width-length ratio (W/L) [Razavi 99].

Figure 3.2: Layout of a folded MOS transistor (a) planar cut (b) 3D view.

Furthermore, the effective gate series resistance is reduced by the folding factor n squared:

$$R_{Gate} = \frac{R_g/sq}{3} \cdot \frac{W}{n^2 L},\tag{3.1}$$

where  $R_g/sq$  denotes the sheet resistance of the gate material (typically 7  $\Omega/sq$ ), W is the total width and L the total length of the transistor. For RF analog

circuits, however, the capacitances associated with the devices must also be taken into account. These relevant capacitances are shown in a three dimensional figure (Figure 3.3) of an NMOS device embedded in a p-substrate.

Figure 3.3: n-channel MOSFET with parasitic capacitances.

The conductive channel is drawn at the boundary between linear and saturation region. Each parasitic capacitance may depend on the bias conditions of the transistor. From the Figure, the following capacitances can be identified:

- **Oxide Capacitance:** The contribution of gate-to-channel capacitance  $C_{GC}$  to the terminal capacitances depends on the operation region of the device. Total value  $C_{oxt}$  equals  $C_{ox}WL_{eff}$ .

- **Depletion Capacitance:** The *channel-bulk* junction capacitance  $C_{CB}$  is the controlling capacitance of the device. The *source-bulk* and *drain-bulk* junction capacitances  $C_{SB}$  and  $C_{DB}$  consist of a bottom-plate capacitance associated with the bottom of the junction, and a side wall capacitance due to the perimeter of the junction.

- **Overlap Capacitance:** The overlap capacitance  $C_{OV}$  is a result of the gate overlapping with source and drain area by an amount of  $L L_{eff}$ .

#### nMOS in Linear Region

The linear region of operation is defined as one in which  $V_{gs}$  is large enough to guarantee an inversion layer from source to drain. The boundary between linear and saturation region is defined by

$$V_{ds} = V_{gs} - V_T = V_{dsat}.$$

(3.2)

As long as  $V_{ds}$  is smaller than  $V_{dsat}$ , the device will be in the linear region of operation. The drain current is proportional to charge times velocity. The derived expression for the drain current in linear region is

$$I_d = \mu_n C_{ox} \frac{W}{L} \left[ (V_{gs} - V_T) V_{ds} - \frac{V_{ds}^2}{2} \right].$$

(3.3)

where W is the width of the device, L is the length of the gate and  $\mu_n$  represents the mobility of electrons in the channel.  $C_{ox}$  is the total gate oxide capacitance per unit area

$$C_{ox} = \varepsilon_{ox} / t_{ox} \tag{3.4}$$

where  $\varepsilon_{ox}$  is the dielectric constant and  $t_{ox}$  the thickness of the oxide. The relationship between drain current and drain-to-source voltage is nearly linear for small voltages  $V_{ds}$ . An nMOS in the linear region behave like a voltage controlled resistor.

The transconductance of such a device in linear region is easily found by differentiating the expression of Eqn. 3.3 for drain current:

$$g_m = \mu_n C_{ox} \frac{W}{L} V_{ds}. \tag{3.5}$$

#### nMOS in Saturation Region

When  $V_{ds}$  is high enough so that the inversion layer does not extend all over from the drain to source, the device is in saturation. In this case, the channel charge stays constant. The drain current is also constant while  $V_{ds}$  is rising.

The drain current in saturation region can be derived from Eqn. 3.3 by substituting  $V_{ds}$  by  $V_{dsat}$ .

$$I_{d} = \mu_{n} C_{ox} \frac{W}{L} \left[ (V_{gs} - V_{T}) V_{dsat} - \frac{V_{dsat}^{2}}{2} \right].$$

(3.6)

Using Eqn. 3.2, this expression simplifies to

$$I_d = \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_T)^2.$$

(3.7)

In saturation, the drain current has a square-law dependence on the gate-source voltage and is independent of the drain-voltage. Again, the transconductance of the device in saturation is easily found by differentiating the expression Eqn. 3.7 for drain current

$$g_m = \mu_n C_{ox} \frac{W}{L} (V_{ds} - V_T).$$

(3.8)

which can also be written as

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_d}.$$

(3.9)

In order to represent the behavior of transistors in circuit simulations, an accurate model of the NMOS-device is required. For RF-simulations the subcircuit model of Figure 3.4 is preferred which goes in hand with the industry-standard *Berkeley BSIM model* [UC Berkeley 04].

Figure 3.4: Small signal model including the noise sources.

The series resistances of gate, source and drain can not be neglected at high frequencies due to the low-pass poles and the contributed white noise  $(\overline{i_{rg}^2}, \overline{i_{rd}^2}, \overline{i_{rd}^2})$ . The channel charging resistance  $r_i$  models the phenomenon that the channel can not instantaneously respond to changes of the gate-source voltage [Manku 99]. The channel charging resistance is given by

$$r_i = \frac{1}{5g_m},\tag{3.10}$$

which has been theoretically proven. In Equation 3.10  $g_m$  represents the transconductance of the transistor. The drain channel noise consists of flicker noise and thermal noise generated by carriers in the channel. The drain channel noise is typically given as

$$\overline{i_d^2} = 4kT\gamma g_m \Delta f. \tag{3.11}$$

Here,  $\gamma$  is a bias-dependent parameter, where  $\gamma = 2/3$  for long channel devices, k is the Boltzmann's constant, T is the temperature of the carriers in the channel, and  $\Delta f$  is the noise bandwidth. In deep sub-micron processes  $\gamma$  might rather equal to 1 for relevant analog RF operating points [Brederlow 02]. Further, the induced gate noise is generated in the channel standard flicker noise and coupled through the gate as a gate current. At low frequencies this gate induced noise

current can be neglected. Nevertheless, at high frequencies it must be taken into account and is expressed as

$$\overline{i_{ig}^2} = 4kT\delta g_g \triangle f \tag{3.12}$$

with  $\delta = 2\gamma$  and

$$g_g = \frac{(\omega C_{gs})^2}{5g_m}.$$

(3.13)

Since the drain channel noise and induced gate noise arise from the same source, they are correlated with a factor c [Manku 99].

Additionally, in the case of high-frequency performance two figures of merit are popular. These are  $f_t$  and  $f_{max}$ . The transit frequency is defined as the frequency where

$$\left|\frac{i_d}{i_g}\right| \equiv 1,\tag{3.14}$$

where  $i_d$  is the drain current and  $i_g$  is the gate current. Perhaps more relevant than  $f_t$  is the frequency at which the maximum available power gain is extrapolated to fall to unity. However, computing  $f_{max}$  is in general quite difficult and we will take an expression from [Lee 98] for the maximum oscillation frequency

$$f_{max} \approx \sqrt{\frac{f_t}{8\pi r_g C_{gd}}},\tag{3.15}$$

where  $r_g$  is the series gate resistance and  $C_{gd}$  is gate-drain capacitance. The manufactured nMOS transistors in 0.13  $\mu$ m CMOS have a cutoff frequency  $f_t$  of 100 GHz and a maximum oscillation frequency  $f_{max}$  of 50 GHz respectively [Schiml 01]. The devices have typically a qualified maximum supply voltage of 1.5 V.

### **3.2** Passive Devices

Passive devices are of main interest in analog RF-circuit design. These include inductors, capacitors, resistors and varactors. This subchapter gives an overview of the main properties of these devices.

#### 3.2.1 Inductors

Inductors are widely used in RF circuits, e.g. as inductive load or matching element in LNA or as part of the frequency determining LC-tank in voltagecontrolled oscillators. Integrated inductors can be realized as planar structures using metal layers. Modern CMOS processes offer 4 to 9 metal layers which are intended for circuit wiring and used for inductor design. Various layout structures for integrated inductors have been discussed and presented in literature [Ashby 96][Yue 98][Niknejad 00]. For conducting metal layers copper (conductivity  $\sigma = 57.14 \text{ S/m}$ ) or aluminum ( $\sigma = 37.7 \text{ S/m}$ ) are used. The metal layers reside on top of the substrate and are usually embedded in silicon dioxide  $SiO_2$  (relative permittivity  $\varepsilon_r \approx 4$ ). The substrate has a typical conductivity of  $\sigma = 20 \text{ S/m}$  and

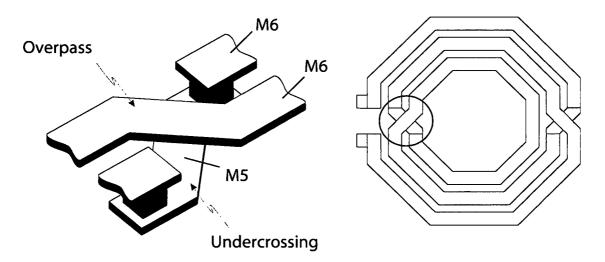

Figure 3.5: Cross-coupled symmetrical inductor for a resonant frequency of 3.4 GHz.

a relative permittivity of  $\varepsilon_r \approx 12$ . Usually two metal layers are shunt connected using VIA bars as intermetallic stripes along the winding. Thereby, the series resistance of the windings is reduced up to 60%.

Figure 3.5 shows an example of a cross-coupled symmetrical integrated inductor. Desiring highly integrated receivers, the symmetrical inductor layout is generally preferred for its inherently better insensitivity to substrate noise.

Main disadvantage is the more complicated layout and modeling. A center tap to the inductor is easily realized as common-mode access point or as direct current (DC) biasing connection. At least two metal layers are needed for the turns else it would be impossible to connect the turns to each other. Figure 3.6 shows how the crossing of the individual turns is realized by the metal layers.

For electrical characterization, several models exist, which differ in their complexity. The aim of a lumped, lower order model is to characterize the integrated

Figure 3.6: Symmetrical inductor

inductor with a minimum number of discrete components. A detailed derivation of the lumped low order model for inductors can be found in [Thüringer 02]. Here, only a brief insight into the modeling process is given. Figure 3.7 shows the cross-section of an integrated inductor together with discrete elements to model the various parasitics.

Figure 3.7: Inductor cross-section and parasitic components

What follows is a short explanation of the various components found in the lumped low order model:

- L: The inductance is caused by the magnetic flux density  $\vec{B}$  of the electromagnetic field.

- $R_{Sub}$ : The resistance  $R_{Sub}$  is used to model the ohmic losses in the substrate.

- $R_S$ : The resistance  $R_S$  characterizes the series resistance of the metal traces with finite conductivity as well as the skin-effect and current crowding. For all inductors in this work, the metal series resistance is dominant due to the thin metal layers in standard CMOS. Therefore  $R_S$  equals to the DC series resistance, neglecting skin effects and current crowding.

- $C_L$ : The capacitive coupling between the turns of the inductor is modeled with the lateral coupling capacitance  $C_L$ .

- $C_{OX}$ : Models the capacitance between inductor and substrate.

- $C_{Sub}$ : The capacitance  $C_{Sub}$  is used to characterize the capacitance in the substrate. Due the highly conductive substrates typically used in standard CMOS processes (1 to 6  $\Omega$ cm),  $C_{Sub}$  is neglected.

It is important to note that the whole inductor is modeled with these components, hence a minimum number of discrete elements is used in the modeling process. The resulting electrical circuit is now easily obtained. The use of a  $\pi$ -circuit is appropriate, since the inductor is a two-port device. The series branch of the  $\pi$ circuit corresponds to the winding of the inductor, so the inductance L and series resistance  $R_s$  are placed here as well as the lateral coupling capacitance  $C_L$ . Since we assume static parasitic components, the overall resistances and capacitances to the substrate can be split into two equal parts to complete the equivalent electrical circuit. The values are divided as follows:

$$C_{ox1} = C_{ox2} = \frac{C_{ox}}{2}$$

(3.16)

$$R_{sub1} = R_{sub2} = 2 \cdot R_{sub} \tag{3.17}$$

$$C_{sub1} = C_{sub2} = \frac{C_{sub}}{2} \tag{3.18}$$

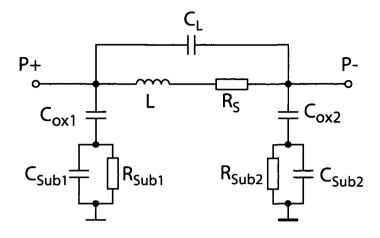

Figure 3.8 shows the resultant electrical circuit. In [Wohlmuth 00], [Kehrer 01], [Thüringer 02] and [M. Engl 03] detailed methods and algorithms for the calculation of these lumped components can be found. For simple spiral coils,  $C_L$  can be neglected as the voltage difference between neighboring windings is small.

For symmetrical inductors (Figure 3.6) the single- $\pi$  lumped model must be extended to the double  $\pi$  model as presented in Figure 3.9. The double  $\pi$ -model allows an accurate modeling of the coil, in balanced as well as in single-ended operation mode. E.g. in balanced mode the capacitor at the middle node completely disappears, causing a totally different self-resonance frequency. The meaning of the model parameters is the same as for the single- $\pi$  model, only a form factor f is introduced to distribute the overall parasitics to each branch. This form factor depends on the winding staggering. For coils without winding staggering f = 0.25. In contrast to simple spiral coils, the lateral winding to winding capacitance  $C_L$  cannot be neglected as the voltage difference between neighboring

Figure 3.8: Low order equivalent circuit

Figure 3.9: Differential inductor lumped model.

windings is maximal due to the differential winding scheme.

Alternatively, commercial 3D electromagnetic simulators like HFSS [HFSS 04] or Agilent MOMENTUM [Momentum 04] can be used to estimate the behaviour of the inductors. These simulators require long simulation times hence run-times are too long to optimize the coils. For a fast and acceptable model estimation, the public domain M.I.T. simulators FASTHENRY [M.I.T. 04,b] and FASTCAP [M.I.T. 04,a] can be combined to provide the magnetical and electrical parts of the lumped model which is described in more detail in [Kehrer 01]. The shorter calculation time of this approach allows a qualitative optimization of integrated inductors.

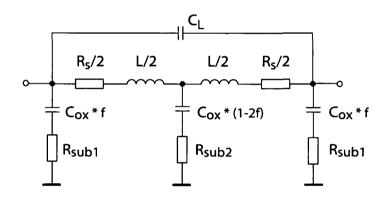

#### **3.2.2** Capacitors

Considering highly integrated transceivers in CMOS, linear capacitors are mainly needed for filtering, for AC-coupling and for inductor-capacitors tanks. Addition-

ally, a capacitor in combination with a MOS-switch can be used to switch the center frequencies of VCOs [Kral 98] or LNAs [Darabi 00]. Linear RF-capacitors can be modeled by the lumped  $\pi$ -model presented in Figure 3.10.

Figure 3.10: RF-capacitor lumped model.

There are two main design parameters for RF-capacitor design, the quality factor Q and ratio  $C/C_p$ , respectively. The quality factor, which is given as

$$Q_c = \frac{1}{j\omega R_s C},\tag{3.19}$$

is dominated by the series resistance. The ratio of wanted to parasitic capacitance  $C/C_p$ . This ratio is best for Metal-Insulator-Metal (MIM) capacitors situated on the top metal layers. Poly-Interpoly-Poly (PIP) or standard metal layer based capacitors feature worse values for  $C/C_p$  of about 10% to 20%.

#### 3.2.3 Varactors

MOS varactors are variable, voltage-controlled capacitors based on the MOS structure. The use of a MOS-device as varactor has been published before [Panasonic 82] and is well known [Porret 00]. Their main application is LC-voltage controlled oscillators (VCOs).

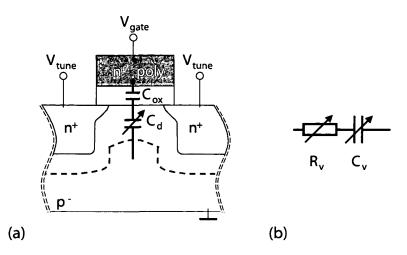

Figure 3.11 shows a cross section of an NMOS varactor and a general small-signal model for varactors: a variable capacitance in series with a variable resistance. For the NMOS device, source and drain are  $n^+$ -doped. The substrate (or well) region between and around source and drain is of opposite doping, i.e.  $p^-$ -type while the polysilicon gate is of the same doping as source and drain, i.e.  $n^+$ -type. A PMOS device is obtained when all regions have opposite doping as in the NMOS.

Unlike a MOS transistor, a MOS varactor is a three-terminal device. The source and drain regions are shorted to apply the voltage  $V_{tune}$  that tunes the variable capacitance. The  $p^-$  body is grounded and the voltage  $V_{gate}$  is applied to the gate node.

The variable capacitance  $C_v$  appears between the gate node and all other nodes

Figure 3.11: Cross-section of a conventional NMOS varactor in depletion (a) and the generally assumed model (b). The dashed line indicates the border of the depletion region.

at AC ground. Essentially it is the series connection of the gate oxide capacitance  $C_{ox}$  and the variable depletion region capacitance  $C_d$

$$\frac{1}{C_v} = \frac{1}{C_{ox}} + \frac{1}{C_d}.$$

(3.20)

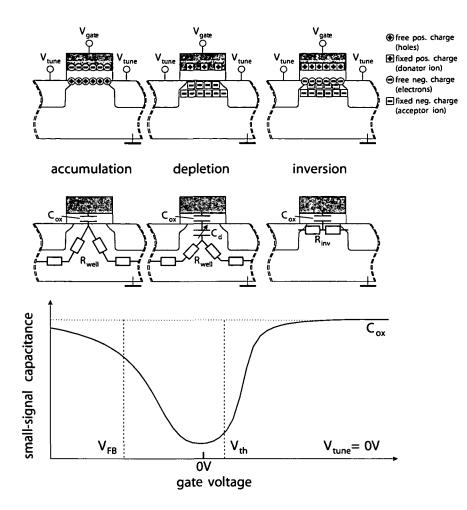

Figure 3.12 depicts the small-signal capacitance of an NMOS varactor at zero tuning voltage. The corresponding charges and the relevant lumped elements in the device are also included.

Negative gate voltages result in surplus of holes at the surface of the semiconductor: the device is in accumulation. Charge variations at the gate are balanced by changes in the accumulation layer charge. A large capacitance determined by the gate oxide is effective.

With increasing gate voltage, flat-band situation is reached. The semiconductor beneath the gate is neutral and fixed oxide while the interface charges balance the gate charge. The flat-band voltage  $V_{FB}$  is usually negative but the oxide charges are comprised of positively charged alkali-ions inevitably introduced during processing. Further, for a particular value of  $V_{FB}$ , different work functions of the gate and well have to be considered. Flat band voltage is close to 0 V, when same type of doping is present in gate and well. Different doping shifts the  $V_{FB}$  by approximately 1 V.

Just above the flat-band voltage holes are repelled from the surface and the negatively charged ions of fixed dopant atoms (acceptors) form the depletion region. Charges at the gate are balanced by widening (more negative dopants) or narrowing (less negative dopants) the depletion region. The capacitance in this case is a series connection of the gate oxide capacitance  $C_{ox}$  and the variable depletion region capacitance  $C_d$ .

Figure 3.12: Typical measured small-signal capacitance characteristic of a NMOS varactor (bottom), the corresponding charges (top) and the relevant lumped elements (middle) at zero tuning voltage. Oxide, interface charges and charges at pn junctions are not shown.

Gate voltages above a certain threshold voltage  $V_{th}$  result in a surplus of electrons at the semiconductor surface, i.e. the device is in inversion. In this situation the depth of the depletion region remains constant and changes in the gate charge are balanced by changes in the electron inversion layer. Again the effective capacitance is determined by the gate oxide capacitance. The necessary electrons can be provided by thermal generation in the depletion region. However, at voltages leading to inversion, the electric field between the gate and the source/drain lowers the barrier between the source/drain and semiconductor's surface considerably. Therefore, the main source of electrons are the  $n^+$ -doped source and drain regions.

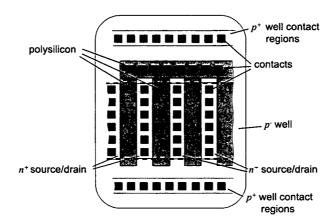

Part of the resistance is always the gate resistance determined by the polysili-

con line. The gate area and thus the gate width have to be large to achieve the necessary capacitance values ( $\approx 500 \, \text{fF}...2 \, \text{pF}$ ) for VCOs in wireless communication systems. With a regular straight transistor design the corresponding gate resistance

$$R_{gate} \propto N_{\Box} R_{\Box} \tag{3.21}$$

is large.  $N_{\Box}$  and  $R_{\Box}$  are the number of squares and the resistance per square of the gate, respectively. To avoid this large undesired resistance, RF transistors as well as varactors are laid out in so called multifinger structures (Figure 3.13).

Figure 3.13: Typical multifinger structure of RF varactors. Dashed line indicates area of thin oxide.

Many short fingers (often less than  $10\mu$ m) connected in parallel resemble a device with large total gate width

$$W_g = L_f N_F \tag{3.22}$$

with  $N_F$  the number of parallel fingers and  $L_f$  the length of each finger. Thereby, the gate resistance is considerably reduced to

$$R_{gate} \propto \frac{F_{\Box} R_{\Box}}{N_F} \tag{3.23}$$

with  $F_{\Box}$  the number of squares per finger. A typical value for  $R_{gate}$  is around  $300 \text{ m}\Omega$  for a  $600 \,\mu\text{m}$  wide device (at  $0.25 \,\mu\text{m}$  gate length). Further reduction of the gate resistance by a factor of  $\frac{1}{4}$  is achieved when contacting the gate fingers at both ends.

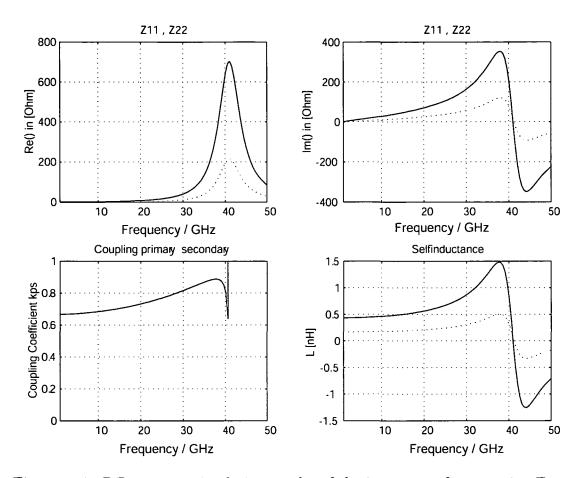

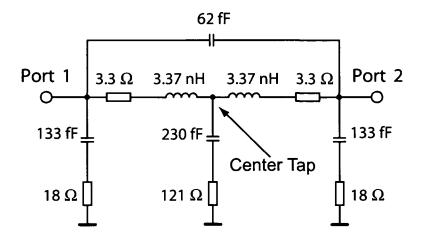

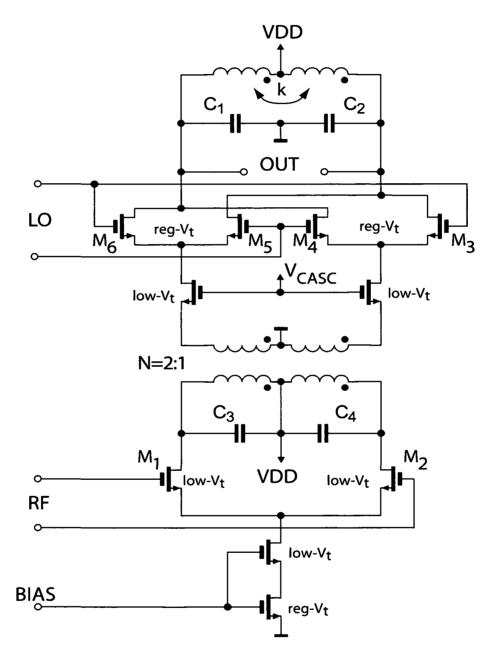

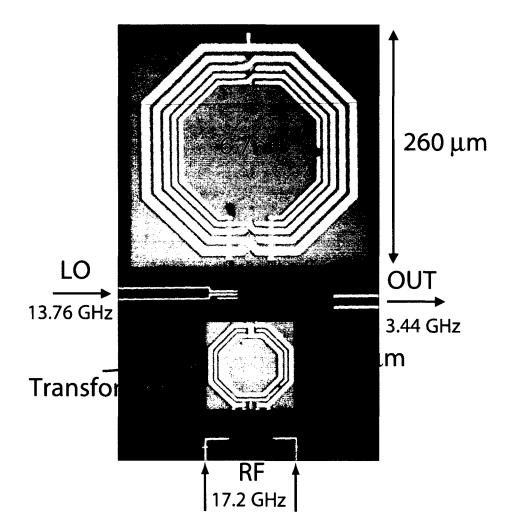

In accumulation, the gate resistance is in series with the resistance extending from the accumulation layer to substrate (well) contacts presents outside the device, see Figure 3.13. This resistance is strongly layout dependent.