The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

### DISSERTATION

# JOP: A Java Optimized Processor for Embedded Real-Time Systems

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger und

Ao.Univ.Prof. Dipl.-Ing. Dr. techn. Peter Puschner Inst.-Nr. E182 Institut für Technische Informatik

> eingereicht an der Technischen Universität Wien Fakultät für Informatik

> > von

DIPL.-ING. MARTIN SCHÖBERL

Matr.-Nr. 8625440

Straußengasse 2-10/2/55

1050 Wien

Men h Slat

Wien, im Jänner 2005

### **Abstract**

Compared to software development for desktop systems, current software design practice for embedded systems is still archaic. C/C++ and even assembler are used on top of a small real-time operating system. Many of the benefits of Java, such as safe object references, the notion of concurrency as a first-class language construct, and its portability, have the potential to make embedded systems much safer and simpler to program. However, Java technology is seldom used in embedded systems, due to the lack of acceptable real-time performance.

This thesis presents a Java processor designed for time-predictable execution of real-time tasks. JOP (Java Optimized Processor) is the implementation of the Java virtual machine in hardware. JOP is intended for applications in embedded real-time systems and the primary implementation technology is in a field programmable gate array. This research demonstrates that a hardware implementation of the Java virtual machine results in a small design for resource-constrained devices.

Architectural advancements in modern processor designs increase average performance with features such as pipelines, caches and branch prediction. However, these features complicate worst-case execution time (WCET) analysis and lead to very conservative WCET estimates. This thesis tackles this problem from the architectural perspective – by introducing a processor architecture in which simpler and more accurate WCET analysis is more important than average case performance.

This thesis evaluates the issues surrounding the use of standard Java for real-time applications. In order to overcome some of the issues with standard Java, a profile for real-time Java is defined. Tight integration of the real-time scheduler with the supporting processor result in an efficient platform for Java in embedded real-time systems.

The proposed processor and the Java real-time profile have been used with success to implement several commercial real-time applications.

### Kurzfassung

Eingebettete Systeme werden zur Zeit vorwiegend in C/C++ oder auch noch in Assembler programmiert. Viele Vorteile der Programmiersprache Java, wie z.B. sichere Objektreferenzen, die Notation von Nebenläufigkeit in der Sprache und auch die Portabilität der Sprache, könnten die Entwicklung dieser Systeme vereinfachen und auch die Sicherheit dieser Systeme erhöhen. Jedoch erschwert die mangelnde Echtzeitfähigkeit von Standard Java den Einsatz in eingebetteten Systemen.

Diese Arbeit beschreibt den Entwurf eines echtzeitfähigen Java Prozessors. JOP (Java Optimized Processor) ist die Realisierung der Java virtual machine in Hardware. JOP ist für den Einsatz in eingebetteten, echtzeitfähigen Systemen entworfen und ist in einem 'Field Programmable Gate Array' implementiert. Diese Arbeit zeigt, dass eine Hardwarerealisierung der Java virtual machine zu einem kleinen System führt, das auch für Applikationen mit rigiden Ressourcebeschränkungen geeignet ist.

Moderne Prozessoren weisen Architekturmerkmale auf (wie z.B. Parallelverarbeitung, Cachespeicher und Sprungvorhersage), die vor allem die durchschnittliche Rechenleistung erhöhen. Diese Architekturmerkmale erschweren jedoch die 'Worst-Case Execution Time' (WCET) Analyse und führen zu pessimistischen WCET Abschätzungen. Diese Arbeit geht einen anderen Weg – Es wird eine Prozessorarchitektur vorgestellt, für die eine einfache und genauere WCET Analyse wichtiger ist als die durchschnittliche Rechenleistung.

Diese Arbeit untersucht die Probleme, die sich bei der Verwendung von Java in Echtzeitsystemen ergeben. Standard Java wird um eine Spezifikation für Echtzeitsysteme erweitert. Die Integration des echtzeitfähigen Schedulers mit dem Prozessor führt zu einer effizienten Plattform für Java in eingebetteten Echtzeitsystemen.

Der vorgestellte Prozessor und die Spezifikation für echtzeitfähiges Java wurden erfolgreich in mehreren kommerziellen Echtzeitsystemen eingesetzt.

# **Contents**

| 1 | Intro | duction  | 1                                 | 1  |

|---|-------|----------|-----------------------------------|----|

|   | 1.1   | Justific | cation for Development            | 1  |

|   | 1.2   | Embed    | dded Real-Time Systems            | 2  |

|   | 1.3   |          | ch Objectives and Contributions   | 3  |

|   | 1.4   | Outlin   | e of the Thesis                   | 6  |

| 2 | Java  | and th   | e Java Virtual Machine            | 7  |

|   | 2.1   | Java .   |                                   | 7  |

|   |       | 2.1.1    | History                           | 9  |

|   |       | 2.1.2    | The Java Programming Language     | 9  |

|   | 2.2   | The Ja   | va Virtual Machine                | 11 |

|   |       | 2.2.1    | Memory Areas                      | 11 |

|   |       | 2.2.2    | JVM Instruction Set               | 12 |

|   |       | 2.2.3    | Methods                           | 13 |

|   |       | 2.2.4    | Implementation of the JVM         | 14 |

|   | 2.3   | Summ     | ary                               | 16 |

| 3 | Rela  | ited Wo  | rk                                | 17 |

|   | 3.1   | Hardw    | vare Translation and Coprocessors | 17 |

|   |       | 3.1.1    | Hard-Int                          | 19 |

|   |       | 3.1.2    | DELFT-JAVA Engine                 | 19 |

|   |       | 3.1.3    | JIFFY                             | 19 |

|   |       | 3.1.4    | Jazelle                           | 20 |

|   |       | 3.1.5    | JSTAR, JA108                      | 21 |

|   |       | 3.1.6    | A Co-Designed Virtual Machine     | 21 |

|   | 3.2   |          | rocessors                         | 22 |

|   | 3.2   | 3.2.1    | picoJava                          | 22 |

|   |       | 3.2.1    | aJile JEMCore                     | 25 |

|   |       | 3.2.2    |                                   | 26 |

|   |       |          | Cjip                              |    |

|   |       | 3.2.4    | Ignite, PSC1000                   | 26 |

CONTENTS \_\_\_\_

|   |     | 3.2.5          | Moon                                          | 27<br>27 |

|---|-----|----------------|-----------------------------------------------|----------|

|   |     | 3.2.6<br>3.2.7 | Lightfoot                                     | 28       |

|   |     | 3.2.7          | LavaCORE                                      | 28<br>28 |

|   |     |                | Komodo                                        | 28<br>28 |

|   | 2.2 | 3.2.9          | FemtoJava                                     | 28<br>29 |

|   | 3.3 |                | onal Comments                                 | 30       |

|   | 3.4 | Resear         | ch Objectives                                 | 30       |

| 4 |     |                | s of Java for Embedded Real-Time Systems      | 33       |

|   | 4.1 |                | upport for Embedded Systems                   | 33       |

|   | 4.2 |                | with Java in Embedded Systems                 | 34       |

|   | 4.3 | Java M         | licro Edition                                 | 37       |

|   |     | 4.3.1          | Connected Limited Device Configuration (CLDC) | 37       |

|   |     | 4.3.2          | Connected Device Configuration (CDC)          | 39       |

|   |     | 4.3.3          | Additional Specifications                     | 40       |

|   |     | 4.3.4          | Discussion                                    | 40       |

|   | 4.4 | Real-T         | ime Extensions                                | 41       |

|   |     | 4.4.1          | Real-Time Core Extension                      | 41       |

|   |     | 4.4.2          | Discussion of the RT Core                     | 42       |

|   |     | 4.4.3          | Real-Time Specification for Java              | 43       |

|   |     | 4.4.4          | Discussion of the RTSJ                        | 45       |

|   |     | 4.4.5          | Subsets of the RTSJ                           | 51       |

|   |     | 4.4.6          | Extensions to the RTSJ                        | 53       |

|   | 4.5 | Summ           | ary                                           | 53       |

| 5 | JOP | Archite        | ecture                                        | 55       |

|   | 5.1 | Benchi         | marking the JVM                               | 55       |

|   |     | 5.1.1          | Bytecode Frequency                            | 55       |

|   |     | 5.1.2          | Methods Types and Length                      | 60       |

|   |     | 5.1.3          | Summary                                       | 64       |

|   | 5.2 | Overvi         | iew of JOP                                    | 64       |

|   | 5.3 | Micro          | code                                          | 66       |

|   |     | 5.3.1          | Translation of Bytecodes to Microcode         | 66       |

|   |     | 5.3.2          | Compact Microcode                             | 68       |

|   |     | 5.3.3          | Instruction Set                               | 69       |

|   |     | 5.3.4          | Bytecode Example                              | 70       |

|   |     | 5.3.5          | Flexible Implementation of Bytecodes          | 70       |

|   |     | 5.3.6          | Summary                                       | 71       |

|   | 5 4 | The Pr         | rocessor Pineline                             | 71       |

CONTENTS

|   |     | 5.4.1  | Java Bytecode Fetch                  |

|---|-----|--------|--------------------------------------|

|   |     | 5.4.2  | JOP Instruction Fetch                |

|   |     | 5.4.3  | Decode and Address Generation        |

|   |     | 5.4.4  | Execute                              |

|   |     | 5.4.5  | Interrupt Logic                      |

|   |     | 5.4.6  | Summary                              |

|   | 5.5 | An Eff | icient Stack Machine                 |

|   |     | 5.5.1  | Java Computing Model                 |

|   |     | 5.5.2  | Access Patterns on the Java Stack    |

|   |     | 5.5.3  | Common Realizations of a Stack Cache |

|   |     | 5.5.4  | A Two-Level Stack Cache              |

|   |     | 5.5.5  | Resource Usage Compared              |

|   |     | 5.5.6  | Summary                              |

|   | 5.6 | HW/S   | W Codesign                           |

|   | 5.7 |        | ime Predictability                   |

|   |     | 5.7.1  | Interrupts                           |

|   |     | 5.7.2  | Task Switch                          |

|   |     | 5.7.3  | Architectural Design Decisions       |

|   |     | 5.7.4  | Summary                              |

|   | 5.8 | A Time | e-Predictable Instruction Cache      |

|   |     | 5.8.1  | Cache Performance                    |

|   |     | 5.8.2  | Proposed Cache Solution              |

|   |     | 5.8.3  | WCET Analysis                        |

|   |     | 5.8.4  | Caches Compared                      |

|   |     | 5.8.5  | Summary                              |

| _ | 100 | D      | ne Svstem 12°                        |

| 6 |     |        |                                      |

|   | 6.1 |        |                                      |

|   |     | 6.1.1  | Application Structure                |

|   |     | 6.1.2  | Threads                              |

|   |     | 6.1.3  | Scheduling                           |

|   |     | 6.1.4  | Memory                               |

|   |     | 6.1.5  | Restriction of Java                  |

|   |     | 6.1.6  | Implementation Results               |

|   | 6.2 |        | Defined Scheduler                    |

|   |     | 6.2.1  | Schedule Events                      |

|   |     | 6.2.2  | Data Structures                      |

|   |     | 6.2.3  | Services for the Scheduler           |

|   |     | 6.2.4  | Class Scheduler                      |

CONTENTS

|   | 6.3                 | 6.2.5<br>6.2.6<br>6.2.7<br>6.2.8<br>6.2.9<br>6.2.10<br>JVM A | Class Task  A Simple Example Scheduler  Interaction of Task, Scheduler and the JVM  Predictability  Related Work  Summary  Architecture | 132<br>133<br>135<br>137<br>140<br>140<br>141 |  |

|---|---------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

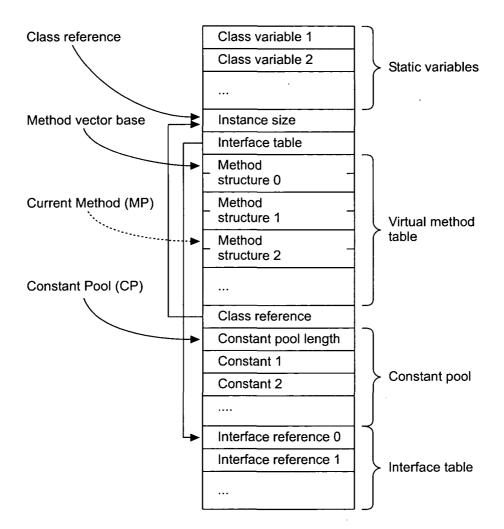

|   |                     | 6.3.1                                                        | Runtime Data Structures                                                                                                                 | 141                                           |  |

| 7 | Resu                | ılts                                                         |                                                                                                                                         | 147                                           |  |

|   | 7.1                 | Hardwa                                                       | are Platforms                                                                                                                           | 148                                           |  |

|   | 7.2                 | Resour                                                       | ce Usage                                                                                                                                | 149                                           |  |

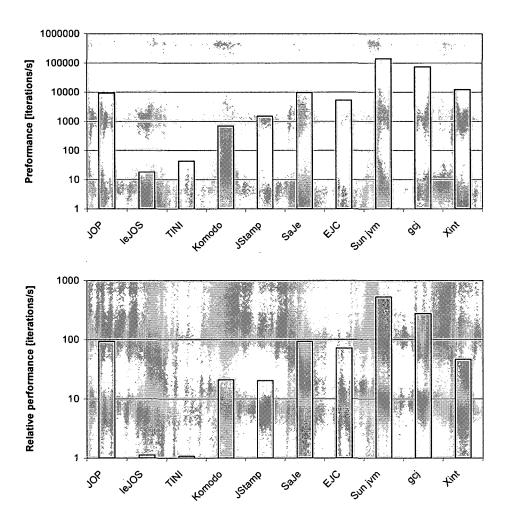

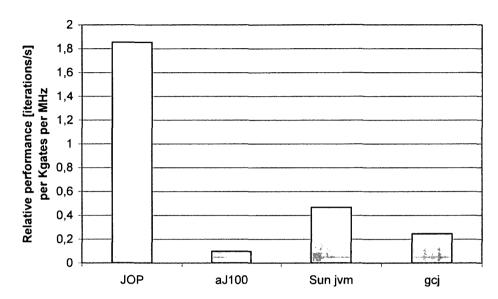

|   | 7.3                 | Perform                                                      | nance                                                                                                                                   | 152                                           |  |

|   |                     | 7.3.1                                                        | General Performance                                                                                                                     | 152                                           |  |

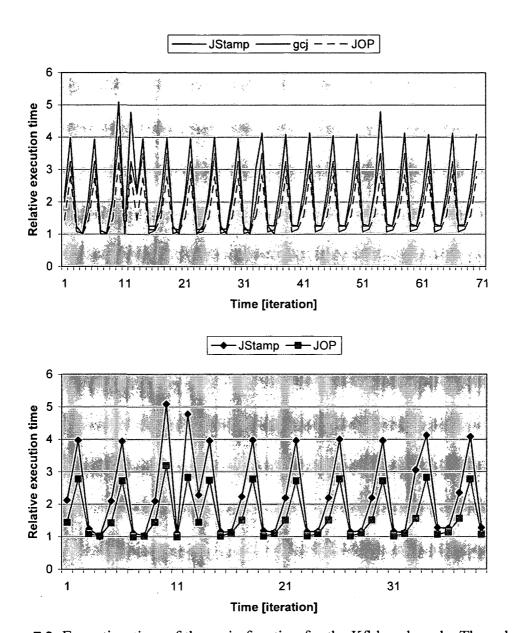

|   |                     | 7.3.2                                                        | Real-Time Performance                                                                                                                   | 159                                           |  |

|   | 7.4                 | WCET                                                         |                                                                                                                                         | 164                                           |  |

|   |                     | 7.4.1                                                        | Microcode Path Analysis                                                                                                                 | 165                                           |  |

|   |                     | 7.4.2                                                        | Microcode Low-level Analysis                                                                                                            | 166                                           |  |

|   |                     | 7.4.3                                                        | Bytecode Independency                                                                                                                   | 166                                           |  |

|   |                     | 7.4.4                                                        | WCET of Bytecodes                                                                                                                       | 167                                           |  |

|   |                     | 7.4.5                                                        | Evaluation                                                                                                                              | 167                                           |  |

|   | 7.5                 | Applica                                                      | ations                                                                                                                                  | 172                                           |  |

|   |                     | 7.5.1                                                        | Motor Control                                                                                                                           | 172                                           |  |

|   |                     | 7.5.2                                                        | Further Projects                                                                                                                        | 176                                           |  |

|   | 7.6                 | Summa                                                        | ary                                                                                                                                     | 176                                           |  |

| 8 | Cond                | clusions                                                     | ·                                                                                                                                       | 179                                           |  |

|   | 8.1                 | Conclu                                                       | sions                                                                                                                                   | 179                                           |  |

|   | 8.2                 | Summa                                                        | ary of Contributions                                                                                                                    | 180                                           |  |

|   | 8.3                 |                                                              | Research Directions                                                                                                                     | 183                                           |  |

| Α | Publ                | ications                                                     | <b>S</b>                                                                                                                                | 195                                           |  |

| В | Acronyms            |                                                              |                                                                                                                                         |                                               |  |

| С | JOP Instruction Set |                                                              |                                                                                                                                         |                                               |  |

| D | Bvte                | code Ex                                                      | recution Time                                                                                                                           | 223                                           |  |

| _ |                     |                                                              | Poculto                                                                                                                                 | 222                                           |  |

CONTENTS

F Cyclone FPGA Board

237

# 1 Introduction

This thesis introduces the concept of a Java processor for embedded real-time systems, in particular the design of a small processor for resource-constrained devices with time-predictable execution of Java programs. This Java processor is called JOP – which stands for Java Optimized Processor –, based on the assumption that a full native implementation of all Java bytecode instructions is not a useful approach.

### 1.1 Justification for Development

To justify Java's use in embedded real-time systems we quote from a document published by the National Institute of Standards and Technology [47]:

- Java's higher level of abstraction allows for increased programmer productivity (although recognizing that the tradeoff is runtime efficiency)

- Java is relatively easier to master than C++

- Java is relatively secure, keeping software components (including the JVM itself) protected from one another

- Java supports dynamic loading of new classes

- Java is highly dynamic, supporting object and thread creation at runtime

- Java is designed to support component integration and reuse

- The Java technologies have been developed with careful consideration, erring on the conservative side using concepts and techniques that have been scrutinized by the community

- The Java programming language and Java platforms support application portability

- The Java technologies support distributed applications

- Java provides well-defined execution semantics

2 1 Introduction

Based on the NIST document, the Real-Time for Java Experts Group has published the Real Time Specification for Java (RTSJ) [8] to add real-time extensions to Java.

Despite the above, to date Java is rarely used in embedded real-time systems. High resource requirements for the Java virtual machine and unpredictable real-time behavior are the main issues surrounding the use of Java for embedded systems. This thesis addresses both issues, and the proposed Java processor makes a strong case for the use of Java in embedded systems.

### 1.2 Embedded Real-Time Systems

An embedded system is a special-purpose computer system that is part of a larger system or machine. An embedded system is designed to perform a narrow range of functions with no, or minimal user intervention.

Since many embedded systems are produced in large quantities, the need to reduce costs is a major concern. Embedded systems often have significant energy constraints, and many are battery-powered. As a result of these constraints, embedded systems use a slow processor and small memory size to minimize costs and energy consumption.

Embedded systems interact with the environment and often have to produce output within a given timeframe. Therefore, most embedded systems are real-time systems. Here is a general definition of a real-time system (John A. Stankovic [88]):

In real-time computing the correctness of the system depends not only on the logical result of the computation but also on the time at which the result is produced.

However, it should be noted that 'real-time' does not mean 'really fast'. In pure real-time systems (i.e. without non real-time tasks), there is no additional value in producing results earlier than required.

Embedded real-time systems often have to handle concurrent tasks, such as communication, calculating values for a control loop, user interface and supervision. A natural way to handle these concurrent jobs is to model them as individual tasks. These tasks are executed on a preemptive multi-tasking system. Each task is assigned a priority and the multi-tasking system is responsible for scheduling individual tasks according to their priority.

To fulfil the time constraints for a real-time system, an appropriate schedule needs to be found. This problem was solved in the classic paper by Liu and Layland [61] on independent periodic tasks. The optimal priority assignment for a set of tasks is called the rate monotonic priority order, in which a task with a shorter period is

assigned a higher priority. If the Worst-Case Execution Time (WCET) of each task is known, the schedule is feasible and all tasks will meet their deadline<sup>1</sup>, if:

$$\frac{C_1}{T_1} + \dots + \frac{C_n}{T_n} \le U(n) = n(2^{\frac{1}{n}} - 1)$$

where

$C_i$  = worst-case execution time of  $task_i$

$T_i = \text{period of } task_i$

U(n) = utilization bound for n tasks.

In theory, this test is both elegant and simple. For concrete systems, two issues have to be solved:

- There are very few systems in existence that do not require communication between tasks. As a result, tasks cannot be seen as independent and blocking needs to be incorporated into the schedulability analysis.

- The WCET of each task has to be known. This is not a trivial task. Simple

measurements of execution times never fully guarantee a correct value. The

tasks therefore have to be analyzed using the correct model of the target system.

It is almost impossible to provide an accurate and correct model of modern

processors and memory systems.

Several standard textbooks on real-time systems [51, 10] deal with the first issue. JOP is intended to resolve the second issue. It should be noted that there are a number of scheduling approaches and schedulability tests. However, as a rule, these approaches all assume that the WCET of each task is known.

# 1.3 Research Objectives and Contributions

This thesis presents a hardware implementation of the Java Virtual Machine (JVM), targeting small embedded systems with real-time constraints. The processor is designed from the ground up for low WCET of bytecodes, in order to give tasks low WCET values. The following list summarizes the research objectives for the proposed Java processor:

<sup>&</sup>lt;sup>1</sup>The period of a periodic task is the time between consecutive activations of the task. The deadline of the task is assumed to be at the end of the tasks period.

### **Primary Objectives:**

- Time-predictable Java platform for embedded real-time systems

- Small design that fits into a low-cost FPGA

- A working processor, not merely a proposed architecture

### **Secondary Objectives:**

- Acceptable performance compared with mainstream non real-time Java systems

- A flexible architecture that allows different configurations for different application domains

- Definition of a real-time profile for Java

#### Contributions:

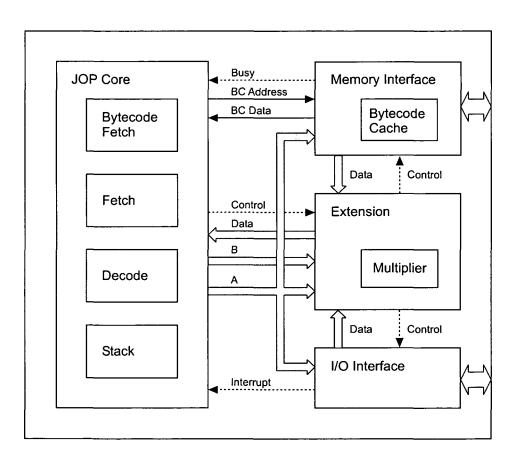

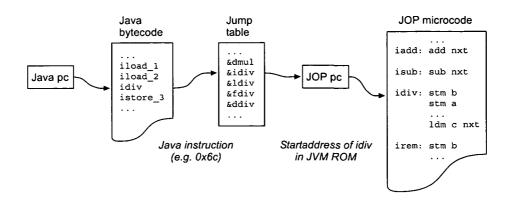

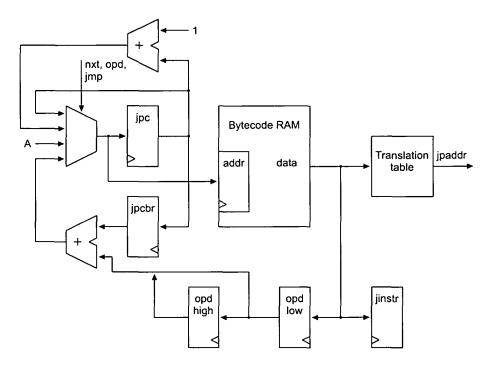

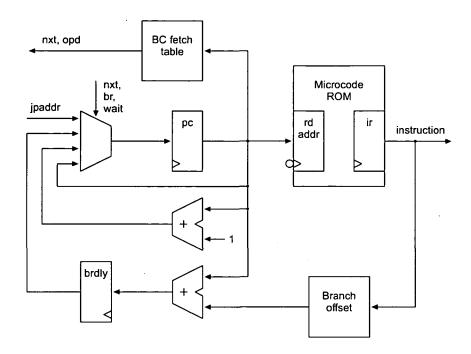

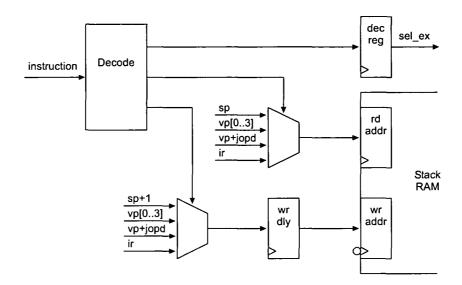

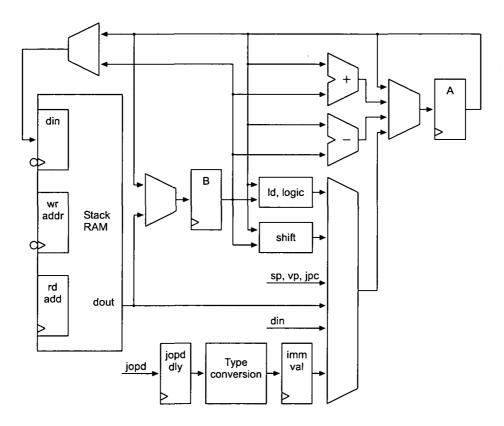

JOP is a stack computer with its own instruction set, called microcode in this thesis. Java bytecodes are translated into microcode instructions or sequences of microcode. The difference between the JVM and JOP is best described as the following:

The JVM is a CISC stack architecture, whereas JOP is a RISC stack architecture.

JOP will help to increase the acceptance of Java for embedded real-time systems. JOP is implemented as a soft-core in a Field Programmable Gate Array (FPGA). Using an FPGA as the processor for embedded systems is uncommon, because of the high costs, compared with a microcontroller. However, if the core is small enough, unused FPGA resources can be used to implement periphery in the FPGA, resulting in a lower chip count and hence lower overall costs.

The thesis' main contributions are as follows:

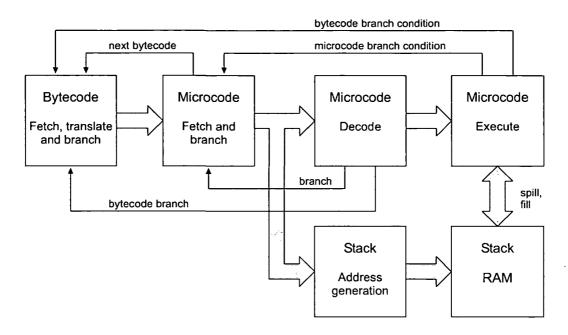

The execution time for Java bytecodes can be exactly predicted in terms of the number of clock cycles. There is no mutual dependency between consecutive bytecodes. Therefore, no pipeline analysis – with possible unbound timing effects – is necessary. These properties greatly simplify low-level WCET analysis.

In order to fill the gap between processor speed and the memory access time, caches are mandatory. In Section 5.8, a novel way to organize an instruction

cache, as *method cache*, is provided. This method cache is simple to analyze with respect to worst-case behavior and still provides a substantial performance gain when compared against a solution without an instruction cache.

The proposed processor architecture results in a predictable and highperformance execution of real-time tasks in Java, without the resource implications and unpredictability of a JIT-compiler.

JOP is microprogrammed using a novel way of mapping bytecodes to microcode addresses. This mapping has zero overheads, even for complex bytecodes.

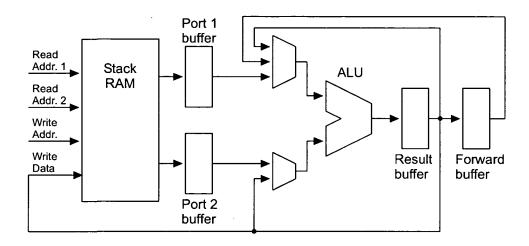

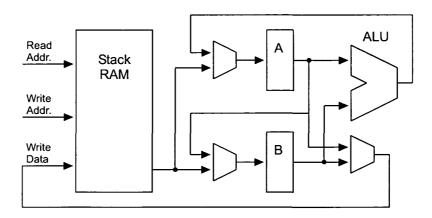

A two-level stack cache, described in Section 5.5, which fits to the embedded memory technologies of current FPGAs and ASICs, ensures the fast execution of basic instructions with minimum resource requirements. Fill and spill of the stack cache is subjected to microcode control and therefore time-predictable.

JOP is the smallest hardware implementation of the JVM available to date. This fact enables low-cost FPGAs to be used in embedded systems. The resource usage of JOP can be configured to trade size against performance for different application domains.

• The definition of standard Java does not fit hard real-time applications. Therefore, a real-time profile for Java (with restrictions) is defined in Section 6.1 and implemented on JOP. Tight integration of the scheduler and the hardware that generates schedule events results in low latency and low jitter of the task dispatch.

In this profile, hardware interrupts are represented as asynchronous events with associated threads. These events are subject to the control of the scheduler and can be incorporated into the priority assignment and schedulability analysis in the same way as normal application tasks.

• One contribution made as part of this thesis is the concrete implementation of the proposed architecture. The author is aware that it is not usually considered necessary to provide a complete implementation as part of a thesis. However, it is the opinion of the author that a simulation-only approach would lead to mistakes or small glitches. By providing a concrete implementation, we are not only confronted with the full complexity of real-life processes, but also with one or more major issues that would often be generously overlooked in a simulation. In Section 7.5, the usage of JOP in a real-world application is described.

### 1.4 Outline of the Thesis

Chapter 2 provides background information on the Java programming language and the execution environment, the Java virtual machine, for Java applications.

The related work is presented in Chapter 3. Different hardware solutions from both academia and industry for accelerating Java in embedded systems are analyzed. This chapter concludes with the research question.

Standard Java is not suitable for the resource-constrained world of embedded systems. Chapter 4 gives an overview of the different restrictions of Java for embedded and real-time systems.

Chapter 5 is the main chapter of this thesis in which the architecture of JOP is described. The motivation behind different design decisions is given.

A Java processor alone is not a complete JVM. Chapter 6 describes the runtime environment on top of JOP, including the definition of a real-time profile for Java and a framework for a user-defined scheduler in Java.

In Chapter 7, JOP is evaluated with respect to size, performance and WCET. This is followed by a description of the first commercial real-world application of JOP.

Finally, in Chapter 8, the work undertaken is reviewed and the major contributions of this thesis are presented. This chapter concludes with directions for future research using JOP and real-time Java.

# 2 Java and the Java Virtual Machine

Java technology consists of the Java language definition, a definition of the standard library, and the definition of an intermediate instruction set with an accompanying execution environment. This combination helps to make *write once, run anywhere* possible.

The following chapter gives a short overview of the Java programming language. A more detailed description of the Java Virtual Machine (JVM) and the explanation of the JVM instruction set, the so-called bytecodes follows. The exploration of dynamic instruction counts of typical Java programs can be found in Section 5.1.

### 2.1 Java

Java is a relatively new and popular programming language. The main features that have helped Java achieve success are listed below:

**Simple and object oriented:** Java is a simple programming language that appears very similar to C. This 'look and feel' of C means that programmers that know C, can switch to Java without difficulty. Java provides a simplified object model with single inheritance<sup>1</sup>.

**Portability**: To accommodate the diversity of operating environments, the Java compiler generates bytecodes – an architecture neutral intermediate format. To guarantee platform independence, Java specifies the sizes of its basic data types and the behavior of its arithmetic operators. A Java interpreter, the Java virtual machine, is available on various platforms to help make 'write once, run anywhere' possible.

Availability: Java is not only available for different operating systems, it is available at no cost. The runtime system and the compiler can be downloaded from Sun's website for Windows, Linux and Solaris. Sophisticated development environments, such as Netbeans or Eclipse, are available under the GNU Public License.

<sup>&</sup>lt;sup>1</sup> Java has single inheritance of implementation – only one class can be extended. However, a class can implement several interfaces, which means that Java has multiple interface inheritance.

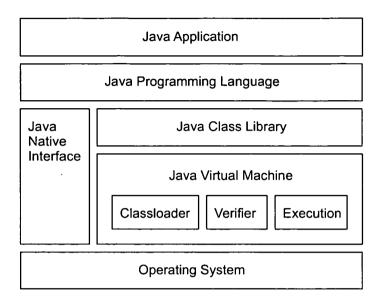

Figure 2.1: Java system overview

**Library:** The complete Java system includes a rich class library to increase programming productivity. Besides the functionality from a C standard library, it also contains other tools, such as collection classes and a GUI toolkit.

Built-in multithreading: Java supports multithreading at the language level: the library provides the Thread class, the language provides the keyword synchronized for critical sections and the runtime system provides monitor and condition lock primitives. The system libraries have been written to be thread-safe: the functionality provided by the libraries is available without conflicts due to multiple concurrent threads of execution.

**Safety:** Java provides extensive compile-time checking, followed by a second level of runtime checking. The memory management model is simple – objects are created with the new operator. There are no explicit pointer data types and no pointer arithmetic, but there is automatic garbage collection. This simple memory management model eliminates a large number of the programming errors found in C and C++ programs. A restricted runtime environment, the so-called *sandbox*, is available when executing small Java applications in Web browsers.

As can be seen in Figure 2.1, Java consists of three main components:

1. The Java programming language as defined in [33]

- 2. The class library, defined as part of the Java specification. All implementations of Java have to contain the library defined by Sun

- 3. The Java virtual machine (defined in [60]) that loads, verifies and executes the binary representation (the *class file*) of a Java program

The Java native interface supports functions written in C or C++. This combination is sometimes called *Java technology* to emphasize the fact that Java is more than just another object-oriented language.

However, a number of issues have hindered a broad acceptance of Java. The original presentation of Java as an Internet language led to the misconception that Java was not a general-purpose programming language. Another obstacle was the first implementation of the JVM as an interpreter. Execution of Java programs was *very* slow compared to compiled C/C++ programs. Although advances in its runtime technology, in particular the just-in-time compiler, have closed the performance gap, it is still a commonly held view that Java is slow.

### 2.1.1 History

The Java programming language originated as part of a research project to develop software for network devices and embedded systems. In the early '90s, Java, which was originally known as Oak [65, 67], was created as a programming tool for a consumer device that we would today call a PDA. The device (known as \*7) was a small SPARC-based hardware device with a tiny embedded OS. However, the \*7 was not issued as a product and Java was officially released in 1995 as a new language for the Internet (to be integrated into Netscape's browser). Over the years, Java technology has become a programming tool for desktop applications, web servers and server applications. These application domains resulted in the split of the Java platform into the Java standard edition (J2SE) and the enterprise edition (J2EE) in 1999. With every new release, the library (defined as part of the language) continued to grow. Java for embedded systems was clearly not an area Sun was interested in pursuing. However, with the arrival of mobile phones, Sun again became interested in this embedded market. Sun defined different subsets of Java, which have now been combined into the Java Micro Edition (J2ME). A detailed description of the J2ME follows in Section 4.3.

### 2.1.2 The Java Programming Language

The Java programming language is a general-purpose object-oriented language. Java is related to C and C++, but with a number of aspects omitted. Java is a strongly

| Type    | Description                           |

|---------|---------------------------------------|

| boolean | either true or false                  |

| char    | 16-bit Unicode character (unsigned)   |

| byte    | 8-bit integer (signed)                |

| short   | 16-bit integer (signed)               |

| int     | 32-bit integer (signed)               |

| long    | 64-bit integer (signed)               |

| float   | 32-bit floating-point (IEEE 754-1985) |

| double  | 64-bit floating-point (IEEE 754-1985) |

Table 2.1: Java primitive data types

typed language, which means that type errors can be detected at compile time. Other errors, such as wrong indices in an array, are checked at runtime. The problematic<sup>2</sup> pointer in C and explicit deallocation of memory is completely avoided. The pointer is replaced by a reference, i.e. an abstract pointer to an object. Storage for an object is allocated from the heap during creation of the object with new. Memory is freed by automatic storage management, typically using a garbage collector. The garbage collector avoids memory leaks from a missing free() and the safety problems exposed by dangling pointers.

The types in Java are divided into two categories: primitive types and reference types. Table 2.1 lists the available primitive types. Method local variables, class fields and object fields contain either a primitive type value or a reference to an object.

Classes and class instances, the objects, are the fundamental data and code organization structures in Java. There are no global variables or functions as there are in C/C++. Each method belongs to a class. This 'everything belongs to a class or an object' combined with the class naming convention, as suggested by Sun, avoids name conflicts in even the largest applications.

New classes can extend exactly one superclass. Classes that do not explicitly extend a superclass become direct subclasses of Object, the root of the whole class tree. This single inheritance model is extended by *interfaces*. Interfaces are abstract classes that only define method signatures and provide no implementation. A concrete class can implement several interfaces. This model provides a simplified form of multiple inheritance.

Java supports multitasking through *threads*. Each thread is a separate flow of control, executing concurrently with all other threads. A thread contains the method

<sup>&</sup>lt;sup>2</sup>C pointers represent memory addresses as data. Pointer arithmetic and direct access to memory leads to common and hard-to-find program errors.

stack as thread local data – all objects are shared between threads. Access conflicts to shared data are avoided by the proper use of synchronized methods or code blocks.

Java programs are compiled to a machine-independent bytecode representation as defined in [60]. Although this intermediate representation is defined for Java, other programming languages (e.g. ADA [13]) can also be compiled into Java bytecodes.

### 2.2 The Java Virtual Machine

The Java virtual machine (JVM) is a definition of an abstract computing machine that executes bytecode programs. The JVM specification [60] defines three elements:

- An instruction set and the meaning of those instructions the bytecodes

- A binary format the *class file* format. A class file contains the bytecodes, a symbol table and other ancillary information

- An algorithm to *verify* that a class file contains valid programs

In the solution presented in this thesis, the class files are verified, linked and transformed into an internal representation before being executed on JOP. This transformation is performed with JavaCodeCompact and is not executed on JOP. We will therefore omit the description of the class file and the verification process.

The instruction set of the JVM is stack-based. All operations take their arguments from the stack and put the result onto the stack. Values are transferred between the stack and various memory areas. We will discuss these memory areas first, followed by an explanation of the instruction set.

### 2.2.1 Memory Areas

The JVM contains various runtime data areas. Some of these areas are shared between threads, whereas other data areas exist separately for each thread.

**Method area:** The method area is shared among all threads. It contains static class information such as field and method data, the code for the methods and the constant pool. The constant pool is a per-class table, containing various kinds of constants such as numeric values or method and field references. The constant pool is similar to a symbol table.

Part of this area, the code for the methods, is very frequently accessed (during instruction fetch) and therefore is a good candidate for caching.

**Heap:** The heap is the data area where all objects and arrays are allocated. The heap is shared among all threads. A garbage collector reclaims storage for objects.

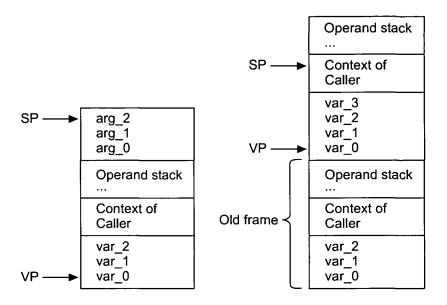

JVM stack: Each thread has a private stack area that is created at the same time as the thread. The JVM stack is a logical stack that contains following elements:

- 1. A frame that contains return information for a method

- 2. A local variable area to hold local values inside a method

- 3. The operand stack, where all operations are performed

Although it is not strictly necessary to allocate all three elements to the same type of memory we will see in Section 5.5 that the argument-passing mechanism regulates the layout of the JVM stack.

Local variables and the operand stack are accessed as frequently as registers in a standard processor. A Java processor shall provide some caching mechanism of this data area.

The memory areas are similar to the various segments in conventional processes (e.g. the method code is analogous to the 'text' segment). However, the operand stack replaces the registers in a conventional processor.

### 2.2.2 JVM Instruction Set

The instruction set of the JVM contains 201 different instructions [60], the *bytecodes* that can be grouped into the following categories:

Load and store: Load instructions push values from the local variables onto the operand stack. Store instructions transfer values from the stack back to local variables. 70 different instructions belong to this category. Short versions (single byte) exist to access the first four local variables. There are unique instructions for each basic type (int, long, float, double and reference). This differentiation is necessary for the bytecode verifier, but is not needed during execution. For example iload, fload and aload all transfer one 32-bit word from a local variable to the operand stack.

Arithmetic: The arithmetic instructions operate on the values found on the stack and push the result back onto the operand stack. There are arithmetic instructions for int, float and double. There is no direct support for byte, short or char types. These values are handled by int operations and have to be converted back before being stored in a local variable or an object field.

- **Type conversion:** The type conversion instructions perform numerical conversions between all Java types: as implicit widening conversions (e.g. int to long, float or double) or explicit (by casting to a type) narrowing conversions.

- **Object creation and manipulation:** Class instances and arrays (that are also objects) are created and manipulated with different instructions. Objects and class fields are accessed with type-less instructions.

- Operand stack manipulation: All direct stack manipulation instructions are typeless and operate on 32-bit or 64-bit entities on the stack. Examples of these instructions are dup, to duplicate the top operand stack value, and pop, to remove the top operand stack value.

- Control transfer: Conditional and unconditional branches cause the JVM to continue execution with an instruction other than the one immediately following. Branch target addresses are specified relative to the current address with a signed 16-bit offset. The JVM provides a complete set of branch conditions for int values and references. Floating-point values and type long are supported through compare instructions. These compare instructions result in an int value on the operand stack.

- Method invocation and return: The different types of methods are supported by four instructions: invoke a class method, invoke an instance method, invoke a method that implements an interface and an invokespecial for an instance method that requires special handling, such as private methods or a superclass method.

A bytecode consists of one instruction byte followed by optional operand bytes. The length of the operand is one or two bytes, with the following exceptions: multianewarray contains 3 operand bytes; invokeinterface contains 4 operand bytes, where one is redundant and one is always zero; lookupswitch and tableswitch (used to implement the Java switch statement) are variable-length instructions; and goto\_w and jsr\_w are followed by a 4 byte branch offset, but neither is used in practice as other factors limit the method size to 65535 bytes.

#### 2.2.3 Methods

A Java method is equivalent to a function or procedure in other languages. In object oriented terminology this method is invoked instead of called. We will use method and invoke in the remainder of this text. In Java and the JVM, there are five types of methods:

- Static or class methods

- Virtual methods

- Interface methods

- Class initialization

- Constructor of the parent class (super())

For these five types there are only four different bytecodes:

- invokestatic: A class method (declared static) is invoked. As the target does not depend on an object, the method reference can be resolved at load/link time.

- invokevirtual: An object reference is resolved and the corresponding method is invoked. The resolution is usually done with a dispatch table per class containing all implemented and inherited methods. With this dispatch table, the resolution can be performed in constant time.

- invokeinterface: An interface allows Java to emulate multiple inheritance. A class can implement several interfaces, and different classes (that have no inheritance relation) can implement the same interface. This flexibility results in a more complex resolution process. One method of resolution is a search through the class hierarchy that results in a variable, and possibly lengthy, execution time. A constant time resolution is possible by assigning every interface method a unique number. Each class that implements an interface needs its own table with unique positions for each interface method of the *whole* application.

- invokespecial: Invokes an instance method with special handling for superclass, private, and instance initialization. This bytecode catches many different cases. This results in expensive checks for common private instance methods.

### 2.2.4 Implementation of the JVM

There are several different ways to implement a virtual machine. The following list presents these possibilities and analyses how appropriate they are for embedded devices.

```

for (;;) {

instr = bcode[pc++];

switch (instr) {

...

case IADD:

tos = stack[sp]+stack[sp-1];

--sp;

stack[sp] = tos;

break;

...

}

}

```

Listing 2.1: Typical JVM interpreter loop

Interpreter: The simplest realization of the JVM is a program that interprets the bytecode instructions. The interpreter itself is usually written in C and is therefore easy to port to a new computer system. The interpreter is very compact, making this solution a primary choice for resource-constrained systems. The main disadvantage is the high execution overhead. From a code fragment of the typical interpreter loop, as shown in Listing 2.1, we can examine the overhead: The emulation of the stack in a high-level language results in three memory accesses for a simple i add bytecode. The instruction is decoded through an indirect jump. Indirect jumps are still a burden for standard branch prediction logic.

Just-In-Time Compilation: Interpreting JVMs can be enhanced with just-in-time (JIT) compilers. A JIT compiler translates Java bytecodes to native instructions during runtime. The time spent on compilation is part of the application execution time. JIT compilers are therefore restricted in their optimization capacity. To reduce the compilation overhead, current JVMs operate in mixed mode: Java methods are executed in interpreter mode and the call frequency is monitored. Often-called methods, the hot spots, are then compiled to native code.

JIT compilation has several disadvantages for embedded systems, notably that a compiler (with the intrinsic memory overhead) is necessary on the target sys-

tem. Due to compilation during runtime, execution times are not predictable<sup>3</sup>.

**Batch Compilation:** Java can be compiled, in advance, to the native instruction set of the target. Precompiled libraries are linked with the application during runtime. This is quite similar to C/C++ applications with shared libraries. This solution undermines the flexibility of Java: dynamic class loading during runtime. However, this is not a major concern for embedded systems.

Hardware Implementation: A Java processor is the implementation of the JVM in hardware. The JVM bytecode is the native instruction set of such a processor. This solution can result in quite a small processor, as a stack architecture can be implemented very efficiently. A Java processor is memory-efficient as an interpreting JVM, but avoids the execution overhead. The main disadvantage of a Java processor is the lack of capability to execute C/C++ programs.

### 2.3 Summary

Java is a unique combination of the language definition, a rich class library and a runtime environment. A Java program is compiled to bytecodes that are executed by a Java virtual machine. Strong typing, runtime checks and avoidance of pointers make Java a *safe* language. The intermediate bytecode representation simplifies porting of Java to different computer systems. An interpreting JVM is easy to implement and needs few system resources. However, the execution speed suffers from interpreting. JVMs with a just-in-time compiler are state-of-the-art for desktop and server systems. These compilers require large amounts of memory and have to be ported for each processor architecture, which means they are not the best choice for embedded systems. A Java processor is the implementation of the JVM as a concrete machine. A Java processor avoids the slow execution model of an interpreting JVM and the memory requirements of a compiler, thus making it an interesting execution system for Java in embedded systems.

<sup>&</sup>lt;sup>3</sup>Even if the time for the compilation is known, the WCET for a method has to include the compile time!

# 3 Related Work

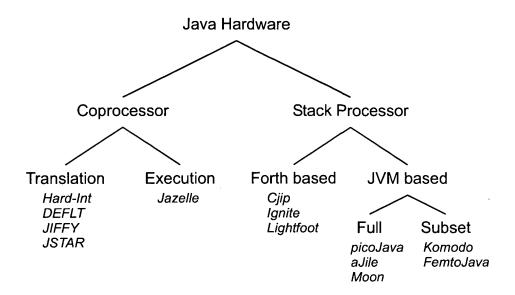

Two different approaches can be found to improve Java bytecode execution by hardware. The first type operates as a Java coprocessor in conjunction with a general-purpose microprocessor. This coprocessor is placed in the instruction fetch path of the main processor and translates Java bytecodes to sequences of instructions for the host CPU or directly executes basic Java bytecodes. The complex instructions are emulated by the main processor. Java chips in the second category replace the general-purpose CPU. All applications therefore have to be written in Java. While the first type enables systems with mixed code capabilities, the additional component significantly raises costs. Table 3.1 provides an overview of the described Java hardware.

Blank fields in the table indicate that the information is not available or not applicable (e.g. for simulation-only projects). Minimum CPI is the number of clock cycles for a simple instruction such as nop. One entry, the TINI system, is not a real Java hardware, but is included in the table since it is often incorrectly cited as an embedded Java processor.

## 3.1 Hardware Translation and Coprocessors

The simplest enhancement for Java is a translation unit, which substitutes the switch statement of an interpreter JVM (bytecode decoding) through hardware and/or translates simple bytecodes to a sequence of RISC instructions on the fly.

A standard JVM interpreter contains a loop with a large switch statement that decodes the bytecode (see Listing 2.1). This switch statement is compiled to an indirect branch. The destinations of these indirect branches change frequently and do not benefit from branch-prediction logic. This is the main overhead for simple bytecodes on modern processors. The following approaches enhance the execution of Java programs on a standard processor through the substitution of the memory read and switch statement with bytecode fetch and decode through hardware.

<sup>&</sup>lt;sup>1</sup>TINI is a standard interpreting JVM running on an enhanced 8051 processor.

<sup>&</sup>lt;sup>2</sup>J2ME CLDC stands for Java2 Micro Edition, Connected Limited Device Configuration, which is described in Section 4.3.1.

|           | Туре                 | Target                 | Size                    | Speed | Java                                   | Min. |

|-----------|----------------------|------------------------|-------------------------|-------|----------------------------------------|------|

|           |                      | technology             |                         | [MHz] | standard                               | CPI  |

| Hard-Int  | Translation          | Simulation only        |                         |       |                                        |      |

| DELFT     | Translation          | Simulation only        |                         |       |                                        |      |

| JIFFY     | Translation          | Xilinx<br>FPGA         | 3800 LCs,<br>1KB RAM    |       |                                        |      |

| Jazelle   | Co-<br>processor     | ASIC 0.18μ             | 12K gates               | 200   |                                        |      |

| JSTAR     | Co-<br>processor     | ASIC 0.18µ<br>Softcore | 30K gates +<br>7KB      | 104   | J2ME<br>CLDC <sup>2</sup>              |      |

| TINI      | Software<br>JVM      | Enhanced<br>8051 clone |                         |       | Java 1.1<br>subset                     |      |

| picoJava  | Processor            | No<br>realization      | 128K gates<br>+ memory  |       | Full                                   | 1    |

| aJile     | Processor            | ASIC 0.25μ             | 25K gates +<br>ROM      | 100   | J2ME<br>CLDC <sup>2</sup>              |      |

| Cjip      | Processor            | ASIC 0.35μ             | 70K gates +<br>ROM, RAM | 67    | J2ME<br>CLDC <sup>2</sup>              | 6    |

| Ignite    | Stack pro-<br>cessor | Xilinx<br>FPGA         | 9700 LCs                |       |                                        |      |

| Moon      | Processor            | Altera<br>FPGA         | 3660 LCs,<br>4KB RAM    |       |                                        |      |

| Lightfoot | Processor            | Xilinx<br>FPGA         | 3400 LCs                | 40    |                                        |      |

| LavaCORE  | Processor            | Xilinx<br>FPGA         | 3800 LCs<br>30K gates   | 20    |                                        |      |

| Komodo    | Processor            | Xilinx<br>FPGA         | 2600 LCs                | 20    | Subset: 50<br>bytecodes                | 4    |

| FemtoJava | Processor            | Altera Flex<br>10K     | 2000 LCs                | 4     | Subset: 69<br>bytecodes,<br>16-bit ALU | 3    |

| JSM [12]  | Processor            | Xilinx<br>FPGA         |                         | 3.5   | Java Card                              |      |

Table 3.1: Java hardware

#### 3.1.1 Hard-Int

Radhakrichnan [80] proposes an additional architecture for a standard RISC processor to speed up a JVM interpreter. The architecture, called Hard-Int, is placed between the cache and instruction fetch of the RISC processor. Simple Java bytecodes are translated to a sequence of RISC instructions. For native RISC code, the unit is bypassed. This architecture implements the expensive switch statement of a typical interpreter in hardware. A simulation of a SPARC processor with four execution units shows a speedup by the factor of 2.6 over JDK 1.2 JIT with SPECjvm98. Since the architecture is only evaluated in a software simulation, the impact of the inserted hardware on the clock frequency of the RISC processor is unknown. No estimation of the additional hardware cost for the translation unit is given.

### 3.1.2 DELFT-JAVA Engine

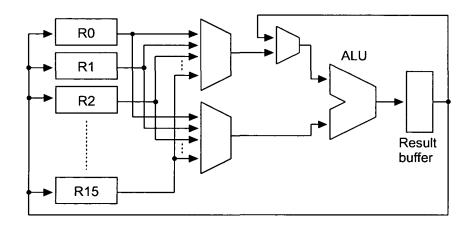

In his thesis [32], Glossner describes a processor for multimedia applications in Java. A RISC processor is extended with DSP capabilities and Java specific instructions. This combination results in a very complex processor. Simple JVM instructions are dynamically translated to the DELFT instruction set. However, no explanation is given as to how this is done. A new register-addressing mode, indirect register addressing with auto increment or decrement, provides support for stack caching in the register file. The translation of JVM bytecode to the DELFT instruction set maps stack-based dependencies into pipeline dependencies. The author expects that these dependencies can be resolved with standard techniques such as register renaming and out-of-order execution. To accelerate dynamic linking a link translation buffer cache resolved entries from the constant pool.

The processor is validated through a C++ model. An experiment with a synthetic benchmark (vector multiplication) compared a stack machine with an ideal register machine. The ideal register machine performs register renaming and out-of-order execution on multiple execution units. The achieved speedup in this experiment was 2.7. The high-level simulation model is more a proof of concept and no estimation is given for the resources needed to implement this complex processor. Since only a restricted subset of the JVM was simulated, no Java applications could be used to estimate the expected speedup.

#### 3.1.3 **JIFFY**

An interesting approach to enhance Java execution in embedded systems is presented in Acher's thesis [1]. He states that JIT-compilation in software is not possible on most embedded devices because of resource constraints. JIFFY, a JIT in an FPGA,

20 3 Related Work

is proposed as a solution to this problem. The compilation is done in the following steps:

The Java bytecode is translated into an intermediate language with three registers and a stack. The reduction to three registers is due to the fact that bytecodes are using a maximum of three stack operands, and it simplifies translation to CISC-architectures with a low register count. In the next step, this instruction sequence, which is still stack-based, is optimized. The main effect of this optimization is to transform stack-based operations into register-based operations. These optimized instructions in the intermediate language are translated to native instructions of the target architecture in the last step.

The quality of the generated code was tested with software versions of JIFFY for a CISC (80586) and a RISC (Alpha 21164) architecture. The resulting code is about 1.1 to 7.5 times faster than interpreting Java bytecode on the x86 architecture. The speedup is similar to Suns first JIT compiler (sunwjit in JDK 1.1). The compilation time is estimated to be 50 to 70 clock cycles for one bytecode. This is 10 times faster than the efficient CACAO JIT [53]. A first prototype implementation in an FPGA used 3800 LCs and 8KBits RAM (80 % of a Xilinx XC2S200).

#### 3.1.4 Jazelle

Jazelle [3] is an extension of the ARM 32-bit RISC processor, similar to the Thumb state (a 16-bit mode for reduced memory consumption). The Jazelle coprocessor is integrated into the same chip as the ARM processor. The hardware bytecode decoder logic is implemented in less than 12K gates. It accelerates, according to ARM, some 95% of the executed bytecodes. 140 bytecodes are executed directly in hardware, while the remaining 94 are emulated by sequences of ARM instructions. This solution also uses code modification with *quick* instructions to substitute certain object-related instructions after link resolution. All Java bytecodes, including the emulated sequences, are re-startable to enable a fast interrupt response time.

A new ARM instruction puts the processor into Java state. Bytecodes are fetched and decoded in two stages, compared to a single stage in ARM state. Four registers of the ARM core are used to cache the top stack elements. Stack spill and fill is handled automatically by the hardware. Additional registers are reused for the Java stack pointer, the variable pointer, the constant pool pointer and locale variable 0 (the *this* pointer in methods). Keeping the complete state of the Java mode in ARM registers simplifies its integration into existing operating systems.

### 3.1.5 JSTAR, JA108

Nozomi's JA108 [14], previously known as JSTAR, Java coprocessor sits between the native processor and the memory subsystem. JA108 fetches Java bytecodes from memory and translates them into native microprocessor instructions. JA108 acts as a pass-through when the core processor's native instructions are being executed. The JA108 is targeted for use in mobile phones to increase performance of Java multimedia applications. The coprocessor is available as standalone package or with included memory and can be operated up to 104MHz. The resource usage for the JSTAR is known to be about 30K gates plus 45Kbits for the microcode.

### 3.1.6 A Co-Designed Virtual Machine

In his thesis [49], Kent proposes an interesting new form of Java coprocessor. He investigates hardware/software co-design for a JVM within the context of a desktop workstation. The execution of the JVM is partitioned between an FPGA and the host processor. An FPGA board with local memory is connected via the PCI bus to the host. This solution provides an add-on accelerator without changing the system. Moreover, as the FPGA can be configured for a different task, the add-on hardware can be used for non-Java applications.

The critical issue in this approach is the partitioning of the JVM and the memory regions between hardware and software. Not all Java bytecodes can be executed in hardware. All object-oriented bytecodes are performed in software. However, once these bytecodes are replaced by their *quick* variants, some of them can then be executed in hardware. The most accessed data structures, i.e. the method's bytecode, execution stack and local variables, are placed in the FPGA board memory. The constant pool and the heap reside in the PC's main memory. The software part of the JVM decides during runtime which instruction sequences can be executed by the hardware. Due to the high cost of a context switch, this is a critical decision. Kent explored various algorithms with different block sizes to find the optimum partitioning of the instructions between the host processor and the FPGA. Tests with small benchmarks on a simulation showed performance gains by a factor of 6 to 11, when compared with an interpreting JVM. Kent is now working on the concurrent use of the FPGA and the host system to execute Java applications. Additional performance increases are expected for multi-threaded applications.

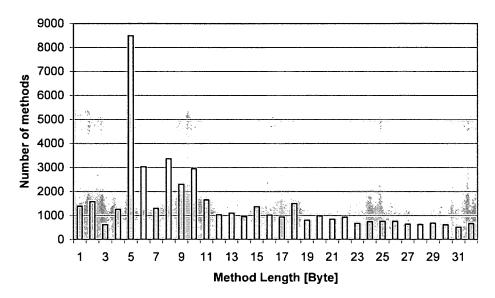

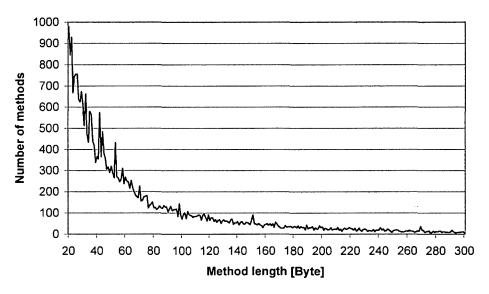

In our view, there are two potential problems with this approach. Firstly, the execution context for the hardware is too small. As invokevirtual and the quick version are implemented in the software partition, the maximum context is one method body. As shown in Section 5.1.2, Java methods are usually small (about 30% are less than 9 bytes long), resulting in many context switches. The second issue is the raw speedup,

without communication overhead, of the FPGA solution. This speedup is stated to be around of 10 times greater, with the same clock frequency. However, FPGA clock rate will never reach the clock rate of a general-purpose processor. With a meaningful design, such as a CPU, the clock rate of an FPGA is about 20 to 50 times lower. However, everyone who uses an FPGA as target technology for a processor design faces this problem. It is better not to try to compete against mainstream PC technology.

### 3.2 Java Processors

Java Processors are primarily used in an embedded system. In such a system, Java is the native programming language and all operating system related code, such as device drivers, are implemented in Java. Java processors are simple or extended stack architectures with an instruction set that resembles more or less the bytecodes from the JVM.

### 3.2.1 picoJava

Sun's picoJava is the Java processor most often cited in research papers. It is used as a reference for new Java processors and as the basis for research into improving various aspects of a Java processor. Ironically, this processor was never released as a product by Sun. After Sun decided to not produce picoJava in silicon, Sun licensed picoJava to Fujitsu, IBM, LG Semicon and NEC. However, these companies also did not produce a chip and Sun finally provided the full Verilog code under an open-source license.

Sun introduced the first version of picoJava [73] in 1997. The processor was targeted at the embedded systems market as a pure Java processor with restricted support of C. picoJava-I contains four pipeline stages. A redesign followed in 1999, known as picoJava-II. This is the version described below. picoJava-II is now freely available with a rich set of documentation [89, 90].

Simple Java bytecodes are directly implemented in hardware, most of them execute in one to three cycles. Other performance critical instructions, for instance invoking a method, are implemented in microcode. picoJava traps on the remaining complex instructions, such as creation of an object, and emulates this instruction. To access memory, internal registers and for cache management picoJava implements 115 extended instructions with 2-byte opcodes. These instructions are necessary to write system-level code to support the JVM.

Traps are generated on interrupts, exceptions and for instruction emulation. A trap is rather expensive and has a minimum overhead of 16 clock cycles:

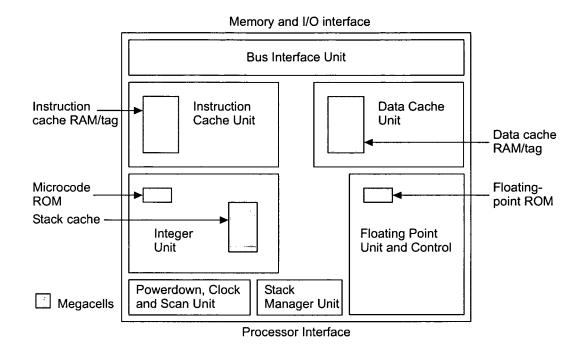

Figure 3.1: Block diagram of picoJava-II (from [89])

- 6 clocks trap execution

- n clocks trap code

- 2 clocks set VARS register

- 8 clocks return from trap

This minimum value can only be achieved if the trap table entry is in the data cache and the first instruction of the trap routine is in the instruction cache. The worst-case interrupt latency is 926 clock cycles [90].

Figure 3.1 shows the major function units of picoJava. The integer unit decodes and executes picoJava instructions. The instruction cache is direct-mapped, while the data cache is two-way set-associative, both with a line size of 16 bytes. The caches can be configured between 0 and 16 Kbytes. An instruction buffer decouples the instruction cache from the decode unit. The FPU is organized as a microcode engine with a 32-bit datapath supporting single- and double-precision operations. Most single-precision operations require four times the number of cycles as single-precision operations. For low-cost designs, the FPU can be removed and the core traps on floating-point instructions to a software routine to emulate these instructions. picoJava provides a 64-entry stack cache as a register file. The core manages this register file as a circular buffer, with a pointer to the top of stack. The stack management unit automatically performs spill

A Java instruction

```

c = a' + b;

```

translates to the following bytecodes:

```

iload_1

iload_2

iadd

istore 3

```

Figure 3.2: A common folding pattern that is executed in a single cycle

to and fill from the data cache to avoid overflow and underflow of the stack buffer. To provide this functionality the register file contains five memory ports. Computation needs two read ports and one write port, the concurrent spill and fill operations the two additional read and write ports. The processor core consists of following six pipeline stages:

**Fetch:** Fetch 8 bytes from the instruction cache or 4 bytes from the bus interface to the 16-byte-deep prefetch buffer.

**Decode:** Group and precode instructions (up to 7 bytes) from the prefetch buffer. Instruction folding is performed on up to four bytecodes.

Register: Read up to two operands from the register file (stack cache).

**Execute:** Execute simple instructions in one cycle or microcode for multi-cycle instructions.

Cache: Access the data cache.

Writeback: Write the result back into the register file.

The integer unit together with the stack unit provides a mechanism, called instruction folding, to speed up common code patterns found in stack architectures, as shown in Figure 3.2. When all entries are contained in the stack cache, the picoJava core can fold these four instructions to one RISC-style single cycle operation.

picoJava contains a simple mechanism to speed-up the common case for monitor enter and exit. The two low order bits of an object reference are used to indicate the lock holding or a request to a lock held by another thread. These bits are examined by monitorenter and monitorexit. For all other operations on the reference, these two bits are masked out by the hardware. Hardware registers cache up to two locks held by a single thread.

To efficiently implement a generational or an incremental garbage collector picoJava offers hardware support for write barriers through memory segments. The hardware checks all stores of an object reference if this reference points to a different segment (compared to the store address). In this case, a trap is generated and the garbage collector can take the appropriate action. Additional two reserved bits in the object reference can be used for a write barrier trap.

The architecture of picoJava is a stack-based CISC processor implementing 341 different instructions [73] and is the most complex Java processor available. The processor can be implemented [23] in about 440K gates (128K for the logic and 314K for the memory components: 284x80 bits microcode ROM, 2x192x64 bits FPU ROM and 2x16KB caches).

#### 3.2.2 aJile JEMCore

aJile's JEMCore is a direct-execution Java processor that is available as both an IP core and a stand alone processor [2, 37]. It is based on the 32-bit JEM2 Java chip developed by Rockwell-Collins. JEM2 is an enhanced version of JEM1, created in 1997 by the Rockwell-Collins Advanced Architecture Microprocessor group. Rockwell-Collins originally developed JEM for avionics applications by adapting an existing design for a stack-based embedded processor. Rockwell-Collins decided not to sell the chip on the open market. Instead, it licensed the design exclusively to aJile Systems Inc., which was founded in 1999 by engineers from Rockwell-Collins, Centaur Technologies, Sun Microsystems, and IDT.

The core contains 24 32-bit wide registers. Six of them are used to cache the top elements of the stack. The datapath consists of a 32-bit ALU, a 32-bit barrel shifter and the support for floating point operations (disassembly/assembly, overflow and NaN detection). The control store is a 4K by 56 ROM to hold the microcode that implements the Java bytecode. An additional RAM control store can be used for custom instructions. This feature is used to implement the basic synchronization and thread scheduling routines in microcode. This results in low execution overheads with thread-to-thread yield of less than one  $\mu$ s (at 100MHz). An optional Multiple JVM Manager (MJM) supports two independent, memory protected JVMs. The two JVMs execute time-sliced on the processor. According to aJile, the processor can be implemented in 25K gates (without the microcode ROM). The MJM needs additional 10K gates.

26 3 Related Work

Two silicon versions of JEM exist today: the aJ-80 and the aJ-100. Both versions comprise a JEM2 core, the MJM, 48KB zero wait state RAM and peripheral components, such as timer and UART. 16KB of the RAM is used for the writable control store. The remaining 32KB is used for storage of the processor stack. The aJ-100 provides a generic 8-bit, 16-bit or 32-bit external bus interface, while the aJ-80 only provides an 8-bit interface. The aJ-100 can be clocked up to 100MHz and the aJ-80 up to 66MHz. The power consumption is about 1mW per MHz.

Since a Jile was a member of the Real-Time for Java Expert Group, the complete RTSJ will be available in the near future. One nice feature of this processor is its availability. A relatively cheap development system, the JStamp [91], was used to compare this processor with JOP.

### 3.2.3 Cjip

The Cjip processor [36, 43] supports multiple instruction sets, allowing Java, C, C++ and assembler to coexist. Internally, the Cjip uses 72 bit wide microcode instructions, to support the different instruction sets. At its core, Cjip is a 16-bit CISC architecture with on-chip 36KB ROM and 18KB RAM for fixed and loadable microcode. Another 1KB RAM is used for eight independent register banks, string buffer and two stack caches. Cjip is implemented in 0.35-micron technology and can be clocked up to 66MHz. The logic core consumes about 20% of the 1.4-million-transistor chip. The Cjip has 40 program controlled I/O pins, a high-speed 8 bit I/O bus with hardware DMA and an 8/16 bit DRAM interface.

The JVM is implemented largely in microcode (about 88% of the Java bytecodes). Java thread scheduling and garbage collection are implemented as processes in microcode. Microcode is also used to implement virtual peripherals such as watchdog timers, display and keyboard interfaces, sound generators and multimedia codecs.

Microcode instructions execute in two or three cycles. A JVM bytecode requires several microcode instructions. The Cjip Java instruction set and the extensions are described in detail in [42]. For example: a bytecode nop executes in 6 cycles while an iadd takes 12 cycles. Conditional bytecode branches are executed in 33 to 36 cycles. Object oriented instructions such getfield, putfield or invokevirtual are not part of the instruction set.

### 3.2.4 Ignite, PSC1000

The PSC1000 [77] is a stack processor, based on ShBoom (originally designed by Chuck Moore [68]), designed for high speed Forth applications. The PSC1000 was later renamed to Ignite and promoted as a Java-processor, though it has it roots in

Forth. The instruction set, called ROSC (Removed Operand Set Computer), is different from Java bytecodes. A small JVM driver converts Java bytecode into the stack instruction set of the processor.

The processor contains two on-chip stacks, as usual in Forth processors [52], and additional 16 global registers. The first elements of the stacks are directly accessible. The bottleneck of instruction fetching without a cache is avoided by fetching up to four 8-bit instructions from a 32-bit memory. To simplify instruction decoding immediate values and branch offsets are placed right aligned in such an instruction group. The PSC1000 is available as ASIC at 80MHz and as a soft-core for Xilinx FPGAs (9700 LCs).

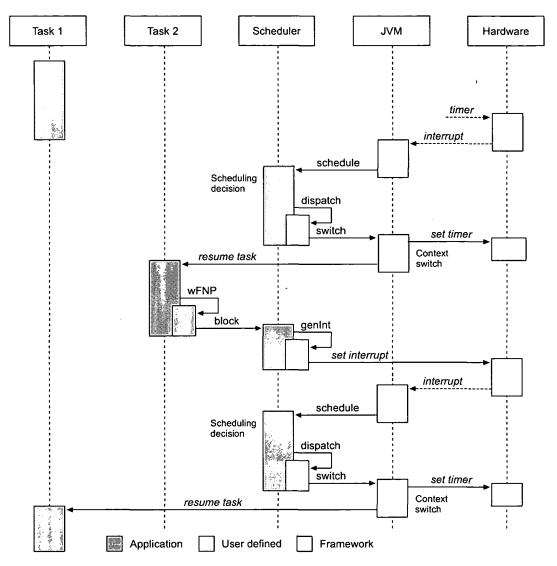

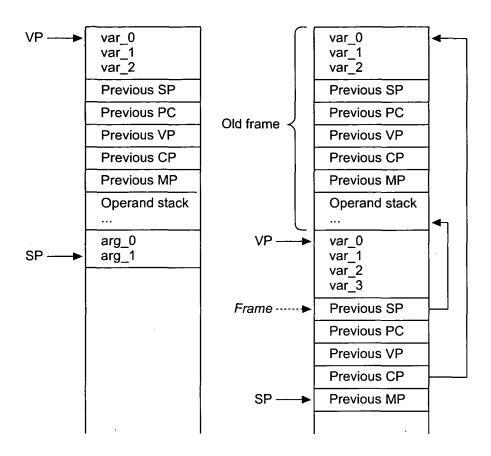

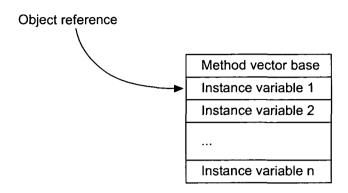

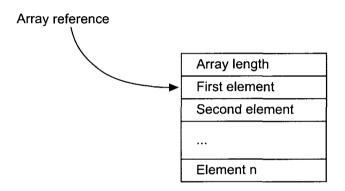

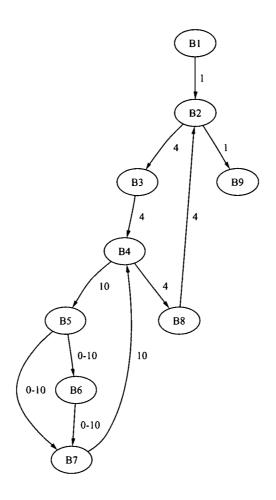

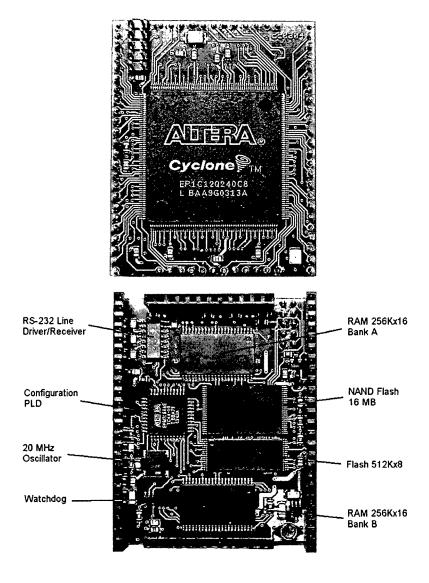

#### 3.2.5 Moon