The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR INFORMATIK

Faculty of Informatics

# ASCARTS

# Design of an Asynchronous Processor using a High-Level Specification Language

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieurin**

im Rahmen des Studiums

## Technische Informatik

eingereicht von

## Claudia Hermann

Matrikelnummer 0125532

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Mitwirkung: Dipl.-Ing. Dr.techn. Jakob Lechner

Wien, 21. Jänner 2016

Claudia Hermann

Andreas Steininger

Faculty of Informatics

# **ASCARTS**

# Design of an Asynchronous Processor using a High-Level Specification Language

# DIPLOMA THESIS

submitted in partial fulfillment of the requirements for the degree of

# **Diplom-Ingenieurin**

in

## **Computer Engineering**

by

## Claudia Hermann

Registration Number 0125532

to the Faculty of Informatics

at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Assistance: Dipl.-Ing. Dr.techn. Jakob Lechner

Vienna, 21<sup>st</sup> January, 2016

Claudia Hermann

Andreas Steininger

# Erklärung zur Verfassung der Arbeit

Claudia Hermann Am Haanbaum 3/7, 3001 Mauerbach

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 21. Jänner 2016

Claudia Hermann

# Kurzfassung

Das Ziel dieser Arbeit ist die Entwicklung des asynchronen Prozessors ASCARTS basierend auf dem Befehlssatz des synchronen Prozessors SCARTS. Für die Umsetzung des Prozessordesigns wird das Open-Source Framework Balsa verwendet, welches die Modellierung asynchroner Schaltungen auf einer abstrakten Ebene durch Verbergen der eigentlichen Handshake-Implementierung erlaubt. Die Benutzerfreundlichkeit der Balsa-Sprache sowie der zugehörigen Werkzeugkette für einen komplexen Schaltungsaufbau ist zu bewerten. Ist das Balsa-Framework ausgereift genug um einen ganzen asynchronen Prozessor zu entwerfen und zu synthetisieren? Ein weiteres Ziel dieser Arbeit ist es, die Unterschiede in der Prozessorarchitektur von synchronen und asynchronen Prozessoren mit identischen ISAs zu identifizieren. Daten- und Steuerkonflikte, die durch die asynchrone Pipeline-Architektur verursacht werden, erfordern innovative Lösungen. Datenkonflikte werden mithilfe eines asynchronen Weiterleitungsmechanismus, basierend auf gespeicherten Informationen über vorhergehende Befehle, vermieden. Um Steuerkonflikte zu lösen wird ein Farbalgorithmus, ähnlich zu den in AMULET1 und SAMIPS verwendeten, implementiert. Um die Prozessorschnittstelle zu herkömmlichen synchronen Speichern zu verbinden, werden die Handshake-Signale in synchrone Signale transformiert. Das Balsa-Design wird mit der quasi delay-insensitive four-phase dual-rail Handshake-Implementierung synthetisiert. Die synthetisierte Netzliste wird auf die UMC 90 nm Technologie abgebildet, auf der Timing-Simulationen durchgeführt werden. Da Synchronisation über das Handshake-Protokoll erreicht wird, passt sich das Design an die tatsächlich vorherrschenden Betriebsbedingungen an. Das führt zu variablen Average-Case-Ausführungszeiten der einzelnen Befehle. Daher ist die Echtzeitfähigkeit ohne genaue Worst-Case-Analyse nicht klar ersichtlich. Die Timing-Simulationsergebnisse von ASCARTS mit Average-Case-Corner Synthese werden mit den Ergebnissen von SCARTS mit Worst-Case-Corner Synthese verglichen. Ein zentrales Ergebnis der vorgestellten ASCARTS Implementierung ist die Prozessorbeschreibung selbst, geschrieben in einer High-Level-HDL, die unabhängig von der tatsächlichen Handshake-Implementierung ist. Daher könnte die Balsa-Beschreibung von ASCARTS nützlich für zukünftige Forschungsarbeiten an unterschiedlichen asynchronen Implementierungsstilen sein.

# Abstract

The purpose of this thesis is the development of the asynchronous processor ASCARTS based on the instruction set of the synchronous processor SCARTS. For the realization of the processor design the open-source framework Balsa, which allows modeling asynchronous circuits at an abstract level by hiding the actual handshake implementation, is used. The usability of the Balsa language as well as the associated toolchain for a complex circuit design is to be evaluated. Is the Balsa framework sophisticated enough to design and synthesize an entire asynchronous processor? A further objective of this thesis is to identify the differences in the processor architecture between synchronous and asynchronous processors with identical ISAs. Data and control hazards caused by the asynchronous pipeline architecture require innovative solutions. Data hazards are avoided by an asynchronous forwarding mechanism based on information stored about previous instructions. To resolve control hazards, a coloring algorithm, similar to the one used for AMULET1 and SAMIPS, is implemented. To connect the processor interface to conventional synchronous memory, the handshake signals are transformed to synchronous signals. The Balsa design is synthesized using the quasi delay-insensitive four-phase dual-rail handshake implementation. The synthesized netlist is mapped to UMC's 90 nm technology on which timing simulations are conducted. As synchronization is achieved via the handshake protocol the design adapts to the actual prevailing operating conditions. This results in variable, average-case execution time of individual instructions. Consequently, real-time capability is not evident without an accurate worst-case analysis. The timing simulation results of ASCARTS with Average-Case-Corner synthesis are compared to the results of SCARTS with Worst-Case-Corner synthesis. A key outcome of the presented ASCARTS implementation is the processor description itself, written in a high-level HDL, which is independent of the actual handshake implementation. Therefore, the Balsa description of ASCARTS might be useful for future research of different asynchronous implementation styles.

# Contents

| Contents |                                        |                                             |    |  |  |  |  |

|----------|----------------------------------------|---------------------------------------------|----|--|--|--|--|

| 1        | Introduction                           |                                             |    |  |  |  |  |

|          | 1.1                                    | Motivation                                  | 2  |  |  |  |  |

|          | 1.2                                    | Contribution                                | 3  |  |  |  |  |

|          | 1.3                                    | Outline                                     | 4  |  |  |  |  |

| 2        | Background                             |                                             |    |  |  |  |  |

|          | 2.1                                    | Fundamentals of Asynchronous Logic          | 5  |  |  |  |  |

|          | 2.2                                    | Balsa                                       | 14 |  |  |  |  |

| 3        | State of the Art 2                     |                                             |    |  |  |  |  |

|          | 3.1                                    | AMULET1                                     | 21 |  |  |  |  |

|          | 3.2                                    | AMULET2                                     | 22 |  |  |  |  |

|          | 3.3                                    | AMULET3                                     | 23 |  |  |  |  |

|          | 3.4                                    | SAMIPS                                      | 23 |  |  |  |  |

|          | 3.5                                    | Asynchronous MIPS R3000                     | 23 |  |  |  |  |

|          | 3.6                                    | Lutonium                                    | 24 |  |  |  |  |

| 4        | SCA                                    | ARTS - Basis For The Asynchronous Processor | 25 |  |  |  |  |

|          | 4.1                                    | Processor Architecture                      | 25 |  |  |  |  |

|          | 4.2                                    | Extension Modules                           | 28 |  |  |  |  |

|          | 4.3                                    | Instruction Set Architecture                | 31 |  |  |  |  |

| 5        | ASCARTS - The Asynchronous Processor 3 |                                             |    |  |  |  |  |

|          | 5.1                                    | Processor Interface                         | 34 |  |  |  |  |

|          | 5.2                                    | Processor Architecture                      | 34 |  |  |  |  |

|          | 5.3                                    | Extension Modules                           | 43 |  |  |  |  |

|          | 5.4                                    | Instruction Set Architecture                | 46 |  |  |  |  |

| 6        | Design Flow 5                          |                                             |    |  |  |  |  |

| -        | 6.1                                    |                                             | 51 |  |  |  |  |

|          | 6.2                                    | Synthesis                                   | 53 |  |  |  |  |

|          | 6.3                                    | Structural Simulation                       | 54 |  |  |  |  |

|          |                                        |                                             |    |  |  |  |  |

|              | 6.4                    | Design Implementation | 56 |  |  |

|--------------|------------------------|-----------------------|----|--|--|

|              | 6.5                    | Timing Simulation     | 57 |  |  |

| 7            | Results                |                       |    |  |  |

|              | 7.1                    | Resource Usage        | 59 |  |  |

|              | 7.2                    | Performance           | 60 |  |  |

| 8            | Conclusion and Outlook |                       |    |  |  |

| A            | Test                   | Programs              | 67 |  |  |

| B            |                        | ruction Set           | 71 |  |  |

|              | <b>B</b> .1            | Overview              | 72 |  |  |

|              | <b>B</b> .2            | Notation              | 76 |  |  |

|              | <b>B</b> .3            | Instructions          | 76 |  |  |

| Bibliography |                        |                       |    |  |  |

## CHAPTER

# Introduction

Embedded systems play an important role nowadays. They can be found in many different application fields solving different tasks like monitoring, controlling and processing signals. In the last couple of years especially portable devices gained in importance. The powerful smartphones and tablets are getting an every day part in our lives. The more powerful smartphones as well as tablets are getting more and more popular. The processors of these devices are getting faster, more efficient and more flexible to handle a major variety of tasks. At the same time they are supposed to be more energy-efficient so that the run-time of the batteries does not decrease.

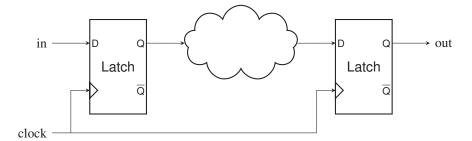

Current processor development is based on synchronous and asynchronous design principles. Synchronous circuit designs rely on a global periodic signal, called clock, to synchronize the data flow. With every clock pulse the results of the combinational logic of all components on the chip are stored in registers, as illustrated in Figure 1.1.

Figure 1.1: Synchronous Circuit

The frequency of the clock has to be chosen in such a way that on all paths signal changes can be propagated in one cycle. The maximum possible clock frequency is determined by the path with the longest propagation delay, the critical path. To accomplish that in any environment, the chip has to be designed for worst-case scenarios, such as worst-case temperature, low voltage supply or process variations.

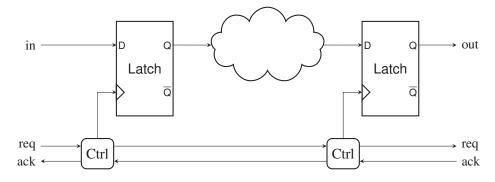

Conversely asynchronous designs are self-timed. Clock signals are replaced by handshakes to control the data flow between adjacent components. Each component signals a request once there is new data to be processed. Likewise it sends an acknowledge signal once it has finished processing the data and is ready to accept new one. See Figure 1.2 for an illustration.

Figure 1.2: Asynchronous Circuit

## **1.1 Motivation**

Synchronous processors dominate the market nowadays. The reason for this dominance is that synchronous designs are simple and well-understood. In addition, all industrial-strength computer aided design tools for design and verification target clocked circuits. Both facts lead to fast development and short design cycles of synchronous processors. In recent technologies, however, the global time assumption becomes a performance and power limiting issue. The different characteristics of asynchronous circuits can be exploited to design circuits which overcome the problematic factors of synchronous circuits [18].

One big disadvantage of synchronous designs is the global clock network. On one hand the network occupies a huge amount of area on the chip. On the other hand it takes a lot of effort to distribute the clock in a way that the skew between different clock signals is minimal. The faster the clocks are, the more difficult it is to route the wires properly, as the margin gets even smaller. On each clock transition the clock network consumes a large amount of power, no matter if the processor is performing useful computations or is in idle state. Furthermore, as all computations start at the clock edge, the most current is drawn at this time and shortly thereafter. This leads to high electromagnetic interferences at the clock frequency. However, in asynchronous designs there is no global clock signal to be distributed. The local clock pulses, derived from handshake signals, are only generated where and when they are needed. Hence, the power and electromagnetic dissipation is lower and the current consumption is more uniformly distributed without spikes, as the signal switching of the individual components is not correlated.

In synchronous designs the operating speed is determined by the critical path. Mapped to processors the operating frequency is as slow as the slowest instruction or stage in pipelined designs, respectively. In contrast, the asynchronous counterparts start immediately with a new computation once the previous one is finished. So the speed of such processors varies over

time and is only as slow as the current instruction or the slowest stage of the current instruction in pipelined designs, respectively. For correct operation in all conditions worst-case timing assumptions have to be made in synchronous designs. This leads to idle times in optimal conditions. However, due to the fact that a handshake protocol is used for synchronization, asynchronous designs adapt to the actual prevailing operating conditions. Because of their insensitivity to delays and their simple handshake interface, asynchronous circuits are rather modular and, hence, have a better composability.

Although replacing synchronous logic by asynchronous logic opens up ways to further improve processor performance, omitting the clock has some drawbacks. The asynchronous control logic induces overheads in area, which again leads to increased power consumption. Besides, the more complex data paths of asynchronous logic have a negative impact on the operating speed.

The complex structures of asynchronous circuits make it more difficult to design and harder to verify or debug them. As there are not any strategies to efficiently develop asynchronous designs there is lack of computer aided design tools, and even the few available ones are not well maintained. The missing tool chain and the extensive know-how required to design such circuits lead to the fact that only few people exist who are able to develop asynchronous processors.

## 1.2 Contribution

The objective of this thesis is the development of the asynchronous processor ASCARTS. It is based on the instruction set of the synchronous processor SCARTS [3]. So far only a design tool was developed at *Vienna University of Technology, Department of Computer Engineering*, which transforms a conventional synchronous circuit description into an asynchronous circuit [12]. However, the resulting asynchronous circuit, generated from the SCARTS design, is not satisfactory. Hence, the manual design of an asynchronous counterpart was demanded.

The development of the processor without any tools implies the design of the underlying handshake protocol as well. To be able to concentrate on the actual processor design, a tool which hides the handshake circuits is used. The decision was made in favor of the open-source project Balsa [4]. It is a high-level synthesis system for asynchronous circuits. A feature of Balsa is that the development of asynchronous circuits is abstracted from the handshake implementation. The actual handshake implementation can be selected during synthesis. This way, the design can be synthesized with different realizations of the handshake protocol. Thus, the effects on the performance with the individual protocols can be observed. Finally a gate-level netlist is generated from the high-level description. This netlist is mapped to UMC's 90 nm technology<sup>1</sup>.

In addition, by designing ASCARTS with the aid of Balsa the usability of such tools for developing asynchronous circuits is to be evaluated.

<sup>&</sup>lt;sup>1</sup>http://freelibrary.faraday-tech.com/

## 1.3 Outline

The second chapter is divided into two parts. First the fundamentals of asynchronous logic are explained. The focus lies on the different ways handshakes can be realized. The second part covers an introduction to Balsa. In the third chapter important asynchronous processors already developed are presented. In the fourth chapter the architecture of SCARTS is summarized. Chapter five gives detailed information about the ASCARTS architecture. Implementation details of the individual units are revealed as well. In chapter six the steps of the design flow are described. Several stages are passed through to obtain the final design description of ASCARTS. In the design process simulations at three different levels are performed. Results achieved from simulations are presented in chapter seven. Finally the findings are summarized and an outlook to future work is given.

# CHAPTER 2

# Background

## 2.1 Fundamentals of Asynchronous Logic

In synchronous circuits a global clock defines points in time where signals are valid and stable. In asynchronous systems control signals have to be valid all the time. Each transition changes the state of the circuit. To avoid hazards and races, additional control logic is needed for synchronization, communication and sequencing of operations [18].

#### 2.1.1 Handshake

Handshaking is used between neighboring components for synchronization or to agree on exchange of data. In general the active party of a handshake-channel initiates the handshake by a *request* signal. The passive party completes the handshake by an *acknowledge* signal.

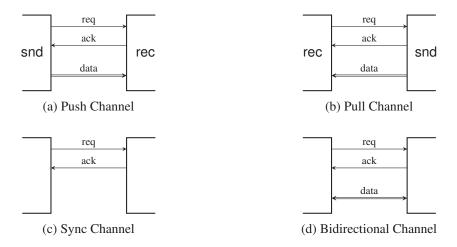

It can be distinguished between different types of channels depending on the direction of data or if data is transmitted at all.

#### **Push Channel**

If the sender is the active party, the sender indicates the capture condition for the receiver with the request signal. Likewise the receiver indicates the issue condition for the sender with the acknowledge signal. The validity of the data is denoted by the request signal. A push channel is illustrated in Figure 2.1a.

#### **Pull Channel**

If the receiver is the active party, the receiver indicates the issue condition for the sender with the request signal. Likewise the sender indicates the capture condition for the receiver with the acknowledge signal. The validity of the data is denoted by the acknowledge signal. A pull channel is illustrated in Figure 2.1b.

#### Sync Channel

Channels without a data path can be used for synchronization. A sync channel is illustrated in Figure 2.1c.

#### **Bidirectional Channel**

A channel where data is transmitted in both directions is illustrated in Figure 2.1d. The data passing from the active party to the passive party acts as a push channel. Hence, the validity is denoted by the request signal. The data passing from the passive party back to the active party acts as a pull channel. Hence, the validity is denoted by the acknowledge signal.

Figure 2.1: Handshake Channels

The handshake establishes a closed loop control for the data flow between two parties. New data is only issued if the previous data is acknowledged and, therefore, captured. On the one hand this makes the circuit timing adaptive. On the other hand this is not fault tolerant as deadlocks occur if data gets lost.

#### 2.1.2 Handshake Styles

The request signal determines the start of one communication cycle, whereas the acknowledge signal determines the end of one communication cycle. There are two approaches how to implement the control protocol. These are presented on the basis of a push channel.

#### **Four-Phase Protocol**

The four-phase protocol uses Boolean levels on the request and acknowledge wires to encode the state of the communication cycle. The term *four-phase* refers to the number of edge transitions on the control wires during one protocol cycle. Figure 2.2a illustrates the four phases of the four-phase protocol for a push channel.

First the sender issues new data and sets request to high. Second the receiver captures the data and sets acknowledge to high. This indicates that data is not needed anymore. In response the sender sets request to low. Data might not be valid anymore. Finally the receiver sets acknowledge to low. A new communication cycle can be initiated by the sender.

This protocol uses level signaling for the control signals. The state of the signals is always known without knowledge of the history. However, the advantage of level signaling comes at the cost of unnecessary time and energy for the return-to-zero transitions of the signals.

#### **Two-Phase Protocol**

In the two-phase protocol each transition on the request and acknowledge wires, irrespective if it is a rising or falling edge, represents a signal event. The term *two-phase* refers to the number of edge transitions on the control wires during one protocol cycle. Figure 2.2b illustrates the two phases of the two-phase protocol for a push channel.

First the sender issues new data and sets request to high. Second the receiver captures the data and sets acknowledge to high. This indicates that data is not needed anymore. At this point data might become invalid. A new communication cycle can be initiated by the sender.

This protocol uses transition signaling for the control signals. The state of the signals is not representative for the state of the handshake protocol. The disadvantage of transition signaling is the more complex implementation as state-holding elements are needed to store the current signal states.

Figure 2.2: Single-Rail Protocol (Push Channel)

#### 2.1.3 Design Techniques

To build control circuits with transition signaling, logic elements that perform logical operations on events are necessary.

#### **Or Element**

The Boolean xor gate acts as the or element for events. When either input of the xor gate changes its state the output also changes its state. Thus, an event received on any input of the xor gate triggers an event on the output. For more than two inputs the parity function acts as the or element for events.

#### **Muller C-Element**

There is no Boolean function that performs an and operation on events. The and gate and the or gate are asymmetric functions regarding the logical level. An or gate immediately propagates a rising transition on a single input to its output, without waiting for a transition on its second input. Likewise, the and gate immediately propagates a falling input transition. Thus, a gate is needed that behaves like an and gate for rising transitions and like an or gate for falling transitions.

Building an and element of combinational gates is not an option. The *Muller C-Element* [16] is a sequential gate and acts as the and element for events. The symbol and the truth table are illustrated in Figure 2.3.

|                                 | a | b | У         |

|---------------------------------|---|---|-----------|

| a                               | 0 | 0 | 0         |

| <sup>∞</sup> <sub>b</sub> C ) y | 0 | 1 | no change |

|                                 | 1 | 0 | no change |

|                                 | 1 | 1 | 1         |

Figure 2.3: Muller C-Element

The *Muller C-Element* is designed in a way that the output only changes its level if both inputs of the element have the same logical level. If the levels differ at the inputs, the element holds the previous level on the output, which is stored internally. Thus, an event is only generated at the output after an event took place on each input. The *Muller C-Element* can be generalized for three or more inputs with the only requirement that all inputs must have the same logical level before the output changes to that level.

This state-holding element is not a conventional gate but rather like a latch. It is an indispensable component when designing asynchronous circuits.

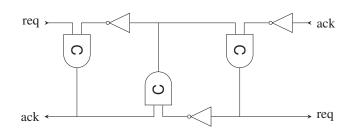

#### Micropipeline

A *Micropipeline* [19, 18] is a circuit built of *Muller C-Elements* and inverters as depicted in Figure 2.4. Request and acknowledge signals are passed between adjacent stages. Observing one stage of the pipeline the request signal of the predecessor is only propagated if the acknowledge signal of the successor is of the opposite level. In other words a stage can only pass the predecessor's request if the previous request is already acknowledged by the successor. Data might also be passed between stages of the *Micropipeline*, but for clearness the data path is omitted in this figure and only the control signals are shown.

The *Micropipeline* is an elastic event-driven pipeline. Without internal processing of data it acts as a first-in first-out memory. Due to its modularity an arbitrary number of stages can be linked together.

There are some remarkable facts about the *Micropipeline* due to its simplicity and symmetry. The handshake style can be four-phase or two-phase. The difference is only in how the signals are

Figure 2.4: Micropipeline

interpreted. The pipeline works from either side, only request and acknowledge signals have to be swapped. The circuit works correctly regardless of the gate delays. It is delay-insensitive.

Because of its powerfulness a *Micropipeline* can be found in all asynchronous circuits as a control circuit.

#### 2.1.4 Timing Models

Asynchronous circuits can be categorized by the employed timing assumptions [11].

#### **Bounded Delay**

In this timing model the delays of all gates and wires must be known or at least bounded. Obviously assumptions on the worst-case operating conditions have to be made. However, constraints on the path delays decrease robustness of a circuit against variations within the manufacturing process. Hence, circuits with bounded delay deliver worst-case performance.

With the use of *Micropipelines* for local handshaking the skew of the individual stages does not add up. Thus, timing assumptions only need to be made locally.

#### **Delay-Insensitive**

In this timing model the delays of all gates and wires are finite but unbounded. As no assumptions on the computation time are made it can handle arbitrary delay. Obviously this realization of a circuit is robust to process variations and interconnect delays. Hence, delay-insensitive circuits deliver average-case performance.

To achieve validity in delay-insensitive circuits, the state of the output of a gate has to be preserved until all inputs are valid. For this purpose only *Muller C-Gates* and single input gates like inverters and buffers are applicable. Thus, a *Micropipeline* is delay-insensitive but circuits with Boolean logic gates are not.

#### **Quasi Delay-Insensitive**

In this timing model the delays of all gates are finite but unbounded. The delays of branches of certain critical wire forks have identical wire delay. These forks are called isochronic forks [18]. The same coding techniques as for delay-insensitive circuits are applicable.

#### 2.1.5 Data path Implementation Styles

The implementation and behavior of a handshake protocol depends on the encoding of the control and data paths. Furthermore, the handshake style, i.e. four-phase or two-phase, has an effect on the protocol. First techniques to achieve validity are described. Then the most common handshake protocols are presented [18].

#### Validity

A bit at the output is valid if the inputs are valid and the output is stable. Validity is either indicated by separate control signals or by codewords. In case of a data bus all bits at the input have to be valid before the data is acknowledged.

Employing the bounded delay model delay elements have to be placed on the control path to assure that the outputs of combinational logic and the inputs of the circuit have settled before they are captured. Validity of datawords is guaranteed by adding an adequate amount of delay elements to match worst-case computation times.

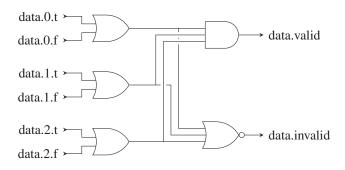

Employing the quasi delay-insensitive model correct circuit behavior is achieved by an appropriate coding technique or data representation. To have an unambiguous valid state in quasi delay-insensitive circuits, no intermediate valid codewords are allowed. To identify a new codeword, successive codewords must be separated by at least one signal transition. Validity of datawords is determined by a separate completion detection circuit.

#### Single-Rail

The term *single-rail* refers to all encodings where the individual data bits are encoded with Boolean values, each on a single wire. All data wires are bundled together accompanied by a separate request and acknowledge signal.

Figure 1.2 shows a circuit with a single-rail protocol. For circuits implementing the single-rail protocol assumptions about the computation time of the combinational logic have to be made. To maintain correct behavior, matching delays in the control path are needed to compensate the delay of the data path in the combinational logic. Refer to Figure 2.5 for a *Micropipeline* with delay elements on the control paths. The control path of the pipeline is quasi delay-insensitive, whereas the data path follows the bounded delay model.

Waveforms that show the behavior of the data and control signals for both four-phase and two-phase handshaking are depicted in Figure 2.2.

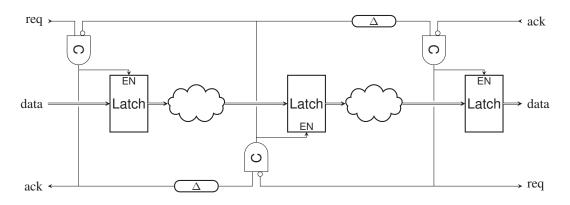

**Four-Phase Single-Rail** An implementation of a single-rail pipeline in combination with a four-phase handshake is illustrated in Figure 2.5. The output signal of a *Muller C-Element* controls the attached latch. When a new request arrives from the predecessor and the the previous request is acknowledged by the successor the latch starts passing the data. Once this stage acknowledges the request to the predecessor the latch is switched to capture mode.

Figure 2.5: Four-Phase Single-Rail Pipeline

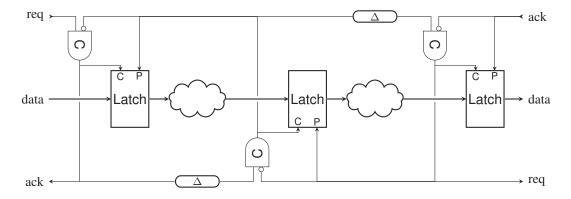

**Two-Phase Single-Rail** As the two-phase handshake implementation is event-driven the latch control must be event-driven as well. For this reason special latches are required. Figure 2.6 depicts a single-rail pipeline in combination with a two-phase handshake. This pipeline can be distinguished from the one with a four-phase handshake by special capture-pass latches along the data path. If an event triggers the C input of the latch it starts to output the captured data. On the other hand if an event triggers the P input of the latch it starts passing the data.

Figure 2.6: Two-Phase Single-Rail Pipeline

#### Multi-Rail

The term *multi-rail* refers to all protocols with combined encoding of data and the request signal accompanied by a common acknowledge signal on push channels. To accomplish combined encoding of data and request, more than two signal states per bit are required. Hence, more than one wire per bit is needed. Likewise, the encoding of data and the acknowledge signal is combined accompanied by a common request signal on pull channels. For convenience, only push channels are explained in greater detail. Pull channels can be derived.

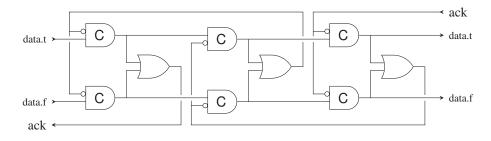

Figure 2.7 shows a 1-bit wide four-phase dual-rail pipeline without data processing. It can

be seen as two *Micropipelines* with a common acknowledge signal. The request wires of the pipelines carry besides the request the data, encoded in a codeword. In this figure one wire is used to represent a logical one, the other wire is used to represent a logical zero. The request is acknowledged when either of the two wires is set to high.

Figure 2.7: Four-Phase Dual-Rail Pipeline

To ensure correct indication in combinational blocks for multi-rail protocols, state-holding elements are required. With the combined encoding of data and the request signal a reliable communication is achieved regardless of gate delays. Due to isochronic forks, which can usually be found in these circuits, the control path as well as the data path of the pipeline are quasi delay-insensitive.

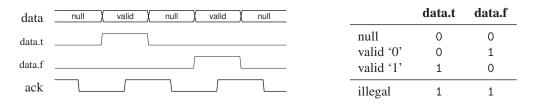

**Null Convention Logic (Four-Phase Dual-Rail)** *Null Convention Logic* is a four-phase protocol using two wires per data bit [6]. One wire is used to represent a logic one, the other wire is used to represent a logic zero. Valid datawords are always spaced with empty codewords. Figure 2.8 illustrates the channel encoding for the *Null Convention Logic* protocol. In this example the code 10 is transmitted.

Figure 2.8: Null Convention Logic Protocol (Push Channel)

There is exactly one transition change for each bit between two valid codewords. For a switch from the empty codeword to a dataword the corresponding wire changes from zero to one. For a switch from a dataword to the empty codeword the corresponding wire changes back from one to zero. Once the completion detector indicates a valid dataword the acknowledge signal is asserted. Since this is a four-phase protocol the empty codeword resets all data wires before another codeword can be transmitted. Hence, the acknowledge signal is only deasserted when all bits are empty.

**Level-Encoded Two-Phase Dual-Rail (LEDR)** *LEDR* is a two-phase dual-rail protocol with level signaling [2]. In the *Null Convention Logic* protocol every second codeword does not carry information. An alternative solution is to use two codewords for each logic value, each of them belongs to a different phase. To distinguish consecutive datawords, the corresponding codewords have alternating phases. Figure 2.9 illustrates the channel encoding for the *LEDR* protocol. In this example the code 11000 is transmitted. As can be seen from the example the throughput of a circuit with *LEDR* encoding is twice as high as for circuits with *Null Convention Logic* encoding.

Figure 2.9: Level-Encoded Two-Phase Dual-Rail Protocol (Push Channel)

The codewords are chosen in a way that all codewords of the other phase are reached by exactly one transition. An encoding for the *LEDR* protocol can be seen in Figure 2.9. Completion detection works similarly as for *Null Convention Logic*.

**Transition-Encoded Two-Phase Dual-Rail** A two-phase dual-rail protocol can also be implemented with transition signaling. Each transition represents a codeword. Figure 2.10 illustrates the channel encoding for a *Transition-Encoded Two-Phase Dual-Rail* protocol. In this example the code 1001 is transmitted.

Figure 2.10: Transition-Encoded Two-Phase Dual-Rail Protocol (Push Channel)

The current state of a codeword depends on the previous transitions. Thus, it is not visible but must rather be stored in state-holding elements. This is problematic for the identification of consistent datawords. Likewise it is difficult to implement a transition-based completion detection.

## 2.2 Balsa

For designing asynchronous circuits that are only synchronized by handshake communications a special development environment is of advantage. Conventional tools for design and verification are tailored to the clocked approach. As asynchronous development is not widely spread not many design tools optimized for asynchronous circuits are available. The development environment of choice for implementing ASCARTS is the open-source project Balsa, which was developed at the *APT group of the School of Computer Science, The University of Manchester*. This section gives an overview over Balsa. For a more detailed description see [4].

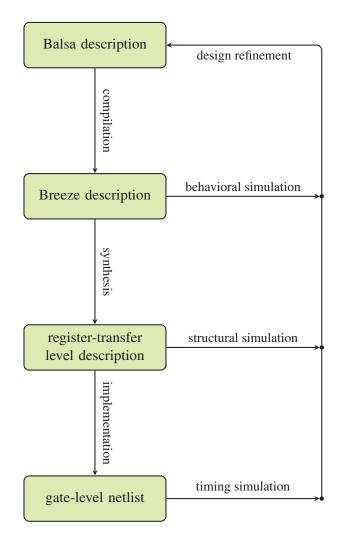

Balsa is a language for describing asynchronous hardware systems as well as a framework for developing such systems. A key feature of the language is transparent compilation. There is a one to one mapping between language constructs and intermediate handshake circuits. The advantage of this approach is that incremental changes in the code result in predictable changes in the generated circuits.

The Balsa framework comprises a collection of tools. The most important ones are listed in Table 2.1.

| balsa-c       | compiles Balsa files into intermediate Breeze description |

|---------------|-----------------------------------------------------------|

| breeze-sim    | behavioral simulator for Breeze files on handshake level  |

| balsa-netlist | produces a netlist from Breeze description                |

Table 2.1: Balsa Tools

Balsa is a strongly typed language, hence, all casts have to be explicit. The only exception to this are implicit casts of numeric types to wider numeric types. Thus, special care has to be taken with arithmetic operations.

The language supports modular compilation to realize a library mechanism. With the import statement precompiled Balsa components, i.e. Breeze design files, can be included into the current Balsa design file allowing component reuse.

#### 2.2.1 Control Flow

In this section Balsa or rather asynchronous specific language constructs are explained in more detail and are illustrated by examples. For conventional constructs, which might be familiar, refer to [4].

**Sync** Control only handshake channels communicate via sync commands. Both ends have to signal a sync request to successfully complete the handshake. In Listing 2.1 first the handshake on the sync channel i is completed. Afterwards a handshake on the sync channel o is initialized.

```

procedure sync_buffer (

sync i ;

sync o

)

is

begin

loop

sync i

;

sync o

end

end

```

Listing 2.1: Sync Buffer

**Channel Assignment** The operators  $\rightarrow$  and  $\leftarrow$  are channel assignment operators implying a handshake data transfer over that channel.  $\rightarrow$  assigns the data read from the input channel to a variable or an output channel and completes the handshake.  $\leftarrow$  assigns data to an output channel from a variable or expression and initializes the handshake. Each channel has exactly one input and one output port. Hence, passing a signal to several procedures is not possible as used to from conventional languages. For each procedure a separate channel is needed with explicit signal assignment. In Listing 2.2 first the data from the input channel i is assigned to x and simultaneously the handshake on that channel is completed. Afterwards the data from x is written to the output channel o and simultaneously a handshake on that channel is initialized.

The operator := assigns the result of an expression to a variable. In Listing 2.3 data of x is transferred to y. The transfer is implicitly performed by a handshaking communication channel. Hence, y := x can also be written as  $ch \leftarrow x \parallel ch \rightarrow y$ .

```

import [balsa.types.basic]

import [balsa.types.basic]

procedure single_place_buffer (

procedure two_place_buffer (

input i : byte;

input i : byte;

output o : byte

output o : byte

)

)

is

is

variable x : byte

variable x, y : byte

begin

begin

loop

loop

i -> x

i -> x

11

0 <- x

o <- y

y := x

end

end

end

end

```

Listing 2.2: Single-Place Buffer

Listing 2.3: Two-Place Buffer

**Sequencing** The ; operator connects two statements or blocks sequentially. A sequence operator is used in Listing 2.2. First the input channel i is read. Once the handshake on that channel is completed it is written to the output channel o.

**Parallel Composition** The || operator connects two statements or blocks concurrently and independently. Both commands must be completed before processing the subsequent command or commands. This operator has precedence to the sequence operator. A parallel composition operator is used in Listing 2.3. Reading the input channel i and writing to the output channel o occurs concurrently. Once the handshakes on both channels are completed the value of x is copied to y.

**Choice** For situations where a handshake may occur only on one channel out of several a multiplexer is needed. In the Balsa language self-selecting multiplexer is available for this purpose. This operator waits for a handshake request on any of the channels. Once a handshake initialization is detected the block associated with the selected channel is processed before the handshake on that channel is acknowledged. This is a type of handshake enclosure which is described in more detail in Section 2.2.3.

In Listing 2.4 the select operator is used to choose between input channel i and input channel j. The system design must ensure that handshakes on the channels in a select statement never occur simultaneously.

For truly independent channels another choice operator arbitrate is available. As with nondeterministic choices the possibility of entering metastability arises, additional hardware is needed to avoid or resolve that state. Due to this overhead arbiters are expensive in both area and speed. Hence, the arbitrate statement should only be used if really necessary. In Listing 2.5 the arbitrate operator is used to choose between input channel i and input channel j. If a handshake request arrives on both channels simultaneously the order in which the corresponding blocks are processed is not deterministic.

Both choice operators can be used for control only channels as well as channels transferring data or a mixture of both. In Listing 2.4 a choice operator is applied to data bearing channels, whereas in Listing 2.5 a choice operator is applied to dataless channels.

#### 2.2.2 Design Structure

A design consists of several files containing procedures, type and constant declarations. If several procedures are defined in the top-level design file the bottom one is taken as main procedure.

Additionally, to the previous mentioned declarations a procedure can also have local variable and channel declarations. The scope of each declaration starts at the point of declaration and ends at the end of the enclosing block. If a declaration within an enclosed block uses the same name as a previously made declaration in the enclosing context, the outer declaration is hidden until the end of the enclosed block.

```

import [balsa.types.basic]

procedure choice (

procedure arbitrated_choice (

input i : byte;

sync i;

input j : byte;

sync j;

sync o

output o : byte

)

)

is

is

begin

begin

1000

loop

select i then

arbitrate i then

o <- i

sync o

j then

i then

o <- j

sync o

end

end

end

end

end

end

```

Listing 2.4: Non-Arbitrated Choice

Listing 2.5: Arbitrated Choice

**Shared Procedures** Each instantiation of a procedure induces separate hardware. If the calls to a procedure are mutually exclusive the individual instantiations can share their hardware. For these cases Balsa provides shared procedures. Calls to such procedures access common hardware, hence, multiplexers are needed to coordinate the access. In Listing 2.6 a counter with the possibility to change the direction is implemented. In the design two adders are instantiated, one used for incrementing the register and one used for decrementing the register. As the adders are not used concurrently in Listing 2.7 the design is rewritten to share a single adder.

**Parameterized Procedures** Procedures can be parameterized to be used as generic library components with varying parameter types. No hardware is generated for parameterized procedures until it is instantiated with defined parameters. In Listing 2.8 a buffer definition with generic input and output types is given. Aliasing of procedures with defined parameters, see last line of Listing 2.8, is optional. Instead of calling the aliased procedure byte\_buffer(i, o) a call to the procedure could also be generic\_buffer(byte, i, o).

#### 2.2.3 Handshake Enclosure

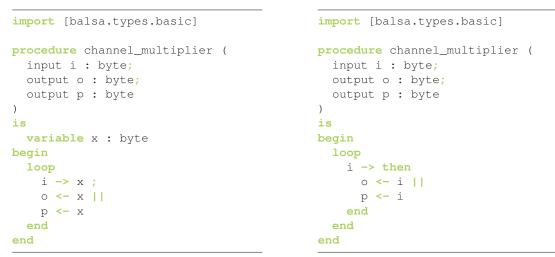

With channel assignments in Balsa once the data is consumed the handshake is completed and the data may be removed from the channel. Hence, if the data is required more than once it has to be stored in a variable. Listing 2.9 shows a channel multiplier. The data of input channel i has to be stored in a temporary variable as it is needed twice. To avoid temporary variables, Balsa provides two constructs where the handshake is held open until a sequence of commands is processed. One possibility is the select statement as used in Listing 2.4. If there is no choice necessary an alternative command is provided as used in Listing 2.10. In this listing the  $\rightarrow$  operator is used to hold the handshake on input channel i open. Using these constructs the channel acts like a variable in the enclosed block.

```

import [balsa.types.basic]

import [balsa.types.basic]

procedure counter (

procedure counter (

input direction : bit;

input direction : bit;

output count : byte

output count : byte

)

)

is

is

variable tmp_direction : bit

variable tmp_direction : bit

variable reg : byte

variable reg : byte

variable inc : 2 signed bits

shared adder is

begin

reg := (reg + inc as byte)

end

begin

begin

loop

loop

direction -> tmp_direction ;

direction -> tmp_direction ;

if tmp_direction then

if tmp_direction then

inc := 1 ;

reg := (reg + 1 as byte)

adder()

else

else

inc := -1 ;

reg := (reg - 1 as byte)

adder()

end ;

end ;

count <- reg

count <- reg

end

end

end

end

```

Listing 2.6: Counter

Listing 2.7: Counter with Shared Adder

```

import [balsa.types.basic]

procedure generic_buffer (

parameter X : type;

input i : X;

output o : X

)

is

variable x : X

begin

loop

i -> x ;

o <- x

end

end

procedure byte_buffer is generic_buffer(byte)</pre>

```

Listing 2.8: Generic Buffer

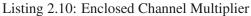

Figure 2.11 shows the circuit behavior without handshake enclosure and the circuit behavior with enclosed handshake. The waveform in the figure shows a four-phase protocol. Green logical 1 denotes an active request and red logical x denotes an active acknowledge. Green logical 0 represents a removed request and with blue logical z the acknowledge is removed as well. Comparing the two traces reveals the difference in behavior for these two approaches. The advantage of enclosed handshakes is that the channel can be read several times, even zero times, without deadlocking and at the same time avoiding internal latches for storing the data. On the other side the performance decreases because the handshake completion is delayed. Hence, the data provider is locked and cannot continue processing independently.

Listing 2.9: Channel Multiplier

Figure 2.11: Waveform of Channel Multipliers

#### 2.2.4 Simulation

For simulation purposes additional built-in types and functions are available originally defined in C. Built-in types represent pointers to BalsaObject structures, which can be used as parameters, ports and variables. However, arithmetic functions cannot be applied to them.

Built-in functions for generating and manipulating String objects as well as for string conversion are available. For file access the built-in object type File and associating functions which operate on that type are provided. To simulate memory, a library with the built-in type BalsaMemory and built-in functions for reading from and writing to that object exist. In addition, a Balsa procedure

#### 2. BACKGROUND

with a read and write port implementing the memory access logic is provided by the library. An in-depth description of the built-in library types and functions can be found in [4].

# CHAPTER 3

# State of the Art

This chapter gives an overview of the most important asynchronous processors.

At *The University of Manchester* three versions of an ARM-compatible microprocessor were developed, AMULET1 [22], AMULET2 [8], AMULET3 [9]. Asynchronous implementations of the MIPS R3000 processors were developed at *The University of Birmingham* [23] and at *California Institute of Technology* [13], respectively. At the *California Institute of Technology* Lutonium [14], an asynchronous 8051 microcontroller, was also developed. An asynchronous 80C51 microcontroller [20] was developed at *Eindhoven University of Technology* and *Philips Research Labs*. This processor is, however, not presented in this chapter.

## 3.1 AMULET1

AMULET1 [22] is an asynchronous processor based on the *ARMv3* microprocessor architecture. It was developed using an approach derived from Sutherland's *Micropipelines* [19]. Unusual properties comprise non-deterministic, but bounded, prefetch depth beyond a branch instruction, a data dependent throughput and a novel register locking mechanism.

The architecture consists of four major functional units, the *Address Interface, Register Bank, Execute* unit and *Data Interface*. These operate concurrently and asynchronously, synchronizing with each other only to exchange data. Instruction stream *coloring* is used for discarding an uncertain number of prefetched instructions from the interrupted instruction stream. Whenever the instruction stream terminates the color of the instruction is changed. By checking the color at the decode stage and at the ALU result stage wrongly prefetched instructions and their results can be identified and discarded. A failing memory access on instruction fetch only causes a trap to be entered for instructions actually required, i.e. if the color matches. To handle read and write operations correctly in an asynchronous environment, the register bank uses *FIFO Lock Registers* [17] for pending write backs. Separate ones are used to lock registers subjected to memory writes and ALU writes, respectively.

As implementation style the two-phase single-rail protocol was chosen. However, instead of capture-pass latches conventional latches are used. Thus a conversion from two-phase protocol to four-phase protocol as well as the back conversion is needed.

The chip was developed with the aid of conventional synchronous tools using a conventional design flow. For high-level simulation a proprietary simulator from ARM Limited was used. Transistor level simulation and all layout was performed with commercial VLSI CAD tools. In addition software was developed, which checks the validity of data bundles of the single-rail protocol between request and acknowledge signals. The components for the data path are primarily fully customized, whereas for control logic the layout consists mostly of compiled standard cell circuits.

## **3.2 AMULET2**

AMULET2 [8] is an enhanced version of AMULET1. Analysis of AMULET1 revealed that the pipeline depths are too large. Some stages hardly increase performance but cost area and power dissipation. Others even decrease performance. With regard to these aspects the pipelines were reorganized. To avoid pipeline stalls when a register dependency is detected, *last result* registers are used to emulate register forwarding. The latter one is only reasonable in synchronous design as it relies on pipeline synchronization. Separate *last result* registers are used for the ALU, which is used when the result calculated by the ALU is required as an operand, and the memory, which is used when the operand being loaded from the memory is required. Only the results of instructions with the *always* guard, i.e. instructions that are unconditionally executed, are forwarded to be sure that the value will become available. AMULET2 employs a *Branch Target Cache* to predict the target of the next branch instruction. It is a static branch predictor that caches the addresses and targets of the 20 recently taken branch instructions. AMULET2 detects instructions that branch to themselves as *halt* instructions and triggers a mechanism to stall the processor.

As implementation style the four-phase single-rail protocol was adopted. In AMULET1 many two- to four-phase conversions were needed for pipeline registers and dynamic logic. Besides, the implementation of two-phase control elements was inefficient.

The chip was developed with off-the-shelf commercial EDA tools and design libraries, which are optimized for synchronous designs. For high-level simulation a proprietary simulator from ARM Limited was used. Several potential deadlocks were found early in the design cycle by varying the delays of gates within the asynchronous control paths. Many of the asynchronous control circuits were synthesized using a specific asynchronous logic tool, Forcage. The data path and most of the cache is fully customized. However, large amounts of the control logic were compiled from standard cells supplemented with physically compatible cells.

## **3.3 AMULET3**

AMULET3 [9, 10] is the third generation of asynchronous ARM-compatible microprocessors. It is based on the ARMv4T microprocessor architecture including full compliance with the 16-bit thumb instruction set.

The instruction port fetches 32-bit words unless it is known that only one half-word is needed when operating in thumb mode. As the pipeline is elastic and units are only invoked when needed by the instructions, the pipeline's depth varies. Some instructions may be discarded already before the execution stage. Others may be expanded into multiple cycles inside the pipeline. Instruction stream *coloring* is used for discarding prefetched instructions in a similar way as in earlier AMULET processors. However, in AMULET3 the instructions are already discarded in the decode stage. This adaption leads to power reduction as registers are not read unnecessarily.

The instruction prefetch unit comprises some novel features. Instructions that branch to themselves are reinterpreted as *halt* instructions. On execution this causes the prefetch unit to stop, which, in turn, stops the asynchronous subsystem. AMULET3 employs a *Branch Target Buffer* with 16 entries. It provides all the information contained in the instruction. Therefore, instruction fetch is suppressed. This leads to faster instruction delivery and less power consumption.

As the previous AMULET processors the implementation is based on an asynchronous micropipeline structure using four-phase control signals. Balsa was used to implement parts of the DMA controller, which is included in the AMULET3i microprocessor subsystem.

## 3.4 SAMIPS

SAMIPS [23] is an asynchronous processor core based on the MIPS R3000 architecture. Its pipeline consists of five stages, the *Instruction Fetch*, *Instruction Decode*, *Execution*, *Memory Access*, *Register Write Back*. The control signals are generated in the instruction decode stage and then bundled together with the data and passed through the pipeline. To avoid data hazards, an asynchronous register forwarding mechanism was developed based on history information. An extended version of the *coloring* mechanism of the one used in AMULET1 is used for discarding prefetched instructions. The color of the instructions as well as of the processor change every time a control hazard occurs. Instructions are only executed if the color matches that of the processor.

SAMIPS was modeled in Balsa. For behavioral simulation LARD, a hardware description language for describing asynchronous systems [5], was used. The memory model for the simulation was also written in LARD. LARD is able to detect deadlocks by terminating the simulator when a deadlock occurs with subsequent channel activity analysis.

## 3.5 Asynchronous MIPS R3000

An asynchronous MIPS R3000 processor [13] was developed to optimize the average cycle time and the average energy per instruction. By minimizing  $Et^2$  both high speed at high voltage and low power at low voltage can be achieved. MIPS R3000 was chosen because it is the archetype of a commercial RISC microprocessor. However not the complete MIPS was implemented.

The processor consists of two distinct parts, the fetch loop, consisting of the *PC* unit, the *Fetch* and the *Decode*, and the execution pipeline, consisting of the execution units, register unit and *Write Back*. All execution units operate in parallel and can execute different instructions concurrently. The whole design is very finely pipelined.

To determine the sequence of canceled instructions for precise exceptions, the decoder maintains a queue of unit numbers that represent the order of the dispatched instructions. The central mechanism for exception handling is the write back unit. It sends a discard message to the register unit if the instruction was canceled. The PC unit generates a bit, which signals the write back unit that the instruction stream is valid again. A pseudo-instruction is inserted into the instruction stream before the first instruction of the exception handler, which requests to store the information about the exception. The register unit has two result buses, which are used alternately to reduce pipeline stalls. The processor has two caches. The cache core is pipelined internally allowing two look-ups to proceed concurrently. When a cache miss occurs the handshake between the cache and the main pipeline is stretched making the latency variations transparent to the rest of the system.

This processor is quasi delay-insensitive using four-phase control signals. The data is encoded using 1-of-N and dual-rail codes.

## 3.6 Lutonium

Lutonium [14] is an asynchronous 8051-architecture microcontroller. It is designed for low Et<sup>2</sup>, the best trade-off between energy and cycle time. The choice of the 8051 ISA is justified by the fact that it is the most popular microcontroller. On the other hand, though, it is a complex and irregular instruction set that tends to increase the energy consumption.

For energy efficiency, switching activity is minimized. No register or execution unit receives control unless it will process data. Nothing is computed or routed unless necessary. Thus the pipeline is non-speculative. It is filled by the instruction fetch unit with instructions only if these are definitely going to be executed. Therefore, cycles executing interrupt requests or branches are stretched. For energy and time savings implicit operands and special registers have their own channels. As instruction Fetch is the limiting part of the design two consecutive bytes of code are fetched simultaneously. Even though that introduces some speculation if the last byte of a basic block happens to fall on an even address, the speed advantage compensates the energy costs. To not make the optimizations pointless, direction registers were added to the peripheral interfaces so that passive pull-ups are not required.

Lutonium is quasi delay-insensitive using four-phase control signals. The processor description is composed of concurrent *Communicating Hardware Processes* [15].

## CHAPTER 4

## **SCARTS - Basis For The Asynchronous Processor**

SCARTS is an abbreviation for Scalable Computer Architecture for Real-Time Systems. It is a synchronous processor developed and actively maintained at *Vienna University of Technology*, *Department of Computer Engineering*. This processor was specifically designed as a soft-core processor for embedded systems with real-time requirements. To fulfill these requirements, the processor has to be adaptable and real-time capable [3]. Adaptability is accomplished by the usage of extension modules to extend the functionality of the processor. Real-time capability is achieved by constant execution time of all instructions, even if a conditional instruction is not executed, and deterministic behavior of interrupt execution.

The features that are adopted for the implementation of ASCARTS are described in more detail. For other information about SCARTS refer to [7, 21].

#### 4.1 Processor Architecture

SCARTS is a RISC<sup>1</sup> processor with a 16-bit address bus and a customizable data path. The data path can be switched between 16-bit for small processor cores used for FPGAs with little resources and 32-bit for improved performance and higher storage capacity due to 32-bit addresses. Figure 4.1 shows the block diagram of SCARTS. The processor has four pipeline stages. These are *Instruction Fetch*, *Instruction Decode*, *Execute* and *Write Back*. Data hazards are resolved by the usage of a register forwarding unit. Control hazards are also resolved in hardware. These mechanisms keep programs simple and worst-case execution times rather predictable.

The register file has 16 registers, whereof two are special purpose registers. In addition four frame pointers are available.

<sup>&</sup>lt;sup>1</sup>RISC, Reduced Instruction Set Computing, is a load/store architecture.

Figure 4.1: Block Diagram of SCARTS

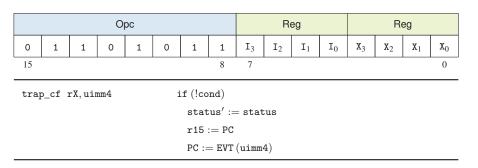

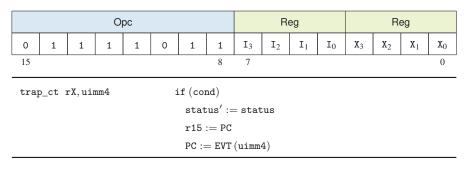

SCARTS supports 32 exceptions, 16 of which are hardware triggered interrupts and 16 are software triggered traps. The exception vector table is stored in a separate memory. The instruction set provides special instructions to build and to manipulate the exception vector table.

To get high flexibility, the processor can be extended by extension modules, which are mapped to data memory address space. The processor status and the interrupt handling logic are controlled by the processor control module. Therefore, it is obligatory to include that module for correct processor operation. For a detailed description of extension modules see Section 4.2.

A sleep mode is provided for power saving. Once the processor is in sleep mode it only wakes up if an interrupt is triggered.

#### 4.1.1 Memory Architecture

The memory architecture of SCARTS is a *Harvard Architecture*, i.e. instruction memory and data memory are two separate physical memories with independent signal buses. The instruction memory uses word access since instructions are read as words. As far as the data memory is concerned a byte access memory organization was implemented. The byte ordering of this memory is little endian. Memory accesses have to be aligned.

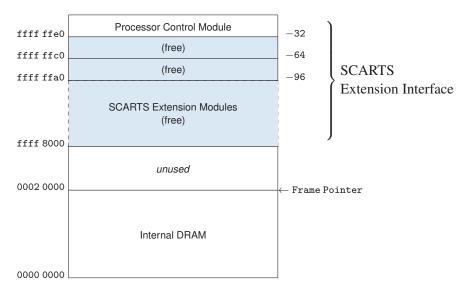

The physical interface of extension modules is also mapped into data memory. Each module allocates 32 bytes of the memory starting at the top of the memory. The size of the internal dynamic memory is configurable as well as the address space reserved for extension modules. The default memory mapping of SCARTS' data memory with a 32-bit configuration can be seen in Figure 4.2. The extension module interface is mapped to the top of the address space. The processor control module is by default mapped to the slot with the base address of -32. All frame pointers point to the top of the internal dynamic memory on program start-up.

Addressing modes of an architecture define how the physical instruction operand addresses in the memory are calculated by a processor [21]. The memory addressing modes supported by

Figure 4.2: Data Memory Address Space for 32-bit Configuration

SCARTS are presented in Table 4.1.

| Mode                          | Description                                      | Instruction<br>Memory   | Data<br>Memory          |

|-------------------------------|--------------------------------------------------|-------------------------|-------------------------|

| Absolute<br>Register Indirect | address constants<br>address values in registers | $\overline{\checkmark}$ | $\overline{\checkmark}$ |

| FP-Relative                   | displacement value added to frame pointer        |                         | $\checkmark$            |

| PC-Relative                   | displacement value added to pro-<br>gram counter | $\checkmark$            |                         |

Table 4.1: Memory Addressing Modes

#### 4.1.2 Register File

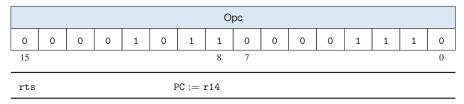

The register file consists of 16 registers. All registers, r0 to r15, are accessible from all instructions. Two registers, r14 and r15, additionally have special functionality. The return address after a subroutine call is saved to the rts register, mapped to r14. The rte register, mapped to r15, holds the return address in case of an interrupt. For nested subroutine calls and interrupts the appropriate register has to be saved manually.

#### 4.1.3 Frame Pointers

The SCARTS processor provides four frame pointers to control four different frames. Frames are similar to stacks. The difference, however, is that data can be stored to and read from frames in

arbitrary order by specifying an offset to the frame pointer. Due to 6-bit offset values 64 words can be addressed from one frame pointer as only word access is allowed.

With post-increment and post-decrement frame pointer access instructions auto-increment and auto-decrement functionality is supported. As the address space of frames expands from the top to the bottom by recommendation pop can be easily realized with a post-increment instruction and an offset of 0. On the other hand, push needs pre-decrement functionality, which has to be simulated by a post-decrement instruction with an offset of -1.

#### 4.2 Extension Modules

SCARTS can be adapted for different requirements by integrating extension modules. To keep the usage of different modules simple and consistent, a common interface was designed. Each extension module is accessed through 32 bytes irrespective of the data path size. The interface is mapped with the module's base address into data memory. Thus, no additional instructions are required as conventional memory instructions can be used.

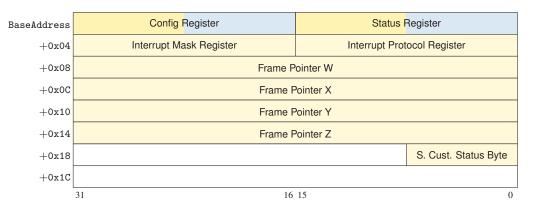

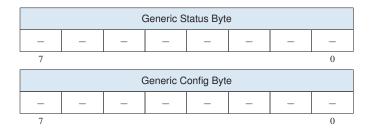

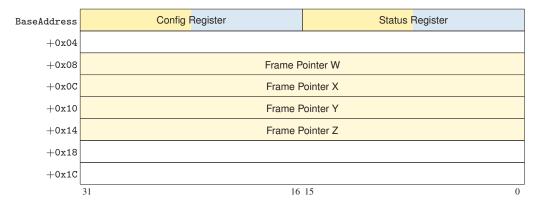

The first two bytes of the interface define the status register, which is read-only. The subsequent two bytes form the configuration register for the module. Each of these two registers is split into a generic part and a custom part. The generic low byte of the status register and the generic low byte of the configuration register define the common interface to the extension modules. The high bytes of both registers as well as the other 28 bytes can be used module specific. In Figure 4.3 the register interface specification of extension modules is depicted.

| BaseAddress | Config Register | Status Register |

|-------------|-----------------|-----------------|

| +0x04       | Data Re         | gister 0        |

| +0x08       | Data Re         | gister 1        |

| +0x0c       | Data Re         | gister 2        |

| +0x10       | Data Re         | gister 3        |

| +0x14       | Data Re         | gister 4        |

| +0x18       | Data Re         | gister 5        |

| +0x1c       | Data Re         | gister 6        |

|             | 31 16           | 15 0            |

Figure 4.3: Register Interface for Extension Modules

Figure 4.4 shows the generic parts of the status register and the configuration register. The register description of these registers is listed in Table 4.2 and Table 4.3. The functionality for these bytes has to be implemented together with the customized part for each module.

#### 4.2.1 Processor Control Module

The processor control module is essential for the processor and, hence, cannot be omitted. It contains the processor status register, the frame pointers, is responsible for controlling exceptions

| Generic Status Byte |                  |   |      |      |      |    |      |  |  |  |

|---------------------|------------------|---|------|------|------|----|------|--|--|--|

| LOOR                | FSS BUSY ERR RDY |   |      |      |      |    |      |  |  |  |

| 7                   |                  |   |      |      |      |    | 0    |  |  |  |

| Generic Config Byte |                  |   |      |      |      |    |      |  |  |  |

| LOOW                | _                | _ | EFSS | OUTD | SRES | ID | INTA |  |  |  |

| 7                   |                  |   |      |      |      |    | 0    |  |  |  |

Figure 4.4: Generic Status and Configuration Byte

- INT The *Interrupt* bit is set if an interrupt was triggered by the module.

- RDY The *Ready* bit indicates that the module is ready to operate.

- ERR The *Error* bit is set if an error occurred.

- BUSY The *Busy* bit indicates that the module is not ready for new tasks.

- FSS The *Fail-Safe-State* bit can be set by the module or by the *Enter-Fail-Safe-State* bit of the configuration register and indicates that the module is in the fail-safe-state.

- LOOR The *Loop-Read* bit shows the *Loop-Write* bit of the configuration register with one cycle delay. It is used to determine the presence of a module.

Table 4.2: Generic Status Byte

- INTA The *Interrupt Acknowledge* bit acknowledges the interrupt and clears the *Interrupt* bit in the status register.

- ID If the *Identify* bit is set, manufacturer and version number can be read from data register 0.

- SRES The *Soft-Reset* bit triggers a software reset of the module.

- **DUTD** The *Output-Disable* bit disables the module.

- EFSS If the *Enter-Fail-Safe-State* bit is set, the module enters the fail safe state.

- LOOW The *Loop-Write* bit is shown as *Loop-Read* bit of the status register with one cycle delay. It is used to determine the presence of a module.

Table 4.3: Generic Configuration Byte

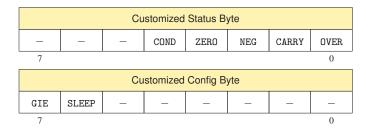

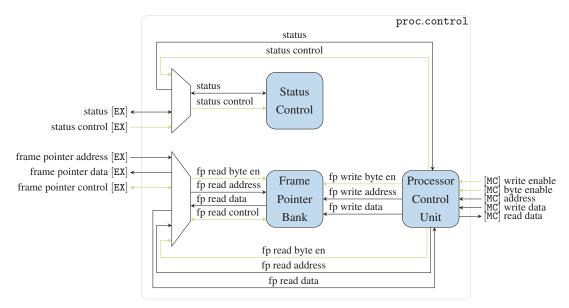

and activates the sleep mode. In Figure 4.5 the register interface of the processor control module is depicted. Figure 4.6 shows the register description of the customized parts of the status register and the configuration register.

Figure 4.5: Register Interface for Processor Control Module

Figure 4.6: Customized Status and Configuration Byte of Processor Control Module

The customized status byte comprises the status flags of ALU<sup>2</sup> operations. These flags are *Overflow*, *Carry*, *Negative*, *Zero* and *Condition*. The customized configuration byte provides the *Global Interrupt Enable* bit and the *Sleep* bit to put the processor into sleep mode. The customized status byte is saved to the *Saved Customized Status Register* upon an exception occurrence and restored from it after the execution of the interrupt handler.

In case of a reduced-16-bit data path the upper 16 bits of the frame pointer registers are unused. The frame pointer registers are described in Section 4.1.3.

**Interrupts** For enabling interrupts globally the GIE bit of the customized configuration register has to be set. To disable interrupts individually, a mask bit for each of the 16 interrupts is provided in the *Interrupt Mask Register*. The *Interrupt Protocol Register* captures incoming interrupts. The corresponding bit number is set until the interrupt service routine is executed or it is cleared by the programmer.

<sup>&</sup>lt;sup>2</sup>The Arithmetic and Logic Unit is a component in a processor that performs arithmetic and logical operations.

#### 4.3 Instruction Set Architecture

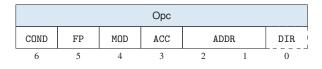

The SCARTS instruction set comprises 122 instructions of which 48 are conditional. All instructions have a fixed length. They are encoded in 16-bit words, which reduces hardware complexity. They have a constant execution time of one clock cycle per instruction, which is an important feature for real-time capability. As only 16-bit instructions are used there was not enough scope to design an instruction set with a consistent structure. Therefore, the length of opcodes and immediate values vary.

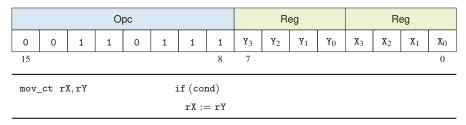

#### 4.3.1 Conditional Instructions

Besides conditional jumps, the instruction set also comes with conditional arithmetic and logic instructions. These instructions test the condition flag in the status register, which is set or cleared by compare and test instructions, respectively. If the condition applies the instruction is executed else it is replaced by a nop instruction. Thus, with the support of conditional instructions the execution time of programs is constant and independent of data. Hence, the worst-case execution time can be calculated easier. For small conditional sequences the execution time is even shorter, compared to conventional sequences, as no jumps and pipeline flushes are required.

## CHAPTER 5

## ASCARTS - The Asynchronous Processor

The asynchronous processor was developed to be compatible with the toolchain used for the synchronous counterpart. Hence, it is named ASCARTS, which stands for Asynchronous **SCARTS**. In order to achieve this most of the just introduced features of SCARTS have been adopted for the implementation of ASCARTS.

As the asynchronous design style is quite different from the synchronous one, differences in the architecture are inevitable. Recall that in asynchronous designs the execution time varies depending on the instruction and its operands. Thus, worst-case execution time has to be calculated with greater expense, which in turn weakens the feature of real-time capability. The design of this processor is platform-independent. The ASCARTS can be used as a soft-core processor for FPGAs<sup>1</sup>, or the design is synthesized with a library for ASICs<sup>2</sup>. The latter will result in a more efficient design in terms of area, power and performance as most of the FPGAs are not designed for implementing asynchronous circuits.

Besides the asynchronous design-related modifications, other decisions are changed as well. The customizable data path was not implemented in that way again. Only a 32-bit data path is available anymore. The 16-bit version was omitted as experience showed that the performance gain is disproportionate to the additional hardware resources used, especially because modern FPGAs provide enough resources. However, the instructions are still 16-bit words. The instruction set architecture was refined as well to facilitate the decoding process.

To keep the work within reasonable limits, the processor control module was slimmed down to the indispensable parts for the processor. Besides the exceptions, the sleep mode, which is provided for power saving in the synchronous processor, was omitted. The justification for implementing

<sup>&</sup>lt;sup>1</sup>A Field Programmable Gate Array is an integrated circuit that can be programmed after manufacturing.

<sup>&</sup>lt;sup>2</sup>A Application-Specific Integrated Circuit is an integrated circuit that is customized for a particular application.

the sleep mode in SCARTS is the high power consumption while the processor is idle. Due to the asynchronous logic design this justification is no longer met in ASCARTS. The optional extension modules have not yet been implemented either as their functionality is not sufficiently relevant for an asynchronous prototype of SCARTS.

#### 5.1 **Processor Interface**

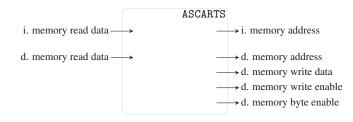

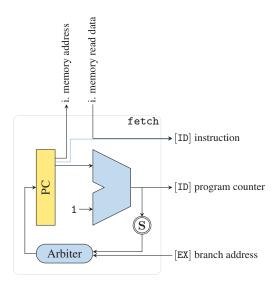

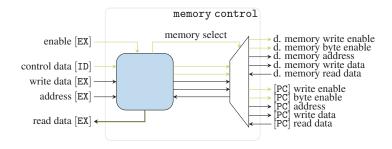

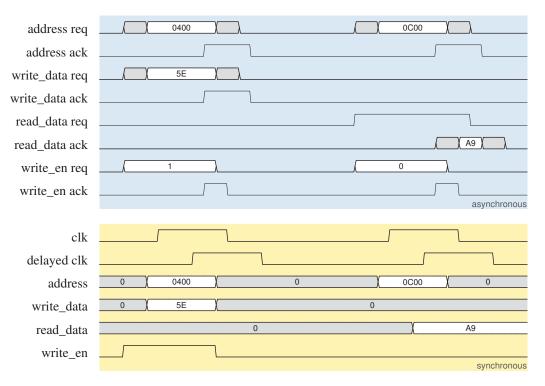

The interface of ASCARTS basically consists of the interfaces to the instruction memory and data memory, respectively. The data memory interface consists of the read data input signal and the address and write data output signals. Additionally, it includes the two control signals write enable and byte enable. The instruction memory interface has only the read data input signal and the address output signal. As this memory is read only no write data and write enable signals are needed. The byte enable signal can also be omitted as always the whole instruction word is read in ASCARTS. The interface of ASCARTS is depicted in Figure 5.1.

Figure 5.1: ASCARTS Interface

#### 5.2 **Processor Architecture**

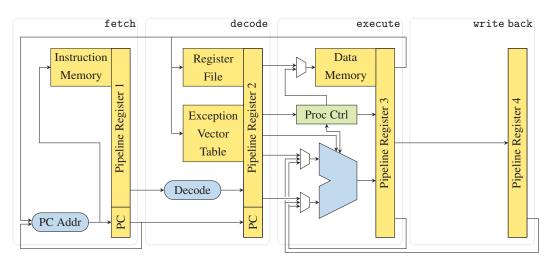

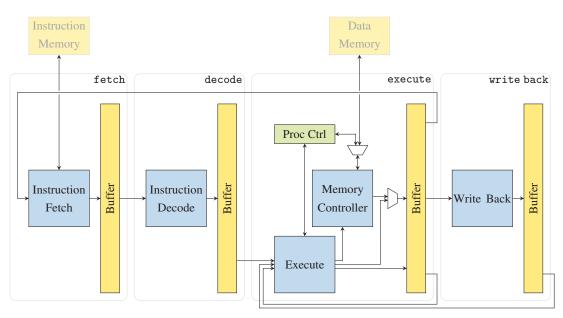

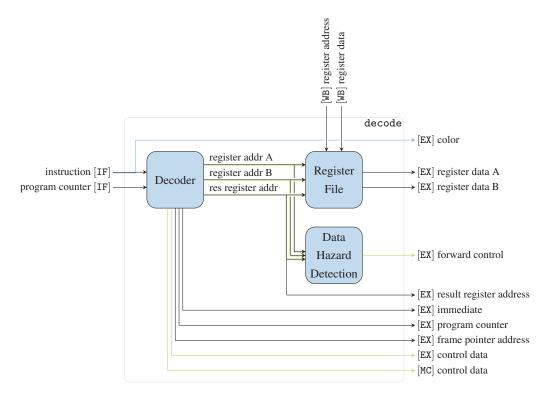

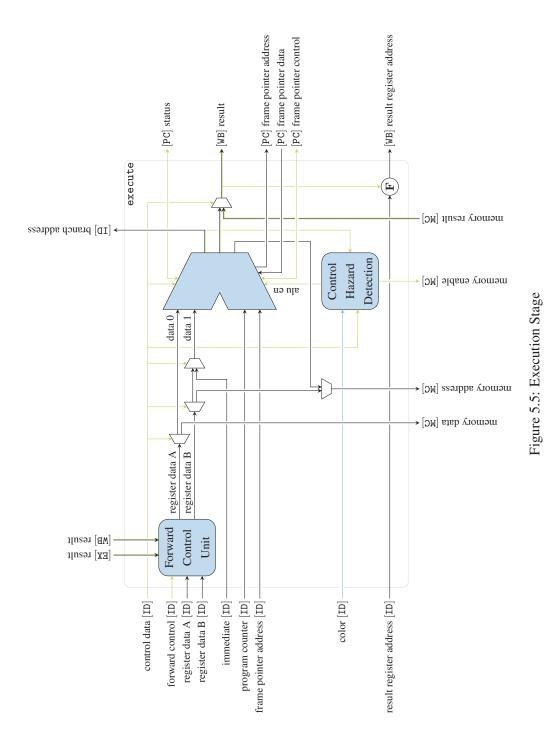

The ASCARTS coarse pipeline structure is identical to SCARTS. The processor's pipeline is four stages long. These comprise *Instruction Fetch*, *Instruction Decode*, *Execution and Memory Control* and *Write Back*. Between these stages buffers latch the data and control signals. Otherwise the first stage would have to wait until the last stage processed its data, which makes a pipelined structure useless. The third stage combines the execution and memory access as the ALU is barely used by memory access instructions. Only some need the adder for address calculations. While executing one of these instructions the processor slows down a bit. On the other hand an almost unnecessary stage can be omitted, which decreases required resources.